# ARM® Compiler Version 6.6

**User Guide**

## **ARM®** Compiler

#### **User Guide**

Copyright © 2016, 2017 ARM Limited or its affiliates. All rights reserved.

#### Release Information

#### **Document History**

| Issue   | Date             | Confidentiality  | Change                                                                           |

|---------|------------------|------------------|----------------------------------------------------------------------------------|

| 0606-00 | 04 November 2016 | Non-Confidential | ARM Compiler v6.6 Release                                                        |

| A       | 08 May 2017      | Non-Confidential | ARM Compiler v6.6.1 Release. Document number has changed from 100748 to DUI1093. |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of ARM. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, ARM makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to ARM's customers is not intended to create or refer to any partnership relationship with any other company. ARM may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any signed written agreement covering this document with ARM, then the signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

Words and logos marked with ® or TM are registered trademarks or trademarks of ARM Limited or its affiliates in the EU and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow ARM's trademark usage guidelines at <a href="http://www.arm.com/about/trademark-usage-guidelines.php">http://www.arm.com/about/trademark-usage-guidelines.php</a>

Copyright © 2016, 2017, ARM Limited or its affiliates. All rights reserved.

ARM Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

## **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

Unrestricted Access is an ARM internal classification.

### **Product Status**

The information in this document is Final, that is for a developed product.

### Web Address

http://www.arm.com

## Contents

## **ARM®** Compiler User Guide

|           | Preface                                                                             |                  |

|-----------|-------------------------------------------------------------------------------------|------------------|

|           | About this book                                                                     | 9                |

| Chapter 1 | Getting Started                                                                     |                  |

| 1         | 1.1 Introduction to ARM® Compiler 6                                                 | 1-12             |

| 1         | 1.2 Installing ARM® Compiler                                                        | 1-14             |

| 1         | 1.3 Accessing ARM® Compiler from ARM® DS-5                                          | 1-10             |

| 1         | 1.4 Accessing ARM <sup>®</sup> Compiler from Keil <sup>®</sup> μVision <sup>®</sup> | 1-18             |

| 1         | 1.5 Compiling a Hello World example                                                 |                  |

| 1         | 1.6 Running bare-metal images                                                       | 1-2 <sup>-</sup> |

| 1         | 1.7 ARM architectures supported by the toolchain                                    |                  |

| Chapter 2 | Using Common Compiler Options                                                       |                  |

| 2         | 2.1 Mandatory armclang options                                                      | 2-2              |

| 2         | 2.2 Selecting source language options                                               | 2-27             |

| 2         | 2.3 Selecting optimization options                                                  | 2-29             |

| 2         | 2.4 Building to aid debugging                                                       | 2-3°             |

| 2         | 2.5 Linker options for mapping code and data to target memory                       |                  |

| 2         | 2.6 Controlling diagnostic messages                                                 | 2-33             |

| 2         | 2.7 Selecting floating-point options                                                | 2-3              |

| 2         | 2.8 Compilation tools command-line option rules                                     |                  |

| Chapter 3 | Writing Optimized Code                                                              |                  |

| 3         | 3.1 Optimizing loops                                                                | 3-39             |

|            | 3.2  | Inlining functions                                               | 3-43       |

|------------|------|------------------------------------------------------------------|------------|

|            | 3.3  | Examining stack usage                                            |            |

|            | 3.4  | Packing data structures                                          | 3-47       |

| Chapter 4  | Usin | g Assembly and Intrinsics in C or C++ Code                       |            |

|            | 4.1  | Using intrinsics                                                 | 4-52       |

|            | 4.2  | Writing inline assembly code                                     | 4-53       |

|            | 4.3  | Calling assembly functions from C and C++                        | 4-55       |

| Chapter 5  | Мар  | ping Code and Data to the Target                                 |            |

|            | 5.1  | What the linker does to create an image                          | 5-58       |

|            | 5.2  | Placing data items for target peripherals with a scatter file    | 5-60       |

|            | 5.3  | Placing the stack and heap with a scatter file                   | 5-61       |

|            | 5.4  | Root region                                                      | 5-62       |

|            | 5.5  | Placing functions and data in a named section                    | 5-65       |

|            | 5.6  | Placing functions and data at specific addresses                 | 5-67       |

|            | 5.7  | Placing ARM® C and C++ library code                              | 5-75       |

|            | 5.8  | Placing unassigned sections                                      | 5-77       |

|            | 5.9  | Placing veneers with a scatter file                              | 5-87       |

|            | 5.10 | Preprocessing a scatter file                                     | 5-88       |

|            | 5.11 | Reserving an empty block of memory                               | 5-89       |

|            | 5.12 | Aligning regions to page boundaries                              | 5-91       |

|            | 5.13 | Aligning execution regions and input sections                    | 5-92       |

| Appendix A | Supp | porting reference information                                    |            |

|            | A.1  | Support level definitions                                        | Appx-A-94  |

|            | A.2  | Standards compliance in ARM® Compiler                            | Appx-A-97  |

|            | A.3  | Compliance with the ABI for the ARM Architecture (Base Standard) | Appx-A-98  |

|            | A.4  | GCC compatibility provided by ARM® Compiler 6                    | Appx-A-100 |

|            | A.5  | Toolchain environment variables                                  | Appx-A-101 |

|            | A.6  | Clang and LLVM documentation                                     | Appx-A-103 |

|            | Δ7   | Further reading                                                  | Anny-A-104 |

# List of Figures **ARM® Compiler User Guide**

| Figure 1-1 | A typical tool usage flow diagram                    | 1-13      |

|------------|------------------------------------------------------|-----------|

| Figure 1-2 | Accessing ARM Compiler settings from DS-5            |           |

| Figure 1-3 | Accessing the ARM Compiler version from Keil μVision | 1-18      |

| Figure 1-4 | Debug configurations                                 | 1-21      |

| Figure 3-1 | Structure without packing attribute or pragma        | 3-48      |

| Figure 3-2 | Structure with attribute packed                      |           |

| Figure 3-3 | Structure with pragma pack with 1 byte alignment     |           |

| Figure 3-4 | Structure with pragma pack with 2 byte alignment     |           |

| Figure 3-5 | Structure with pragma pack with 4 byte alignment     | 3-49      |

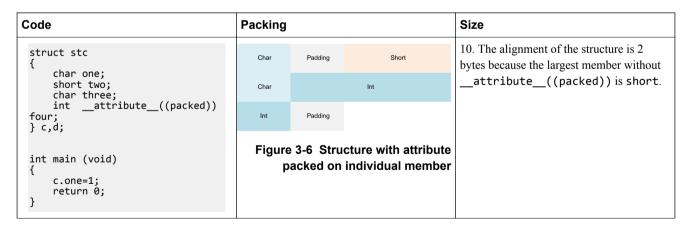

| Figure 3-6 | Structure with attribute packed on individual member | 3-49      |

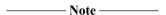

| Figure 5-1 | Memory map for fixed execution regions               | 5-63      |

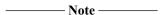

| Figure 5-2 | .ANY contingency                                     |           |

| Figure 5-3 | Reserving a region for the stack                     |           |

| Figure A-1 | Integration boundaries in ARM Compiler 6.            | Appx-A-95 |

# List of Tables **ARM® Compiler User Guide**

| Table 2-1  | Source language variants                                         | 2-27         |

|------------|------------------------------------------------------------------|--------------|

| Table 2-2  | Optimization example                                             | 2-29         |

| Table 2-3  | Optimization example                                             | 2-30         |

| Table 2-4  | Common diagnostic options                                        | 2-33         |

| Table 2-5  | Options for floating-point selection                             | 2-35         |

| Table 2-6  | Floating-point linkage for AArch32                               | 2-36         |

| Table 3-1  | Loop unrolling pragmas                                           | 3-39         |

| Table 3-2  | Loop optimizing example                                          | 3-39         |

| Table 3-3  | Loop examples                                                    | 3-40         |

| Table 3-4  | Example loops                                                    | 3-40         |

| Table 3-5  | Assembly code from vectorizable and non-vectorizable loops       | 3-41         |

| Table 3-6  | Function inlining                                                | 3-43         |

| Table 3-7  | Effect of -fno-inline-functions                                  | 3-44         |

| Table 3-8  | Packing members in a structure or union                          | 3-47         |

| Table 3-9  | Packing structures                                               | 3-48         |

| Table 3-10 | Packing individual members                                       | 3-49         |

| Table 5-1  | Input section properties for placement of .ANY sections          | 5-79         |

| Table 5-2  | Input section properties for placement of sections with next_fit | 5-81         |

| Table 5-3  | Input section properties for sections_a.o                        | 5-82         |

| Table 5-4  | Input section properties for sections_b.o                        | 5-82         |

| Table 5-5  | Sort order for descending_size algorithm                         | 5-82         |

| Table 5-6  | Sort order for cmdline algorithm                                 | <b>5-8</b> 3 |

| Table A-1  | Environment variables used by the toolchain                      | Appx-A-101   |

|            |                                                                  |              |

## **Preface**

This preface introduces the ARM® Compiler User Guide.

It contains the following:

• About this book on page 9.

8

### About this book

The ARM® Compiler Compiler User Guide provides information for users new to ARM Compiler 6.

## Using this book

This book is organized into the following chapters:

## Chapter 1 Getting Started

This introduces ARM® Compiler 6 and helps you start working with ARM Compiler 6 quickly. You can use ARM Compiler 6 from ARM DS-5, Keil MDK, or as a standalone product.

## **Chapter 2 Using Common Compiler Options**

There are a large number of options that you can use to control how ARM Compiler 6 generates code for your application. This lists the mandatory and commonly used optional command-line arguments, such as to control target selection, optimization, and debug view.

## **Chapter 3 Writing Optimized Code**

To make best use of the optimization capabilities of ARM Compiler, there are various options, pragmas, attributes, and coding techniques that you can use.

## Chapter 4 Using Assembly and Intrinsics in C or C++ Code

All code for a single application can be written in the same source language. This is usually a high-level language such as C or C++ that is compiled to instructions for ARM architectures. However, in some situations you might need lower-level control than what C and C++ provide.

## Chapter 5 Mapping Code and Data to the Target

There are various options in ARM Compiler to control how code, data and other sections of the image are mapped to specific locations on the target.

## Appendix A Supporting reference information

The various features in ARM Compiler might have different levels of support, ranging from fully supported product features to community features.

#### Glossary

The ARM Glossary is a list of terms used in ARM documentation, together with definitions for those terms. The ARM Glossary does not contain terms that are industry standard unless the ARM meaning differs from the generally accepted meaning.

See the ARM Glossary for more information.

## Typographic conventions

italic

Introduces special terminology, denotes cross-references, and citations.

#### bold

Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.

#### monospace

Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.

#### <u>mono</u>space

Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.

#### monospace italic

Denotes arguments to monospace text where the argument is to be replaced by a specific value.

## monospace bold

Denotes language keywords when used outside example code.

#### <and>

Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:

#### SMALL CAPITALS

Used in body text for a few terms that have specific technical meanings, that are defined in the *ARM glossary*. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE.

#### **Feedback**

## Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic

procedures if appropriate.

### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- The title ARM Compiler User Guide.

- The number ARM DUI1093A.

- If applicable, the page number(s) to which your comments refer.

- A concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

| Note | - |  |  |

|------|---|--|--|

|      |   |  |  |

ARM tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader.

## Other information

- ARM Information Center.

- ARM Technical Support Knowledge Articles.

- Support and Maintenance.

- ARM Glossary.

## Chapter 1 **Getting Started**

This introduces ARM® Compiler 6 and helps you start working with ARM Compiler 6 quickly. You can use ARM Compiler 6 from ARM DS-5, Keil MDK, or as a standalone product.

## It contains the following sections:

- 1.1 Introduction to ARM® Compiler 6 on page 1-12.

- 1.2 Installing ARM® Compiler on page 1-14.

- 1.3 Accessing ARM® Compiler from ARM® DS-5 on page 1-16.

- 1.4 Accessing ARM® Compiler from Keil® µVision® on page 1-18.

- 1.5 Compiling a Hello World example on page 1-19.

- 1.6 Running bare-metal images on page 1-21.

- 1.7 ARM architectures supported by the toolchain on page 1-23.

## 1.1 Introduction to ARM® Compiler 6

ARM Compiler 6 is ARM's most advanced C and C++ compilation toolchain for ARM Cortex processors. ARM Compiler 6 is co-developed alongside the ARM architecture. This has enabled the toolchain to be tuned to generate highly efficient code for embedded bare-metal applications ranging from small sensors to 64-bit devices.

ARM Compiler 6 is a component of *ARM DS-5 Development Studio* and *Keil MDK-ARM*. Alternatively, you can use ARM Compiler 6 as a *standalone product*. The list of features and processors supported by ARM Compiler 6 depends on the product edition. Refer to *ARM Developer* for the specification of the different standard products.

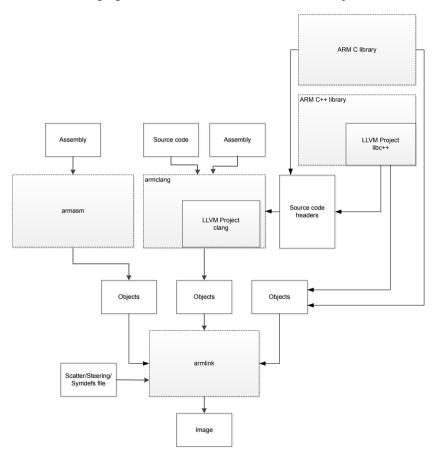

ARM Compiler 6 combines ARM's optimized tools and libraries, with a modern LLVM-based compiler framework. The components in ARM Compiler 6 are:

#### armclang

The compiler and integrated assembler. This compiles C, C++, and GNU assembly language sources.

The compiler is based on LLVM and Clang technology.

Clang is a compiler front end for LLVM, providing support for the C and C++ programming languages.

#### armasm

The legacy assembler. Only use armasm for legacy ARM syntax assembly code. Use the armclang assembler and GNU syntax for all new assembly files.

#### armlink

The linker. This combines the contents of one or more object files with selected parts of one or more object libraries to produce an executable program.

#### armar

The archiver. This enables sets of ELF object files to be collected together and maintained in archives or libraries. You can pass such a library or archive to the linker in place of several ELF files. You can also use the archive for distribution to a third party for further application development.

## fromelf

The image conversion utility. This can also generate textual information about the input image, such as its disassembly and its code and data size.

## **ARM C++ libraries**

The ARM C++ libraries are based on the LLVM libc++ project:

- The libc++abi library is a runtime library providing implementations of low-level language features.

- The libc++ library provides an implementation of the ISO C++ library standard. It depends on the functions provided by libc++abi.

#### **ARM C libraries**

The ARM C libraries provide:

- An implementation of the library features as defined in the C standards.

- Nonstandard extensions common to many C libraries.

- · POSIX extended functionality.

- Functions standardized by POSIX.

## **Application development**

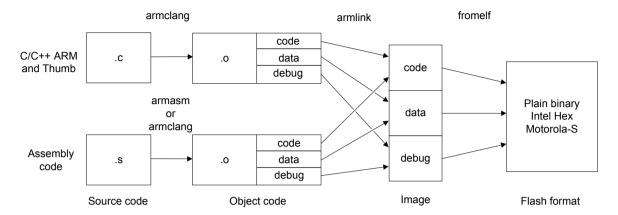

A typical application development flow might involve the following:

- Developing C/C++ source code for the main application (armclang).

- Developing assembly source code for near-hardware components, such as interrupt service routines (armclang, or armasm for legacy assembly code).

• Linking all objects together to generate an image (armlink).

documents, see the documentation on ARM Developer.

· Converting an image to flash format in plain binary, Intel Hex, and Motorola-S formats (fromelf).

The following figure shows how the compilation tools are used for the development of a typical application.

Figure 1-1 A typical tool usage flow diagram

ARM Compiler 6 has more functionality than the set of product features described in the documentation. The various features in ARM Compiler 6 can have different levels of support and guarantees. For more information, see *Support level definitions* on page Appx-A-94.

## 1.2 Installing ARM® Compiler

This topic lists the system requirements for running ARM Compiler, and then guides you through the installation process.

## **System Requirements**

ARM Compiler 6 is available for the following operating systems:

- Windows 64-bit.

- Windows 32-bit.

- Linux 64-bit.

For more information on system requirements see the ARM Compiler release note.

## Installing ARM® Compiler

You can install ARM Compiler as a standalone product on supported Windows and Linux platforms. If you use ARM Compiler as part of a development suite such as ARM DS-5 or Keil\*  $\mu$ Vision\*, then installing the development suite also installs ARM Compiler. The following instructions are for installing ARM Compiler as a standalone product.

## Prerequisites:

- 1. Download ARM Compiler 6.

- 2. Obtain a license. Contact your ARM sales representative or request a license.

- Set the ARMLMD\_LICENSE\_FILE environment variable to point to your license file or license server.

—— Note ——

This path must not contain double quotes on Windows. A path that contains spaces still works without the quotes.

If you need to set any other environment variable, such as ARM\_TOOL\_VARIANT, see *Toolchain environment variables* on page Appx-A-101 for more information.

### Installing a standalone ARM® Compiler on Windows platforms

To install ARM Compiler as a standalone product on Windows, you need the setup.exe installer on your machine. This is in the *ARM Compiler 6 download*:

- 1. On 64-bit platforms, run win-x86 64\setup.exe. On 32-bit platforms, run win-x86 32\setup.exe.

- 2. Follow the on-screen installation instructions.

If you have an older version of ARM Compiler 6 and you want to upgrade, ARM recommends that you uninstall the older version of ARM Compiler 6 before installing the new version of ARM Compiler 6.

## Installing a standalone ARM® Compiler on Linux platforms

To install ARM Compiler as a standalone product on Linux platforms, you need the install\_x86\_64.sh installer on your machine. This is in the *ARM Compiler 6 download*:

- 1. Run install x86 64.sh normally, without using the source Linux command.

- 2. Follow the on-screen installation instructions.

#### Uninstalling a standalone ARM® Compiler

To uninstall ARM Compiler on Windows, use the Control Panel:

- 1. Select Control Panel > Programs and Features.

- 2. Select the version that you want to uninstall, for example **ARM Compiler 6.5**.

- 3. Click the **Uninstall** button.

To uninstall ARM Compiler on Linux, delete the ARM Compiler 6 installation directory for the compiler version you want to delete.

For more information on installation, see the ARM Compiler release note.

## Related tasks

1.3 Accessing ARM® Compiler from ARM® DS-5 on page 1-16.

1.4 Accessing ARM® Compiler from Keil® µVision® on page 1-18.

## 1.3 Accessing ARM® Compiler from ARM® DS-5

ARM DS-5 is a development suite that provides ARM Compiler 6 as a built-in toolchain.

This task describes how to access and configure ARM Compiler from the DS-5 environment.

## **Prerequisites**

Ensure you have DS-5 installed. Create a new C or C++ project in DS-5. For information on creating new projects in DS-5, see *Creating a new C or C++ project*.

### **Procedure**

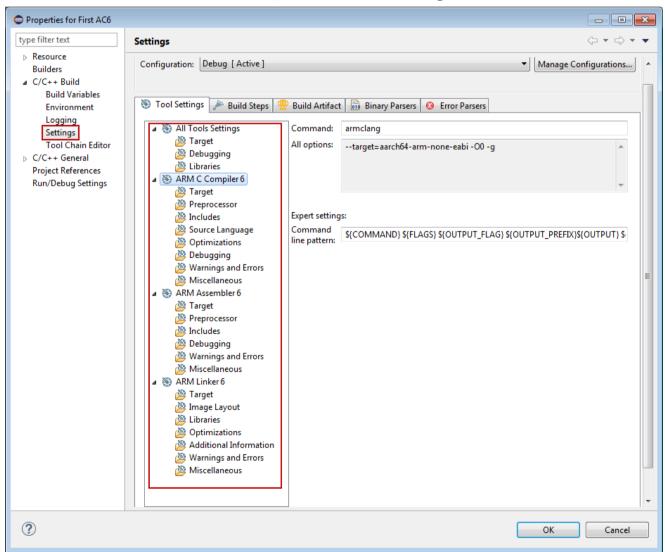

- 1. Select the project in DS-5.

- 2. Select **Project** > **Properties**.

- 3. From the left-hand side menu, select C/C++ Build > Tool Chain Editor.

- 4. In the Current toolchain options, select ARM Compiler 6 (DS-5 built-in) if this is not already selected.

- 5. From the left-hand side menu, select C/C++ Build > Settings.

Figure 1-2 Accessing ARM Compiler settings from DS-5

For information about using DS-5, see the DS-5 Getting Started Guide and DS-5 Debugger Guide.

6. After setting the compiler options, to build the project, right-click on the project and select **Build Project**.

## **Related references**

1.2 Installing ARM® Compiler on page 1-14.

## 1.4 Accessing ARM® Compiler from Keil® µVision®

Keil  $\mu$ Vision is a microprocessor development suite that provides ARM Compiler 6 as a builtin toolchain.

This task describes how to access and configure ARM Compiler from the Keil µVision environment:

## **Prerequisites**

Ensure you have Keil μVision installed. Create a new project in μVision.

### **Procedure**

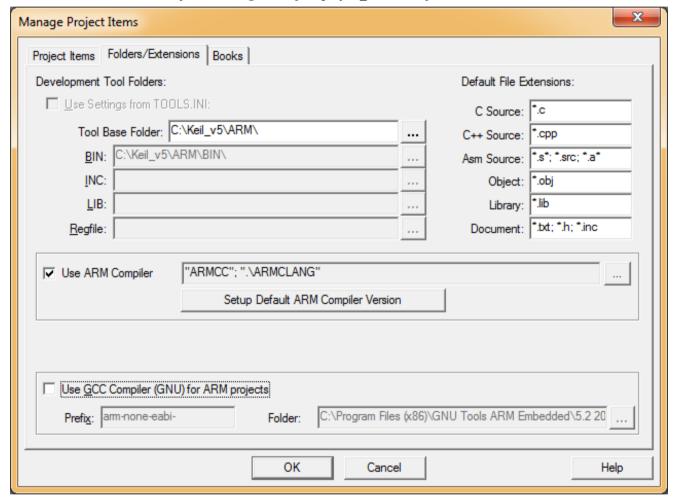

- 1. Select the project in μVision.

- 2. Select Project > Manage > Project 'project name' Project Items.

Figure 1-3 Accessing the ARM Compiler version from Keil µVision

- 3. Select the Folders/Extensions tab.

- 4. Click Setup Default ARM Compiler Version.

- 5. For each device, select the version of ARM Compiler you want to use. For example, v6.6.

- 6. Click **OK** to close each of the dialog boxes in turn.

## Related references

1.2 Installing ARM® Compiler on page 1-14.

## 1.5 Compiling a Hello World example

These examples show how to use the ARM Compiler toolchain to build and inspect an executable image from C/C++ source files.

#### The source code

The source code that is used in the examples is a single C source file, hello.c, to display a greeting message:

```

#include <stdio.h>

int main() {

printf("Hello World\n");

return 0;

}

```

## Compiling in a single step

When compiling code, you must first decide which target the executable is to run on. An ARMv8-A target can run in different states:

- AArch64 state targets execute A64 instructions using 64-bit wide general-purpose registers.

- AArch32 state targets execute A32 or T32 instructions using 32-bit wide general-purpose registers.

The --target option determines which target state to compile for. This option is a mandatory option.

To create an executable for an AArch64 target in a single step:

```

armclang --target=aarch64-arm-none-eabi hello.c

```

This command creates an executable, a.out.

The --target option selects the target that you want to compile for. This example compiles for an AArch64 state target. Because only --target is specified, the compiler defaults to generating code that runs on any ARMv8-A target. You can also use -mcpu to target a specific processor.

To create an executable for an AArch32 target in a single step:

```

armclang --target=arm-arm-none-eabi -mcpu=cortex-a53 hello.c

```

In this example, there is no default target for AArch32 state, so you must specify either -march to target an architecture or -mcpu to target a processor. This example uses -mcpu to target the Cortex\*-A53 processor. The compiler generates code that is optimized specifically for the Cortex-A53, but might not run on other processors.

Use -mcpu=list or -march=list to see all available options.

#### Beyond the defaults

Compiler options let you specify precisely how the compiler behaves when generating code.

The *armclang Reference Guide* describes all the supported options, but here are some of the most common:

- Including debug information. The -g option tells the compiler to produce DWARF debug information. You can then use a compatible debugger, such as ARM DS-5 Debugger, to load, run, and debug images.

- Optimization. The -Olevel option specifies the level of optimization to use when compiling source files. The default is -O0, with no optimization. Different optimization levels let you control what type of optimization the compiler performs. For example, -Os aims to reduce code size, balancing code size against code speed. Whereas -Omax uses aggressive optimizations to target performance optimization.

- Instruction set. AArch32 targets support two instruction sets: A32 (32-bit instructions, emphasizing performance) and T32 (mixed 32-bit and 16-bit instructions, emphasizing code density). The -marm and -mthumb options let you specify which instruction set to target.

## **Examining the executable**

The frome1f tool lets you examine a compiled binary, extract information about it, or convert it.

For example, you can:

• Disassemble the code that is contained in the executable:

```

fromelf --text -c a.out

main

0x000081a0:

e92d4800

PUSH

\{r11, lr\}

.H-.

0x000081a4:

e1a0b00d

MOV

r11.sp

sp,sp,#0x10

0x000081a8:

e24dd010

SUB

r0,#0

0x000081ac:

e3a00000

MOV

r0,[r11,#-4]

0x000081b0:

e50b0004

STR

0x000081b4:

e30a19cc

r1.#0xa9cc

MOV

```

• Examine the size of code and data in the executable:

```

fromelf --text -z a.out

RO Data

Code (inc. data)

RW Data

ZI Data

Debug

Object Name

10436

492

596

16

348

3468

a.out

10436

596

16

ROM Totals for a.out

```

Convert the ELF executable image to another format, for example a plain binary file:

```

fromelf --bin --output=outfile.bin a.out

```

## Compiling and linking as separate steps

For simple projects with small numbers of source files, compiling and linking in a single step might be the simplest option:

```

armclang --target=aarch64-arm-none-eabi file1.c file2.c -o image.axf

```

This example compiles the two source files file1.c and file2.c for an AArch64 state target. The -o option specifies that the filename of the generated executable is image.axf.

More complex projects might have many more source files. It is not efficient to compile every source file at every compilation, because most source files are unchanged. To avoid compiling unchanged source files, you can compile and link as separate steps. In this way, you can then use a build system (such as make) to only compile those source files that have changed, then link the object code together. The armclang -c option tells the compiler to compile to object code and stop before calling the linker:

```

armclang -c --target=aarch64-arm-none-eabi file1.c armclang -c --target=aarch64-arm-none-eabi file2.c armlink file1.o file2.o -o image.axf

```

These commands do the following:

- Compile file1.c to object code, and save using the default name file1.o.

- Compile file2.c to object code, and save using the default name file2.o.

- Link the object files file1.o and file2.o to produce an executable that is called image.axf.

In the future, if you modify file2.c, you can rebuild the executable by recompiling only file2.c then linking the new file2.o with the existing file1.o to produce a new executable:

```

armclang -c --target=aarch64-arm-none-eabi file2.c armlink file1.o file2.o -o image.axf

```

## **Related information**

```

armclang --target option.

armclang -march option.

armclang -mcpu option.

```

## 1.6 Running bare-metal images

By default, ARM Compiler produces bare-metal images. Bare-metal images can run standalone without an operating system. The images can run on a hardware target or on a software application that simulates the target, such as Fast Models or Fixed Virtual Platforms.

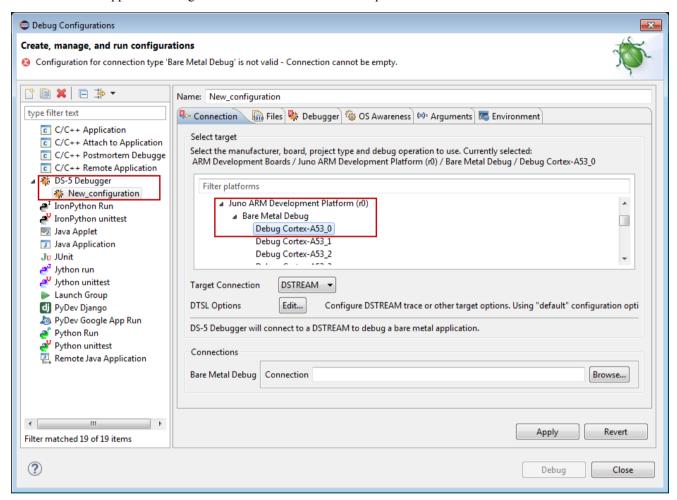

If you are using DS-5, you can select **Run > Debug Configurations** to configure and load your application image into either a model or hardware platform.

Figure 1-4 Debug configurations

For more information on configuring and running the image using DS-5, see the *DS-5 Debugger User Guide*.

By default, the C library in ARM Compiler uses special functions to access the input and output interfaces on the host computer. These functions implement a feature called semihosting. Semihosting is useful when the input and output on the hardware is not available during the early stages of application development.

When you want your application to use the input and output interfaces on the hardware, you must retarget the required semihosting functions in the C library.

For more information on configuring the DS-5 Debugger settings, see *Configuring debug connections in DS-5 Debugger*.

## Outputting debug messages from your application

The semihosting feature enables your bare-metal application, running on an ARM target, to use the input and output interface on a host computer. This feature requires the use of a debugger that supports semihosting, for example DS-5 Debugger, on the host computer.

A bare-metal application that uses semihosting does not use the input and output interface of the development platform. When the input and output interfaces on the development platform are available, you must reimplement the necessary semihosting functions to use the input and output interfaces on the development platform.

For more information, see how to use the libraries in *semihosting* and *nonsemihosting* environments.

#### Related information

ARM DS-5 Debugger User Guide.

## 1.7 ARM architectures supported by the toolchain

ARM Compiler supports a number of different architecture profiles.

ARM Compiler supports the following architectures:

- ARMv8-A bare metal targets.

- ARMv8.1-A bare metal targets.

- ARMv8.2-A bare metal targets.

- ARMv8.3-A bare metal targets.

- ARMv8-R targets.

- ARMv8-M targets.

- ARMv7-A bare metal targets.

- ARMv7-R targets.

- ARMv7-M targets.

- ARMv6-M targets.

When compiling code, the compiler needs to know which architecture to target in order to take advantage of features specific to that architecture.

To specify a target, you must supply the target execution state (AArch32 or AArch64), together with either a target architecture (for example ARMv8-A) or a target processor (for example Cortex-A53).

To specify a target execution state (AArch64 or AArch32) with armclang, use the mandatory --target command-line option:

--target=arch-vendor-os-abi

Supported targets include:

aarch64-arm-none-eabi

Generates A64 instructions for AArch64 state. Implies -march=armv8-a unless -march or -mcpu is specified.

arm-arm-none-eabi

Generates A32 and T32 instructions for AArch32 state. Must be used in conjunction with - march (to target an architecture) or -mcpu (to target a processor).

To generate generic code that runs on any processor with a particular architecture, use the -march option. Use the -march=list option to see all supported architectures.

To optimize your code for a particular processor, use the -mcpu option. Use the -mcpu=list option to see all supported processors.

| <br>Note — |

|------------|

| 11010      |

The --target, -march, and -mcpu options are armclang options. For all of the other tools, such as armasm and armlink, use the --cpu option to specify target processors and architectures.

#### **Related information**

armclang --target option. armclang -march option. armclang -mcpu option. armlink --cpu option. ARM Glossary.

## Chapter 2 **Using Common Compiler Options**

There are a large number of options that you can use to control how ARM Compiler 6 generates code for your application. This lists the mandatory and commonly used optional command-line arguments, such as to control target selection, optimization, and debug view.

## It contains the following sections:

- 2.1 Mandatory armclang options on page 2-25.

- 2.2 Selecting source language options on page 2-27.

- 2.3 Selecting optimization options on page 2-29.

- 2.4 Building to aid debugging on page 2-31.

- 2.5 Linker options for mapping code and data to target memory on page 2-32.

- 2.6 Controlling diagnostic messages on page 2-33.

- 2.7 Selecting floating-point options on page 2-35.

- 2.8 Compilation tools command-line option rules on page 2-37.

## 2.1 Mandatory armclang options

When using armclang, you must always specify a target on the command-line. Depending on the target you use, you might also have to specify an architecture or processor.

## Specifying a target

| • | To generate A64 instructions for AArch64 state, specifytarget=aarch64-arm-none-eabi.                                                                                                 |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Note                                                                                                                                                                                 |

|   | For AArch64, the default architecture is ARMv8-A.                                                                                                                                    |

|   |                                                                                                                                                                                      |

| • | To generate A32 and T32 instructions for AArch32 state, specifytarget=arm-arm-none-eabi. To specify generation of either A32 or T32 instructions, use -marm or -mthumb respectively. |

|   | Note                                                                                                                                                                                 |

|   | AArch32 has no defaults. You must always specify an architecture or processor.                                                                                                       |

|   |                                                                                                                                                                                      |

## Specifying an architecture

To generate code for a specific architecture, use the *-march* option. The supported architectures vary according to the selected target.

To see a list of all the supported architectures for the selected target, use -march=list.

## Specifying a processor

To generate code for a specific processor, use the *-mcpu* option. The supported processors vary according to the selected target.

To see a list of all the supported processors for the selected target, use -mcpu=list.

It is also possible to enable or disable optional architecture features, by using the +[no]feature notation. For a list of the architecture features that your processor supports, see the processor product documentation. See the *armclang Reference Guide* for a *list of architecture features* that ARM Compiler supports.

| Use +feature or +nofeature to explicitly enable or disable an optional architecture feature.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| You do not need to specify both the architecture and processor. The compiler infers the architecture fro the processor. If you only want to run code on one particular processor, you can specify the specific processor. Performance is optimized, but code is only guaranteed to run on that processor. If you want your code to run on a range of processors from a particular architecture, you can specify the architectur. The code runs on any processor implementation of the target architecture, but performance might be impacted. |

### **Examples**

These examples compile and link the input file helloworld.c:

• To compile for ARMv8-A in AArch64 state, use:

```

armclang --target=aarch64-arm-none-eabi -march=armv8-a helloworld.c

```

• To compile for ARMv8-R in AArch32 state, use:

```

armclang --target=arm-arm-none-eabi -march=armv8-r helloworld.c

```

• To compile for ARMv8-M mainline profile, use:

```

armclang --target=arm-arm-none-eabi -march=armv8-m.main helloworld.c

```

• To compile for a Cortex-A53 processor in AArch64 state, use:

```

armclang --target=aarch64-arm-none-eabi -mcpu=cortex-a53 helloworld.c

```

• To compile for a Cortex-A53 processor in AArch32 state, use:

```

armclang --target=arm-arm-none-eabi -mcpu=cortex-a53 helloworld.c

```

• To compile for a Cortex-M4 processor, use:

```

armclang --target=arm-arm-none-eabi -mcpu=cortex-m4 helloworld.c

```

• To compile for a Cortex-M33 processor, with DSP disabled, use:

```

armclang --target=arm-arm-none-eabi -mcpu=cortex-m33+nodsp helloworld.c

```

## **Related information**

```

armclang --target option.

armclang -march option.

armclang -mcpu option.

armclang -marm option.

armclang -mthumb option.

```

## 2.2 Selecting source language options

ARM Compiler infers the source language, for example C or C++, from the filename extension. You can force ARM Compiler to compile for a specific source language using the -x option. ARM Compiler can also compile different variants of C and C++ source code. You can specify the variant using the -std option.

## Source language

By default ARM Compiler treats files with .c extension as C source files. If you want to compile a .c file, for example file.c, as a C++ source file, use the -xc++ option:

```

armclang --target=aarch64-arm-none-eabi -march=armv8-a -xc++ file.c

```

By default ARM Compiler treats files with .cpp extension as C++ source files. If you want to compile a .cpp file, for example file.cpp, as a C source file, use the -xc option:

```

armclang --target=aarch64-arm-none-eabi -march=armv8-a -xc file.cpp

```

The -x option only applies to input files that follow it on the command line.

## Source language standard

ARM Compiler supports Standard and GNU variants of source languages as shown in the following table.

Table 2-1 Source language variants

| Standard C | GNU C | Standard C++ | GNU C++ |

|------------|-------|--------------|---------|

| c90        | gnu90 | c++98        | gnu++98 |

| c99        | gnu99 | c++03        |         |

| c11        | gnu11 | c++11        | gnu++11 |

The default language standard for C code is gnu11. The default language standard for C++ code is gnu++98. To specify a different source language standard, use the -std=name option. ARM Compiler also supports C++14 as a community feature.

ARM Compiler supports various language extensions, including GCC extensions, which you can use in your source code. The GCC extensions are only available when you specify one of the GCC C or C++ language variants. For more information on language extensions, see the *ARM C Language Extensions* in ARM Compiler.

Since ARM Compiler uses the available language extensions by default, it does not adhere to the strict ISO Standard. To compile to strict ISO standard for the source language, you must use the -Wpedantic option. This shows warnings where the source code violates the ISO Standard. ARM Compiler does not support strict adherence to C++98 or C++03.

If you do not use -Wpedantic, ARM Compiler uses the available language extensions without warning. However, where language variants produce different behavior, the behavior of the language variant specified by -std will apply.

Copyright © 2016, 2017 ARM Limited or its affiliates. All rights reserved. Non-Confidential The following example shows the use of a variable length array, which is a C99 feature. In this example, the function declares an array i, with variable length n.

```

#include <stdlib.h>

void function(int n) {

int i[n];

}

```

ARM Compiler does not warn when compiling the example for C99 with -Wpedantic:

```

armclang --target=aarch64-arm-none-eabi -march=armv8-a -c -std=c99 -Wpedantic file.c

```

ARM Compiler does warn about variable length arrays when compiling the example for C90 with - Wpedantic:

```

armclang --target=aarch64-arm-none-eabi -march=armv8-a -c -std=c90 -Wpedantic file.c

```

Outputs the warning:

```

file.c:4:8: warning: variable length arrays are a C99 feature [-Wvla-extension]

int i[n];

^

1 warning generated.

```

## 2.3 Selecting optimization options

ARM Compiler performs several optimizations to reduce the code size and improve the performance of your application. However, optimization techniques can result in the loss of debug information, increased build time, or increase in image size. Optimization levels are always a trade-off between these three parameters.

ARM Compiler provides optimization options for the different optimization trade-offs. Primarily, you can optimize for performance or for image size. However, there are several options for finer control of the optimizations techniques. The optimization options are:

-00

This is the default optimization setting. It turns off most optimizations, and gives the best correlation between the built image and your application source code.

-01

This results in more optimizations for performance, when compared to -00. It also reduces the information available for debugging, and might result in an increased image size. ARM recommends this option for debugging.

-02

This results in more optimizations for performance, when compared to -01. It also reduces the information available for debugging, and might result in an increased image size.

-03

This results in more optimizations for performance, when compared to -02. It also reduces the information available for debugging, and might result in an increased image size.

-Ofast

This results in more optimizations for performance, when compared to -03. It also reduces the information available for debugging, and might result in an increased image size. At this optimization level, ARM Compiler might violate certain language standards.

-Omax

This results in more optimizations for performance, when compared to -Ofast. It also reduces the information available for debugging, and might result in an increased image size. At this optimization level, ARM Compiler might violate certain language standards. ARM recommends this option for best performance.

-0s

This results in reduced code size, and also reduces the information available for debugging. Using this option might make your code slower.

-0z

This results in more reduced image size, when compared to -0s, and also reduces the information available for debugging. Using this option is likely to make your code slower than -0s. ARM recommends this option for best code size.

The example shows the optimization performed with the -O1 optimization option. To perform this optimization, compile your source file using:

```

armclang --target=arm-arm-none-eabi -march=armv7-a -O1 -c -S file.c

```

Table 2-2 Optimization example

| Source code in file.c                                                              | Optimized output from armclang                |  |

|------------------------------------------------------------------------------------|-----------------------------------------------|--|

| <pre>int dummy() {     int x=10, y=20;     int z;     z=x+y;     return 0; }</pre> | dummy:     .fnstart     movs r0, #0     bx lr |  |

The example shows the optimization performed with the -O0 optimization option. To perform this optimization, compile your source file using:

```

armclang --target=arm-arm-none-eabi -march=armv7-a -00 -c -S file.c

```

Table 2-3 Optimization example

| Source code in file.c                                                              | Unoptimized output from armclang                    |

|------------------------------------------------------------------------------------|-----------------------------------------------------|

| <pre>int dummy() {     int x=10, y=20;     int z;     z=x+y;     return 0; }</pre> | <pre>dummy:     .fnstart     .pad #12     sub</pre> |

## 2.4 Building to aid debugging

During application development, you must debug the image that you build. The ARM Compiler tools have various features that provide a good debug view. There are also some features you must avoid using when building an image for debugging.

## Available command-line options

To build an image for debugging, you must compile with the -g option. This option allows you to specify the DWARF format to use. The -g option is a synonym for -gdwarf-4. You can specify DWARF 2 or DWARF 3 if necessary, for example:

```

armclang -gdwarf-3

```

When linking, there are several armlink options available to help improve the debug view:

- --debug. This option is the default.

- --no remove to retain all input sections in the final image even if they are unused.

- --bestdebug. When different input objects are compiled with different optimization levels, this

option enables linking for the best debug illusion.

## Effect of optimizations on the debug view

To build an application that gives the best debug view, it is better to use options that give the fewest optimizations. ARM recommends using optimization level -01 for debugging. This option gives good code density with a satisfactory debug view.

Higher optimization levels perform progressively more optimizations with correspondingly poorer debug views.

The compiler attempts to automatically inline functions at optimization levels -02 and -03. If you have to use these optimization levels, disable the automatic inlining with the armclang option -fno-inline-functions. The linker inlining is disabled by default.

#### Support for debugging overlaid programs

The linker provides various options to support overlay-aware debuggers:

- --emit debug overlay section

- --emit debug overlay relocs

These options permit an overlay-aware debugger to track which overlay is active.

### Features to avoid when building an image for debugging

Avoid using the following in your source code:

- The \_\_attribute\_\_((always\_inline)) function attribute. Qualifying a function with this attribute

forces the compiler to inline the function. If you also use the -fno-inline-functions option, the

function is inlined.

- The \_\_declspec(noreturn) attribute and the \_\_attribute\_\_((noreturn)) function attribute. These attributes limit the ability of a debugger to display the call stack.

Avoid using the following features when building an image for debugging:

- Link time optimization. This feature performs aggressive optimizations and can remove large chunks of code.

- The armlink --no\_debug option.

- The armlink --inline option. This option changes the image in such a way that the debug information might not correspond to the source code.

## 2.5 Linker options for mapping code and data to target memory

For an image to run correctly on a target, you must place the various parts of the image at the correct locations in memory. Linker command-line options are available to map the various parts of an image to target memory.

The options implement the scatter-loading mechanism that describes the memory layout for the image. The options that you use depend on the complexity of your image:

- For simple images, use the following memory map related options:

- --ro\_base to specify the address of both the load and execution region containing the RO output section.

- --rw\_base to specify the address of the execution region containing the RW output section.

- --zi base to specify the address of the execution region containing the ZI output section.

For objects that include *execute-only* (XO) sections, the linker provides the --xo\_base option to locate the XO sections. That is, objects that are targeted at ARMv7-M or ARMv8-M architectures, or objects that are built with the armclang -mthumb option,

• For complex images, use a text format scatter-loading description file. This file is known as a scatter file, and you specify it with the --scatter option.

You cannot use the memory map related options with the --scatter option.

#### **Examples**

The following example shows how to place code and data using the memory map related options:

```

armlink --ro_base=0x0 --rw_base=0x400000 --zi_base=0x405000 --first="init.o(init)" init.o main.o

```

----- Note ------

In this example, --first is also included to make sure that the initialization routine is executed first.

The following example shows a scatter file, scatter.scat, that defines an equivalent memory map:

To link with this scatter file, use the following command:

```

armlink --scatter=scatter.scat init.o main.o

```

## 2.6 Controlling diagnostic messages

ARM Compiler provides diagnostics messages in the form of warnings and errors. You can use options to suppress these messages or enable them as either warnings or errors.

ARM Compiler lists all the warnings and errors it encounters during the compiling and linking process. However, if you specify multiple source files, and ARM Compiler encounters an error from a source file, it does not report any diagnostic information from the other source files that it has not processed.

Diagnostic messages from ARM Compiler include the following information:

- Name of file that contains the error or warning.

- Line number in the file that contains the error or warning.

- Character in the line that is associated with the error or warning.

- Description of the error or warning.

- A diagnostic flag of the form -Wflag, for example -Wvla-extension, to identify the error or warning. Only the messages that you can suppress have an associated flag. Errors that you cannot suppress do not have an associated flag.

An example warning diagnostic message is:

```

file.c:8:7: warning: variable length arrays are a C99 feature [-Wvla-extension] int i[n];

```

This warning message tells you:

- The file that contains the problem is called file.c.

- The problem is on line 8 of file.c, and starts at character 7.

- The warning is about the use of a variable length array i[n].

- The flag to identify, enable or disable this diagnostic message is vla-extension.

The following are common options that control diagnostic output from ARM Compiler.

Table 2-4 Common diagnostic options

| Option         | Description                                                       |  |

|----------------|-------------------------------------------------------------------|--|

| -Werror        | Turn all warnings into errors.                                    |  |

| -Werror=foo    | Turn warning flag foo into an error.                              |  |

| -Wno-error=foo | Leave warning flag foo as a warning even if -Werror is specified. |  |

| -Wfoo          | Enable warning flag foo.                                          |  |

| -Wno-foo       | Suppress warning flag foo.                                        |  |

| -w             | Suppress all warnings. Note that this is a lowercase w.           |  |

| -Weverything   | Enable all warnings.                                              |  |

See *Controlling Errors and Warnings* in the *Clang Compiler User's Manual* for full details about controlling diagnostics with armclang.

### **Examples of controlling diagnostic messages**

Copy the following code example to file.c and compile it with ARM Compiler to see example diagnostic messages.

```

#include <stdlib.h>

#include <stdio.h>

void function (int x) {

int i;

```

```

int y=i+x;

printf("Result of %d plus %d is %d\n", i, x); /* Missing an input argument for the third

%d */

call(); /* This function has not been declared and is therefore an implicit declaration

return;

}

```

Compile file.c using:

```

armclang --target=aarch64-arm-none-eabi -march=armv8 -c file.c

```

By default armclang checks the format of printf() statements to ensure that the number of % format specifiers matches the number of data arguments. Therefore ARM Compiler generates this diagnostic message:

By default armclang compiles for the gnull standard for .c files. This language standard does not allow implicit function declarations. Therefore ARM Compiler generates this diagnostic message:

```

file.c:11:3: warning: implicit declaration of function 'call' is invalid C99 [-Wimplicit-

function-declaration]

call();

^

```

To suppress all warnings, use -w:

```

armclang --target=aarch64-arm-none-eabi -march=armv8-a -c file.c -w

```

To suppress only the -Wformat warning, use -Wno-format:

```

armclang --target=aarch64-arm-none-eabi -march=armv8-a -c file.c -Wno-format

```

To enable the -Wformat message as an error, use -Werror=format:

```

armclang --target=aarch64-arm-none-eabi -march=armv8-a -c file.c -Werror=format

```

Some diagnostic messages are suppressed by default. To see all diagnostic messages use -Weverything:

```

armclang --target=aarch64-arm-none-eabi -march=armv8-a -c file.c -Weverything

```

## 2.7 Selecting floating-point options

ARM Compiler supports floating-point arithmetic and floating-point data types in your source code or application. ARM Compiler supports floating-point arithmetic either by using libraries that implement floating-point arithmetic in software, or by using the hardware floating-point registers and instructions that are available on most ARM architecture-based processors.

You can use various options that determine how ARM Compiler generates code for floating-point arithmetic. Depending on your target, you might need to specify one or more of these options to generate floating-point code that correctly uses floating-point hardware or software libraries.

Table 2-5 Options for floating-point selection

| Option               | Description                                                                                                          |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------|--|

| armclang -mfpu       | Specify the floating point architecture to the compiler.                                                             |  |

| armclang -mfloat-abi | Specify the floating-point linkage to the compiler.                                                                  |  |

| armclang -march      | Specify the target architecture to the compiler. This automatically selects the default floating-point architecture. |  |

| armclang -mcpu       | Specify the target processor to the compiler. This automatically selects the default floating-point architecture.    |  |

| armlinkfpu           | Specify the floating-point architecture to the linker.                                                               |  |

## Benefits of using floating-point hardware versus software floating-point libraries

Code that uses floating-point hardware is more compact and faster than code that uses software libraries for floating-point arithmetic. But code that uses the floating-point hardware can only be run on processors that have the floating-point hardware. Code that uses software floating-point libraries can also run on ARM processors that do not have floating-point hardware, for example Cortex-M0, and this makes the code more portable. You might also disable floating-point hardware to reduce power consumption.

## Enabling and disabling the use of floating-point hardware

By default, ARM Compiler uses the available floating-point hardware that is based on the target you specify for -mcpu or -march. However, you can force ARM Compiler to disable the floating-point hardware. This forces ARM Compiler to use software floating-point libraries, if available, to perform the floating-point arithmetic in your source code.

When compiling for AArch64:

- By default, ARM Compiler uses floating-point hardware that is available on the target.

- To disable the use of floating-point arithmetic, use the +nofp extension on the -mcpu or -march options.

```

armclang --target=aarch64-arm-none-eabi -march=armv8-a+nofp

```

- Software floating-point library for AArch64 is not currently available. Therefore, ARM Compiler does not support floating-point arithmetic in your source code, if you disable floating-point hardware when compiling for AArch64 targets.

- Disabling floating-point arithmetic does not disable all the floating-point hardware because the floating-point hardware is also used for Advanced SIMD arithmetic. To disable all Advanced SIMD and floating-point hardware, use the +nofp+nosimd extension on the -mcpu or -march options:

```

armclang --target=aarch64-arm-none-eabi -march=armv8-a+nofp+nosimd

```

See the armclang Reference Guide for more information on -march option.

When compiling for AArch32:

- By default, ARM Compiler uses floating-point hardware that is available on the target, with the exception for ARMv6-M, which does not have any floating-point hardware.

- To disable the use of floating-point hardware instructions, use the -mfpu=none option.

```

armclang --target=arm-arm-none-eabi -march=armv8-a -mfpu=none

```

On AArch32 targets, using -mfpu=none disables the hardware for both Advanced SIMD and floating-point arithmetic. You can use -mfpu to selectively enable certain hardware features. For example, if you want to use the hardware for Advanced SIMD operations on an ARMv7 architecture-based processor, but not for floating-point arithmetic, then use -mfpu=neon.

```

armclang --target=arm-arm-none-eabi -march=armv7-a -mfpu=neon

```

See the armclang Reference Guide for more information on -mfpu option.

## Floating-point linkage

Floating-point linkage refers to how the floating-point arguments are passed to and returned from function calls.

For AArch64, ARM Compiler always uses hardware floating-point registers to pass and return floating-point values. This is called hardware linkage.

For AArch32, ARM Compiler can use hardware linkage or software linkage. When using software linkage, floating-point values are passed and returned using the general purpose registers. By default, ARM Compiler uses software linkage. You can use the -mfloat-abi option to force hardware linkage or software linkage.

Table 2-6 Floating-point linkage for AArch32

| -mfloat-abi                  | Linkage                                                                                                                         | Floating-point operations                                                                                          |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| hard                         | Hardware linkage. Use floating-point registers. But if -mfpu=none is specified for AArch32, then use general-purpose registers. | Use hardware floating-point instructions. But if -mfpu=none is specified for AArch32, then use software libraries. |

| soft                         | Software linkage. Use general-purpose registers.                                                                                | Use software libraries without floating-point hardware.                                                            |

| softfp (This is the default) | Software linkage. Use general-purpose registers.                                                                                | Use hardware floating-point instructions. But if -mfpu=none is specified for AArch32, then use software libraries. |

Code with hardware linkage can be faster than the same code with software linkage. However, code with software linkage can be more portable because it does not require the hardware floating-point registers. Hardware floating-point is not available on some architectures such as ARMv6-M, or on processors where the floating-point hardware might be powered down for energy efficiency reasons.

See the armclang Reference Guide for more information on -mfloat-abi option.

See the *armlink User Guide* for more information on how the *--fpu* option specifies the linkage type and floating-point hardware.

# 2.8 Compilation tools command-line option rules

You can use command-line options to control many aspects of the compilation tools' operation. There are rules that apply to each tool.

#### armclang option rules

armclang follows the same syntax rules as GCC. Some options are preceded by a single dash -, others by a double dash --. Some options require an = character between the option and the argument, others require a space character.

#### armasm, armar, armlink, and fromelf command-line syntax rules

The following rules apply, depending on the type of option:

#### Single-letter options

All single-letter options, including single-letter options with arguments, are preceded by a single dash -. You can use a space between the option and the argument, or the argument can immediately follow the option. For example:

```

armar -r -a obj1.o mylib.a obj2.o armar -r -aobj1.o mylib.a obj2.o

```

#### **Keyword options**

All keyword options, including keyword options with arguments, are preceded by a double dash --. An = or space character is required between the option and the argument. For example:

```

armlink myfile.o --cpu=list

armlink myfile.o --cpu list

```

# Command-line syntax rules common to all tools

To compile files with names starting with a dash, use the POSIX option -- to specify that all subsequent arguments are treated as filenames, not as command switches. For example, to link a file named -- ifile 1, use:

```

armlink -- -ifile_1

```

In some Unix shells, you might have to include quotes when using arguments to some command-line options, for example:

```

armlink obj1.o --keep='s.o(vect)'

```

# **Chapter 3 Writing Optimized Code**

To make best use of the optimization capabilities of ARM Compiler, there are various options, pragmas, attributes, and coding techniques that you can use.

It contains the following sections:

- 3.1 Optimizing loops on page 3-39.

- 3.2 Inlining functions on page 3-43.

- 3.3 Examining stack usage on page 3-45.

- 3.4 Packing data structures on page 3-47.

# 3.1 Optimizing loops

Loops can take a significant amount of time to complete depending on the number of iterations in the loop. The overhead of checking a condition for each iteration of the loop can degrade the performance of the loop.

# Loop unrolling

You can reduce the impact of this overhead by unrolling some of the iterations, which in turn reduces the number of iterations for checking the condition. Use #pragma unroll (n) to unroll time-critical loops in your source code. However, unrolling loops has the disadvantage of increasing the codes size. These pragmas are only effective at optimization -02, -03, -0fast, and -0max.

Table 3-1 Loop unrolling pragmas

| Pragma                    | Description                             |  |  |

|---------------------------|-----------------------------------------|--|--|

| #pragma unroll (n)        | Unroll <i>n</i> iterations of the loop. |  |  |

| #pragma unroll_completely | Unroll all the iterations of the loop.  |  |  |

The examples below show code with loop unrolling and code without loop unrolling.

Table 3-2 Loop optimizing example

| Bit counting loop without unrolling                                                                                                                             | Bit counting loop with unrolling                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>int countSetBits1(unsigned int n) {    int bits = 0;    while (n != 0)    {       if (n &amp; 1) bits++;       n &gt;&gt;= 1;    }    return bits; }</pre> | <pre>int countSetBits2(unsigned int n) {    int bits = 0;     #pragma unroll (4)    while (n != 0)    {       if (n &amp; 1) bits++;       n &gt;&gt;= 1;    }    return bits; }</pre> |

The code below shows the code that ARM Compiler generates for the above examples. Copy the examples above into file.c and compile using:

```

armclang --target=arm-arm-none-eabi -march=armv8-a file.c -O2 -c -S -o file.s

```

For the function with loop unrolling, countSetBits2, the generated code is faster but larger in size.

Table 3-3 Loop examples

| Bit counting loop without unrolling                                                                                                                                                    | Bit counting loop with unrolling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| countSetBits1:  mov r1, r0 mov r0, #0 cmp r1, #0 bxeq lr mov r2, #0 mov r0, #0  .LBB0_1:  and r3, r1, #1 cmp r2, r1, asr #1 add r0, r0, r3 lsr r3, r1, #1 mov r1, r3 bne .LBB0_1 bx lr | countSetBits2:  mov r0, #0 cmp r1, #0 bxeq lr mov r0, #0 cmp r2, #0 mov r0, #0  LBB0_1:  and r3, r1, #1 cmp r2, r1, asr #1 add r0, r0, r3 beq .LBB0_4  @ BB#2:  asr r3, r1, #1 cmp r2, r1, asr #2 and r3, r3, #1 add r0, r0, r3 asrn r3, r1, #2 andne r3, r3, #1 addne r0, r0, r3 cmpne r2, r1, asr #3 beq .LBB0_4  @ BB#3:  @ BB#3:  asr r3, r1, #3 cmp r2, r1, asr #4 and r3, r3, #1 add r0, r0, r3 asr r3, r1, #3 cmp r2, r1, asr #4 and r3, r3, #1 add r0, r0, r3 asr r3, r1, #4 and r3, r3, #1 add r0, r0, r3 asr r3, r1, #4 and r3, r3, #1 add r0, r0, r3 asr r3, r1, #4 mov r1, r3 bne .LBB0_1  .LBB0_4: bx lr |

ARM Compiler can unroll loops completely only if the number of iterations is known at compile time.

#### Loop vectorization

If your target has the Advanced SIMD unit, then ARM Compiler can use the vectorizing engine to optimize vectorizable sections of the code. At optimization level -01, you can enable vectorization using -fvectorize. At higher optimizations, -fvectorize is enabled by default and you can disable it using -fno-vectorize. See -fvectorize in the armclang Reference Guide for more information. When using -fvectorize with -01, vectorization might be inhibited in the absence of other optimizations which might be present at -02 or higher.

For example, loops that access structures can be vectorized if all parts of the structure are accessed within the same loop rather than in separate loops. The following examples show code with a loop that can be vectorized by Advanced SIMD, and a loop that cannot be vectorized easily.

Table 3-4 Example loops

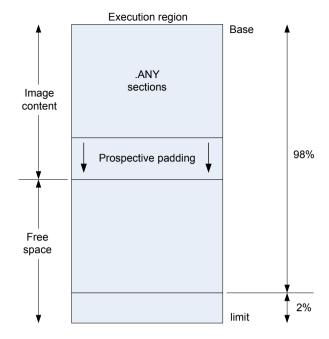

| Vectorizable by Advanced SIMD                                                                                                                                                                                                                  | Not vectorizable by Advanced SIMD                                                                                                                                                                                                                                                                           |