Document number: Date of Issue: Author: DSA09-PRDC-008772 1.0 17 August, 2009 ARM Limited

# ARM<sup>®</sup> Debug Interface v5

Architecture Specification ADIv5.1 Supplement

# **Proprietary notice**

This ARM Architecture Reference Manual is protected by copyright and the practice or implementation of the information herein may be protected by one or more patents or pending applications. No part of this ARM Architecture Reference Manual may be reproduced in any form by any means without the express prior written permission of ARM. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this ARM Architecture Reference Manual.

Your access to the information in this ARM Architecture Reference Manual is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations of the ARM architecture infringe any third party patents.

This ARM Architecture Reference Manual is provided "as is". ARM makes no representations or warranties, either express or implied, included but not limited to, warranties of merchantability, fitness for a particular purpose, or non-infringement, that the content of this ARM Architecture Reference Manual is suitable for any particular purpose or that any practice or implementation of the contents of the ARM Architecture Reference Manual will not infringe any third party patents, copyrights, trade secrets, or other rights.

This ARM Architecture Reference Manual may include technical inaccuracies or typographical errors.

To the extent not prohibited by law, in no event will ARM be liable for any damages, including without limitation any direct loss, lost revenue, lost profits or data, special, indirect, consequential, incidental or punitive damages, however caused and regardless of the theory of liability, arising out of or related to any furnishing, practicing, modifying or any use of this ARM Architecture Reference Manual, even if ARM has been advised of the possibility of such damages.

Words and logos marked with ® or TM are registered trademarks or trademarks of ARM Limited, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

#### Copyright © 2009 ARM Limited

110 Fulbourn Road Cambridge, England CB1 9NJ

Restricted Rights Legend: Use, duplication or disclosure by the United States Government is subject to the restrictions set forth in DFARS 252.227-7013 (c)(1)(ii) and FAR 52.227-19.

This document is Non-Confidential but any disclosure by you is subject to you providing notice to and the acceptance by the recipient of, the conditions set out above.

# Contents

| DSA                         | 09-PRDC-008772 1.0 Copyright © 2007-2009 ARM Limited. All rights reserved. Page 2 of 48 |  |  |  |

|-----------------------------|-----------------------------------------------------------------------------------------|--|--|--|

| 3.2                         | Debug Port architecture versions13                                                      |  |  |  |

| 3.1                         | Introduction13                                                                          |  |  |  |

| 3                           | ADIV5.1 UPDATES13                                                                       |  |  |  |

| 2.17                        | Clarification: Unaligned access to Banked Data registers (DE 643218)12                  |  |  |  |

| 2.16                        | Clarification: ReadResult following IDCODE and ABORT scans (DE 618570)12                |  |  |  |

| 2.15                        | Clarification: AP accesses following a DAP abort (DE 618519)12                          |  |  |  |

| 2.14                        | Clarification: Use of the RESEND register (DE 618517)12                                 |  |  |  |

| 2.13                        | Clarification: Use of PWRUPREQ signals (424966)11                                       |  |  |  |

| 2.12                        | Clarification: UNPREDICTABLE use of transaction counter and transaction mode (414544)10 |  |  |  |

| <b>2.1</b> 1                | Erratum: Incorrect description of JTAG-DP TAP state machine (674167)10                  |  |  |  |

| 2.10                        | Erratum: Use of DP RDBUFF by Serial Wire debug ports (DE 643221)10                      |  |  |  |

| 2.9                         | Erratum: FAULT and WAIT responses to DLCR reads in SW-DP (628066)10                     |  |  |  |

| 2.8                         | Erratum: FAULT response to CTRL/STAT writes in SW-DP (628016)                           |  |  |  |

| 2.7                         | Erratum: Line reset does not have to be detected asynchronously (625117)                |  |  |  |

| 2.6                         | Erratum: Host must drive the Park bit HIGH (618567)9                                    |  |  |  |

| 2.5                         | Erratum: JTAG-DP and SW-DP responses when Sticky Overrun Detect is enabled (604567)     |  |  |  |

| 2.4                         | Erratum: References to asynchronous Serial Wire protocol (513764)                       |  |  |  |

| 2.3                         | Erratum: Emulation of debug reset request (497727) 8                                    |  |  |  |

| 2.2                         | Erratum: ADIv5 gives wrong IDCODE value for SW-DPs (451413)8                            |  |  |  |

| 2.1                         | Introduction                                                                            |  |  |  |

| 2                           | ADIV5.0 ERRATA AND CLARIFICATIONS                                                       |  |  |  |

| 1.3                         | Introduction7                                                                           |  |  |  |

| 1.2 Terms and abbreviations |                                                                                         |  |  |  |

| 1.1 References              |                                                                                         |  |  |  |

| 1                           | ABOUT THIS DOCUMENT                                                                     |  |  |  |

| 3.3 | The identification model for Access Ports13                      |

|-----|------------------------------------------------------------------|

| 3.4 | Multiple Protocol Interoperability14                             |

| 3.5 | Multi-drop Serial Wire protocol extensions14                     |

| 3.6 | Minimal Debug Port (MINDP) extensions15                          |

| 3.7 | Serial Wire protocol programmable turnaround period15            |

| 3.8 | Required support of Memory Access Port (MEM-AP) packed transfers |

| 3.9 | Scope of ADIv5.116                                               |

| 4   | POWER-UP AND RESET CONTROLS16                                    |

| 4.1 | Clarification of PWRUPREQ/ACK signals16                          |

| 4.2 | Limitations of CDBGRSTREQ/CDBGRSTACK18                           |

| 5   | DEBUG PORT ARCHITECTURE VERSIONS19                               |

| 5.1 | The JTAG TAP ID Register, IDCODE19                               |

| 5.2 | DP architecture version 019                                      |

| 5.3 | DP architecture version 121                                      |

| 5.4 | DP architecture version 2                                        |

| 6   | MULTIPLE PROTOCOL INTEROPERABILITY                               |

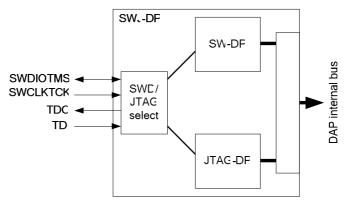

| 6.1 | The Serial Wire/JTAG Debug Port (SWJ-DP)30                       |

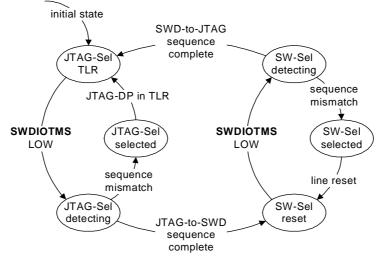

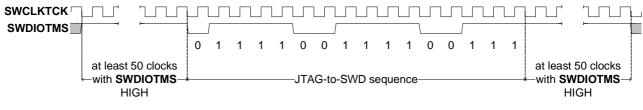

| 6.2 | Serial Wire and JTAG select mechanism31                          |

| 6.3 | Dormant operation                                                |

| 6.4 | Restriction on switching                                         |

| 7   | SERIAL WIRE PROTOCOL VERSION 240                                 |

| 7.1 | Introduction to multi-drop40                                     |

| 7.2 | Limitations of multi-drop40                                      |

| 7.3 | Target selection protocol40                                      |

| 7.4 | Programmer's model41                                             |

| 8   | APPENDIX: SERIAL WIRE PROTOCOL42                                 |

| 8.1  | Introduction                                      | 42 |

|------|---------------------------------------------------|----|

| 8.2  | Clocking                                          | 42 |

| 8.3  | Overview of Serial Wire interface                 | 42 |

| 9    | APPENDIX: STANDARD MEMORY ACCESS PORT DEFINITIONS | -  |

| 9.1  | Introduction                                      |    |

| 9.2  | AMBA AHB                                          | 45 |

| 9.3  |                                                   |    |

| 10   |                                                   |    |

| 10.1 |                                                   |    |

| 10.2 | 2 ARMv6-M                                         | 47 |

| 10.3 | 3 ARMv7-M                                         | 47 |

| 10.4 | 4 ARMv7-A and ARMv7-R                             | 47 |

| 10.5 | 5 Summary                                         | 48 |

# **1 ABOUT THIS DOCUMENT**

## 1.1 References

This document refers to the following documents.

| Doc No              | Author | Title                                                                                                   |

|---------------------|--------|---------------------------------------------------------------------------------------------------------|

| ARM DDI 0211        | ARM    | ARM1136JF-S™ and ARM1136J-S™ Technical Reference Manual*                                                |

| ARM DDI 0314        | ARM    | CoreSight™ Components Technical Reference Manual*                                                       |

| ARM DDI 0406        | ARM    | ARM <sup>®</sup> Architecture Reference Manual ARM <sup>®</sup> v7-A and ARM <sup>®</sup> v7-R edition* |

| <u>ARM IHI 0011</u> | ARM    | AMBA <sup>™</sup> Specification (Rev 2.0) *                                                             |

| ARM IHI 0024        | ARM    | AMBA <sup>™</sup> 3 APB Protocol Specification*                                                         |

| ARM IHI 0031        | ARM    | ARM <sup>®</sup> Debug Interface v5 Architecture Specification*                                         |

| ARM IHI 0033        | ARM    | AMBA <sup>®</sup> 3 AHB-Lite Protocol Specification*                                                    |

| IEEE 1149.1-2001    | IEEE   | IEEE Standard Test Access Port and Boundary Scan Architecture                                           |

|                     |        |                                                                                                         |

\* These documents can be accessed through the ARM website at <a href="http://infocenter.arm.com/">http://infocenter.arm.com/</a>. For further information, contact ARM Limited.

# 1.2 Terms and abbreviations

This document uses the following terms and abbreviations.

#### Data Link

The layer of an ADIv5 implementation that provides the functional and procedural means to transfer data between the external debugger and the Debug Port. ADIv5 defines two Data Link layers, one based on the IEEE 1149.1 Standard Test Access Port and Boundary Scan Architecture, widely referred to as JTAG, and one based on the ARM Serial Wire protocol interface.

#### DATA LINK DEFINED

Means that the behavior is not defined by the base architecture, but should be defined and documented by individual Data Link layers of the architecture.

#### IMPLEMENTATION DEFINED

Means that the behavior is not architecturally defined, but should be defined and documented by individual implementations.

#### **RAZ/WI** fields

Read-As-Zero, Writes Ignored.

In any implementation, the bit must read as 0 (or all 0s for a bit field), and writes to the field must be ignored. Software can rely on the field reading as zero, and on the write being ignored.

#### Read-As-One fields (RAO)

In any implementation, the bit must read as 1, or all 1s for a bit field.

#### Read-As-Zero fields (RAZ)

In any implementation, the bit must read as 0, or all 0s for a bit field.

#### Should-Be-One fields (SBO)

Software should write as 1, or all 1s for a bit field. Values other than 1 produce UNPREDICTABLE results.

#### Should-Be-Zero fields (SBZ)

Software should write as 0, or all 0s for a bit field. Values other than 0 produce UNPREDICTABLE results.

### Should-Be-Zero-or-Preserved fields (SBZP)

Must be written as 0, or all 0s for a bit field, by software if the value is being written without having been previously read, or if the register has not been initialized. Where the register was previously read on the same processor, since the processor was last reset, the value in the field should be preserved by writing the value that was previously read.

Hardware must ignore writes to these fields.

If a value is written to the field that is neither 0 (or all 0s for a bit field), nor a value previously read for the same field on the same processor, the result is UNPREDICTABLE.

#### UNK

Is an abbreviation indicating that software must treat a field as containing an UNKNOWN value.

In any implementation, the bit must read as 0, or all 0s for a bit field. Software must not rely on the field reading as zero.

#### **UNK/SBZP**

UNKNOWN on reads, Should-Be-Zero-or-Preserved on writes.

In any implementation, the bit must read as zero, or all 0s for a bit field, and writes to the field must be ignored. Software must not rely on the bit reading as zero, or all 0s for a bit field, and must use an SBZP policy to write to the field.

#### UNKNOWN

An UNKNOWN value does not contain valid data, and can vary from moment to moment, and implementation to implementation. An UNKNOWN value must not be a security hole.

UNKNOWN values must not be documented or promoted as having a defined value or effect.

#### UNPREDICTABLE

Means the behavior cannot be relied upon. UNPREDICTABLE behavior must not represent security holes.

UNPREDICTABLE behavior must not halt or hang the device, or any parts of the system. UNPREDICTABLE behopavior must not be documented or promoted as having a defined effect.

#### Note

In the ARM® Debug Interface v5 Architecture Specification, UNPREDICTABLE was also used to mean an UNKNOWN value.

#### Write-One-To-Clear bits (W1C)

Writing a 1 to the bit clears it to zero. Writing a 0 to the bit has no effect.

## **1.3 Introduction**

This document is an update to the ARM® Debug Interface v5 Architecture Specification. It includes errata and new features for ADIv5.

Those new features represent a minor revision of the architecture specification, and hence the architecture version number is v5.1. The new features are backwards compatible with v5.0; the version documented by the *ARM® Debug Interface v5 Architecture Specification*. The terms *ARM Debug Interface v5* and *ADIv5* refer to the major revision of ADI, that is, to v5.0, v5.1 or any future minor revision of ADIv5.

Section 2, ADIv5.0 Errata and Clarifications, starting on page 8, describes each of the errata and clarifications in turn.

Section 3, ADIv5.1 Updates, starting on page 13, describes each of the new features in turn.

Sections 4, 5, 6, and 7 give more detailed information for some of the errata, clarifications and updates.

The final sections are new appendices to the *ARM® Debug Interface v5 Architecture Specification*. The information provided is not architectural and hence not part of ADIv5, but is nevertheless useful reference material for implementations and users of ADIv5.

Section 8, *Appendix: Serial Wire Protocol* starting on page 42 provides more background information on the Serial Wire protocol that is required for compatibility with Serial Wire protocol implementations. The Serial Wire protocol was previously described in the *CoreSight<sup>™</sup> Components Technical Reference Manual*.

Section 9, *Appendix: Standard Memory Access Port Definitions* starting on page 45 provides reference material for standard implementations of Memory Access Ports.

Section 10, *Appendix: Cross-over with the ARM® Architecture* starting on page 47 provides detail of how the ADIv5 specification should be used when selecting or implementing Debug Access Ports for each of a variety of ARM<sup>®</sup> architecture variants.

# 2 ADIV5.0 ERRATA AND CLARIFICATIONS

# 2.1 Introduction

This section corrects errata in the ARM® Debug Interface v5 Architecture Specification, and also provides some clarifications where the ARM® Debug Interface v5 Architecture Specification might be ambiguous.

Please use the six-digit reference number provided in each section in any related correspondence with ARM Limited.

# 2.2 Erratum: ADIv5 gives wrong IDCODE value for SW-DPs (451413)

The ARM® Debug Interface v5 Architecture Specification gives the required value for the Part Number field, PARTNO: IDCODE[27:12], for an ARM implementation of a Serial Wire Debug Port (SW-DP) as 0xBA10. The correct value for current ARM implementations of Serial Wire protocol version 1 is 0xBA01.

In this manual, the SW-DP IDCODE register is renamed DPIDR. See *Debug Port architecture versions* on page 13. Also see *Serial Wire Protocol Version 2* on page 40.

# 2.3 Erratum: Emulation of debug reset request (497727)

Table 6-7 of the *ARM®* Debug Interface v5 Architecture Specification directs the reader to section 3.4.4 for details of how to emulate implementation of CDBGRSTACK and CDBGRSTREQ. Section 3.4.4 does not have that information.

The correct behavior is that if the debug reset control is not supported then:

- CDBGRSTACK is RAZ

- it is IMPLEMENTATION DEFINED whether CDBGRSTREQ is read/write or RAZ.

That is, in a standard implementation, CDBGRSTACK can be tied LOW. Whether, in such a system, CDBGRSTREQ registers values written to it is IMPLEMENTATION DEFINED.

See also *Limitations of CDBGRSTREQ/CDBGRSTACK* on page 18.

# 2.4 Erratum: References to asynchronous Serial Wire protocol (513764)

Several sections of the *ARM®* Debug Interface v5 Architecture Specification, including sections 2.2.2, 5.1, 5.2, 5.3, 5.4.6 and 6.2.6, refer to support for an asynchronous mode of operation for the CoreSight Serial Wire interface.

The Serial Wire interface does not support an asynchronous mode of operation.

Bits [7:6] of the Data Link Control Register (DLCR, formerly the Wire Control Register or WCR) are reserved, read as 0b01 and ignore writes. Bits [2:0] of the DLCR are reserved, RAZ/WI.

# 2.5 Erratum: JTAG-DP and SW-DP responses when Sticky Overrun Detect is enabled (604567)

Section 3.1.2 of the *ARM®* Debug Interface v5 Architecture Specification states that when Sticky Overrun Detect is enabled in the Debug Port CTRL/STAT register, the only permitted responses to transactions are OK/FAULT on the JTAG-DP and OK on the SW-DP.

These responses should be described not as "permitted responses", as this implies is that they are the only responses generated in this state. However, the section goes on to correctly describe that when other responses are generated, the STICKYORUN flag is set. That is, all responses can be generated in overrun detection mode.

That is, in overrun detection mode, the Sticky Overrun flag STICKYORUN in the Debug Port (DP) Control/Status register is set to 1 if the response to any transaction is other than:

- OK/FAULT on the JTAG-DP

- OK on the SW-DP.

As the JTAG-DP and SW-DP protocols differ, the exact behavior is DATA LINK DEFINED:

#### For JTAG-DP:

The response is WAIT so long as the previous Access Port (AP) transaction remains not completed, and OK/FAULT thereafter. This is correctly described in the section *Sticky overrun behavior on DPACC and APACC accesses* in section 4.4.3 of the *ARM® Debug Interface v5 Architecture Specification*.

#### For SW-DP:

The first response to a transaction when a previous AP transaction has not completed is WAIT. Following responses will be FAULT, since the STICKYORUN bit is set to 1. This is correctly described in the section 5.4.5 of the *ARM® Debug Interface v5 Architecture Specification*.

Furthermore, when Sticky Overrun Detect is enabled, the STICKYORUN bit is also set to 1:

- when the DP issues a FAULT response

- following a protocol error.

# 2.6 Erratum: Host must drive the Park bit HIGH (618567)

Section 5.3.1 of the *ARM®* Debug Interface v5 Architecture Specification states that the host does not drive the line for the Park bit of Serial Wire protocol, instead relying on the line being pulled HIGH by the Serial Wire interface.

The host must in fact actively drive the line HIGH to park it before tri-stating the line for the turnaround period. This ensures the line is HIGH and is read as HIGH by the target. This is required as the pull-up on the Serial Wire interface is weak.

Section 5.4.6 of the *ARM® Debug Interface v5 Architecture Specification* further implies that a protocol error only occurs on incorrect parity in a command header. The target will in fact signal protocol error if any of the Parity, Stop or Park bits is not driven with the correct value.

# 2.7 Erratum: Line reset does not have to be detected asynchronously (625117)

Section 5.4.1 of the *ARM®* Debug Interface v5 Architecture Specification states that the serial protocol requires that any run of 50 consecutive 1s on the data input is detected as a line reset, regardless of the state of the protocol.

This is incorrect. The target may not detect a line reset if it is not in the correct state. It must detect a sequence of 50 consecutive 1s as a line reset if it receives the sequence when it is expecting the initial Start bit of a packet header.

However, regardless of what state the target is in, it will at least detect the sequence as a protocol error, as it will interpret at least one bit of the sequence as an invalid Stop bit in a packet header.

Having detected a protocol error, the target may respond to the DP DPIDR register read that follows the line reset sequence. However, if the target does not respond, the debugger must retry the line reset sequence.

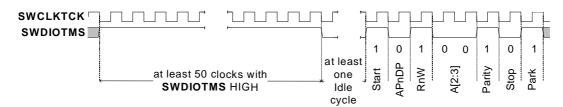

For more information, see *Line reset* on page 43.

# 2.8 Erratum: FAULT response to CTRL/STAT writes in SW-DP (628016)

Table 5-3 of the ARM® Debug Interface v5 Architecture Specification correctly shows that SW-DP must issue a FAULT response to a *write* to the CTRL/STAT register if any sticky flag is set.

However, section 5.4.4 of the ARM® Debug Interface v5 Architecture Specification states that a SW-DP must not issue a FAULT response to an access to the IDCODE, CTRL/STAT or ABORT registers. The implication that this includes writes to CTRL/STAT is incorrect. An SW-DP must only not issue a FAULT response for:

- reads of the IDCODE register (the IDCODE register is read-only)

- writes to the ABORT register (the ABORT register is write-only)

- reads of CTRL/STAT.

# 2.9 Erratum: FAULT and WAIT responses to DLCR reads in SW-DP (628066)

Sections 5.4.3 and 5.4.4 of the ARM® Debug Interface v5 Architecture Specification list the SW-DP register accesses that must never return WAIT or FAULT responses.

However, Table 5-1 implies that reads of DLCR (formerly known as the WCR) will also return a result immediately and never respond with FAULT. This is incorrect. Reads of DLCR return a FAULT response if a sticky error flag is set.

Whether reads of a DLCR return a WAIT response if the AP is not ready is IMPLEMENTATION DEFINED. From Debug Port (DP) architecture version 2, reads of DLCR return a WAIT response if the AP is not ready.

# 2.10 Erratum: Use of DP RDBUFF by Serial Wire debug ports (DE 643221)

Sections 5.4.2 and 6.2.5 of the *ARM®* Debug Interface v5 Architecture Specification states that, for SW-DP, to obtain the result of an AP register read the next access must be either a second AP register read or a read of the DP Read Buffer (RDBUFF) register.

This is incorrect. To allow the debugger to recover from line errors, the next transaction after an AP register read can be any DP register read. If the next transaction is a DP register read other than a read of RDBUFF then a following AP register read or read of RDBUFF will return the result of the first AP register read.

However, if the next transaction following an AP register read is an AP register write or a DP register write then the result of the first AP register read is effectively lost, as any following AP register read or read of RDBUFF will return an UNKNOWN value.

# 2.11 Erratum: Incorrect description of JTAG-DP TAP state machine (674167)

Section 4.2.3 of the *ARM® Debug Interface v5 Architecture Specification* states that for the transition from the Capture-IR state to the Shift-IR state, the instruction register scan chain advances one bit.

The IEEE 1149.1 JTAG specification, upon which the JTAG-DP is closely based, requires that the scan chain advances for each rising edge of **TCK** whilst in the Shift state. That is, the scan chain does not advance for the transition from Capture-IR to Shift-IR. The same is true for data register scan chains on transitions from Capture-DR to Shift-DR.

For more information, see the IEEE Standard Test Access Port and Boundary Scan Architecture.

# **2.12 Clarification: UNPREDICTABLE use of transaction counter and transaction mode (414544)**

An Access Port (AP) is permitted to define that accesses to certain registers in the AP are UNPREDICTABLE when the Debug Port's (DP) Transaction Counter field, TRNCNT, CTRL/STAT[23:12] field is non-zero.

An AP is also permitted to define that the Sticky Compare flag, STICKYCMP, CTRL/STAT[4] is set to an UNKNOWN value in response to an access made to certain registers in the AP when the Transfer Mode field, TRNMODE, CTRL/STAT[3:2] is any value other than 0b00 (*Normal operation*), regardless of the value in the register.

In general, both UNPREDICTABLE behaviors are expected to be defined for any register that does not change its value other than in response to an APACC or DPACC access.

Table 1 lists the register accesses defined by the ARM Debug Interface v5 to:

- be UNPREDICTABLE when the TRNCNT field is not zero

- set the STICKYCMP flag to an UNKNOWN value when the TRNMODE field is not zero.

| Access Port type                 | Register being accessed         |

|----------------------------------|---------------------------------|

| Any Identification Register (IDR |                                 |

|                                  | Any reserved register location  |

| Memory Access Port (MEM-AP)      | Control/Status Word (CSW)       |

|                                  | Transfer Address Register (TAR) |

|                                  | ROM Table Base Register (BASE)  |

|                                  | Configuration Register (CFG)    |

| JTAG Access Port (JTAG-AP)       | Control/Status Word (CSW)       |

|                                  | Port Select Register (PSEL)     |

#### Table 1: UNPREDICTABLE register accesses

If the DP SELECT register selects a non-existent AP, then register accesses:

- are UNPREDICTABLE when the TRNCNT field is not zero

- set the STICKYCMP flag to an UNKNOWN value when the TRNMODE field is not zero.

See also Minimal Debug Port (MINDP) extensions on page 15.

# 2.13 Clarification: Use of PWRUPREQ signals (424966)

CSYSPWRUPREQ and CDBGPWRUPREQ, bits [30,28] of the Debug Port CTRL/STAT register, can independently request power up of debug functions in the debug and system power domains.

The system power domain *includes* the debug power domain. CDBGPWRUPREQ must be set to 1 whenever CSYSPWRUPREQ is set to 1. Setting bits [30,28] to 0b10 gives UNPREDICTABLE system behavior.

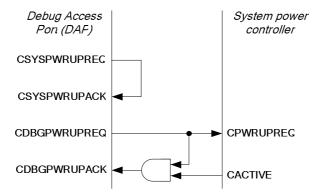

Given this, the example circuit shown in Figure 3-5 of the *ARM®* Debug Interface v5 Architecture Specification can be replaced with the simpler circuit shown in Figure 1.

Figure 1: Signal generation for single power domain

This manual also:

- gives clarification of the roles of these power-up request bits

- describes some limitations of these power-up request bits.

For more details, see *Power-up and Reset Controls* on page 16, which clarifies the descriptions of the power-up request/acknowledge signals, and replaces parts of the descriptions in section 3.4 of the *ARM® Debug Interface v5 Architecture Specification*.

# 2.14 Clarification: Use of the RESEND register (DE 618517)

ARM recommends that debuggers only access the SW-DP RESEND register when a failed read has been indicated by the SW-DP, and not at other times. This is because an implementation is permitted to treat reads of RESEND as a protocol error in the case where it cannot resend the information.

# 2.15 Clarification: AP accesses following a DAP abort (DE 618519)

Section 6.2.1 of the *ARM® Debug Interface v5 Architecture Specification* describes the behavior following a DAP abort. The section states that, following a DAP abort:

- new transactions can be accepted by the DP

- an AP access to the AP that was aborted might return additional WAIT responses

- other APs can be accessed.

This is ambiguous, since the WAIT response is generated by the DP and is the DP's mechanism to not accept a new transaction. Section 6.2.1 should state that, following a DAP abort:

- An AP access to the AP that was aborted might not be accepted by the DP, with the DP returning a WAIT response.

- A DP access or an AP access to any other AP will be accepted by the DP. This includes AP accesses to non-existent APs, which are defined to behave as RAZ/WI.

# 2.16 Clarification: ReadResult following IDCODE and ABORT scans (DE 618570)

On entering the Capture-DR state with the JTAG-DP instruction register (IR) set to the APACC or DPACC instructions, the value captured for ReadResult is always UNKNOWN if either:

- the most recent DR scan was not made with IR set to one of the DPACC, APACC or BYPASS instructions

- there has been no DR scan since leaving the Test-Logic-Reset state.

# 2.17 Clarification: Unaligned access to Banked Data registers (DE 643218)

Section 8.1.3 of the *ARM®* Debug Interface v5 Architecture Specification requires that accesses to a MEM-AP's BD0 to BD3 access addresses starting at the address TAR[31:4].

The description in section 8.1.3 should further state that the value in TAR[3:0] is ignored in constructing the access address for a banked register transfer, and:

- bits [3:2] of the access address depend solely on which of the four banked data registers is being accessed.

- bits [1:0] of the access address will always be zero.

# 3 ADIV5.1 UPDATES

# 3.1 Introduction

This section describes the main changes in ADIv5 between version 5.0 and version 5.1.

# 3.2 Debug Port architecture versions

The *ARM®* Debug Interface v5 Architecture Specification describes two variants of the Debug Port (DP) linked to two implementations, SW-DP and JTAG-DP. This manual formalizes those differences by introducing the concept of a DP architecture version.

The definition of the DP identification registers is updated to allow for this change, and also to accommodate future additions to the DP programmer's model.

The ARM® Debug Interface v5 Architecture Specification describes a Debug Port register named IDCODE. For SW-DP, this register is accessed as DP register 0; for JTAG-DP it is accessed via the JTAG IDCODE instruction. The JTAG IDCODE is part of the IEEE 1149.1 Test Access Port specification, and therefore lies outside the scope of the ADIv5 specification. This manual separates the two concepts.

The versions of the DP architecture described in the *ARM® Debug Interface v5 Architecture Specification* are DP architecture version 0 for JTAG-DP and DP architecture version 1 for SW-DP. ADIv5.1 defines an additional DP architecture version 2.

For full details, see Debug Port Architecture Versions on page 19.

# 3.3 The identification model for Access Ports

The ARM® Debug Interface v5 Architecture Specification defines a single, common identification register that must be implemented by all Access Ports, IDR. In version 5.0, bit [16] of this register is defined as the Access Port Class field and bits [15:8] as reserved, UNK. Version 5.1 redefines the bits in IDR, as shown in Figure 2.

| 31 30 29 28 | 27 26 25 24                     | 23 22 21 20 19 18 17  | 16 15 14 13 12 11 10 9 8 | 7 6 5 4 3 2 1 0   |

|-------------|---------------------------------|-----------------------|--------------------------|-------------------|

| Revision    | JEP-106<br>continuation<br>code | JEP-106 identity code | Class                    | AP identification |

|             | 0 1 0 0                         | 0 1 1 1 0 1 1         |                          |                   |

## Figure 2: Access Port ID Register bit assignments

## Revision, JEP-106 continuation code, and JEP-106 identity code, bits [31:17]

Unchanged. The codes for ARM Limited are shown. See the ARM® Debug Interface v5 Architecture Specification.

## Class, bits [16:13]

This field defines the class of Access Port. An Access Port belongs to a class if it follows a programmer's model defined as part of the ADIv5 specification or extensions to it.

Table 2 lists the Access Port classes defined by the ADIv5 specification. All other values are reserved.

| Class  | Description                                                               |  |

|--------|---------------------------------------------------------------------------|--|

| 0b0000 | No defined class                                                          |  |

| 0b1000 | 000 Memory Access Port.                                                   |  |

|        | See Chapter 11 of the ARM® Debug Interface v5 Architecture Specification. |  |

#### Table 2: Class field values

#### Bits [12:8]

Reserved, must-be-zero. This field is reserved for future ID register fields. If a debugger reads a non-zero value in this field, it must treat the AP as unidentifiable.

#### AP identification, bits [7:0]

Access Port Identification. This field identifies the AP implementation. Each AP designer must maintain their own list of implementations and associated Identification codes.

In an AP implementation by ARM Limited this field is sub-divided as bits [7:4] *Variant*, bits [3:0] *Type*. Table 3 lists the possible values of the Type field for an AP designed by ARM Limited. The Variant field is used to identify different implementations of the same Type.

| Class  | Туре | Bus type                                                                |

|--------|------|-------------------------------------------------------------------------|

| 0b0000 | 0x0  | Not used by MEM-APs; indicates JTAG-AP. Variant field must be non-zero. |

| 0b1000 | 0x1  | AMBA AHB bus                                                            |

| 0b1000 | 0x2  | AMBA APB bus                                                            |

| -      | -    | All other values are reserved.                                          |

|        |      |                                                                         |

#### Table 3: Interpretation of IDR[3:0] for ARM designed MEM-APs

#### Note

The ARM® Debug Interface v5 Architecture Specification required this designation of Variant and Type for all ARM designed APs. In ADIv5.1, this interpretation of the AP Identification field is restricted.

ARM Limited will only assign IDR[3:0] values 0x0, 0x1 and 0x2 in a manner backwards compatible with ADIv5. However, for all other IDR[3:0] values, the Type interpretation only applies for MEM-APs.

The AP Identification field must be unique for each Access Port designed by a given designer, regardless of the value of IDR.Class.

# 3.4 Multiple Protocol Interoperability

The Serial Wire/JTAG Debug Port (SWJ-DP) allows for multiple protocol interoperability. An implementation of SWJ-DP is described in the *CoreSight™ Components Technical Reference Manual*. This manual incorporates those existing implementations within ADIv5.

A further extension, Dormant state, is introduced to increase interoperability with other protocol standards.

For full details, see *Multiple Protocol Interoperability* on page 30.

## 3.5 Multi-drop Serial Wire protocol extensions

Serial Wire protocol version 1 is a point-to-point architecture, supporting connection between a single host and a single device. It allows connection to multiple devices only by providing additional connections from the host.

This has a number of disadvantages:

- It complicates the physical connection standard, by having variants with different numbers of connections.

- It increases the number of pins required for the connector on the device PCB. This is unacceptable where size is a limiting factor.

- It increases the number of pins required on a package with multiple dies inside.

- It makes it difficult to integrate multiple platforms accessed by the Serial Wire protocol into the same chip.

Techniques to solve this require connections that are shared between multiple Serial Wire devices. This is detrimental to the maximum speed of operation, but in many situations this is an acceptable trade-off.

Serial Wire protocol version 2 adds the multi-drop extension, which:

- enables a two wire host connection to communicate simultaneously with multiple devices

- permits an effectively unlimited number of devices to be connected simultaneously, subject to electrical constraints

- is backwards-compatible: provision of multi-drop support in a device does not break point-to-point compatibility with existing host equipment that does not support multi-drop extensions

- permits a device to power down completely while that device is not selected

- prevents multiple devices from driving the wire simultaneously, and continues to support the wire being actively driven both HIGH and LOW, maintaining a high maximum clock speed

- also allows for multi-drop connections incorporating devices that do not implement the Serial Wire protocol.

Serial Wire protocol version 2 is described in Serial Wire Protocol Version 2 starting on page 40.

# 3.6 Minimal Debug Port (MINDP) extensions

The Minimal Debug Port programmer's model is a cut-down version of the Debug Port intended for low-gate-count implementations.

For minimal DP implementations, the following Debug Port features are removed:

- the Transaction Counter

- Pushed Verify operation

- Pushed Find operation.

When MINDP is implemented:

- DPIDR.MIN, bit [16] of Debug Port ID Register, DPIDR, is RAO.

- The following fields, bits [23:8] and [4:3], of the Control/Status Register, CTRL/STAT, are reserved, RAZ:

CTRL/STAT.TRNCNT

- CTRL/STAT.MASKLANE

- CTRL/STAT.MASKLANE

CTRL/STAT.STICKYCMP

- CTRL/STAT.TRNMODE

Writing a non-zero value to any of these fields is UNPREDICTABLE.

• ABORT.STKCMPCLR, bit [1] of the Abort Register, ABORT, is reserved, SBZ. Writing 1 to this bit is UNPREDICTABLE.

# 3.7 Serial Wire protocol programmable turnaround period

Section 6.2.6 of the *ARM® Debug Interface v5 Architecture Specification* describes how the turnaround tri-state period for the Serial Wire protocol can be programmed using the WCR.TURNROUND register.

In ADIv5.1 support for varying the turnaround tri-state period is IMPLEMENTATION DEFINED. An implementation that does not support variable turnaround must treat writing a value other than 0b00 to WCR.TURNROUND as an immediate protocol error.

ARM deprecates use of turnaround tri-state periods other than 1.

# 3.8 Required support of Memory Access Port (MEM-AP) packed transfers

Section 8.2.7 of the ARM® Debug Interface v5 Architecture Specification requires that if a MEM-AP supports access sizes smaller than word it must also support packed transfers.

In ADIv5.1 that requirement is relaxed. Support for packed transfers is IMPLEMENTATION DEFINED.

From ADIv5.1, if a MEM-AP does not support packed transfers then writing 0b10 to CSW.AddrInc selects the *auto-increment off* mode. Subsequently reading back CSW will return 0b00 for CSW.AddrInc.

This was not required by the definition of CSW.AddrInc in the ARM® Debug Interface v5 Architecture Specification.

# 3.9 Scope of ADIv5.1

ADIv5 encompasses a range of technologies and architectures. ADIv5 version 5.0 and version 5.1 are packages of versions of these technologies and architectures. Version 5.1 encompasses all that is defined in version 5.0: an implementation of ADIv5.0 is also an implementation of ADIv5.1.

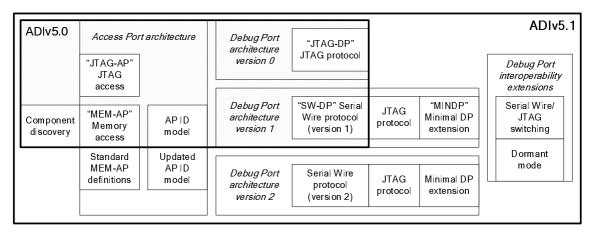

Figure 3 shows the main components of ADIv5, split between the two main areas of ADIv5: the Access Port architecture and the Debug Port architecture. For each component, Figure 3 shows whether the component was defined in ADIv5.0 or is introduced with ADIv5.1. ADIv5.1 adds a third major area of ADIv5: Debug Port interoperability.

For example, Debug Port architecture version 1 is defined by ADIv5.0 but in that version only supports Serial Wire protocol (version 1), and is called SW-DP. In ADIv5.1 it is formalized as *Debug Port architecture version 1*, and also allows JTAG protocol.

Figure 3: Scope of ADIv5.0 and ADIv5.1 and the architecture components defined by each

# 4 POWER-UP AND RESET CONTROLS

# 4.1 Clarification of PWRUPREQ/ACK signals

The ARM® Debug Interface v5 Architecture Specification defines two pairs of signals:

- CDBGPWRUPREQ and CDBGPWRUPACK

- CSYSPWRUPREQ and CSYSPWRUPACK

Table 4 summarizes the programmer's model for CDBGPWRUPREQ/ACK and CSYSPWRUPREQ/ACK.

| Signal       | Programmer's model                |

|--------------|-----------------------------------|

| CDBGPWRUPREQ | Bit[28] of the CTRL/STAT register |

| CDBGPWRUPACK | Bit[29] of the CTRL/STAT register |

| CSYSPWRUPREQ | Bit[30] of the CTRL/STAT register |

| CSYSPWRUPACK | Bit[31] of the CTRL/STAT register |

#### Table 4: Debug Port programmer's model

These signals are expected to provide hints to the system power/clock controller. The following sections describe these signal pairs in turn.

## 4.1.1 CDBGPWRUPREQ and CDBGPWRUPACK

The **CDBGPWRUPREQ** signal indicates that the debugger requires the debug resources to be *communicative*. The power/clock controller must power-up and run the clocks of as many domains as necessary to comply with this request.

*Communicative* means that the debugger can access at least enough registers of the debug resource for it to determine the state of the resource. Whether the resource is *active* is IMPLEMENTATION DEFINED.

The power/clock controller must honor **CDBGPWRUPREQ** for as long as it is asserted. For example, if a component in a debug power domain requests to have its clocks stopped, the request must be emulated. This includes all components with a single shared debug / core power domain: power-down must be emulated for non-debug logic within that power domain.

Components with a split debug / core power domains must have *at least* the minimal debug interface powered up. Even if some debug resources are contained in the core power domain, then power can be removed from the core power domain so long as both:

- there is some means to save and restore the state of these resources over the core power domain being powered down

- the core power domain does not need to be powered for the debugger to be able to communicate with the debug resources.

The means to save and restore these resources might include software means. If the debug resources do lose their value when power is removed from the core power domain, then the debug logic must include means for the debugger to discover that the programmed values have been lost.

**CDBGPWRUPACK** is the acknowledge signal for the **CDBGPWRUPREQ** request signal. **CDBGPWRUPACK** must be asserted for as long as **CDBGPWRUPREQ** is asserted.

## 4.1.2 CSYSPWRUPREQ and CSYSPWRUPACK

The **CSYSPWRUPREQ** signal indicates that the debugger requires all debug resources to be *active*. The power/clock controller must power-up and run the clocks of as many domains as necessary so that all debug resources are active.

Active means that the debug resource is capable of performing its debug function. An active resource is also communicative.

The power/clock controller must honor **CSYSPWRUPREQ** for as long as it is asserted.

**CSYSPWRUPREQ** will have no effect on debug components with a single power-domain, as **CDBGPWRUPREQ** will ensure those components are powered. Similarly, it has no effect on components with a pure debug / core power-domain split, as those components have no debug logic in the core power domain. However, for components where some debug resources are in the core power domain, **CSYSPWRUPREQ** must be seen as a request to emulate power saving in the core power domain.

**CSYSPWRUPACK** is the acknowledge signal for the **CSYSPWRUPREQ** request signal. **CSYSPWRUPACK** must be asserted for as long as **CSYSPWRUPREQ** is asserted. Whenever **CSYSPWRUPREQ** is asserted by the debugger, **CDBGPWRUPREQ** must also be asserted.

# 4.2 Limitations of CDBGRSTREQ/CDBGRSTACK

The DP provides two bits, CDBGRSTREQ and CDBGRSTACK, bits [27:26] of the CTRL/STAT register, for reset control of the debug domain.

The ARM® Debug Interface v5 Architecture Specification shows how these bits can be used to drive the debug reset signal, **PRESETDBGn**. In a real system there are likely to be other reset signals associated with other debug buses. For example in an ARM CoreSight system, **ATRESETn** resets all register in the AMBA Trace Bus domain.

Because debug logic might be accessible by the system, an implementation might have corner cases if CDBGRSTACK is set whilst the system is using the debug logic. For example, the reset might reset a debug bus whilst a transaction is in progress, causing a system or software malfunction.

ARM recommends that such approaches are not mixed without extreme care; that such system-level usage of debug components is not combined with a reset system that allows those components to be reset without the knowledge of the system.

For more details on this issue, contact ARM.

If the debug reset control is not implemented, CDBGRSTACK is RAZ and CDBGRSTREQ might be RAZ. See *Erratum: Emulation of debug reset request (497727)* on page 8.

# 5 DEBUG PORT ARCHITECTURE VERSIONS

The ARM® Debug Interface v5 Architecture Specification describes two forms of Debug Port (DP): the JTAG Debug Port and the Serial Wire Debug Port. This manual reclassifies these as different versions of a common DP architecture. Table 5 lists the versions of the Debug Port (DP) architecture described by ADIv5.1.

#### Version number Description

| 0 | DP architecture version 0 on page 19 |

|---|--------------------------------------|

| 1 | DP architecture version 1 on page 21 |

| 2 | DP architecture version 2 on page 26 |

#### **Table 5: Debug Port architecture versions**

JTAG-DP always implements a JTAG TAP ID Register, which is not related to the Debug Port architecture version.

# 5.1 The JTAG TAP ID Register, IDCODE

The JTAG TAP ID Register, IDCODE, is always present on all JTAG-DP implementations. It provides identification information about the JTAG-DP, such as which scan-chains are implemented.

It is accessed using its own scan chain. See the ARM® Debug Interface v5 Architecture Specification.

It is read-only and always accessible. Figure 4 shows the register bit assignment, with their values for an ARM design.

| 31 30 29 28 | 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 | 11 10 9 8 7 6 5 4 3 2 1 0 |  |

|-------------|-------------------------------------------------|---------------------------|--|

| Version     | PARTNO                                          | DESIGNER 1                |  |

|             |                                                 | 0 1 0 0 0 1 1 1 0 1 1     |  |

#### Figure 4: JTAG TAP ID Register bit assignments

#### Version, bits [31:28]

Version code. The meaning of this field is IMPLEMENTATION DEFINED.

#### PARTNO, bits [27:12]

Part Number for the DP TAP. This value is provided by the designer of the Debug Port TAP and must not be changed. Current DPs designed by ARM have the JTAG-DP PARTNO value 0xBA00.

#### DESIGNER, bits [11:1]

Designer ID. An 11-bit code formed from the JEDEC JEP-106 continuation code and identity code. The ID identifies the designer of the JTAG-DP TAP. The ARM value for this field, shown above, is 0x23B. Other designers must insert their own JEDEC assigned code here.

Bit [0] RAO.

# 5.2 DP architecture version 0

Architecture version 0 only supports JTAG-DPs. Whether a JTAG-DP implements version 0 of the architecture or some other version can be determined by a table lookup based on the JTAG IDCODE value.

In DP architecture version 0:

- the SELECT register is read/write

- bits [5:4] of the CTRL/STAT register are R/W1C

• bits [31:1] of the ABORT register are reserved, SBZ and bit [0] SBO on writes.

#### Note

Debug Port architecture version 0 is the DP architecture defined for JTAG-DP in the *ARM® Debug Interface v5 Architecture Specification*.

The DP register map in version 0 of the DP architecture is shown in Table 6.

| Address | Access        | Description                                                                |

|---------|---------------|----------------------------------------------------------------------------|

| 0x0     | UNPREDICTABLE | Reserved                                                                   |

| 0x4     | Read/write    | The Control/Status Register, CTRL/STAT (architecture version 0) on page 20 |

| 0x8     | Read/write    | The AP Select Register, SELECT (architecture version 0) on page 21         |

| 0xC     | Read-only     | The Read Buffer, RDBUFF                                                    |

|         |               |                                                                            |

#### Table 6: Debug Port register map, architecture version 0

The DP must implement an ABORT register. In DP architecture version 0, how this register is accessed is DATA LINK DEFINED. In JTAG-DP this is implemented through the ABORT instruction.

## 5.2.1 The Control/Status Register, CTRL/STAT (architecture version 0)

In DP architecture version 0, the Control/Status Register, CTRL/STAT, is:

- a read/write register

- accessed by a read or write of DP register 0x4.

Figure 5 shows the register bit assignments.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24  | 23  | 22   | 21 | 20 | 19 | 9 18 | 17  | 16 | 6 15 | 5 14 | 13 | 12 | 2 11 | 10   | 9   | 8   | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|----|-----|-----|------|----|----|----|------|-----|----|------|------|----|----|------|------|-----|-----|----------|---|---|---|---|---|---|---|

|    |    |    |    |    |    |    |     |     |      |    |    |    | TRN  | CNT | -  |      |      |    |    | 1    | MASł | LAN | IE  |          |   |   |   |   |   |   |   |

|    |    |    |    |    |    | CD | BGR | STR | EQ   |    |    |    |      |     |    |      |      |    |    |      | WD   | ATA | ERR |          |   |   |   |   |   |   |   |

|    |    |    |    |    |    | CD | BGR | STA | СК   |    |    |    |      |     |    |      |      |    |    |      |      | REA | DOK | [        |   |   |   |   |   |   |   |

|    |    |    |    |    |    | CD | BGP | WR  | JPR  | EQ |    |    |      |     |    |      |      |    |    |      | STI  | СКҮ | ERR | <u> </u> |   |   |   |   |   |   |   |

|    |    |    |    |    |    | CD | BGP | WR  | JPA  | СК |    |    |      |     |    |      |      |    |    |      | STI  | CKY | CMF |          |   |   |   |   |   |   |   |

|    |    |    |    |    |    | CS | YSP | WRL | IPRI | EQ |    |    |      |     |    |      |      |    |    |      | TRI  | NCM | ODE |          |   |   |   |   |   |   |   |

|    |    |    |    |    |    | CS | YSP | WRL | IPAG | СК |    |    |      |     |    |      |      |    |    |      | STIC | KYO | RUN | I        |   |   |   |   |   |   |   |

|    |    |    |    |    |    |    |     |     |      |    |    |    |      |     |    |      |      |    |    | C    | RUN  | DET | ECT |          |   |   |   |   |   |   |   |

#### Figure 5: Control/Status Register (architecture version 0) bit assignments

#### Bits [31:8,3:2,0]

See the ARM® Debug Interface v5 Architecture Specification.

#### WDATAERR, bit [7] and READOK, bit [6]

Support for these bits is DATA LINK DEFINED:

for JTAG-DP these bits are reserved, RAZ/WI.

DP architecture version 0 only supports JTAG-DP.

#### STICKYERR, bit [5], STICKYCMP, bit [4] and STICKYORUN, bit [1]

These bits are defined as R/W1C. For a definition of these bits, see the ARM® Debug Interface v5 Architecture Specification.

## 5.2.2 The AP Select Register, SELECT (architecture version 0)

In DP architecture version 0, the AP Select Register, SELECT, is:

- a read/write register

- accessed by a read or write of DP register 0x8.

Figure 6 shows the register bit assignments.

| 31 | 30 | 29 | 28  | 27  | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6    | 5    | 4  | 3 | 2 | 1 | 0 |

|----|----|----|-----|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|----|------|------|----|---|---|---|---|

|    |    |    | APS | SEL |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   | AF | PBAN | NKSI | ΞL |   |   |   |   |

#### Figure 6: AP Select Register (architecture version 0) bit assignments

#### APSEL and APBANKSEL, bits [31:24,7:4]

See the ARM® Debug Interface v5 Architecture Specification.

#### Bits [23:8,3:0]

Reserved, UNK/SBZP.

For compatibility with other DP architecture versions, ARM recommends that tools do not read the SELECT register.

## 5.2.3 The AP Abort Register, ABORT (architecture version 0)

In DP architecture version 0, the AP Abort Register, ABORT, is

- a write-only register

- accessed in a DATA LINK DEFINED manner:

- for JTAG-DP it is accessed via its own scan-chain.

DP architecture version 0 only supports JTAG-DP.

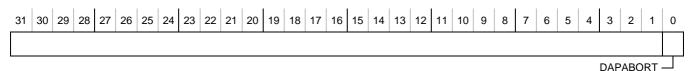

Figure 7 shows the register bit assignments.

Figure 7: AP Abort Register (architecture version 0) bit assignments

#### Bits [31:1]

Reserved, SBZ.

#### DAPABORT, bit [0]

SBO. This bit must be written as 1. See the ARM® Debug Interface v5 Architecture Specification.

#### Note

For JTAG-DP, the ABORT register is written from bits [34:3] of the data register scan-chain selected by the ABORT instruction. Writing a value other than 0x000000008 to the ABORT scan-chain gives UNPREDICTABLE results.

For more details on the ABORT scan-chain see the ARM® Debug Interface v5 Architecture Specification

## 5.3 DP architecture version 1

Architecture version 1 extends version 0 with support for:

• the Debug Port Identification Register, DPIDR

• the AP Abort Register, ABORT

• the Data Link Control Register, DLCR.

The definition of other registers is also changed:

- the behavior on writing to bits [5:4,1] of the CTRL/STAT register is DATA LINK DEFINED

- bit [0] of the SELECT register is defined as DPBANKSEL

- the SELECT register is write-only.

#### Note

Debug Port architecture version 1 is the DP architecture defined for SW-DP in the ARM® Debug Interface v5 Architecture Specification.

| Address | DPBANKSEL | Access     | Description                                                                |

|---------|-----------|------------|----------------------------------------------------------------------------|

| 0x0     | -         | Read-only  | The Debug Port ID Register, DPIDR (architecture version 1) on page 22      |

|         |           | Write-only | DATA LINK DEFINED registers on page 26                                     |

| 0x4     | 0         | Read/write | The Control/Status Register, CTRL/STAT (architecture version 1) on page 25 |

|         | 1         | Read/write | The Data Link Control Register, DLCR on page 26                            |

| 0x8     | -         | Read-only  | DATA LINK DEFINED registers on page 26                                     |

|         |           | Write-only | The AP Select Register, SELECT (architecture version 1) on page 25         |

| 0xC     | -         | Read-only  | The Read Buffer, RDBUFF                                                    |

|         |           | Write-only | DATA LINK DEFINED registers on page 26                                     |

The DP register map in version 1 of the DP architecture is shown in Table 7.

#### Table 7: Debug Port register map, architecture version 1

## 5.3.1 The Debug Port ID Register, DPIDR (architecture version 1)

The Debug Port ID Register, DPIDR, provides identification information about the Debug Port, such as what features are implemented.

The DPIDR is:

- a read-only register

- accessed by a read of DP register 0x0

- not affected by the value of SELECT.CTRLSEL.

Figure 8 shows the register bit assignment, with their values for an ARM design.

| 31 | 3                                                                                                                                                 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20  | 19 | 18 | 17 | 16  | 15   | 14 | 13 | 12 | 11 | 10 | 9  | 8    | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|----|----|----|----|----|----|----|-----|----|----|----|-----|------|----|----|----|----|----|----|------|-----|---|---|---|---|---|---|---|

|    | 1         30         29         28         27         26         25         24         23         22         24           REVISION         PARTNO |    |    |    |    |    |    |    |    |    |    |     |    |    | ١  | VER | SION | ١  |    |    |    |    | DE | SIGN | IER |   |   |   |   | 1 |   |   |

|    | REVISION PARTNO                                                                                                                                   |    |    |    |    |    |    |    |    |    | ſ  | MIN |    |    |    |     |      | 0  | 1  | 0  | 0  | 0  | 1  | 1    | 1   | 0 | 1 | 1 |   |   |   |   |

#### Figure 8: Debug Port ID Register (architecture version 1) bit assignments

#### REVISION, bits [31:28]

Revision code. The meaning of this field is IMPLEMENTATION DEFINED.

#### PARTNO, bits [27:20]

Part Number for the Debug Port. This value is provided by the designer of the Debug Port and must not be changed. Current DPs designed by ARM Limited have the PARTNO value 0xBA.

#### Bits [19:17]

Reserved, UNK.

#### MIN, bit [16]

Minimal Debug Port functions implemented.

- 1 Transaction Counter, Pushed Verify and Pushed Find operations are not implemented.

- **0** Transaction Counter, Pushed Verify and Pushed Find operations are implemented.

#### VERSION, bits [15:12]

- Version of the Debug Port architecture implemented. The valid values for this field are:

- **0x0** Reserved. Implementations of DP architecture version 0 do not implement DPIDR.

- **0x1** DP architecture version 1.

All other values are reserved.

#### DESIGNER, bits [11:1]

Designer ID. An 11-bit code formed from the JEDEC JEP-106 continuation code and identity code. The ID identifies the designer of the Debug Port. The ARM Limited value for this field, shown above, is 0x23B. Other designers must insert their own JEDEC-assigned code here.

Bit [0] RAO.

#### Note

JTAG-DP implementations of architecture version 1 are required to also implement the IDCODE instruction and IDCODE scan-chain. The architecture does not require that the DPIDR value and JTAG IDCODE value are the same. The JTAG IDCODE value identifies the JTAG-DP TAP and its designer. See *The JTAG TAP ID Register*, IDCODE on page 19.

## 5.3.2 The AP Abort Register, ABORT (architecture version 1)

In DP architecture version 1, the ABORT register:

- is a write-only register

- accessed in a DATA LINK DEFINED manner:

- for SW-DP it is accessed by a write to DP register 0x0

- for JTAG-DP it is accessed via its own scan-chain

- has fields that are not defined for architecture version 0.

Figure 9 shows the register bit assignments.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8  | 7   | 6   | 5    | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|----|-----|-----|------|---|---|---|---|---|

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |    |     |     |      |   |   |   |   |   |

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   | OR | UNE | RRC | LR - |   |   |   |   |   |

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   | ١  | VDE | RRC | LR - |   |   |   |   |   |

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   | S  | TKE | RRC | LR - |   |   |   |   |   |

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   | S  | ткс | MPC | LR - |   |   |   |   |   |

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |    | DAP | ABO | RT - |   |   |   |   |   |

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |    |     |     |      |   |   |   |   |   |

#### Figure 9: AP Abort Register (architecture version 1) bit assignments

#### Bits [31:5]

Reserved, SBZ.

#### ORUNERRCLR, WDERRCLR, STKERRCLR, STKCMPCLR, and DAPABORT, bits [4:0]

See the ARM® Debug Interface v5 Architecture Specification.

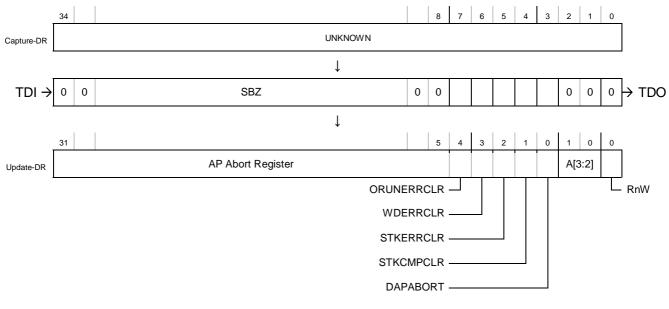

#### ABORT scan-chain operation, JTAG-DP (architecture version 1)

As in DP architecture version 0, when the ABORT instruction is the current instruction in the IR, the serial path between **TDI** and **TDO** is connected to a 35-bit scan chain that is used to access the AP Abort Register.

On Capture-DR, an UNKNOWN value is written to this scan chain. The debugger must scan 0 into bits [34:8,2:0] of this scan chain. This value:

- writes the RnW bit as 0

- writes the A[3:2] field as 0

- writes the SBZ fields of the AP Abort Register as 0.

The effect of scanning a 1 into any of bits [34:8,2:0] of this scan chain is UNPREDICTABLE. On Update-DR, bits [34:3] of this scan chain are written to the AP Abort Register.

Figure 10 shows the operation of this scan chain.

#### Figure 10: JTAG-DP ABORT scan-chain operation

#### Note

For JTAG-DP, the ABORT register is written from bits [34:3] of the data register scan-chain selected by the ABORT instruction. As in DP architecture version 0, this scan-chain returns an UNKNOWN value on Capture-DR, and at Update-DR bits [2:0] are SBZ.

In DP architecture version 0, bits [34:4] of the scan-chain are SBZ and bit [3] is SBO, since ABORT[31:1] is SBZ and ABORT[0] is SBO. Bits [2:0] of the scan-chain are SBZ.

In DP architecture version 1, bits [34:8] are SBZ and no bits are SBO, since ABORT[31:5] is SBZ and ABORT[4:0] are as defined above.

For more details on the ABORT scan-chain see the ARM® Debug Interface v5 Architecture Specification.

## 5.3.3 The AP Select Register, SELECT (architecture version 1)

In DP architecture version 1, the SELECT register

- is a write-only register

- is accessed by a write of DP register 0x8

- has fields that are not defined for architecture version 0.

Figure 11 shows the register bit assignments.

| 31 30 29 28 27 26 25 24 | 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 | 7 6 5 4   | 3 2 1 | 0 |

|-------------------------|-----------------------------------------------|-----------|-------|---|

| APSEL                   |                                               | APBANKSEL |       |   |

DPBANKSEL

#### Figure 11: AP Select Register (architecture version 1) bit assignments

#### APSEL, APBANKSEL, and DPBANKSEL, bits [31:24,7:4,0]

See the ARM® Debug Interface v5 Architecture Specification.

#### Note

In the ARM® Debug Interface v5 Architecture Specification DPBANKSEL is named CTRLSEL.

#### Bits [23:8,3:1]

Reserved, UNK/SBZP.

The reset value of the SELECT register is UNKNOWN. Tools must initialize SELECT before accessing any AP registers or registers affected by DPBANKSEL.

## 5.3.4 The Control/Status Register, CTRL/STAT (architecture version 1)

In DP architecture version 1, the CTRL/STAT register:

- is a read/write register

- is accessed by a read or write of DP register 0x4 when SELECT.DPBANKSEL is 0x0

- has behavior for some fields that differs from that for architecture version 0.

Figure 12 shows the register bit assignments.

| 31 | 30 | 29 | 28 | 27 | 26 | 25   | 24  | 23  | 22   | 21 | 20 | 19 | 18  | 8 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10    | 9   | 8    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|------|-----|-----|------|----|----|----|-----|------|----|----|----|----|----|----|-------|-----|------|---|---|---|---|---|---|---|---|

|    |    |    |    |    |    |      |     |     |      |    |    |    | TRI | NCNT | Т  |    |    |    |    | ſ  | MASK  | LAN | IE   |   |   |   |   |   |   |   |   |

|    |    |    |    |    |    | CD   | BGR | STR | EQ   |    |    |    |     |      |    |    |    |    |    |    | WD    | ATA | ERR- |   |   |   |   |   |   |   |   |

|    |    |    |    |    |    | CD   | BGR | STA | СК   |    |    |    |     |      |    |    |    |    |    |    | I     | REA | DOK- |   |   |   |   |   |   |   |   |

|    |    |    |    |    |    | CD   | BGP | WRI | JPRI | EQ |    |    |     |      |    |    |    |    |    |    | STI   | СКҮ | ERR- |   |   |   |   |   |   |   |   |

|    |    |    |    |    |    | CD   | BGP | WRI | JPA  | СК |    |    |     |      |    |    |    |    |    |    | STI   | CKY | CMP- |   |   |   |   |   |   |   |   |

|    |    |    |    |    |    | CS   | YSP | WRL | JPRE | Q  |    |    |     |      |    |    |    |    |    |    | TRM   | ICM | ODE- |   |   |   |   |   | J |   |   |

|    |    |    |    |    |    | - CS | YSP | WRL | JPAC | СК |    |    |     |      |    |    |    |    |    | :  | STICI | ۲O  | RUN- |   |   |   |   |   |   |   |   |

|    |    |    |    |    |    |      |     |     |      |    |    |    |     |      |    |    |    |    |    | С  | RUN   | DET | ECT- |   |   |   |   |   |   |   |   |

#### Figure 12: Control/Status Register (architecture version 1) bit assignments

Bits [31:24:2,0]

See the ARM® Debug Interface v5 Architecture Specification.

#### TRNCNT, MASKLANE and TRNMODE, bits [23:8,3:2]

Not supported in MINDP configuration. In MINDP configuration, writing a value other than zero to either TRNCNT or TRNMODE is UNPREDICTABLE.

For a definition of these bits, see the ARM® Debug Interface v5 Architecture Specification.

#### WDATAERR and READOK, bits [7:6]

Support for these bits is DATA LINK DEFINED.

- For SW-DP these bits are RO/WI.

- For JTAG-DP these bits are reserved, RAZ/WI.

For a definition of these bits, see the ARM® Debug Interface v5 Architecture Specification.

#### STICKYERR, STICKYCMP, and STICKYORUN, bit [5:4,1]

The behavior on writing to these bits is DATA LINK DEFINED.

- For SW-DP, these bits are RO/WI.

- For JTAG-DP, these bits are R/W1C. Writing a 0 to these bits is ignored.

For a definition of these bits, see the ARM® Debug Interface v5 Architecture Specification.

STICKYCMP is not supported in MINDP configuration. In MINDP configuration, writing a 1 to STICKYCMP is UNPREDICTABLE.

## 5.3.5 The Data Link Control Register, DLCR

The Data Link Control Register, DLCR, is:

- a DATA LINK DEFINED read/write register

- defined in architecture version 1

- accessed by a read or write of DP register 0x4 when SELECT.DPBANKSEL is 0x1.

- The contents of the Data Link Control Register, DLCR, are DATA LINK DEFINED.

In the *ARM*® *Debug Interface v5 Architecture Specification* the Serial Wire definition of DLCR is named WCR. The definition of DLCR for Serial Wire is unchanged.

For JTAG-DP, DLCR is reserved. Accessing the DLCR is UNPREDICTABLE.

#### 5.3.6 DATA LINK DEFINED registers

For SW-DP the DATA LINK DEFINED registers are listed in Table 8.

| Address | Access     | Description                                                                                           |

|---------|------------|-------------------------------------------------------------------------------------------------------|

| 0x0     | Write-only | The AP Abort Register, ABORT (architecture version 1) on page 23                                      |

| 0x8     | Read-only  | The Read Resend Register, RESEND. See the <i>ARM</i> ® Debug Interface v5 Architecture Specification. |

| 0xC     | Write-only | Reserved                                                                                              |

#### Table 8: SW-DP DATA LINK DEFINED registers

For JTAG-DP both  $\ensuremath{\mathsf{DATA}}\xspace$  LINK  $\ensuremath{\mathsf{DeFINED}}\xspace$  registers are reserved.

Accessing a reserved DATA LINK DEFINED register is UNPREDICTABLE.

## 5.4 DP architecture version 2

Architecture version 2 extends version 1 with support for:

- the Target Identifier Register, TARGETID

- the Data Link Protocol Identification Register, DLPIDR.

The definition of other registers is also changed:

• the DPBANKSEL field in the SELECT register is extended to bits [3:0].

The DP register map in version 2 of the DP architecture is shown in Table 9.

| Address | DPBANKSEL | Access     | Description                                                           |

|---------|-----------|------------|-----------------------------------------------------------------------|

| 0x0     | -         | Read-only  | The Debug Port ID Register, DPIDR (architecture version 2) on page 27 |

| _       |           | Write-only | DATA LINK DEFINED registers                                           |

| 0x4     | 0x0       | Read/write | The Control/Status Register, CTRL/STAT                                |

|         | 0x1       | Read/write | The Data Link Control Register, DLCR                                  |

|         | 0x2       | Read-only  | The Target Identification Register, TARGETID on page 28               |

|         | 0x3       | Read/write | The Data Link Protocol Identification Register, DLPIDR on page 29     |

| 0x8     | -         | Read-only  | DATA LINK DEFINED registers                                           |

|         |           | Write-only | The AP Select Register, SELECT (architecture version 2) on page 28    |

| 0xC     | -         | Read-only  | The Read Buffer, RDBUFF                                               |

|         |           | Write-only | DATA LINK DEFINED registers                                           |

#### Table 9: Debug Port register map, architecture version 2

## 5.4.1 The Debug Port ID Register, DPIDR (architecture version 2)

The DPIDR is:

- a read-only register

- accessed by a read of DP register 0

- not affected by the value of SELECT.CTRLSEL.

Figure 13 shows the register bit assignment, with their values for an ARM design.

| 31 30 29 28 | 27 26 | 25 | 24 | 23 | 22 | 21 | 20  | 19   | 18 | 17  | 16 | 15 | 14 | 13 | 12   | 11  | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------|-------|----|----|----|----|----|-----|------|----|-----|----|----|----|----|------|-----|----|---|---|---|---|---|---|---|---|---|---|

| REVISION    |       |    |    |    |    | Ņ  | VER | SION | 1  |     |    |    |    | DE | SIGN | IER |    |   |   |   | 1 |   |   |   |   |   |   |

|             | •     |    |    |    |    |    |     |      | ſ  | MIN |    |    |    |    |      | 0   | 1  | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 |   |

#### Figure 13: Debug Port ID Register (architecture version 2) bit assignments

#### REVISION, PARTNO, and DESIGNER, bits [31:16,11:1]

See The Debug Port ID Register, DPIDR (architecture version 1) on page 22.

#### Bits [19:7]

Reserved, UNK.

MIN, bit [16]

See The Debug Port ID Register, DPIDR (architecture version 1) on page 22.

#### VERSION, bits [15:12]

Version of the Debug Port architecture implemented. The valid values for this field are:

- **0x0** Reserved. Implementations of DP architecture version 0 do not implement DPIDR.

- **0x1** DP architecture version 1.

- **0x2** DP architecture version 2.

- All other values are reserved.

### Bit [0] RAO.

## 5.4.2 The AP Select Register, SELECT (architecture version 2)

In DP architecture version 2, the SELECT register is:

- a write-only register

- accessed by a write of DP register 0x8.

Figure 14 shows the register bit assignments.

| 31 30 29 28 27 26 25 24 | 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 | 7 6 5 4   | 3 2 1 0   |

|-------------------------|-----------------------------------------------|-----------|-----------|

| APSEL                   |                                               | APBANKSEL | DPBANKSEL |

#### Figure 14: AP Select Register (architecture version 2) bit assignments

#### APSEL, bits [31:24], and APBANKSEL, bits [7:4]

See the ARM® Debug Interface v5 Architecture Specification.

#### Bits [23:8]

Reserved, UNK/SBZP.

#### DPBANKSEL, bits [3:0]

Selects the register that appears at DP register 0x4:

- **0x0** CTRL/STAT, read/write

- 0x1 DLCR, read/write

- **0x2** TARGETID, read-only

- **0x3** DLPIDR, read-only.

All other values are reserved. Writing a reserved value to DPBANKSEL is UNPREDICTABLE.

This field replaces the previously defined DPBANKSEL, bit [0].

## 5.4.3 The Target Identification Register, TARGETID

The Target Identification Register, TARGETID, is:

- a read-only register

- defined in DP architecture version 2

- accessed by a read of DP register 0x4 when SELECT.DPBANKSEL is set to 0x2.

This register provides information about the target when the host is connected to a single device. Figure 15 shows the register bit assignments.

| 3 | 1  | 30   | 29   | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20  | 19  | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7   | 6   | 5   | 4 | 3 | 2 | 1 | 0 |

|---|----|------|------|----|----|----|----|----|----|----|----|-----|-----|----|----|----|----|----|----|----|----|----|---|---|-----|-----|-----|---|---|---|---|---|

|   | ΤF | REVI | ISIO | N  |    |    |    |    |    |    | Г  | PAF | RTN | )  |    |    |    |    |    |    |    |    |   |   | TDE | SIG | NER |   |   |   |   | 1 |

#### Figure 15: Target Identification Register bit assignments

#### TREVISION, bits [31:28]

Target revision.

#### TPARTNO, bits [27:12]

IMPLEMENTATION DEFINED. The value is assigned by the designer of the part and should be unique to that part.

#### TDESIGNER, bits [11:1]

IMPLEMENTATION DEFINED. An 11-bit code formed from the JEDEC JEP-106 continuation code and identity code. The ID identifies the designer of the part. Designers must insert their own JEDEC-assigned code here.

#### Note

The ARM Limited JEP-106 value is not shown for this field. Although ARM Limited might design a DP containing the TARGETID register, the designer of *part* is typically another designer who takes that DP and creates a part around it.

If the designer of the part is ARM Limited, then the value of this field is 0x23B.

#### Bit [0] RAO.

## 5.4.4 The Data Link Protocol Identification Register, DLPIDR

The Data Link Protocol Identification Register, DLPIDR is:

- a read-only register

- defined in DP architecture version 2

- accessed by a read of DP register 0x4 when SELECT.DPBANKSEL is set to 0x3.

The contents of the Data Link Protocol Identification Register, DLPIDR, are DATA LINK DEFINED.

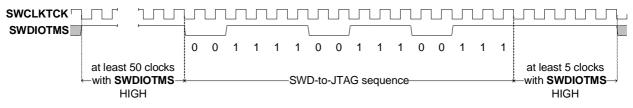

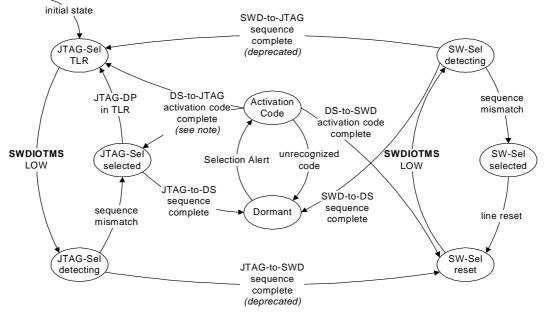

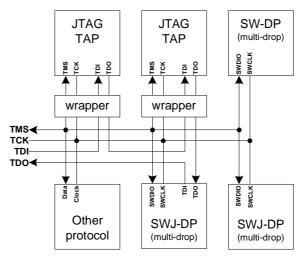

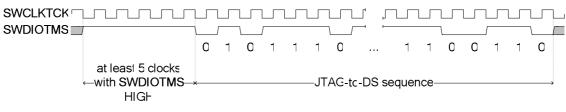

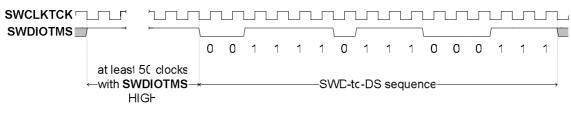

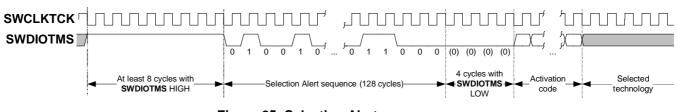

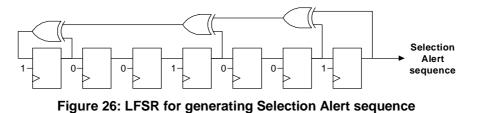

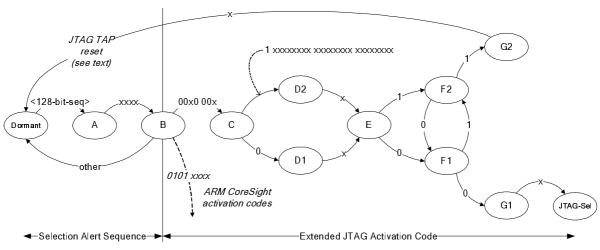

For Serial Wire, DLPIDR gives Serial Wire protocol version information. Figure 16 shows the register bit assignments for Serial Wire protocol.