## Cortex-M33 processor ARMv8-M IoT Kit FVP User Guide

Version 2.0

Copyright © 2017 ARM Limited or its affiliates. All rights reserved.

#### **Revision Information**

| Date            | Version | Confidentiality  | Change         |

|-----------------|---------|------------------|----------------|

| 06 October 2016 | 1.0     | Confidential     | First release  |

| 10 March 2017   | 2.0     | Non-Confidential | Second release |

The following revisions have been made to this document.

#### **Proprietary Notice**

Words and logos marked with ® or <sup>™</sup> are registered trademarks or trademarks of ARM® in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

Unrestricted Access is an ARM internal classification.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

## Contents

| 1   | Introduction                                          | 5  |

|-----|-------------------------------------------------------|----|

| 1.1 | IoT Kit MPS2+ system                                  | 5  |

| 1.2 | IoT subsystem                                         | 5  |

| 1.3 | FPGA expansion subsystem                              | 6  |

| 2   | System requirements and compliance                    | 8  |

| 2.1 | Generic TrustZone technology for ARMv8-M requirements | 8  |

| 2.2 | ARM IoT system requirements                           | 9  |

| 3   | IoT Kit subsystem architecture                        | 10 |

| 3.1 | System top-level interfaces                           | 11 |

| Fι  | unctional clock and reset interfaces                  | 11 |

| Al  | HB Slave expansion interfaces                         | 13 |

| Al  | HB Master expansion interfaces                        | 13 |

| In  | terrupt interface                                     | 14 |

| JT  | rAG and SWO interface                                 | 15 |

| Tr  | ace port                                              | 15 |

| De  | ebug authentication interface                         | 16 |

| Тс  | op-level static configuration signals                 | 16 |

| Se  | ecurity control expansion signals                     | 16 |

| 3.2 | Top-level system parameters                           | 22 |

| 3.3 | System memory map                                     | 23 |

| In  | ternal SRAM regions                                   |    |

| Ba  | ase peripheral regions                                |    |

| Pr  | rivate CPU region                                     |    |

| Sy  | ystem control                                         |    |

| PI  | PB region                                             |    |

| Sy  | ystem debug region                                    |    |

| 3.4 | CPU element                                           |    |

| C   | PU_IDENTITY                                           | 32 |

| 3.5 | Base element                                          |    |

| Se  | ecure privilege control block                         |    |

| N   | on-secure privilege control block                     | 50 |

| SI  | RAM Memory Protection Controllers                     |    |

| A   | PB Peripheral Protection Controller                   | 57 |

| 3.6 | SRAM element                                          | 58 |

| E   | Exclusive Access Monitor                                | 58 |

|-----|---------------------------------------------------------|----|

| 3.7 | System control element                                  | 59 |

| S   | System Information block                                | 59 |

| S   | SYS_VERSION                                             | 60 |

| S   | SYS_CONFIG                                              | 60 |

| S   | System Control Register block                           | 62 |

| 3.8 | Interrupt Map                                           | 72 |

| 3.9 | Clocking infrastructure                                 | 73 |

| 3.1 | 0 Reset infrastructure                                  | 73 |

| Ρ   | Power control infrastructure                            | 73 |

| 4   | MPS2+ system expansion                                  | 74 |

| 4.1 | MPS2+ FPGA based on IoT Kit subsystem                   | 75 |

| 4.2 | Memory Maps                                             | 77 |

| E   | External ZBT SRAMs synchronous SRAM for code (SSRAM1)   | 77 |

| E   | External ZBT SRAMs Synchronous SRAM (SSRAM2 and SSRAM3) | 78 |

| Ρ   | PSRAM                                                   | 80 |

| E   | Expansion system peripherals                            | 81 |

| F   | PGA Secure privilege control                            | 85 |

| 4.3 | Interrupt Map                                           | 89 |

| 5   | AHB5 TrustZone memory protection controller             | 91 |

| 5.1 | Look Up Table (LUT) examples                            | 93 |

| 6   | AHB5 TrustZone master security controller               | 95 |

| 7   | Peripheral Protection Controller                        | 96 |

## 1 Introduction

This document provides a description of a reference system that uses the TrustZone<sup>®</sup> technology to implement a secure subsystem. The system integrates a generic *Internet of Things* (IoT) subsystem that is referred to as a Kit, and includes extra system peripherals to form a full system. This system is intended to be implemented on the *Cortex-M Prototyping System* (MPS2+)-based system *Field Programmable Gate Array* (FPGA) and on Fast Models *Fixed Virtual Platform* (FVP).

### 1.1 IoT Kit MPS2+ system

The IoT Kit MPS2 system integrates the following two key parts:

- An IoT subsystem.

- An FPGA expansion subsystem.

#### Note

Only the components that are described in the IoT Kit subsystem are considered to be part of the Secure system. Other peripherals that may be present in the FPGA or FVP implementations are not within the scope of the Secure system.

## 1.2 IoT subsystem

The IoT subsystem integrates key components available from ARM to create a subsystem that can remain largely unmodified when integrated into different systems. The IoT subsystem integrates the following parts:

• An ARMv8-M processor core with a *Floating Point Unit* (FPU) and *Digital Signal Processor* (DSP) extensions and *Embedded Trace Macrocell* (ETM).

#### Note

The FVP does not support the ETM.

- A single bank of SRAM.

- CoreLink SDK-200 components including:

- o CoreLink<sup>™</sup> SIE-200 System IP for Embedded components:

- AHB5 Memory Protection Controller (MPC).

- AHB5 Peripheral Protection Controller (PPC).

- AHB5 Exclusive Access Monitor (EAM).

- AHB5 to APB Bridge.

- AHB5 Fabric.

- o CMSDK components including.

- Timers and Dual timers.

- Watchdog timer.

- An Implementation Defined Attribution Unit (IDAU).

- A Subsystem Security Controller.

The IoT subsystem described here is the first-generation IoT subsystem Kit and does not implement the following:

• Power control.

The subsystem is expected to be always ON.

• Clock control.

The main system runs from a single clock source that is generated from outside the subsystem.

Comprehensive reset generation.

The subsystem contains a basic reset control. Power-on reset is generated externally for the subsystem, and the processor is able to request and therefore cause a system reset that does not affect the Debug logic within the processor.

Note

The full Cortex-M33 subsystem IP is available as part of the CoreLink SDK-200.

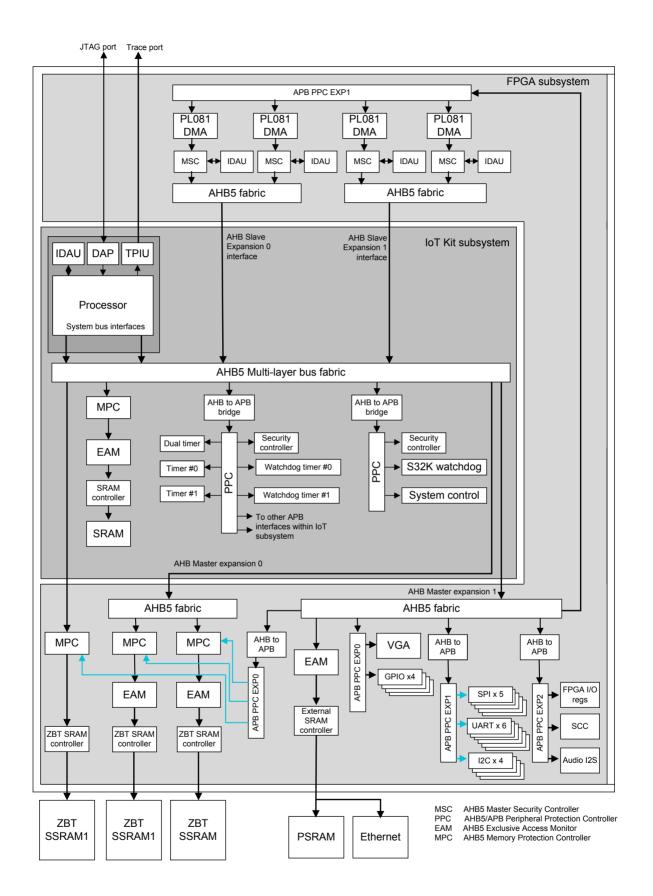

## 1.3 FPGA expansion subsystem

The FPGA expansion subsystem extends the IoT subsystem by integrating more components to form a full example system. The FPGA expansion subsystem integrates the following:

- ZBT SRAM controllers provide access to on board ZBT SRAMs. These function as the main code memory and also as extra data storage memory.

- PL081 DMA controllers, primarily to acts as other masters within the system.

- An SRAM controller, to provide access to external devices with asynchronous SRAM like interfaces.

- An FPGA system controller.

- An Implementation Defined Attribution Unit (IDAU).

- CoreLink SDK-200 components including:

- CoreLink SIE-200 System IP for Embedded and CMSDK components:

- GPIOs.

- UARTs.

- AHB5 Memory Protection Controller (MPC).

- AHB5 Master Security Controller (MSC).

- AHB5 Peripheral Protection Controller (PPC).

- AHB5 Exclusive Access Monitor (EAM).

- AHB5 to APB Bridge.

- AHB5 Fabric.

- PL022 SPI.

- I2S Controller.

## 2 System requirements and compliance

The IoT Kit MPS2 system is designed to meet requirements as follows:

- Generic TrustZone technology for ARMv8-M requirements.

- ARM IoT system design requirements.

# 2.1 Generic TrustZone technology for ARMv8-M requirements

The following requirements form a basic set that all systems that support TrustZone technology for ARMv8-M must have:

- Memory spaces (program and data) that are already, or can be partitioned, into Secure, and Non-secure memory space.

- Peripherals that are already in, or can be placed into Secure and Non-secure memory space.

- No access to Secure assets from the Non-secure world, which includes software running on processors in Non-secure mode, and peripherals that are Non-secure.

- Secure assets can be program code or data memory space, or any operating hardware and program state. This includes avoiding cases where states are inadvertently shared by using peripherals that are able to operate both in Secure and Non-secure mode concurrently.

- Boot-up from a memory space that is Secure, and optionally execute Non-secure firmware after Secure world initialization.

- Support for debug authentication signals that allow or disallow Secure debug and trace. This includes the ability to set the default reset values, and extra capability at boot either automatically or by Secure boot firmware to override the reset values after extra certificate authentication. The certificate authentication scheme is not defined in this document.

In an IoT SoC, Secure code and data memory are often implemented on-chip. Since this system is targeting the MPS2 FPGA platform, most of the memory system is implemented with ZBT SRAMs on the circuit board. These SRAMs are also used to store Secure code, which means the Secure memory content is observable by probing the PCB board traces or pins. An attacker with physical access to the board might compromise the security of the system by viewing Secure memory content, modifying it, and so change the behavior of the program.

On an FPGA implementation of this platform, extra back doors might be provided to allow the designer to override some security measures. These include an access path from external on board *Microcontroller Unit* (MCU) to access the *Advanced High Performance* Bus (AHB) system using *Serial Peripheral Interface* (SPI).

This path provides access to Secure peripherals and allows the MCU to control **SPIDEN** and **SPNIDEN** settings. Debug tool vendors can make use of this back door for tool testing.

## 2.2 ARM IoT system requirements

The IoT Kit MPS2 system is also designed to meet a set of ARM requirements. These requirements are selected with the aim of:

- Demonstrating the creation of a Secure hardware platform using ARMv8-M processors, bus, and peripheral components.

- Providing an example implementation of key blocks in the system.

- Creating a degree of standardization in parts of the system design to ease software and firmware developers as they move between different generations of the IoT subsystem.

These requirements are as follows:

- The system fabric is primarily AHB5 based.

- The system is partitioned into a IoT Kit subsystem and the expansion subsystem, where:

- The IoT Kit subsystem contains the processor, and other key bus, and peripheral components that are expected to be common among many IoT systems.

- The expansion subsystem, where extra masters and peripherals are added to form an example system. For example, to target the FPGA on the MPS2 board.

- This partitioning also extends to memory and interrupt maps, where memory regions and interrupt signals specific to the IoT subsystem Kit are defined and reserved only for its own use, and in other areas that are provided as extension.

- The system uses ARMv8-M TrustZone technology and separates the system into two worlds, where:

- The IDAU defines the main system partitioning between Secure and Non-secure world where there are strict association of addresses spaces with security.

- Aliasing with extra security filters are used to map shared resources between the Secure and Non-secure worlds.

- The *Secure Attribution Unit* (SAU) allows trusted firmware to map more memory for Secure use only, and define memory areas as Non-secure Callable.

- Basic timers and Watchdog are placed within the IoT Kit subsystem to provide a standard set for use by software.

## 3 IoT Kit subsystem architecture

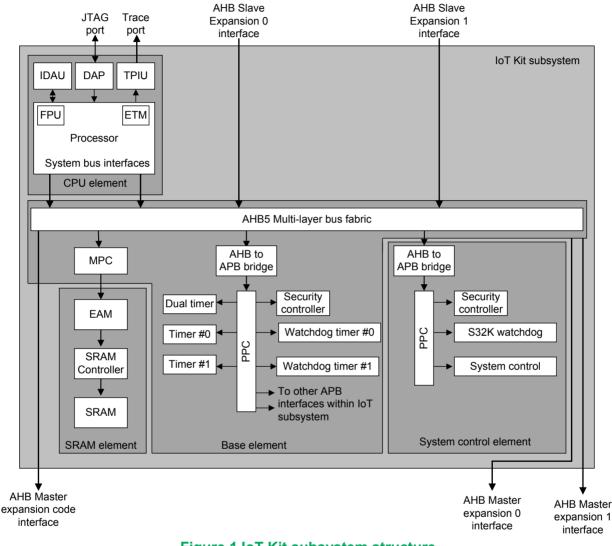

The IoT Kit subsystem integrates key components available from ARM to create a subsystem that can be integrated into different systems. The following figure shows the structure of the IoT Kit subsystem.

Figure 1 IoT Kit subsystem structure

The subsystem is divided into several elements:

• CPU element.

This element contains an ARMv8-M processor.

Base element.

This element implements the main AHB5 and APB interconnect. In addition, it also contains several timers and watchdog timers. The *Memory Protection Controller* (MPC) and *Peripheral Protection Controller* (PPC) are also on paths to memory and peripherals respectively to provide security gating.

• The SRAM element implements the main storage RAM for the system which is primarily intended for data storage, though code can also reside in the memory. *Exclusive*

Access Monitors (EAMs) are implemented in this element to support exclusive access that is now supported on AMBA AHB5.

• The System control element contains logic to provide software controls for power, clocks, resets, and general system control. In addition, a slow watchdog timer and a simple dual timer running on a separate slow clock are implemented within this element. The PPC is also included to provide Security gating to all peripheral in the element.

## 3.1 System top-level interfaces

The top-level system provides the following interfaces:

- Functional clock and reset interfaces.

- AHB slave expansion interfaces.

- AHB master expansion interfaces.

- Interrupt interface.

- JTAG and SWO interface.

- Trace port.

- Debug authentication interface.

- Top-level static configuration signals.

- Security control expansion signals.

These interfaces are not visible in the FVP.

#### Functional clock and reset interfaces

These interfaces are not visible in the FVP.

The IoT Kit subsystem has the following clock and reset signals<sup>1</sup>.

| Signal Name | Width | IN/OUT | Description                                                                                           |

|-------------|-------|--------|-------------------------------------------------------------------------------------------------------|

| MAINCLK     | 1     | IN     | Main Clock Input.                                                                                     |

|             |       |        | This clock is used by the subsystem to generate most other clocks that are used within the subsystem. |

| nPORESET    | 1     | IN     | Active low power-on reset input signal.                                                               |

| SYSCLK      | 1     | OUT    | Main system clock.                                                                                    |

|             |       |        | This clock is used by the subsystem.                                                                  |

<sup>&</sup>lt;sup>1</sup> FPGA Users should refer to Application Note AN505 Example IoT Kit Subsystem design for V2M-MPS2 (ARM DAI 0505).

| S32KCLK       | 1 | IN  | Slow clock.                                                                                           |

|---------------|---|-----|-------------------------------------------------------------------------------------------------------|

|               |   |     | A 32KHz clock input and is asynchronous to the other clocks in the system.                            |

| SWCLKTCK      | 1 | IN  | SW/JTAG clock.                                                                                        |

|               |   |     | Typically driven by an external debugger and<br>is asynchronous to the other clocks in the<br>system. |

| nTRST         | 1 | IN  | Active Low JTAG test logic reset signal.                                                              |

| TRACECLKIN    | 1 | IN  | Trace port clock input.                                                                               |

|               |   |     | Typically driven by the external Trace Port<br>Analyzer.                                              |

| TRACECLK      | 1 | OUT | Exported trace port clock.                                                                            |

| TRESETn       | 1 | IN  | Active low trace port asynchronous reset.                                                             |

|               |   |     | Typically driven by the external Trace Port<br>Analyzer.                                              |

| nPORESET_OUT  | 1 | OUT | Active low power-on reset for the expansion subsystem                                                 |

| nSYSRESET_OUT | 1 | OUT | Active low system reset for the expansion subsystem.                                                  |

| WARMRESETREQ  | 1 | IN  | Active high request to perform a warm system reset.                                                   |

#### Table 1 Functional clock and reset related interfaces

The IoT subsystem uses a main input clock, **MAINCLK**, that is used to derive most other clocks within the subsystem. This includes **SYSCLK**, which is synchronous and at the same frequency as **MAINCLK**.

The **nPORESET** signal is the power-on reset signal for the system. This signal must be held for at least four **S32KCLK** cycles at power-on of the system.

The **S32KCLK** clock input is an asynchronous clock input that is used to drive the **S32KWATCHDOG** and **S32KTIMER** signals. The **SWCLKTCK** input clock and **nTRST** reset input are associated with the JTAG or *Serial Wire Out* (SWO) debug port. The **TRACECLKIN** input clock, **TRACECLK** output clock, and **TRESETn** reset inputs are associated with the Trace output port.

The **nPORESET\_OUT** reset output is the power-on reset signal that is used by the expansion logic to the subsystem. The reset output merges other reset sources that are required to cause power-on reset. The **nSYSRESET\_OUT** reset output is the system reset signal that is generated by the subsystem to perform system reset. This reset signal must not be used to reset any debug related logic. This reset output is also asserted if **nPORESET\_OUT** is asserted. Both reset outputs are synchronous to **SYSCLK**, and will be sufficiently long enough in duration to reset logic on the S32KCLK domain after resynchronization to **S32KCLK**.

If the expansion logic to the subsystem requires system reset to be asserted, it can raise the request by asserting the **WARMRESETREQ** signal. This signal, when asserted, but is held high until the reset occurs on **nSYSRESET\_OUT** and must be cleared as a result of the reset being asserted.

#### AHB Slave expansion interfaces

The IoT Kit subsystem provides two AMBA AHB5 slave expansion interfaces<sup>2</sup> to allow the system integrator to add extra bus masters to the system. These interfaces are named:

- AHB5 Slave expansion 0 interface.

- AHB5 Slave expansion 1 interface.

Each of these interfaces supports the following features:

- A full 32-bit address bus, with each access providing access to the full 32-bit address space.

- 32-bit data width.

- TrustZone technology for ARMv8-M support, with the **HNONSEC** signal.

- Exclusive access support to SRAM memory.

#### AHB Master expansion interfaces

The IoT Kit subsystem provides two AMBA AHB5 master expansion interfaces<sup>2</sup> to allow the system integrator to add extra slave peripherals to the system. These interfaces are named:

- AHB5 Master expansion 0 interface.

- AHB5 Master expansion 1 interface.

In addition, a separate AHB5 Master interface is provided primarily to provide access to code memory. This interface is called the AHB5 Master expansion code interface.

Each of these interfaces supports the following features:

- A 32-bit address bus, with each access providing the full 32-bit address.

- 32-bit data width.

- TrustZone technology for ARMv8-M support, with the inclusion of the **HNONSEC** signal.

- Exclusive Access support, though the slave memory device in the expansion system that is expected to support exclusive access accessible must implement exclusive access monitoring in order for exclusive accesses to function correctly.

<sup>&</sup>lt;sup>2</sup> FPGA Users should refer to Application Note AN505 Example IoT Kit Subsystem design for V2M-MPS2 (ARM DAI 0505).

#### Note

In the expansion system, a *Memory Protection Controller* (MPC) must be placed on the path to code memory on the AHB5 Master expansion code interface to provide security access gating for the aliased memory region that this interface supports.

#### Interrupt interface

The following table lists the interrupt signals for use by the expansion subsystem. These connect to the interrupt controller of the processor within the IoT Kit subsystem.

| Signal Name                 | Width                   | IN/OUT | Description                                                                                                                                                                                  |

|-----------------------------|-------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXP_IRQ[EXP_NUMIRQ-<br>1:0] | EXP_NUMIRQ <sup>3</sup> | IN     | These are interrupt inputs from the expansion subsystem to the interrupt controller of the processor core within the subsystem.                                                              |

|                             |                         |        | The ARMv8-M core in the<br>subsystem implements with 32<br>reserved interrupt lines for internal<br>use and the remaining<br>(EXP_NUMIRQ) made available<br>for expansion on this interface. |

|                             |                         |        | Each bit EXP_IRQ[n] is connected to IRQ[32+n] of the processor NVIC.                                                                                                                         |

| EXP_NMI                     | 1                       | IN     | This provides a <i>Non-maskable</i><br><i>Interrupt</i> (NMI) input from the<br>expansion subsystem to the<br>interrupt controller of the<br>processor core within the<br>subsystem.         |

|                             |                         |        | This input is merged with other<br>NMI interrupt sources with the IoT<br>Kit subsystem before being seen<br>by the NVIC of the processor core.                                               |

**Table 2 Interrupt interface**

<sup>&</sup>lt;sup>3</sup> Defined in Table 12.

#### JTAG and SWO interface

The processor JTAG interface is made available to the top level of the IoT Kit subsystem. The interrupt signals are listed in the following table. Refer to the *Integration and Implementation Manual* for the ARMv8-M processor for more information on this interface.

| Signal Name | Width | IN/OUT | Description                         |

|-------------|-------|--------|-------------------------------------|

| TDI         | 1     | IN     | JTAG data in.                       |

| TDO         | 1     | OUT    | JTAG data out.                      |

| nTDOEN      | 1     | OUT    | JTAG TDO output enable.             |

| SWDITMS     | 1     | IN     | Serial wire data input and JTAG TMS |

| SWDO        | 1     | OUT    | Serial wire data output.            |

| SWDOEN      | 1     | OUT    | Serial wire data output enable.     |

| SWSEL       | 1     | OUT    | Serial wire protocol active signal. |

| JTAGSEL     | 1     | OUT    | JTAG protocol active signal.        |

| JTAGSEL     | 1     | OUT    | JTAG protocol active signal.        |

Table 3 JTAG and SWO interface

This interface is synchronous to the SWCLKTCK clock and the nTRST reset input resets it.

#### Trace port

The ARMv8-M processor trace port is made available to the top level of the IoT Kit subsystem. The interrupt signals are listed in the following table. See *the Integration and Implementation Manual* for the processor for more information on this interface.

| Signal Name | Width | IN/OUT | Description                |

|-------------|-------|--------|----------------------------|

| TRACECLK    | 1     | OUT    | Exported trace port clock. |

| TRACEDATA   | 4     | OUT    | Trace port data.           |

| TRACESWO    | 1     | OUT    | Serial Wire Viewer data    |

|             | 1     |        | •                          |

Table 4 Trace port

This interface is synchronous to the **TRACECLK** clock output.

#### Debug authentication interface<sup>4</sup>

The following table lists the debug authentication signals of the IoT Kit subsystem.

The inputs signals define the debug authentication signal values when not overridden by the internal Debug Authentication Registers. The final Debug Authentication signals are then made available as outputs to the rest of the system.

| Signal Name | Width | IN/OUT | Description                                                 |

|-------------|-------|--------|-------------------------------------------------------------|

| DBGEN_IN    | 1     | IN     | Debug enable input                                          |

| NIDEN_IN    | 1     | IN     | Non-Invasive Debug Enable Input                             |

| SPIDEN_IN   | 1     | IN     | Secure privilege Invasive Debug Enable Input                |

| SPNIDEN_IN  | 1     | IN     | Secure privilege Non-Invasive Debug Enable Input            |

| DBGEN       | 1     | OUT    | Merged Debug Enable Output                                  |

| NIDEN       | 1     | OUT    | Merged Non-Invasive Debug Enable Output                     |

| SPIDEN      | 1     | OUT    | Merged Secure privilege Invasive Debug Enable<br>Output     |

| SPNIDEN     | 1     | OUT    | Merged Secure privilege Non-Invasive Debug<br>Enable Output |

#### Table 5 Debug authentication interface

#### Note

The **DEVICEEN** input of the *Debug Access Port* (DAP) is connected to **DBGEN**. Therefore to begin JTAG-based Debug, **DBGEN** must be set to HIGH.

Top-level static configuration signals.

There are currently no static configuration signals that are defined at the top level of the IoT Kit subsystem.

Security control expansion signals.

The IoT Kits subsystem provides extra status and control signals to handle more *Master Security Controllers* (MSCs), *Memory Protection Controllers* (MPCs), *Peripheral Protection* Controllers (PPCs) and bridges with write buffers in the expansion system. These signals allow all to be controlled using the set of security control registers already implemented in the IoT Kit subsystem.

<sup>&</sup>lt;sup>4</sup> FPGA Users should refer to Application Note AN505 Example IoT Kit Subsystem design for V2M-MPS2 (ARM DAI 0505).

#### Memory Protection Controller expansion

The IoT Kit can support up to 16 MPCs in the expansion system.

The following signals allow the interrupts of the MPCs to be merged to the single MPC combined interrupt.

| Signal Name     | Width | IN/OUT | Description                                                                                                                                                                                                                                                |

|-----------------|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S_MPCEXP_STATUS | 16    | IN     | Interrupt status inputs from all expansion<br>MPCs. These are visible to the programmer<br>using the S_MPCEXP_STATUS register in<br>the Secure privilege Control Register block<br>and are used to raise an interrupt using the<br>MPC combined interrupt. |

#### Table 6 MPC expansion interrupt status input

APB Peripheral Protection Controller expansion

The IoT Kit can support up to four extra APB PPCs in the expansion system.

The following signals are provided to control the PPCs.

| Signal Name        | Width | IN/OUT | Description                                                                                                                                                                   |

|--------------------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S_APBPPCEXP_STATUS | 4     | IN     | APB PPC interrupt status input.                                                                                                                                               |

|                    |       |        | Each bit 'N' is connected to a single APB<br>PPC <n> where N is 0-3. These are<br/>associated to the<br/>S_APBPPCEXP_STATUS[3:0] field in the<br/>SECPPCINTSTAT register.</n> |

| S_APBPPCEXP_CLEAR  | 4     | OUT    | APB PPC interrupt clear output.                                                                                                                                               |

|                    |       |        | Each bit 'N' is connected to a single APB<br>PPC <n> where N is 0-3.These are<br/>associated to the<br/>S_APBPPCEXP_CLR[3:0] field in the<br/>SECPPCINTCLR register.</n>      |

| APB_NS_PPCEXP0     | 16    | OUT    | APB PPC Non-secure gating control.                                                                                                                                            |

| APB_NS_PPCEXP1     | 16    | OUT    | These are a set of four 16-bit interfaces,<br>and each interface connects to a PPC.                                                                                           |

| APB_NS_PPCEXP2     | 16    | OUT    | When each bit 'm' of an interface is HIGH,                                                                                                                                    |

| APB_NS_PPCEXP3     | 16    | OUT    | it defines the APB <m> interface that the target PPC controls as Non-secure access only.</m>                                                                                  |

|                    |       |        | Each 16-bit signal <b>APB_NS_PPCEXP<n></n></b><br>is driven by the APBNSPPCECP <n><br/>register.</n>                                                                          |

| APB_P_PPCEXP0      | 16    | OUT    | APB PPC privilege gating control.                                                                                                                                             |

| APB_P_PPCEXP1      | 16    | OUT    | These are a set of four 16-bit interfaces.                                                                                                                                    |

| APB_P_PPCEXP2      | 16    | OUT    | When each bit 'm' of an interface is HIGH,                                                                                                                                    |

| APB_P_PPCEXP3 | 16 | OUT | it defines the APB <m> interface that the<br/>target PPC controls as privilege access<br/>only.</m>                                                     |

|---------------|----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |    |     | Each signal is selected from either<br><b>APBSPPPCEXP<n>[m]</n></b> if<br>APB_NS_PPCEXP <n>[m] is 0 or<br/><b>APBNSPPPCEXP<n>[m]</n></b> otherwise.</n> |

Table 7 APB PPC expansion interface

Copyright © 2017 ARM Limited or its affiliates. All rights reserved.

#### AHB Protection Controller expansion

The IoT Kit can support up to four extra AHB PPCs in the expansion system.

The following signals are provided to control each PPC.

| Signal Name        | Width | IN/OUT | Description                                                                                                                                                                     |

|--------------------|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S_AHBPPCEXP_STATUS | 4     | IN     | AHB PPC interrupt status input.                                                                                                                                                 |

|                    |       |        | Each bit 'N' is connected to a single AHB<br>PPC <n> where N is 0-3. These are<br/>associated with the<br/>S_AHBPPCEXP_STATUS[3:0] field in the<br/>SECPPCINTSTAT register.</n> |

| S_AHBPPCEXP_CLEAR  | 4     | OUT    | AHB PPC interrupt clear output.                                                                                                                                                 |

|                    |       |        | Each bit 'N' is connected to a single AHB<br>PPC <n> where N is 0-3. These are<br/>associated with the<br/>S_AHBPPCEXP_CLR[3:0] field in the<br/>SECPPCINTCLR register.</n>     |

| AHB_NS_PPCEXP0     | 16    | OUT    | AHB PPC Non-secure gating control.                                                                                                                                              |

| AHB_NS_PPCEXP1     | 16    | OUT    | These are a set of four 16-bit interfaces,<br>and each interface connects to a PPC.                                                                                             |

| AHB_NS_PPCEXP2     | 16    | OUT    | When each bit 'm' of an interface is HIGH,                                                                                                                                      |

| AHB_NS_PPCEXP3     | 16    | OUT    | it defines the AHB <m> interface that the target PPC controls as Non-secure access only.</m>                                                                                    |

|                    |       |        | Each 16-bit signal<br>AHB_NS_PPCEXP <n> is driven by the<br/>AHBNSPPCECP<n> register.</n></n>                                                                                   |

| AHB_P_PPCEXP0      | 16    | OUT    | AHB PPC privilege gating control.                                                                                                                                               |

| AHB_P_PPCEXP1      | 16    | OUT    | These are a set of four 16-bit interfaces.                                                                                                                                      |

| AHB_P_PPCEXP2      | 16    | OUT    | When each bit 'm' of an interface is HIGH,<br>it defines the AHB <m> interface that the</m>                                                                                     |

| AHB_P_PPCEXP3      | 16    | OUT    | target PPC controls as privilege access only.                                                                                                                                   |

|                    |       |        | Each signal is selected from either<br><b>AHBSPPPCEXP<n>[m]</n></b> if<br>AHB_NS_PPCEXP <n>[m] = '0' or<br/><b>AHBNSPPPCEXP<n>[m]</n></b> otherwise.</n>                        |

Table 8 AHB PPC expansion interface

#### Master Security controller expansion

The IoT Kit supports up to 16 extra MSC in the expansion system.

The following signals are provided to control each PPC.

| Signal Name     | Width | IN/OUT | Description                                                                                                                                                                                                       |

|-----------------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S_MSCEXP_STATUS | 16    | IN     | MSC interrupt status input.                                                                                                                                                                                       |

|                 |       |        | Each bit 'N' is connected to a single MSC <n><br/>where N is 0-15. These are associated with<br/>the S_MSCEXP_STATUS[15:0] field in the<br/>SECMSCINTSTAT register.</n>                                           |

| S_MSCEXP_CLEAR  | 16    | OUT    | MSC interrupt clear output.                                                                                                                                                                                       |

|                 |       |        | Each bit 'N' is connected to a single MSC <n><br/>where N is 0-15. These are associated with<br/>the S_MSCEXP_CLR[15:0] field in the<br/>SECMSCINTCLR register.</n>                                               |

| NS_MSCEXP       | 16    | OUT    | MSC Non-secure configuration.                                                                                                                                                                                     |

|                 |       |        | Each bit 'N' is connected to a single MSC <n><br/>where N is 0-15. Set to HIGH to configure a<br/>master as Non-secure. These are associated<br/>with the NS_MSCEXP[15:0] field in the<br/>NSMSCECP register.</n> |

#### Table 9 MSC expansion interface

Bridge buffer error expansion

Some bridges in the system can contain write buffers. To avoid slowing down bus interfaces, buffered write access arriving at these bridges can be completed in advance without error. If any bus error occurs downstream, interrupts are used to notify the processor of the error.

The IoT Kit can support up to 16 extra bridges with buffer error signaling in the expansion system.

| Signal Name      | Width | IN/OUT | Description                                                                                                                                                         |

|------------------|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BRGEXP_STATUS 16 |       | IN     | Bridge Error Interrupt Status Input.                                                                                                                                |

|                  |       |        | Each bit 'N' is connected to a single bridge<br><n> where N is 0-15. These are associated<br/>with the BRGEXP_STATUS[15:0] field in the<br/>BRGINSTAT register.</n> |

| BRGEXP_CLEAR     | 16    | OUT    | Bridge Error Interrupt Clear Output.                                                                                                                                |

|                  |       |        | Each bit 'N' is connected to a single bridge<br><n> where N is 0-15. These are associated<br/>with the BRGEXP _CLR[15:0] field in the<br/>BRGINSTAT register.</n>   |

#### Table 10 Bridge error interrupt expansion interface

Other security expansion signals

The following table lists other signals that are related to security that are required by PPCs and MSCs in the expansion system.

| Signal Name  | Width | IN/OUT | Description                                                                          |

|--------------|-------|--------|--------------------------------------------------------------------------------------|

| SEC_RESP_CFG | 1     | OUT    | This signal configures how to respond to an access when a security violation occurs. |

|              |       |        | <ul><li>0 Read-Zero Write Ignore</li><li>1 Bus error</li></ul>                       |

|              |       |        | This signal is controlled by the SECRESPCFG register.                                |

Table 11 Other security expansion signals

## 3.2 Top-level system parameters

The following table lists all the parameters that are available at the top level of the IoT Kit subsystem for user configuration. These parameters are not directly visible to the FVP.

| Parameter                     | Default Values                                        | Description                                                                                                                                                                                        |

|-------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INITSVTOR0_RST[31:0]          | 0x1000_0000                                           | Reset value of the Secure vector table<br>offset address register in the System<br>Control Register.                                                                                               |

| INITNSVTOR0[31:0]             | 0×0000_0000                                           | Reset value of the Non-secure vector table offset address at the processor core.                                                                                                                   |

| CPU0WAIT_RST                  | 0                                                     | CPU wait at boot:                                                                                                                                                                                  |

|                               |                                                       | 0 Boot normally<br>1 Wait at boot.                                                                                                                                                                 |

| EXP_NUMIRQ                    | 64                                                    | Specifies the number of expansion interrupts.                                                                                                                                                      |

|                               |                                                       | Set to 64.                                                                                                                                                                                         |

|                               |                                                       | This means that the NVIC has 64+32 = 96 interrupts.                                                                                                                                                |

|                               |                                                       | Minimum value of 2.                                                                                                                                                                                |

|                               |                                                       | Note                                                                                                                                                                                               |

|                               |                                                       | The FPGA implementation<br>changes this value to 92.                                                                                                                                               |

| EXP_IRQ_DIS_0[EXP_NUMIRQ-1:0] | EXP_IRQ_DIS_0[EXP_N<br>UMIRQ-1:0] all set to<br>high. | Disables support for individual expansion<br>interrupts on the primary processor core,<br>enabling a range of non-contiguous<br>interrupts IRQDIS[i] = 1 indicates that<br>IRQ[i] is not present   |

| EXP_SYS_ID_PRESENT[31:16]     | 0xFFFF                                                | Each bit n of this vector defines if an AHB<br>master with HMASTERID = n exist in the<br>system. Bit 15 down to 0 are all IDs<br>reserved for internal use and not available<br>on this interface. |

| CPU0_FPU                      | 1                                                     | Floating Point Unit (FPU) is present on the processor                                                                                                                                              |

| CPU0_DSP                      | 1                                                     | Digital Signal Processing (DSP) extension instructions are included on the processor.                                                                                                              |

| CPU0_MPU_NS                   | 8                                                     | Number of Non-secure MPU entries on the processor                                                                                                                                                  |

| CPU0_MPU_S                    | 8                                                     | Number of Secure MPU entries on the processor                                                                                                                                                      |

| CPU0_SAU                      | 8                                                     | Number of SAU entries on the processor                                                                                                                                                             |

| CPU0_IRQ_LVL                  | 4                                                     | Number of interrupt priorities that are implemented in the NVIC, equal to $2^{CPU0\_IRQ\_LVL}$ .                                                                                                   |

|                               |                                                       | Supports 3-8 bits. Currently at four.                                                                                                                                                              |

|                               |                                                       | This provides 16 levels of interrupt priority.                                                                                                                                                     |

#### Table 12 Top-level user configurable parameters

## 3.3 System memory map

The following table shows the high-level view of the memory map of the IoT Kit subsystem. This memory map is divided into Secure and Non-secure regions. In general, the memory alternates between Secure and Non-secure regions in 256MB steps, with only a few address areas that are exempted from security mapping because they are related to debug functionality.

To provide memory and peripherals that can be mapped as Secure or Non-secure using software, several address regions are aliased as shown in the table. *The Implementation Defined Attribution Unit* (IDAU) region ID, and the *Non-secure Callable* (NSC) setting for each region are also shown in the table.

#### Note

For a row where the column **Alias with row ID** is not empty, the column indicates which other row entry it is aliased to in the memory map within the same table for that entry.

In general, except when stated, all access to unmapped regions of the memory results in a bus-error response. The exception to that is when accessing unmapped address space within a 4KB region of a peripheral area that did not result in a security violation, the access is Read Zero or Write Ignored (RZWI). Any accesses that result in security violations will either RZWI or result in a bus error response depending on the SECRESPCFG register setting.

Some regions of memory map are reserved to maintain compatibility as more features are added into future subsystem. Other areas are mapped to AHB Master expansion 0 interface and AHB Master expansion 1 interface.

| Row<br>ID | Address     | Size region | Description | Alias<br>with  | IDAU region values                                          |                   |                       |            |                          |

|-----------|-------------|-------------|-------------|----------------|-------------------------------------------------------------|-------------------|-----------------------|------------|--------------------------|

|           | From        | То          |             | name           |                                                             | with<br>row<br>ID | Security <sup>5</sup> | IDAU<br>ID | NSC                      |

| 1         | 0×0000_0000 | 0x0DFF_FFFF | 224MB       | Code<br>Memory | Maps to<br>AHB5<br>Master<br>expansion<br>code<br>interface | 3 <sup>6</sup>    | NS                    | 0          | 0                        |

| 2         | 0x0E00_0000 | 0x0FFF_FFFF | 32MB        | Reserved       | Reserved                                                    |                   |                       |            |                          |

| 3         | 0×1000_0000 | 0x1DFF_FFFF | 224MB       | Code<br>Memory | Maps to<br>AHB5<br>Master<br>expansion<br>code<br>interface | 1 <sup>2</sup>    | S                     | 1          | CODE<br>NSC <sup>7</sup> |

<sup>&</sup>lt;sup>5</sup> This column does not define privileged or unprivileged accessibility. These are defined by the MPC, PPC, or by the register blocks that are mapped to each area.

<sup>&</sup>lt;sup>6</sup> Even though they actually not aliased at the interface, these areas are expected to be aliased by customers for Non-secure and Secure shared code memory. In addition you should use Memory Protection Controller(s) externally to selectively map each block of memory between secure and non-secure memory regions.

<sup>&</sup>lt;sup>7</sup> The NSC values are currently defined in the FVP model using parameters only.

| 4  | 0x1E00_0000 | 0x1FFF_FFFF | 32MB  | Reserved           | Reserved                                              |    |    |   |             |

|----|-------------|-------------|-------|--------------------|-------------------------------------------------------|----|----|---|-------------|

| 5  | 0x2000_0000 | 0x20FF_FFFF | 16MB  | Internal<br>SRAM   | Internal<br>SRAM Area.                                | 8  | NS | 2 | 0           |

| 6  | 0x2100_0000 | 0x27FF_FFFF | 112MB | Reserved           | Reserved                                              |    |    |   |             |

| 7  | 0x2800_0000 | 0x2FFF_FFFF | 128MB | Expansion<br>0     | Maps to<br>AHB5<br>Master<br>expansion 0<br>interface |    |    |   |             |

| 8  | 0x3000_0000 | 0x30FF_FFFF | 16MB  | Internal<br>SRAM   | Internal<br>SRAM Area.                                | 5  | S  | 3 | RAMNS<br>C2 |

| 9  | 0x3100_0000 | 0x37FF_FFFF | 112MB | Reserved           | Reserved                                              | _  |    |   |             |

| 10 | 0x3800_0000 | 0x3FFF_FFFF | 128MB | Expansion<br>0     | Maps to<br>AHB5<br>Master<br>expansion 0<br>interface |    |    |   |             |

| 11 | 0x4000_0000 | 0x4000_FFFF | 64KB  | Base<br>peripheral | Base<br>element<br>peripheral<br>region.              |    | NS | 4 | 0           |

| 12 | 0x4001_0000 | 0x4001_FFFF | 64KB  | Private<br>CPU     | CPU<br>element<br>peripheral<br>region.               | 18 | _  |   |             |

| 13 | 0x4002_0000 | 0x4002_FFFF | 64KB  | System<br>Control  | System<br>Control<br>element<br>peripheral<br>region. | 19 |    |   |             |

| 14 | 0x4003_0000 | 0x4007_FFFF |       | Reserved           | Reserved                                              |    |    |   |             |

| 15 | 0x4008_0000 | 0x400F_FFFF | 512KB | Base<br>peripheral | Base<br>element<br>peripheral<br>region.              |    |    |   |             |

| 16 | 0x4010_0000 | 0x4FFF_FFFF | 255MB | Expansion<br>1     | Maps to<br>AHB5<br>Master<br>expansion 1<br>interface |    |    |   |             |

| 17 | 0x5000_0000 | 0x5000_FFFF | 64KB  | Base<br>peripheral | Base<br>element<br>peripheral<br>region.              |    | S  | 5 | 0           |

| 18 | 0x5001_0000 | 0x5001_FFFF | 64KB  | Private<br>CPU     | CPU<br>element<br>peripheral<br>region.               | 12 | _  |   |             |

| 19 | 0x5002_0000 | 0x5002_FFFF | 64KB  | System<br>Control  | System<br>Control<br>element<br>peripheral<br>region. | 13 | _  |   |             |

| 20 | 0x5003_0000 | 0x5007_FFFF |       | Reserved           | Reserved                                              |    | _  |   |             |

| 21 | 0x5008_0000 | 0x500F_FFFF | 512KB | Base<br>peripheral | Base<br>element<br>peripheral<br>region.              |    | _  |   |             |

| 22 | 0x5010_0000 | 0x5FFF_FFF  | 255MB | Expansion          | Maps to                                               |    |    |   |             |

Copyright © 2017 ARM Limited or its affiliates. All rights reserved.

|    |             |             |       |                 | Master<br>expansion 1<br>interface                    |        |   |   |  |

|----|-------------|-------------|-------|-----------------|-------------------------------------------------------|--------|---|---|--|

| 23 | 0x6000_0000 | 0x6FFF_FFFF | 256MB | Expansion<br>0  | Maps to<br>AHB5<br>Master<br>expansion 0<br>interface | NS     | 6 | 0 |  |

| 24 | 0x7000_0000 | 0x7FFF_FFFF | 256MB | Expansion<br>0  | Maps to<br>AHB5<br>Master<br>expansion 0<br>interface | S      | 7 | 0 |  |

| 25 | 0x8000_0000 | 0x8FFF_FFFF | 256MB | Expansion<br>1  | Maps to<br>AHB5<br>Master<br>expansion 1<br>interface | NS     | 8 | 0 |  |

| 26 | 0x9000_0000 | 0x9FFF_FFFF | 256MB | Expansion<br>1  | Maps to<br>AHB5<br>Master<br>expansion 1<br>interface | S      | 9 | 0 |  |

| 27 | 0xA000_0000 | 0xAFFF_FFFF | 256MB | Expansion<br>1  | Maps to<br>AHB5<br>Master<br>expansion 1<br>interface | NS     | A | 0 |  |

| 28 | 0xB000_0000 | 0xBFFF_FFFF | 256MB | Expansion<br>1  | Maps to<br>AHB5<br>Master<br>expansion 1<br>interface | S      | В | 0 |  |

| 29 | 0xC000_0000 | 0xCFFF_FFFF | 256MB | Expansion<br>1  | Maps to<br>AHB5<br>Master<br>expansion 1<br>interface | NS     | С | 0 |  |

| 30 | 0xD000_0000 | 0xDFFF_FFFF | 256MB | Expansion<br>1  | Maps to<br>AHB5<br>Master<br>expansion 1<br>interface | S      | D | 0 |  |

| 31 | 0×E000_0000 | 0XE00F_FFFF | 1MB   | PPB             | Private<br>peripheral<br>Bus. Local to<br>each core.  | Exempt |   |   |  |

| 32 | 0xE010_0000 | ØXEFFF_FFFF | 255MB | Expansion<br>1  | Maps to<br>AHB5<br>Master<br>expansion 1<br>interface | NS     | E | 0 |  |

| 33 | 0xF000_0000 | 0XF00F_FFFF | 1MB   | System<br>Debug | System<br>Debug.                                      | Exempt |   |   |  |

| 34 | 0xF010_0000 | 0XFFFF_FFFF | 255MB | Expansion<br>1  | Maps to<br>AHB5<br>Master<br>expansion 1<br>interface | S      | F | 0 |  |

#### Table 13 High-level system address map

#### Internal SRAM regions

The Internal SRAM regions are the location of SRAM within the subsystem. Currently, only a single SRAM is mapped into both the Secure and Non-secure regions. The remaining of the regions are reserved. An MPC then determines how the memory locations within the SRAM are mapped to the Secure and Non-secure regions.

| Row<br>ID | Address     | Address     |      | Region<br>Name | Description                     | Alias<br>with | Security <sup>8</sup> |

|-----------|-------------|-------------|------|----------------|---------------------------------|---------------|-----------------------|

|           | From        | То          |      | Name           |                                 | row ID        |                       |

| 1         | 0x2000_0000 | 0x2000_7FFF | 32KB | SRAM Bank<br>0 | Maps to internal<br>SRAM bank 0 | 3             | NS-MPC                |

| 2         | 0x2000_8000 | 0x20FF_FFFF |      | Reserved       | Reserved                        |               |                       |

| 3         | 0x3000_0000 | 0x3000_7FFF | 32KB | SRAM Bank<br>0 | Maps to internal SRAM bank 0    | 1             | S-MPC                 |

| 4         | 0x3000_8000 | 0x30FF_FFFF |      | Reserved       | Reserved                        |               |                       |

#### Table 14 SRAM region Address Map

#### Base peripheral regions

The Base peripheral regions are where the peripherals of the Base element are located. There are four regions in total, two Secure and two Non-secure regions. Some peripherals are aliased to both Secure and Non-secure regions.

The final mapping to both the Secure or Non-secure world, and privileged or Non-privileged world is determined by PPCs.

| Row<br>ID | Address<br>From | То          | Size | Region Name            | Description                               | Alias<br>with<br>row ID | Security <sup>9</sup> |

|-----------|-----------------|-------------|------|------------------------|-------------------------------------------|-------------------------|-----------------------|

| 1         | 0x4000_0000     | 0x4000_0FFF | 4KB  | Timer 0                | CMSDK timer                               | 8                       | NS-PPC                |

| 2         | 0x4000_1000     | 0x4000_1FFF | 4KB  | Timer 1                | CMSDK timer                               | 9                       | NS-PPC                |

| 3         | 0x4000_2000     | 0x4000_2FFF | 4KB  | Dual timer             | CMSDK Dual timer                          | 10                      | NS-PPC                |

| 4         | 0x4000_3000     | 0x4000_FFFF |      | Reserved               | Reserved                                  |                         |                       |

| 5         | 0x4008_0000     | 0x4008_0FFF | 4KB  | NSPCTRL                | Non-secure<br>privilege<br>Control block. |                         | NSP                   |

| 6         | 0x4008_1000     | 0x4008_1FFF | 4KB  | Non-secure<br>Watchdog | Non-secure<br>CMSDK<br>Watchdog           |                         | NSP                   |

| 7         | 0x4008_2000     | 0x400F_FFFF |      | Reserved               | Reserved                                  |                         |                       |

| 8         | 0x5000_0000     | 0x5000_0FFF | 4KB  | Timer 0                | CMSDK timer                               | 1                       | S-PPC                 |

| 9         | 0x5000_1000     | 0x5000_1FFF | 4KB  | Timer 1                | CMSDK timer                               | 2                       | S-PPC                 |

Copyright © 2017 ARM Limited or its affiliates. All rights reserved.

<sup>&</sup>lt;sup>8</sup> NS\_MPC: Non-secure access only gated by an MPC. S\_MPC: Secure access only gated by an MPC.

<sup>&</sup>lt;sup>9</sup> NS\_MPC: Non-secure access only gated by a PPC. S\_PPC: Secure access only gated by a PPC. NSP: Non-secure privilege access only. SP: Secure privilege access only.

| 10 | 0x5000_2000 | 0x5000_2FFF | 4KB | Dual timer         | CMSDK Dual<br>timer                           | 3 | S-PPC |

|----|-------------|-------------|-----|--------------------|-----------------------------------------------|---|-------|

| 11 | 0×5000_3000 | 0x5000_FFFF |     | Reserved           | Reserved                                      |   |       |

| 12 | 0x5008_0000 | 0x5008_0FFF | 4KB | SPCTRL             | Secure<br>privilege<br>Control block          |   |       |

| 13 | 0x5008_1000 | 0x5008_1FFF | 4KB | Secure<br>Watchdog | Secure CMSDK<br>Watchdog                      |   | SP    |

| 14 | 0x5008_2000 | 0x5008_2FFF |     | Reserved           | Reserved                                      |   |       |

| 15 | 0x5008_3000 | 0x5008_3FFF | 4KB | SRAM0MPC           | SRAM 0<br>Memory<br>Protection<br>Controller. |   | SP    |

| 16 | 0x5008_4000 | 0x500F_FFFF |     | Reserved           | Reserved                                      |   |       |

Table 15 Base peripheral regions Address Map

#### Private CPU region

The Private CPU region is privately visible to each processor element. If there are multiple processor elements in the subsystem, each only sees its own implementation of this region. Currently, there are no peripherals that are implemented within this block and this area is reserved for future use.

#### System control

The System control region is where peripherals in the System control element are located.

| Row<br>ID | Address<br>From | То          | Size | Region Name  | Description                                | Alias<br>with<br>row ID | Security <sup>10</sup> |

|-----------|-----------------|-------------|------|--------------|--------------------------------------------|-------------------------|------------------------|

| 1         | 0x4002_0000     | 0x4002_1FFF | 4KB  | SYSINFO      | System<br>Information<br>block.            | 4                       | NS                     |

|           | 0x4002_1000     | 0x4002_EFFF |      | Reserved     | Reserved                                   |                         |                        |

| 2         | 0x4002_F000     | 0x4001_FFFF | 4KB  | S32KTIMER    | CMSDK timer<br>running on<br>S32KCLK       | 6                       | NS-PPC                 |

| 3         | 0x5002_0000     | 0x5002_0FFF | 4KB  | SYSINFO      | System<br>information<br>block.            | 1                       | S                      |

| 4         | 0x5002_1000     | 0x5002_1FFF | 4KB  | SYSCONTROL   | System control block.                      | 1                       | SP                     |

|           | 0x5002_1000     | 0x5001_FFFF | -    | Reserved     | Reserved                                   | -                       | -                      |

| 5         | 0x5002_E000     | 0x5002_EFFF | 4KB  | S32KWATCHDOG | CMSDK<br>Watchdog<br>running on<br>S32KCLK |                         | SP                     |

| 6         | 0x5002_F000     | 0x5001_FFFF | 4KB  | S32KTIMER    | CMSDK timer<br>running on<br>S32KCLK       | 2                       | S-PPC                  |

#### Table 16 System control region address map

#### PPB region

The PPB memory region provides access to internal and external processor resources. This includes the following:

- The Instrumentation Trace Macrocell (ITM).

- The Data Watchpoint and Trace (DWT).

- The Flashpatch and Breakpoint (FPB).

- The System Control Space (SCS), including the Memory Protection Unit (MPU) and the Nested Vectored Interrupt Controller (NVIC).

<sup>&</sup>lt;sup>10</sup> NS\_MPC: Non-secure access only gated by a PPC. S\_PPC: Secure access only gated by a PPC. NSP: Non-secure privilege access only. SP: Secure privilege access only.

- The Embedded Trace Macrocell (ETM).

- Cross Trigger interface (CTI), if included.

- The Debug ROM table.

This region is as defined in the *ARMv8-M Architecture Reference Manual* and the *ARM Integration and Implementation Manual* for the processor.

Note

The FVP does not implement the ITM, ETM, or CTI.

System debug region

This region is reserved.

## 3.4 CPU element

The IoT Kit subsystem contains a single ARMv8-M processor core. It is configured with the following features:

| Parameter  | Configuration                                                            | Description                                                                                                                                                        |

|------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPU        | CPU0_FPU                                                                 | <i>Floating Point Unit</i> (FPU) is present.                                                                                                                       |

| DSP        | CPU0_DSP                                                                 | <i>Digital Signal Processing</i> (DSP) extension instructions are included.                                                                                        |

| SECEXT     | 1                                                                        | ARMv8-M Security Extension is included.                                                                                                                            |

| CPIF       | 0                                                                        | Coprocessor interface is not included.                                                                                                                             |

| MPU_NS     | CPU0_MPU_NS                                                              | 8 Non-secure <i>Memory</i><br><i>Protection Unit</i> (MPU) regions<br>included.                                                                                    |

| MPU_S      | CPU0_MPU_S                                                               | 8 Secure MPU regions<br>included.                                                                                                                                  |

| SAU        | CPU0_SAU                                                                 | 8 Secure Attribution Unit (SAU) regions included                                                                                                                   |

| NUMIRQ     | EXP_NUMIRQ + 32                                                          | Number of user interrupts implemented.                                                                                                                             |

| IRQLVL     | CPU0_IRQ_LVL                                                             | Defines the number of bits of interrupt priority that is implemented in the NVIC, which therefore provides 2 <sup>CPU0_IRQ_LVL</sup> levels of interrupt priority. |

| IRQLATENCY | All Zeros                                                                | Set all interrupts to not low latency.                                                                                                                             |

| IRQDIS     | IRQDIS[31:0] = 0x38F<br>IRQDIS[95:32] =<br>EXP_IRQ_DIS_0[EXP_NUMIRQ-1:0] | Disable support for individual interrupt.                                                                                                                          |

| DBGLVL     | 2                                                                        | Full debug resources included,<br>which includes four watchpoint<br>and eight breakpoint<br>comparators                                                            |

| ITM        | 1                                                                        | DWT and ITM instrumentation trace supported                                                                                                                        |

| ETM        | 1                                                                        | ETM Trace included.                                                                                                                                                |

| МТВ        | 0                                                                        | MTB trace not included                                                                                                                                             |

| MTBWIDTH   | 12                                                                       | 12 bits MTB RAM interface address width. But not used.                                                                                                             |

Copyright © 2017 ARM Limited or its affiliates. All rights reserved.

| WIC      | 1               | WIC included                                   |

|----------|-----------------|------------------------------------------------|

| WICLINES | EXP_NUMIRQ + 35 | All interrupts are sensitive to WIC.           |

| СТІ      | 0               | CTI not included                               |

| RAR      | 1               | Only reset the architecturally required state. |

#### Table 17 IoT Kit subsystem processor configuration settings

The processor has several static configuration input signals. These are tied as shown in the following table.

| Signal Name        | Tie Value  | Description                                                                                                                                                                                              |

|--------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CFGBIGEND          | 0          | Little-endian data endianness.                                                                                                                                                                           |

| CFGSSTCALIB[25:0]  | 0x200_0000 | Secure SysTick calibration configuration<br>indicating that no alternative reference<br>clock is provided, and the frequency of<br>clock arriving at the processor is not<br>computable in hardware.     |

| CFGSSTCALIB[23:0]  | TENMS      | = 0x00_0000                                                                                                                                                                                              |

| CFGSSTCALIB[24]    | SKEW       | = LOW                                                                                                                                                                                                    |

| CFGSSTCALIB[25]    | NOREF      | = HIGH                                                                                                                                                                                                   |

| CFGNSSTCALIB[25:0] | 0x200_0000 | Non-secure SysTick calibration<br>configuration indicating that no alternative<br>reference clock is provided, and the<br>frequency of clock arriving at the<br>processor is not computable in hardware. |

| CFGNSSTCALIB[23:0] | TENMS      | = 0×00_0000                                                                                                                                                                                              |

| CFGNSSTCALIB[24]   | SKEW       | = LOW                                                                                                                                                                                                    |

| CFGNSSTCALIB[25]   | NOREF      | = HIGH                                                                                                                                                                                                   |

| CFGFPU             | 1          | CFGFPU hardware support enabled.                                                                                                                                                                         |

| CFGDSP             | 1          | CFGDSP hardware support enabled.                                                                                                                                                                         |

| CFGSECEXT          | 1          | ARMv8-M security support enabled.                                                                                                                                                                        |

| MPUNSDISABLE       | 0          | Disable support for the Non-secure MPU not enabled.                                                                                                                                                      |

| MPUSDISABLE        | 0          | Disable support for the Secure MPU not enabled.                                                                                                                                                          |

| SAUDISABLE         | 0          | Disable support for the SAU not enabled.                                                                                                                                                                 |

|                    | Table 18   |                                                                                                                                                                                                          |

#### Table 18

#### IoT Kit subsystem processor static configuration input signals settings

The CPU element also integrates the *Debug Access Port* (DAP) and the *Trace Port interface Unit* (TPIU) that is provided with the processor. Their respective JTAG and Trace interfaces are available as the interfaces on the top level of the IoT subsystem.

Both Code and System AHB interfaces are connected to the AHB5 interconnect in the Base element.

Note

The FVP does not implement DAP or TPIU.

#### CPU\_IDENTITY

The CPU element also implements a CPU\_IDENTITY register block that is only visible to accesses on the system interface from the processor.

This base address of this register is 0x4001\_F000 in a Non-secure region and 0x5001\_F000 in the Secure region. Both areas are always read accessible. Write accesses to this register block are always ignored.

#### Note

In the single processor system as defined in this document, CPU\_IDENTITY is not needed. Therefore this register block is not implemented in this IoT Kit subsystem and reserved. Access to this register block results in a bus error response, or RAZ/WI in the FVP.

## 3.5 Base element

The Base element integrates the following CoreLink SDK-200 components:

- AHB5 interconnect.

- Memory Protection Controllers (MPCs).

- AHB5 to APB bus converters

- APB Peripheral Protection Controller (PPC)

- Exclusive Access Monitors (EAM)

- Timers and Dual timers.

- Watchdogs

The IoT Kit subsystem also includes a security controller that is unique to the subsystem.