# ARM7DI

## **Data Sheet**

Document Number: ARM DDI 0027D

Issued: Dec 1994

Copyright Advanced RISC Machines Ltd (ARM) 1994

All rights reserved

#### **Proprietary Notice**

ARM, the ARM Powered logo, BlackICE and ICEbreaker are trademarks of Advanced RISC Machines Ltd.

Neither the whole nor any part of the information contained in, or the product described in, this datasheet may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this datasheet is subject to continuous developments and improvements. All particulars of the product and its use contained in this datasheet are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties or merchantability, or fitness for purpose, are excluded.

This datasheet is intended only to assist the reader in the use of the product. ARM Ltd shall not be liable for any loss or damage arising from the use of any information in this datasheet, or any error or omission in such information, or any incorrect use of the product.

#### **Change Log**

| Issue | Date      | Ву  | Change                                                                                              |

|-------|-----------|-----|-----------------------------------------------------------------------------------------------------|

| A     | July 1994 | EH  | Created. Updated Instruction Cycle Operations Sources repaired: no material changes to text Edited. |

| B     | Aug 94    | BJH |                                                                                                     |

| C     | Oct 94    | EH  |                                                                                                     |

| D     | Dec 94    | PB  |                                                                                                     |

#### **Preface**

The ARM7DI is a low-power, general purpose 32-bit RISC microprocessor with integrated debug support. It comprises the ARM7D CPU core, and ICEbreaker module and a TAP controller. Its simple, elegant and fully static design is particularly suitable for cost and power sensitive applications.

#### **Enhancements**

The ARM7DI is similar to the ARM6 but with the following enhancements:

- advanced debug (integrated ICE) support for faster time to market

- fabrication on a sub-micron process for increased speed and reduced power consumption

- 3V operation, for very low power consumption, as well as 5V operation for system compatibility

- higher clock speedfor faster program execution.

#### **Feature Summary**

- 32-bit RISC processor (32-bit data & address bus)

- Advanced debug fully integrated ICE

- Big and Little Endian operating modes

- High performance RISC

- Low power consumption

- Fully static operation ideal for power-sensitive applications

- Fast interrupt response for real-time applications

- Virtual Memory System Support

- Excellent high-level language support

- Simple but powerful instruction set

#### **Applications**

The ARM7DI is ideally suited to those applications requiring RISC performance from a compact, power-efficient processor. These include:

Telecomms GSM terminal controller

Datacomms Protocol conversion

Palmtop computer

Portable InstrumentS Handheld data acquisition unit

Automotive Engine management unit

Information SystemsSmart cardsImagingJPEG controller

iv ARM7DI Data Sheet

## **Table of Contents**

| 1.0        | Intro       | oduction                                                 | 5        |

|------------|-------------|----------------------------------------------------------|----------|

|            | 1.1         | ARM7DI Block Diagram                                     | 6        |

|            | 1.2         | ARM7D Core Diagram                                       | 7        |

|            | 1.3         | ARM7DI Functional Diagram                                | 8        |

| 2.0        | Sign        | al Description                                           | 9        |

| 3.0        | Prog        | grammer's Model                                          | 15       |

|            | 3.1         | Hardware Configuration Signals                           | 15       |

|            | 3.2         | Operating Mode Selection                                 | 16       |

|            | 3.3         | Registers                                                | 17       |

|            | 3.4         | Exceptions                                               | 20       |

|            | 3.5         | Reset                                                    | 24       |

| 4.0        | Insti       | ruction Set                                              | 25       |

|            | 4.1         | Instruction Set Summary                                  | 25       |

|            | 4.2         | The Condition Field                                      | 26       |

|            | 4.3         | Branch and Branch with link (B, BL)                      | 27       |

|            | 4.4         | Data processing                                          | 29       |

|            | 4.5         | PSR Transfer (MRS, MSR)                                  | 36       |

|            | 4.6         | Multiply and Multiply-Accumulate (MUL, MLA)              | 40       |

|            | 4.7         | Single data transfer (LDR, STR)                          | 42       |

|            | 4.8<br>4.9  | Block Data Transfer (LDM, STM)<br>Single data swap (SWP) | 48<br>55 |

|            | 4.9<br>4.10 | Software interrupt (SWI)                                 | 57       |

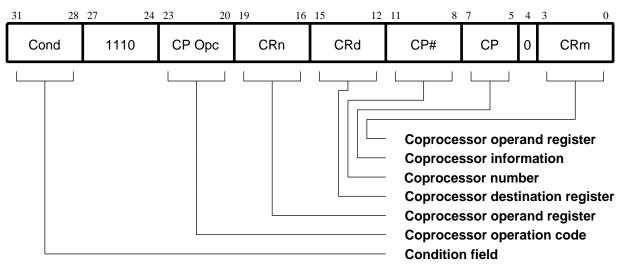

|            | 4.11        | Coprocessor data operations (CDP)                        | 59       |

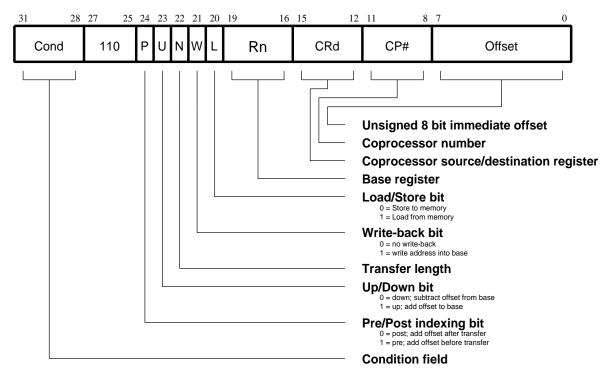

|            | 4.12        | Coprocessor data transfers (LDC, STC)                    | 61       |

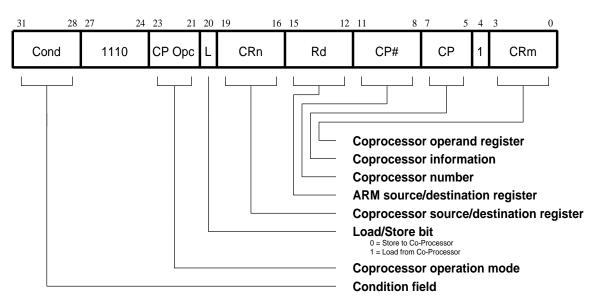

|            | 4.13        | Coprocessor register transfers (MRC, MCR)                | 64       |

|            | 4.14        | Undefined instruction                                    | 66       |

|            | 4.15        | Instruction Set Examples                                 | 67       |

| <b>5.0</b> | Men         | nory Interface                                           | 71       |

|            | 5.1         | Cycle types                                              | 71       |

|            | 5.2         | Byte addressing                                          | 72       |

|            | 5.3         | Address timing                                           | 74       |

|            | 5.4         | Memory management                                        | 74       |

|            | 5.5         | Locked operations                                        | 75<br>75 |

|            | 5.6<br>5.7  | Stretching access times The External Data Bus            | 75<br>76 |

| 6.0        |             | rocessor Interface                                       | 81       |

| 0.0        | 6.1         | Interface signals                                        | 81       |

|            | 6.2         | Data transfer cycles                                     | 82       |

|            | 6.3         | Register transfer cycle                                  | 82       |

|            | 6.4         | Privileged instructions                                  | 82       |

|            | 6.5         | Idempotency                                              | 83       |

|            | 6.6         | Undefined instructions                                   | 83       |

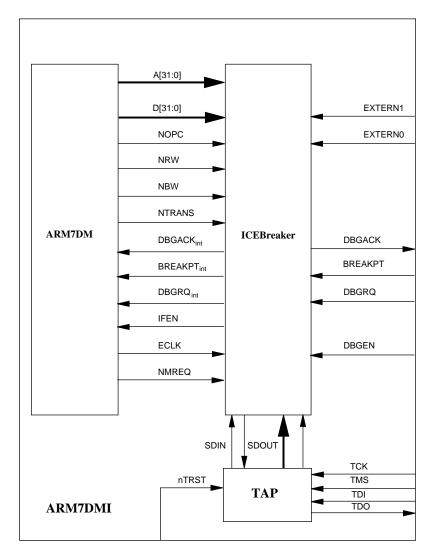

| 7.0        |             | oug Interface                                            | 85       |

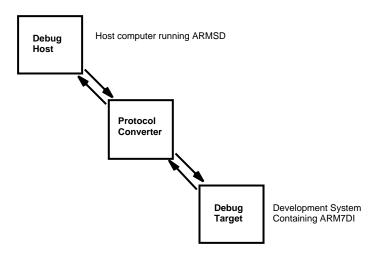

|            | 7.1         | Overview                                                 | 85       |

|            | 7.2         | Debug Systems                                            | 85       |

|            | 7.3         | Debug Interface Signals                                  | 86       |

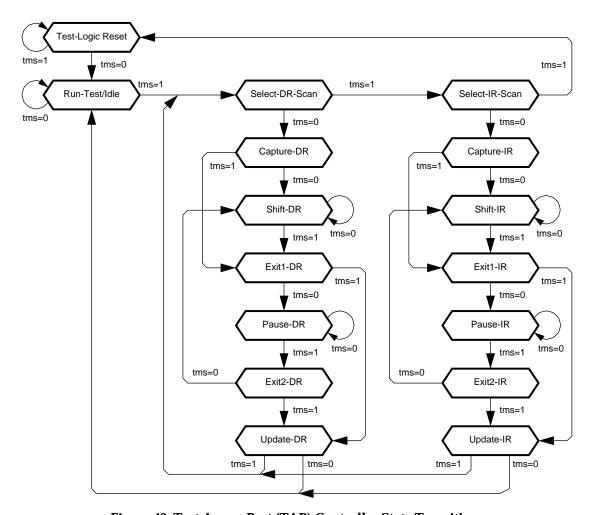

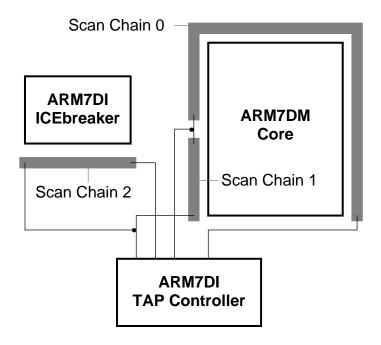

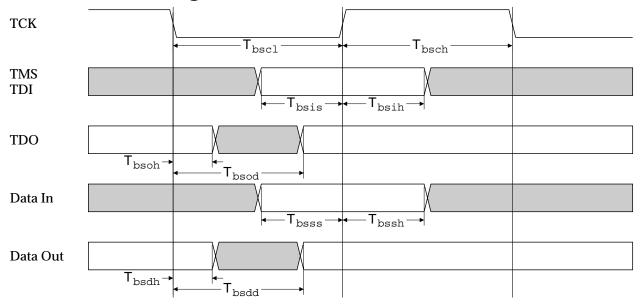

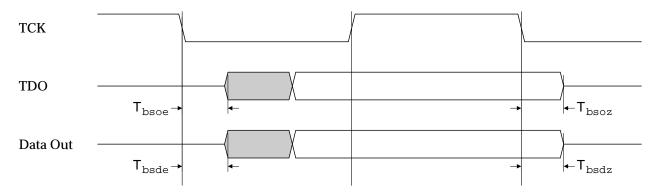

|      | 7.4   | Scan Chains and JTAG Interface                         | 89  |

|------|-------|--------------------------------------------------------|-----|

|      | 7.5   | Reset                                                  | 91  |

|      | 7.6   | Pullup Resistors                                       | 91  |

|      | 7.7   | Instruction Register                                   | 92  |

|      | 7.8   | Public Instructions                                    | 92  |

|      | 7.9   | Test Data Registers                                    | 94  |

|      | 7.10  | ARM7DI Core Clocks                                     | 99  |

|      | 7.11  | Determining the Core and System State                  | 100 |

|      | 7.12  | The PC's Behaviour During Debug                        | 103 |

|      | 7.13  | Priorities / Exceptions                                | 105 |

|      | 7.14  | Scan Interface Signals                                 | 106 |

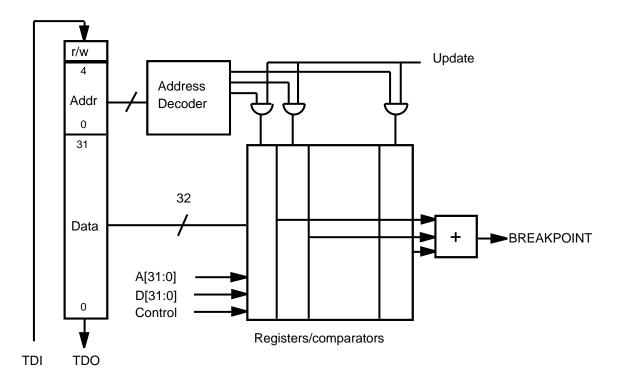

| 8.0  | The . | ARM7DI ICEBreaker Module                               | 109 |

|      | 8.1   | The Watchpoint Registers                               | 110 |

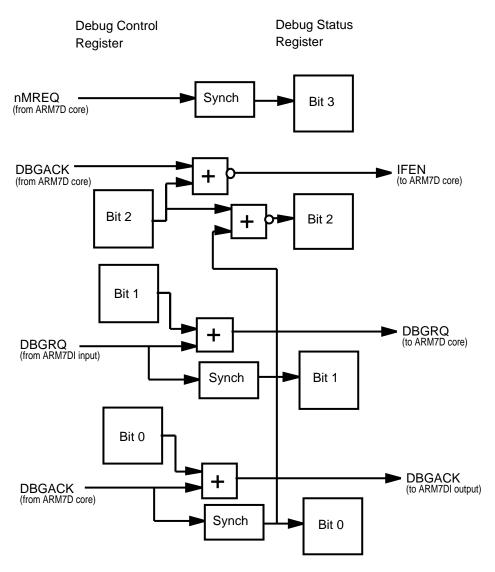

|      | 8.2   | The Debug Control Register                             | 115 |

|      | 8.3   | Debug Status Register                                  | 116 |

|      | 8.4   | Coupling Breakpoints and Watchpoints                   | 119 |

|      | 8.5   | Disabling ICEbreaker                                   | 120 |

|      | 8.6   | ICEbreaker Timing                                      | 120 |

|      | 8.7   | ICEBreaker Programming Restriction                     | 120 |

| 9.0  | Instr | uction Cycle Operations                                | 121 |

|      | 9.1   | Branch and branch with link                            | 121 |

|      | 9.2   | Data Operations                                        | 121 |

|      | 9.3   | Multiply and multiply accumulate                       | 123 |

|      | 9.4   | Load register                                          | 123 |

|      | 9.5   | Store register                                         | 124 |

|      | 9.6   | Load multiple registers                                | 125 |

|      | 9.7   | Store multiple registers                               | 127 |

|      | 9.8   | Data swap                                              | 127 |

|      | 9.9   | Software interrupt and exception entry                 | 128 |

|      | 9.10  | Coprocessor data operation                             | 129 |

|      | 9.11  | Coprocessor data transfer (from memory to coprocessor) | 129 |

|      | 9.12  | Coprocessor data transfer (from coprocessor to memory) | 131 |

|      | 9.13  | Coprocessor register transfer (Load from coprocessor)  | 132 |

|      | 9.14  | Coprocessor register transfer (Store to coprocessor)   | 132 |

|      | 9.15  | Undefined instructions and coprocessor absent          | 133 |

|      | 9.16  | Unexecuted instructions                                | 134 |

|      | 9.17  | Instruction Speed Summary                              | 134 |

| 10.0 | DC I  | Parameters                                             | 137 |

|      | 10.1  | Absolute Maximum Ratings                               | 137 |

|      | 10.2  | DC Operating Conditions:                               | 137 |

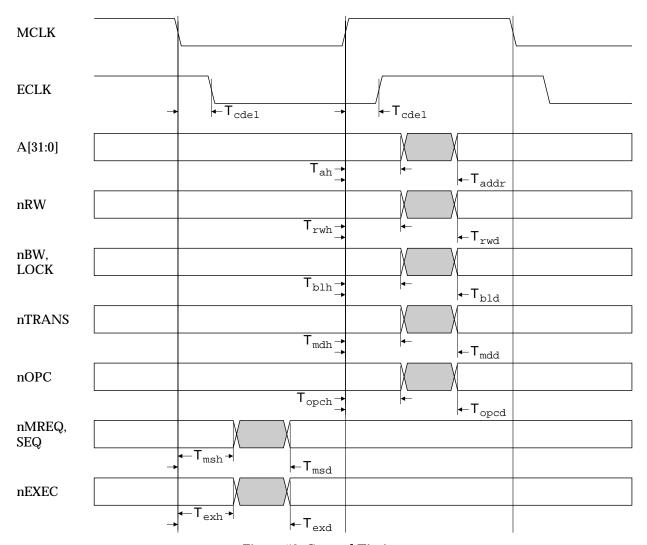

| 11.0 | AC F  | Parameters                                             | 139 |

| 12.0 | App   | endix - Backward Compatibility                         | 149 |

#### 1.0 Introduction

The ARM7DI is part of the Advanced RISC Machines (ARM) family of general purpose 32-bit microprocessors, which offer very low power consumption and price for high performance devices. The architecture is based on Reduced Instruction Set Computer (RISC) principles, and the instruction set and related decode mechanism are much simpler in comparison with microprogrammed Complex Instruction Set Computers. This results in a high instruction throughput and impressive real-time interrupt response from a small and cost-effective chip.

The instruction set comprises eleven basic instruction types:

- Two of these make use of the on-chip arithmetic logic unit, barrel shifter and multiplier to perform high-speed operations on the data in a bank of 31 registers, each 32 bits wide;

- Three classes of instruction control data transfer between memory and the registers, one optimised for flexibility of addressing, another for rapid context switching and the third for swapping data;

- Three instructions control the flow and privilege level of execution; and

- Three types are dedicated to the control of external coprocessors which allow the functionality of the instruction set to be extended off-chip in an open and uniform way.

The ARM instruction set is a good target for compilers of many different high-level languages. Where required for critical code segments, assembly code programming is also straightforward, unlike some RISC processors which depend on sophisticated compiler technology to manage complicated instruction interdependencies.

Pipelining is employed so that all parts of the processing and memory systems can operate continuously. Typically, while one instruction is being executed, its successor is being decoded, and a third instruction is being fetched from memory.

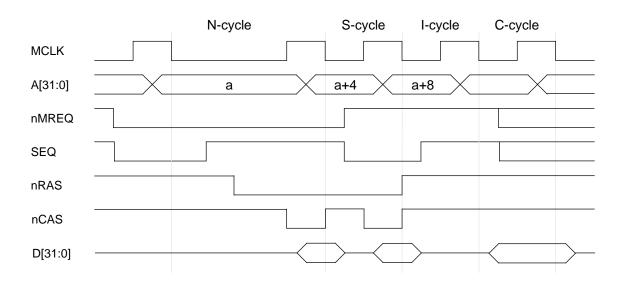

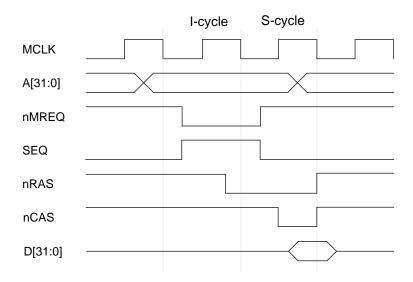

The memory interface has been designed to allow the performance potential to be realised without incurring high costs in the memory system. Speed critical control signals are pipelined to allow system control functions to be implemented in standard low-power logic, and these control signals facilitate the exploitation of the fast local access modes offered by industry standard dynamic RAMs.

ARM7DI has a 32 bit address bus. All ARM processors share the same instruction set, and ARM7DI can be configured to use a 26 bit address bus for backwards compatibility with earlier processors.

ARM7DI is a fully static CMOS implementation of the ARM which allows the clock to be stopped in any part of the cycle with extremely low residual power consumption and no loss of state.

#### **Notation:**

0x - marks a Hexadecimal quantity

**BOLD** - external signals are shown in bold capital letters

- where it is not clear that a quantity is binary it is followed by the word binary

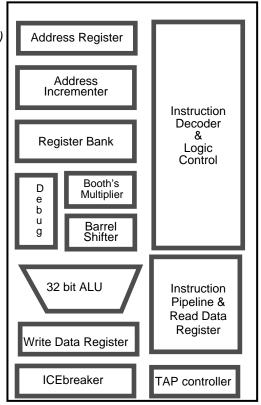

### 1.1 ARM7DI Block Diagram

Figure 1: ARM7DI Block Diagram

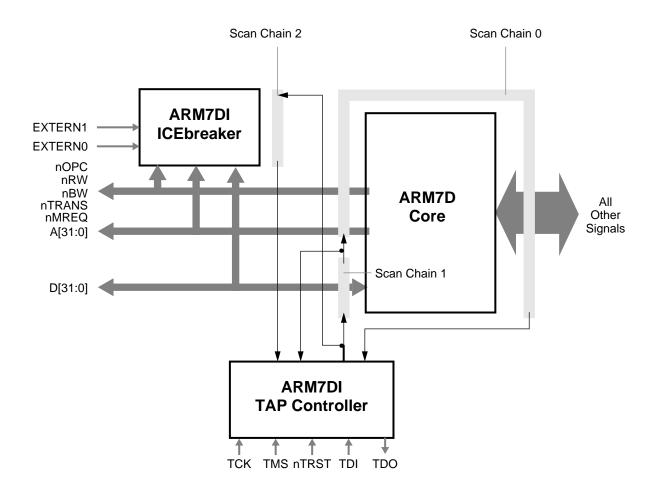

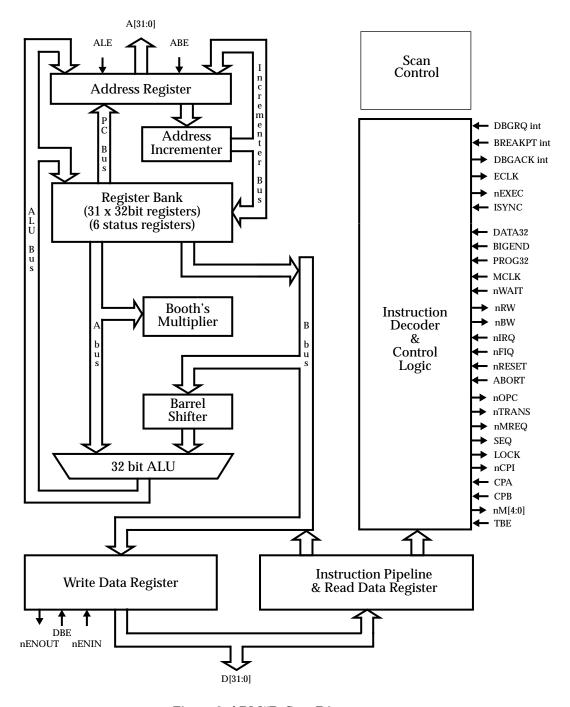

#### 1.2 ARM7D Core Diagram

Figure 2: ARM7D Core Diagram

#### 1.3 ARM7DI Functional Diagram MCLK TCK nWAIT Clocks **TMS ECLK** Boundary TDI Scan PROG32 nTRST DATA32 TDO Configuration **BIGEND** Processor nM[4:0] Mode nIRQ nFIQ Interrupts **ISYNC** A[31:0] nRESET **ARM7DI** nENIN D[31:0] nENOUT Memory Bus ABE nMREQ Interface Controls **SEQ** ALE nRW DBE nBW **TBE** LOCK VDD Power VSS Memory nTRANS Management **DBGRQ ABORT** Interface **BREAKPT** Debug DBGACK nOPC nEXEC nCPI Coprocessor **EXTERN 1** CPA Interface **EXTERN 0** CPB **DBGEN**

Figure 3: ARM7DI Functional Diagram

## 2.0 Signal Description

| Name    | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[31:0] | O8   | Addresses. This is the processor address bus. If <b>ALE</b> (address latch enable) is HIGH, the addresses become valid during phase 2 of the cycle before the one to which they refer and remain so during phase 1 of the referenced cycle. Their stable period may be controlled by <b>ALE</b> as described below.                                                                                                                                                                                                                                                                                                                                 |

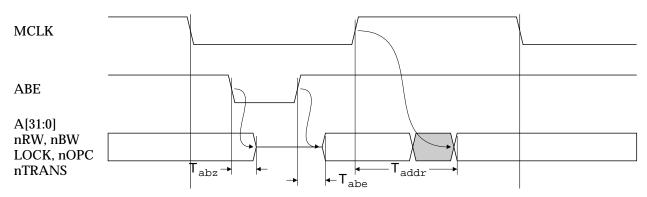

| ABE     | IC   | Address bus enable. This is an input signal which, when LOW, puts the address bus drivers into a high impedance state. This signal has a similar effect on the following control signals: nBW, nRW, LOCK, nOPC and nTRANS. ABE must be tied HIGH when there is no system requirement to turn off the address drivers.                                                                                                                                                                                                                                                                                                                               |

| ABORT   | IC   | Memory Abort. This is an input which allows the memory system to tell the processor that a requested access is not allowed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

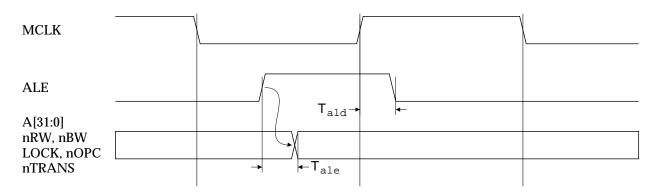

| ALE     | IC   | Address latch enable. This input is used to control transparent latches on the address outputs. Normally the addresses change during phase 2 to the value required during the next cycle, but for direct interfacing to ROMs they are required to be stable to the end of phase 2. Taking ALE LOW until the end of phase 2 will ensure that this happens. This signal has a similar effect on the following control signals: nBW, nRW, LOCK, nOPC and nTRANS. If the system does not require address lines to be held in this way, ALE must be tied HIGH. The address latch is static, so ALE may be held LOW for long periods to freeze addresses. |

| BIGEND  | IC   | Big Endian configuration. When this signal is HIGH the processor treats bytes in memory as being in Big Endian format. When it is LOW memory is treated as Little Endian. ARM processors which do not have selectable Endianism (ARM2, ARM2aS, ARM3, ARM61) are Little Endian.                                                                                                                                                                                                                                                                                                                                                                      |

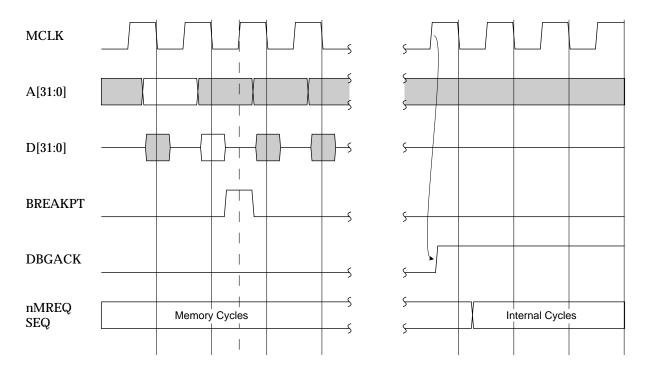

| BREAKPT | IC   | Breakpoint. This signal allows external hardware to halt the execution of the processor for debug purposes. When HIGH causes the current memory access to be breakpointed. If the memory access is an instruction fetch, ARM7DI will enter debug state if the instruction reaches the execute stage of the ARM7DI pipeline. If the memory access is for data, ARM7DI will enter debug state after the current instruction completes execution. This allows extension of the internal breakpoints provided by the ICEBreaker module. See <i>Chapter 8.0 The ARM7DI ICEBreaker Module</i> .                                                           |

| СРА     | IC   | Coprocessor absent. A coprocessor which is capable of performing the operation that ARM7DI is requesting (by asserting <b>nCPI</b> ) should take <b>CPA</b> LOW immediately. If <b>CPA</b> is HIGH at the end of phase 1 of the cycle in which <b>nCPI</b> went LOW, ARM7DI will abort the coprocessor handshake and take the undefined instruction trap. If <b>CPA</b> is LOW and remains LOW, ARM7DI will busy-wait until <b>CPB</b> is LOW and then complete the coprocessor instruction.                                                                                                                                                        |

Table 1: Signal Description

| Name    | Type  | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СРВ     | IC    | Coprocessor busy. A coprocessor which is capable of performing the operation which ARM7DI is requesting (by asserting nCPI), but cannot commit to starting it immediately, should indicate this by driving CPB HIGH. When the coprocessor is ready to start it should take CPB LOW. ARM7DI samples CPB at the end of phase 1 of each cycle in which nCPI is LOW.                                                                     |

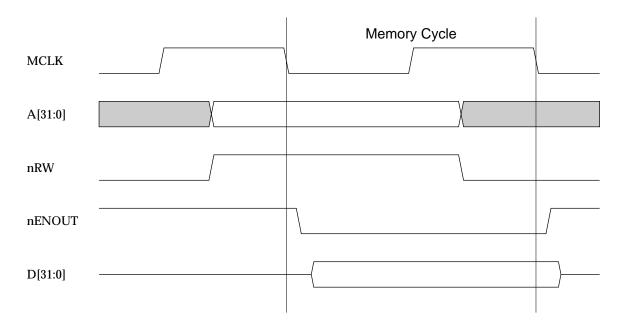

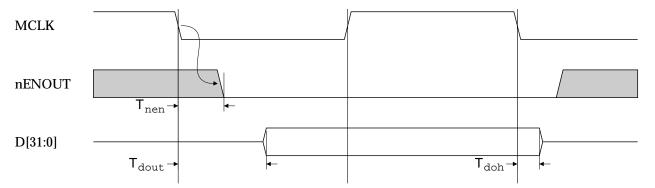

| D[31:0] | IC/O8 | Data Bus. These are bidirectional signal paths which are used for data transfers between the processor and external memory. During read cycles (when <b>nRW</b> is LOW), the input data must be valid before the end of phase 2 of the transfer cycle. During write cycles (when <b>nRW</b> is HIGH), the output data will become valid during phase 1 and remain valid throughout phase 2 of the transfer cycle.                    |

| DATA32  | IC    | 32 bit Data configuration. When this signal is HIGH the processor can access data in a 32 bit address space using address lines A[31:0]. When it is LOW the processor can access data from a 26 bit address space using A[25:0]. In this latter configuration the address lines A[31:26] are not used. Before changing DATA32, ensure that the processor is not about to access an address greater that 0x3FFFFFF in the next cycle. |

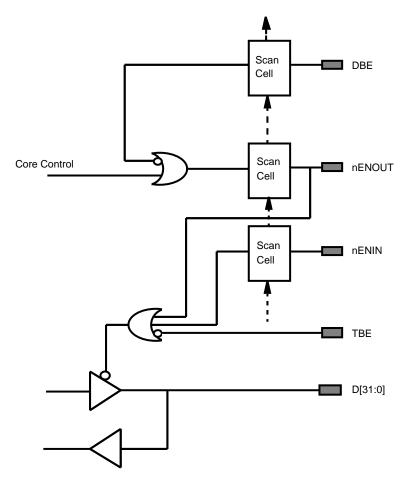

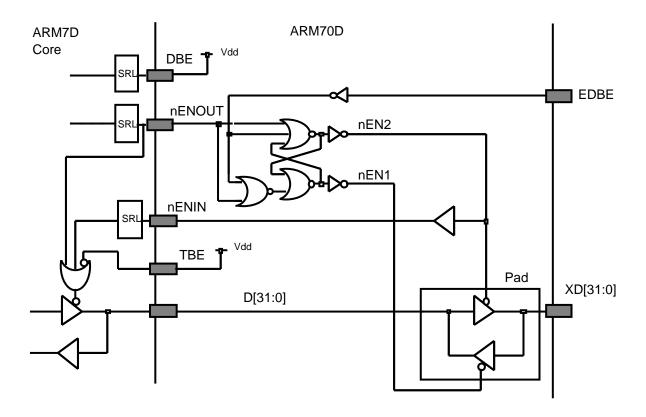

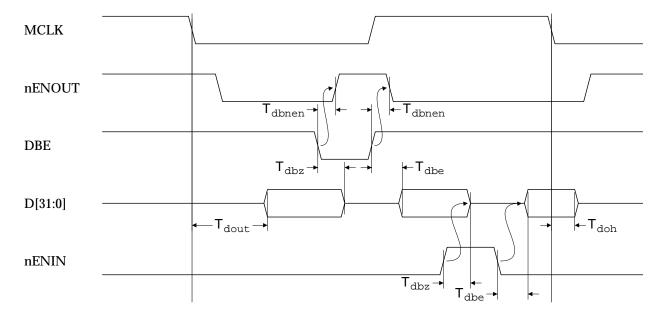

| DBE     | IC    | Internal Data Bus Enable. This is an input signal which, when driven LOW, puts the internal data bus (the bus between the core logic and the pads) into the high impedance state. This is included for test purposes, and should be tied HIGH at all times.                                                                                                                                                                          |

| DBGACK  | O4    | Debug acknowledge. When HIGH indicates ARM is in debug state.                                                                                                                                                                                                                                                                                                                                                                        |

| DBGEN   | IC    | Debug Enable. This input signal allows the debug features of ARM7DI to be disabled. This signal should be driven LOW when debugging is not required.                                                                                                                                                                                                                                                                                 |

| DBGRQ   | IC    | Debug request. This is a level-sensitive input, which when HIGH causes ARM7DI to enter debug state after executing the current instruction. This allows external hardware to force ARM7DI into the debug state, in addition to the debugging features provided by the ICEBreaker block. See <i>Chapter 8.0 The ARM7DI ICEBreaker Module</i> for details.                                                                             |

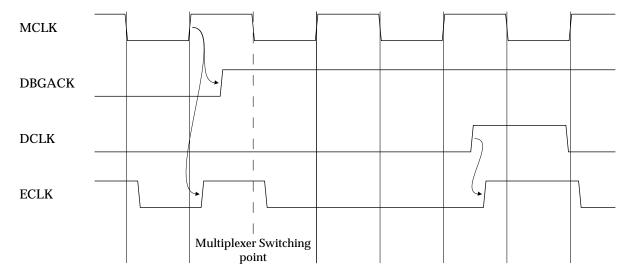

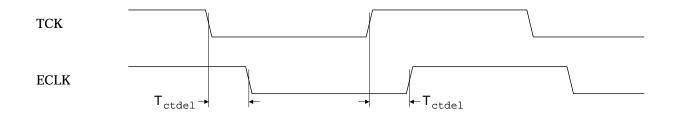

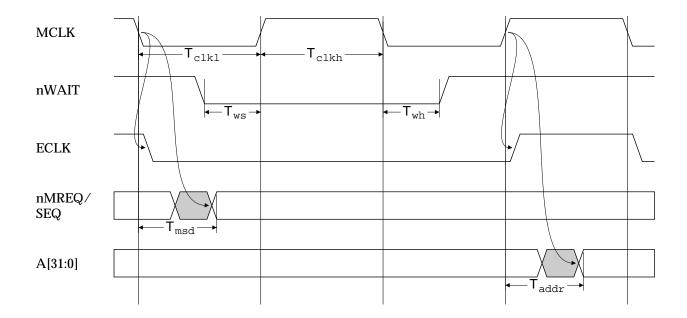

| ECLK    | O4    | External clock output. In normal operation, this is simply MCLK (optionally stretched with nWAIT) exported from the core. When the core is being debugged, this is DCLK. This allows external hardware to track when the ARM7DI core is clocked.                                                                                                                                                                                     |

| EXTERN1 | IC    | External input 1. This is an input to the ICEBreaker logic in the ARM7DI which allows breakpoints and/or watchpoints to be dependent on an external condition.                                                                                                                                                                                                                                                                       |

| EXTERN0 | IC    | External input 0. This is an input to the ICEBreaker logic in the ARM7DI which allows breakpoints and/or watchpoints to be dependent on an external condition.                                                                                                                                                                                                                                                                       |

| HIGHZ   | O4    | This signal denotes that the HIGHZ instruction has been loaded into the TAP controller. See <i>Chapter 7.0 Debug Interface</i> for details.                                                                                                                                                                                                                                                                                          |

**Table 1: Signal Description (Continued)**

## **Signal Description**

| Name   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISYNC  | IC   | Synchronous interrupts. When LOW indicates that the <b>nIRQ</b> and <b>nFIQ</b> inputs are to be synchronised by the ARM core. When HIGH disables this synchronisation for inputs that are already synchronous.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| LOCK   | O8   | Locked operation. When LOCK is HIGH, the processor is performing a "locked" memory access, and the memory controller must wait until LOCK goes LOW before allowing another device to access the memory. LOCK changes while MCLK is HIGH, and remains HIGH for the duration of the locked memory accesses. It is active only during the data swap (SWP) instruction. The timing of this signal may be modified by the use of ALE in a similar way to the address, please refer to the ALE description. This signal may also be driven to a high impedance state by driving ABE LOW.                                                                                                          |

| MCLK   | IC   | Memory clock input. This clock times all ARM7DI memory accesses and internal operations. The clock has two distinct phases - phase 1 in which MCLK is LOW and phase 2 in which MCLK (and nWAIT) is HIGH. The clock may be stretched indefinitely in either phase to allow access to slow peripherals or memory. Alternatively, the nWAIT input may be used with a free running MCLK to achieve the same effect.                                                                                                                                                                                                                                                                             |

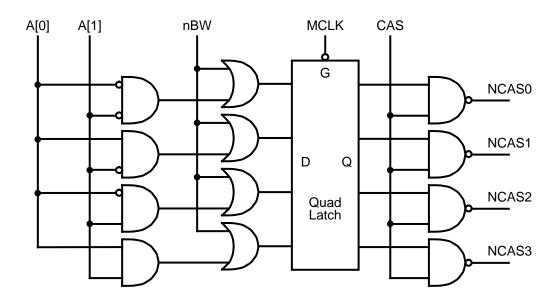

| nBW    | O8   | Not byte/word. This is an output signal used by the processor to indicate to the external memory system when a data transfer of a byte length is required. The signal is HIGH for word transfers and LOW for byte transfers and is valid for both read and write cycles. The signal will become valid during phase 2 of the cycle before the one in which the transfer will take place. It will remain stable throughout phase 1 of the transfer cycle. The timing of this signal may be modified by the use of <b>ALE</b> in a similar way to the address, please refer to the <b>ALE</b> description. This signal may also be driven to a high impedance state by driving <b>ABE</b> LOW. |

| nCPI   | O4   | Not Coprocessor instruction. When ARM7DI executes a coprocessor instruction, it will take this output LOW and wait for a response from the coprocessor. The action taken will depend on this response, which the coprocessor signals on the <b>CPA</b> and <b>CPB</b> inputs.                                                                                                                                                                                                                                                                                                                                                                                                               |

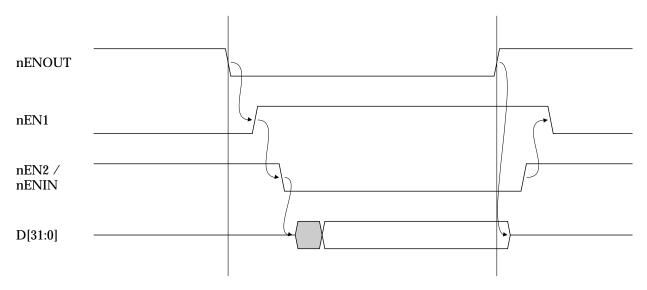

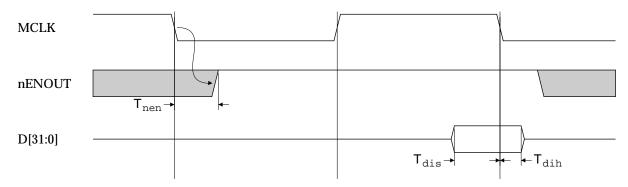

| nENIN  | IC   | NOT enable input. This signal may be used in conjunction with <b>nENOUT</b> to control the data bus during write cycles. See <i>Chapter 5.0 Memory Interface</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| nENOUT | O4   | Not enable output. During a data write cycle, this signal is driven low during phase 1, and remains low for the entire cycle. This may be used to aid arbitration in shared bus applications. See <i>Chapter 5.0 Memory Interface</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| nEXEC  | O4   | Not executed. When HIGH indicates that the instruction in the execution unit is not being executed, because for example it has failed its condition code check.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| nFIQ   | IC   | Not fast interrupt request. This is an interrupt request to the processor which causes it to be interrupted if taken LOW when the appropriate enable in the processor is active. The signal is level-sensitive and must be held LOW until a suitable response is received from the processor. <b>nFIQ</b> may be synchronous or asynchronous, depending on the state of <b>ISYNC</b> .                                                                                                                                                                                                                                                                                                      |

Table 1: Signal Description (Continued)

| Name    | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nIRQ    | IC   | Not interrupt request. As <b>nFIQ</b> , but with lower priority. May be taken LOW to interrupt the processor when the appropriate enable is active. <b>nIRQ</b> may be synchronous or asynchronous, depending on the state of <b>ISYNC</b> .                                                                                                                                                                                                                                                                                                                                                                               |

| nM[4:0] | O4   | Not processor mode. These are output signals which are the inverses of the internal status bits indicating the processor operation mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

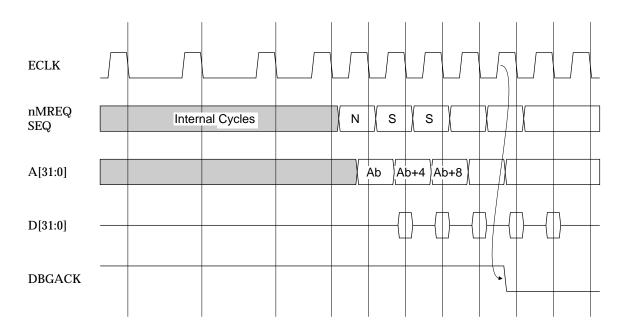

| nMREQ   | O4   | Not memory request. This signal, when LOW, indicates that the processor requires memory access during the following cycle. The signal becomes valid during phase 1, remaining valid through phase 2 of the cycle preceding that to which it refers.                                                                                                                                                                                                                                                                                                                                                                        |

| nOPC    | O8   | Not op-code fetch. When LOW this signal indicates that the processor is fetching an instruction from memory; when HIGH, data (if present) is being transferred. The signal becomes valid during phase 2 of the previous cycle, remaining valid through phase 1 of the referenced cycle. The timing of this signal may be modified by the use of <b>ALE</b> in a similar way to the address, please refer to the <b>ALE</b> description. This signal may also be driven to a high impedance state by driving <b>ABE</b> LOW.                                                                                                |

| nRESET  | IC   | Not reset. This is a level sensitive input signal which is used to start the processor from a known address. A LOW level will cause the instruction being executed to terminate abnormally. When nRESET becomes HIGH for at least one clock cycle, the processor will re-start from address 0. nRESET must remain LOW (and nWAIT must remain HIGH) for at least two clock cycles. During the LOW period the processor will perform dummy instruction fetches with the address incrementing from the point where reset was activated. The address will overflow to zero if nRESET is held beyond the maximum address limit. |

| nRW     | O8   | Not read/write. When HIGH this signal indicates a processor write cycle; when LOW, a read cycle. It becomes valid during phase 2 of the cycle before that to which it refers, and remains valid to the end of phase 1 of the referenced cycle. The timing of this signal may be modified by the use of <b>ALE</b> in a similar way to the address, please refer to the <b>ALE</b> description. This signal may also be driven to a high impedance state by driving <b>ABE</b> LOW.                                                                                                                                         |

| nTDOEN  | O4   | Not <b>TDO</b> Enable. When LOW, this signal denotes that serial data is being driven out on the <b>TDO</b> output. <b>nTDOEN</b> would normally be used as an output enable for a <b>TDO</b> pin in a packaged part.                                                                                                                                                                                                                                                                                                                                                                                                      |

| nTRANS  | O8   | Not memory translate. When this signal is LOW it indicates that the processor is in user mode. It may be used to tell memory management hardware when translation of the addresses should be turned on, or as an indicator of non-user mode activity. The timing of this signal may be modified by the use of <b>ALE</b> in a similar way to the address, please refer to the <b>ALE</b> description. This signal may also be driven to a high impedance state by driving <b>ABE</b> LOW.                                                                                                                                  |

**Table 1: Signal Description (Continued)**

## **Signal Description**

| Name   | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| nTRST  | I    | NOT Test Reset. Active-low reset signal for the boundary scan logic. This pin must be pulsed or driven low to achieve normal device operation, in addition to the normal device reset (nRESET). The action of this and the other four boundary scan signals are described in more detail later in this document.                                                                                                                                                                           |  |  |  |  |  |

| nWAIT  | I    | Not wait. When accessing slow peripherals, ARM7DI can be made to wait an integer number of MCLK cycles by driving nWAIT LOW. InternatinwAIT is ANDed with MCLK and must only change when MCLK is LOW nWAIT is not used it must be tied HIGH.                                                                                                                                                                                                                                               |  |  |  |  |  |

| PROG32 | I    | 32 bit Program configuration. When this signal is HIGH the processor can instructions from a 32 bit address space using address lines A[31:0]. When LOW the processor fetches instructions from a 26 bit address space using A[25:0]. In this latter configuration the address lines A[31:26] are not used instruction fetches. Before changing PROG32, ensure that the processor is 26 bit mode, and is not about to write to an address in the range 0 to (inclusive) in the next cycle. |  |  |  |  |  |

| SEQ    | O4   | Sequential address. This output signal will become HIGH when the address of the next memory cycle will be related to that of the last memory access. The new address will either be the same as or 4 greater than the old one.                                                                                                                                                                                                                                                             |  |  |  |  |  |

|        |      | The signal becomes valid during phase 1 and remains so through phase 2 of the cycle before the cycle whose address it anticipates. It may be used, in combination with the low-order address lines, to indicate that the next cycle can use a fast memory mode (for example DRAM page mode) and/or to bypass the address translation system.                                                                                                                                               |  |  |  |  |  |

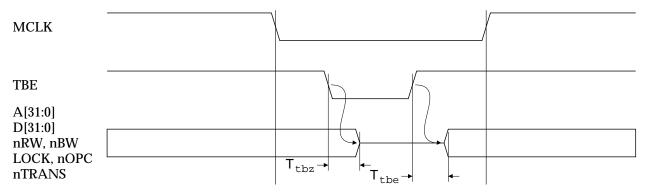

| ТВЕ    | IC   | Test Bus Enable. When driven LOW, TBE forces the data bus D[31:0], the Address bus A[31:0], plus LOCK, nBW, nRW, nTRANS and nOPC to high impedance. This is as if both ABE and DBE had both been driven LOW. However, TBE does not have an associated scan cell and so allows external signls to be driven high impedance during scan testing. Under normal operating conditions, TBE should be held HIGH at all times.                                                                    |  |  |  |  |  |

| тск    | IC   | Test Clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| TDI    | IC   | Test Data Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| TDO    | О    | Test Data Output. Output from the boundary scan logic.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| TMS    | IC   | Test Mode Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| VDD    | P    | Power supply. These connections provide power to the device.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| VSS    | P    | Ground. These connections are the ground reference for all signals.                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

**Table 1: Signal Description (Continued)**

#### **Key to Signal Types:**

IC - Input CMOS thresholds O4 - Output with INV4 driver P - Power

O8 - Output with INV8 driver

#### Note:

For a 0.8 µm ARM7DI:

INV4 driver has transistor sizes of p = 29.76  $\mu m/0.8~\mu m$ ; N = 16.96  $\mu m/0.8~\mu m$  INV8 driver has transistor sizes of p = 47.04  $\mu m/0.8~\mu m$ ; N = 33.6  $\mu m/0.8~\mu m$

## 3.0 Programmer's Model

ARM7DI supports a variety of operating configurations. Some are controlled by inputs and are known as the *hardware configurations*. Others may be controlled by software and these are known as *operating modes*.

#### 3.1 Hardware Configuration Signals

The ARM7DI processor provides 3 hardware configuration signals which may be changed while the processor is running and which are discussed below.

#### 3.1.1 Big and Little Endian

The **BIGEND** input sets whether the ARM7DI treats words in memory as being stored in Big Endian or Little Endian format. Memory is viewed as a linear collection of bytes numbered upwards from zero. Bytes 0 to 3 hold the first stored word, bytes 4 to 7 the second and so on.

In the Little Endian scheme the lowest numbered byte in a word is considered to be the least significant byte of the word and the highest numbered byte is the most significant. Byte 0 of the memory system should be connected to data lines 7 through 0 (**D[7:0]**) in this scheme.

Little Endian

#### Higher Address 31 24 23 16 15 8 7 0 Word Address 11 10 9 8 8 7 6 5 4 4 3 2 0 0 1 Lower Address

Least significant byte is at lowest address

Word is addressed by byte address of least significant byte

Figure 4: Little Endian addresses of bytes within words

In the Big Endian scheme the most significant byte of a word is stored at the lowest numbered byte and the least significant byte is stored at the highest numbered byte. Byte 0 of the memory system should therefore be connected to data lines 31 through 24 (**D[31:24]**). Load and store are the only instructions affected by the endian-ness: see *Section 4.7: Single data transfer (LDR, STR)* on page 42 for more details.

Lower Address

#### **Higher Address** Word Address

**Big Endian**

- Most significant byte is at lowest address

- · Word is addressed by byte address of most significant byte

Figure 5: Big Endian addresses of bytes within words

#### 3.1.2 Configuration Bits for Backward Compatibility

The other two inputs, **PROG32** and **DATA32** are used for backward compatibility with earlier ARM processors (see *12.0*: Appendix - Backward Compatibility) but should normally be set to 1. This configuration extends the address space to 32 bits, introduces major changes in the programmer's model as described below, and provides support for running existing 26 bit programs in the 32 bit environment. This mode is recommended for compatibility with future ARM processors and all new code should be written to use only the 32 bit operating modes.

Because the original ARM instruction set has been modified to accommodate 32 bit operation there are certain additional restrictions which programmers must be aware of. These are indicated in the text by the words *shall* and *shall not*. Reference should also be made to the *ARM Application Notes "Rules for ARM Code Writers"* and *"Notes for ARM Code Writers"*, available from your supplier.

### 3.2 Operating Mode Selection

ARM7DI has a 32 bit data bus and a 32 bit address bus. The processor supports *byte* (8 bit) and *word* (32 bit) data types, where words must be aligned to four byte boundaries. Instructions are exactly one word long, and data operations (eg ADD) are only performed on word quantities. Load and store operations can transfer either bytes or words.

ARM7DI supports six modes of operation:

- (1) User mode (usr): the normal program execution state

- (2) FIQ mode (fiq): designed to support a data transfer or channel process

- (3) IRQ mode (irq): used for general purpose interrupt handling

- (4) Supervisor mode (svc): a protected mode for the operating system

- (5) Abort mode (abt): entered after a data or instruction prefetch abort

- (6) Undefined mode (und): entered when an undefined instruction is executed

Mode changes may be made under software control or may be brought about by external interrupts or exception processing. Most application programs will execute in User mode. The other modes, known as *privileged modes*, will be entered to service interrupts or exceptions or to access protected resources.

#### 3.3 Registers

The processor has a total of 37 registers made up of 31 general 32 bit registers and 6 status registers. At any one time 16 general registers (R0 to R15) and one or two status registers are visible to the programmer. The visible registers depend on the processor mode. The other registers, known as the *banked registers*, are switched in to support IRQ, FIQ, Supervisor, Abort and Undefined mode processing. *Figure 6: Register Organisation* shows how the registers are arranged, with the banked registers shaded.

In all modes 16 registers, R0 to R15, are directly accessible. All registers except R15 are general purpose and may be used to hold data or address values. Register R15 holds the Program Counter (PC). When R15 is read, bits [1:0] are zero and bits [31:2] contain the PC. A seventeenth register (the CPSR - Current Program Status Register) is also accessible. It contains condition code flags and the current mode bits and may be thought of as an extension to the PC.

R14 is used as the subroutine link register and receives a copy of R15 when a Branch and Link instruction is executed. It may be treated as a general purpose register at all other times. R14\_svc, R14\_irq, R14\_fiq, R14\_abt and R14\_und are used similarly to hold the return values of R15 when interrupts and exceptions arise, or when Branch and Link instructions are executed within interrupt or exception routines.

#### **General Registers and Program Counter Modes**

| User32   | FIQ32    | Supervisor32 | Abort32  | IRQ32    | Undefined32 |

|----------|----------|--------------|----------|----------|-------------|

| R0       | R0       | R0           | R0       | R0       | R0          |

| R1       | R1       | R1           | R1       | R1       | R1          |

| R2       | R2       | R2           | R2       | R2       | R2          |

| R3       | R3       | R3           | R3       | R3       | R3          |

| R4       | R4       | R4           | R4       | R4       | R4          |

| R5       | R5       | R5           | R5       | R5       | R5          |

| R6       | R6       | R6           | R6       | R6       | R6          |

| R7       | R7       | R7           | R7       | R7       | R7          |

| R8       | R8_fiq   | R8           | R8       | R8       | R8          |

| R9       | R9_fiq   | R9           | R9       | R9       | R9          |

| R10      | R10_fiq  | R10          | R10      | R10      | R10         |

| R11      | R11_fiq  | R11          | R11      | R11      | R11         |

| R12      | R12_fiq  | R12          | R12      | R12      | R12         |

| R13      | R13_fiq  | R13_svc      | R13_abt  | R13_irq  | R13_und     |

| R14      | R14_fiq  | R14_svc      | R14_abt  | R14_irq  | R14_und     |

| R15 (PC) | R15 (PC) | R15 (PC)     | R15 (PC) | R15 (PC) | R15 (PC)    |

#### **Program Status Registers**

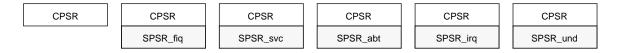

Figure 6: Register Organisation

FIQ mode has seven banked registers mapped to R8-14 (R8\_fiq-R14\_fiq). Many FIQ programs will not need to save any registers. User mode, IRQ mode, Supervisor mode, Abort mode and Undefined mode each have two banked registers mapped to R13 and R14. The two banked registers allow these modes to each have a private stack pointer and link register. Supervisor, IRQ, Abort and Undefined mode programs which require more than these two banked registers are expected to save some or all of the caller's registers (R0 to R12) on their respective stacks. They are then free to use these registers which they will restore before returning to the caller. In addition there are also five SPSRs (Saved Program Status Registers) which are loaded with the CPSR when an exception occurs. There is one SPSR for each privileged mode.

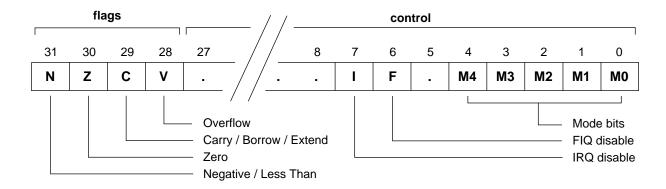

Figure 7: Format of the Program Status Registers (PSRs)

The format of the Program Status Registers is shown in *Figure 7: Format of the Program Status Registers (PSRs)*. The N, Z, C and V bits are the *condition code flags*. The condition code flags in the CPSR may be changed as a result of arithmetic and logical operations in the processor and may be tested by all instructions to determine if the instruction is to be executed.

The I and F bits are the *interrupt disable bits*. The I bit disables IRQ interrupts when it is set and the F bit disables FIQ interrupts when it is set. The M0, M1, M2, M3 and M4 bits (M[4:0]) are the *mode bits*, and these determine the mode in which the processor operates. The interpretation of the mode bits is shown in *Table 2: The Mode Bits*. Not all bit combinations define a valid processor mode. Only those explicitly described shall be used. The user should be aware that if any illegal value is programmed into the mode bits, M[4:0], the processor will enter an unrecoverable state. If this occurs, reset should be applied.

The bottom 28 bits of a PSR (incorporating I, F and M[4:0]) are known collectively as the *control bits*. These will change when an exception arises and in addition can be manipulated by software when the processor is in a privileged mode. Unused bits in the PSRs are reserved and their state shall be preserved when changing the flag or control bits. Programs shall not rely on specific values from the reserved bits when checking the PSR status, since they may read as one or zero in future processors.

| M[4:0] | Mode       | Accessible register set   |                |  |  |  |

|--------|------------|---------------------------|----------------|--|--|--|

| 10000  | User       | PC, R14R0                 | CPSR           |  |  |  |

| 10001  | FIQ        | PC, R14_fiqR8_fiq, R7R0   | CPSR, SPSR_fiq |  |  |  |

| 10010  | IRQ        | PC,R14_irqR13_irq,R12R0   | CPSR, SPSR_irq |  |  |  |

| 10011  | Supervisor | PC, R14_svcR13_svc, R12R0 | CPSR, SPSR_svc |  |  |  |

| 10111  | Abort      | PC, R14_abtR13_abt, R12R0 | CPSR, SPSR_abt |  |  |  |

| 11011  | Undefined  | PC,R14_undR13_und,R12R0   | CPSR, SPSR_und |  |  |  |

**Table 2: The Mode Bits**

#### 3.4 Exceptions

Exceptions arise whenever there is a need for the normal flow of program execution to be broken, so that (for example) the processor can be diverted to handle an interrupt from a peripheral. The processor state just prior to handling the exception must be preserved so that the original program can be resumed when the exception routine has completed. Many exceptions may arise at the same time.

ARM7DI handles exceptions by making use of the banked registers to save state. The old PC and CPSR contents are copied into the appropriate R14 and SPSR and the PC and mode bits in the CPSR bits are forced to a value which depends on the exception. Interrupt disable flags are set where required to prevent otherwise unmanageable nestings of exceptions. In the case of a re-entrant interrupt handler, R14 and the SPSR should be saved onto a stack in main memory before re-enabling the interrupt; when transferring the SPSR register to and from a stack, it is important to transfer the whole 32 bit value, and not just the flag or control fields. When multiple exceptions arise simultaneously, a fixed priority determines the order in which they are handled. This is listed later in *Section 3.4.7: Exception Priorities* on page 23.

#### 3.4.1 FIQ

The FIQ (Fast Interrupt reQuest) exception is externally generated by taking the **nFIQ** input LOW. This input can except either synchronous or asynchronous transitions, depending on the state of the **ISYNC** input signal. When **ISYNC** is LOW, **nFIQ** (and **nIRQ**) are considered asynchronous, and a cycle delay for synchronisation is incurred before the interrupt can affect the processor flow. FIQ is designed to support a data transfer or channel process, and has sufficient private registers to remove the need for register saving in such applications (thus minimising the overhead of context switching). The FIQ exception may be disabled by setting the F flag in the CPSR (but note that this is not possible from User mode). If the F flag is clear, ARM7DI checks for a LOW level on the output of the FIQ synchroniser at the end of each instruction.

When a FIQ is detected, ARM7DI:

- (1) Saves the address of the next instruction to be executed plus 4 in R14\_fiq; saves CPSR in SPSR\_fiq

- (2) Forces M[4:0]=10001 (FIQ mode) and sets the F and I bits in the CPSR

- (3) Forces the PC to fetch the next instruction from address 0x1C

To return normally from FIQ, use SUBS PC, R14\_fiq,#4 which will restore both the PC (from R14) and the CPSR (from SPSR\_fiq) and resume execution of the interrupted code.

#### 3.4.2 IRQ

The IRQ (Interrupt ReQuest) exception is a normal interrupt caused by a LOW level on the **nIRQ** input. It has a lower priority than FIQ, and is masked out when a FIQ sequence is entered. Its effect may be masked out at any time by setting the I bit in the CPSR (but note that this is not possible from User mode). If the I flag is clear, ARM7DI checks for a LOW level on the output of the IRQ synchroniser at the end of each instruction. Note that **nIRQ** may also have synchronous or asynchronous timing, depending on the state of the **ISYNC** input. When an IRQ is detected, ARM7DI:

- (1) Saves the address of the next instruction to be executed plus 4 in R14\_irq; saves CPSR in SPSR\_irq

- (2) Forces M[4:0]=10010 (IRQ mode) and sets the I bit in the CPSR

- (3) Forces the PC to fetch the next instruction from address 0x18

To return normally from IRQ, use SUBS PC,R14\_irq,#4 which will restore both the PC and the CPSR and resume execution of the interrupted code.

#### **3.4.3 Abort**

An abort can be signalled by the external **ABORT** input. **ABORT** indicates that the current memory access cannot be completed. For instance, in a virtual memory system the data corresponding to the current address may have been moved out of memory onto a disc, and considerable processor activity may be required to recover the data before the access can be performed successfully. ARM7DI checks for aborts during memory access cycles. When successfully aborted ARM7DI will respond in one of two ways:

- (1) If the abort occurred during an instruction prefetch (a *Prefetch Abort*), the prefetched instruction is marked as invalid but the abort exception does not occur immediately. If the instruction is not executed, for example as a result of a branch being taken while it is in the pipeline, no abort will occur. An abort will take place if the instruction reaches the head of the pipeline and is about to be executed.

- (2) If the abort occurred during a data access (a *Data Abort*), the action depends on the instruction type.

- (a) Single data transfer instructions (LDR, STR) will write back modified base registers and the Abort handler must be aware of this.

- (b) The swap instruction (SWP) is aborted as though it had not executed, though externally the read access may take place.

- (c) Block data transfer instructions (LDM, STM) complete, and if write-back is set, the base is updated. If the instruction would normally have overwritten the base with data (i.e. LDM with the base in the transfer list), this overwriting is prevented. All register overwriting is prevented after the Abort is indicated, which means in particular that R15 (which is always last to be transferred) is preserved in an aborted LDM instruction.

When either a prefetch or data abort occurs, ARM7DI:

- (1) Saves the address of the aborted instruction plus 4 (for prefetch aborts) or 8 (for data aborts) in R14\_abt; saves CPSR in SPSR\_abt.

- (2) Forces M[4:0]=10111 (Abort mode) and sets the I bit in the CPSR.

- (3) Forces the PC to fetch the next instruction from either address 0x0C (prefetch abort) or address 0x10 (data abort).

To return after fixing the reason for the abort, use SUBS PC,R14\_abt,#4 (for a prefetch abort) or SUBS PC,R14\_abt,#8 (for a data abort). This will restore both the PC and the CPSR and retry the aborted instruction.

The abort mechanism allows a *demand paged virtual memory system* to be implemented when suitable memory management software is available. The processor is allowed to generate arbitrary addresses, and when the data at an address is unavailable the MMU signals an abort. The processor traps into system software which must work out the cause of the abort, make the requested data available, and retry the aborted instruction. The application program needs no knowledge of the amount of memory available to it, nor is its state in any way affected by the abort.

#### 3.4.4 Software interrupt

The software interrupt instruction (SWI) is used for getting into Supervisor mode, usually to request a particular supervisor function. When a SWI is executed, ARM7DI performs the following:

- (1) Saves the address of the SWI instruction plus 4 in R14\_svc; saves CPSR in SPSR\_svc

- (2) Forces M[4:0]=10011 (Supervisor mode) and sets the I bit in the CPSR

- (3) Forces the PC to fetch the next instruction from address 0x08

To return from a SWI, use MOVS PC,R14\_svc. This will restore the PC and CPSR and return to the instruction following the SWI.

#### 3.4.5 Undefined instruction trap

When the ARM7DI comes across an instruction which it cannot handle (see *Chapter 4.0: Instruction Set*), it offers it to any coprocessors which may be present. If a coprocessor can perform this instruction but is busy at that time, ARM7DI will wait until the coprocessor is ready or until an interrupt occurs. If no coprocessor can handle the instruction then ARM7DI will take the undefined instruction trap.

The trap may be used for software emulation of a coprocessor in a system which does not have the coprocessor hardware, or for general purpose instruction set extension by software emulation.

When ARM7DI takes the undefined instruction trap it performs the following:

- (1) Saves the address of the Undefined or coprocessor instruction plus 4 in R14\_und; saves CPSR in SPSR\_und.

- (2) Forces M[4:0]=11011 (Undefined mode) and sets the I bit in the CPSR

- (3) Forces the PC to fetch the next instruction from address 0x04

To return from this trap after emulating the failed instruction, use MOVS PC,R14\_und. This will restore the CPSR and return to the instruction following the undefined instruction.

#### 3.4.6 Vector Summary

| Address    | Exception             | Mode on entry |  |  |

|------------|-----------------------|---------------|--|--|

| 0x00000000 | Reset                 | Supervisor    |  |  |

| 0x00000004 | Undefined instruction | Undefined     |  |  |

| 0x00000008 | Software interrupt    | Supervisor    |  |  |

| 0x000000C  | Abort (prefetch)      | Abort         |  |  |

| 0x00000010 | Abort (data)          | Abort         |  |  |

| 0x00000014 | reserved              |               |  |  |

| 0x00000018 | IRQ                   | IRQ           |  |  |

| 0x0000001C | FIQ                   | FIQ           |  |  |

**Table 3: Vector Summary**

These are byte addresses, and will normally contain a branch instruction pointing to the relevant routine.

The FIQ routine might reside at 0x1C onwards, and thereby avoid the need for (and execution time of) a branch instruction.

#### 3.4.7 Exception Priorities

When multiple exceptions arise at the same time, a fixed priority system determines the order in which they will be handled:

- (1) Reset (highest priority)

- (2) Data abort

- (3) FIQ

- (4) IRQ

- (5) Prefetch abort

- (6) Undefined Instruction, Software interrupt (lowest priority)

Note that not all exceptions can occur at once. Undefined instruction and software interrupt are mutually exclusive since they each correspond to particular (non-overlapping) decodings of the current instruction.

If a data abort occurs at the same time as a FIQ, and FIQs are enabled (i.e. the F flag in the CPSR is clear), ARM7DI will enter the data abort handler and then immediately proceed to the FIQ vector. A normal return from FIQ will cause the data abort handler to resume execution. Placing data abort at a higher priority than FIQ is necessary to ensure that the transfer error does not escape detection; the time for this exception entry should be added to worst case FIQ latency calculations.

#### 3.4.8 Interrupt Latencies

The worst case latency for FIQ, assuming that it is enabled, consists of the longest time the request can take to pass through the synchroniser (*Tsyncmax* if asynchronous), plus the time for the longest instruction to complete (*Tldm*, the longest instruction is an LDM which loads all the registers including the PC), plus the time for the data abort entry (*Texc*), plus the time for FIQ entry (*Tfiq*). At the end of this time ARM7DI will be executing the instruction at 0x1C.

*Tsyncmax* is 3 processor cycles, *Tldm* is 20 cycles, *Texc* is 3 cycles, and *Tfiq* is 2 cycles. The total time is therefore 28 processor cycles. This is just over 1.4 microseconds in a system which uses a continuous 20 MHz processor clock. The maximum IRQ latency calculation is similar, but must allow for the fact that FIQ has higher priority and could delay entry into the IRQ handling routine for an arbitrary length of time. The minimum latency for FIQ or IRQ consists of the shortest time the request can take through the synchroniser (*Tsyncmin*) plus *Tfiq*. This is 4 processor cycles.

#### 3.5 Reset

When the **nRESET** signal goes LOW, ARM7DI abandons the executing instruction and then continues to fetch instructions from incrementing word addresses.

When nRESET goes HIGH again, ARM7DI does the following:

- (1) Overwrites R14\_svc and SPSR\_svc by copying the current values of the PC and CPSR into them. The value of the saved PC and CPSR is not defined.

- (2) Forces M[4:0]=10011 (Supervisor mode) and sets the I and F bits in the CPSR.

- (3) Forces the PC to fetch the next instruction from address 0x00

### 4.0 Instruction Set

### **4.1 Instruction Set Summary**

A summary of the ARM7DI instruction set is shown in Figure 8: Instruction Set Summary.

Note: some instruction codes are not defined but do not cause the Undefined instruction trap to be taken, for instance a Multiply instruction with bit 6 changed to a 1. These instructions shall not be used, as their action may change in future ARM implementations.

| 31 28 | 27 26 25 | 24 | 23  | 2                                      | 2  | 21  | 20 | 19 16 | 15 12      | 11 8        | 7 5       | 4         | 3 0 | _                               |

|-------|----------|----|-----|----------------------------------------|----|-----|----|-------|------------|-------------|-----------|-----------|-----|---------------------------------|

| Cond  | 0 0 1    |    | Op  | cc                                     | de |     | S  | Rn    | Rd         |             | Operand 2 |           |     | Data Processing<br>PSR Transfer |

| Cond  | 000      | 0  | 0 0 | )                                      |    | Α   | S  | Rd    | Rn         | Rs          | 1 0 0     | 1         | Rm  | Multiply                        |

| Cond  | 0 0 0    | 1  | 0   | ı                                      | В  | 0   | 0  | Rn    | Rd         | 0 0 0 0     | 1 0 0     | 1         | Rm  | Single Data Swap                |

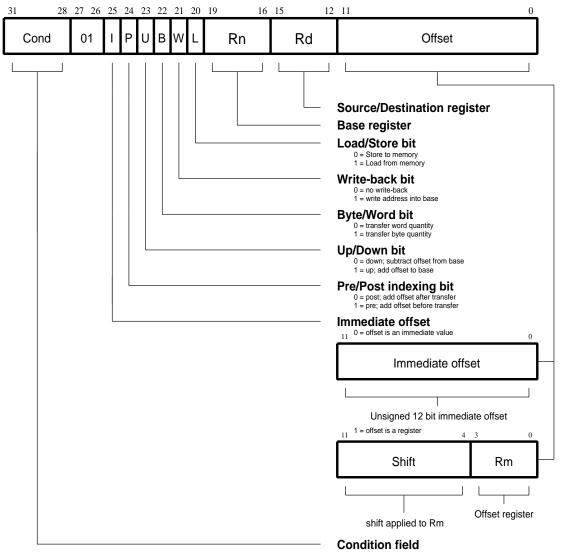

| Cond  | 0 1 I    | Р  | U   |                                        | В  | W   | ┙  | Rn    | Rd         |             | offset    |           |     | Single Data Transfer            |

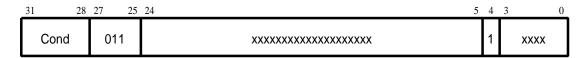

| Cond  | 0 1 1    |    |     | XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX |    |     |    |       |            |             | XXXX      | Undefined |     |                                 |

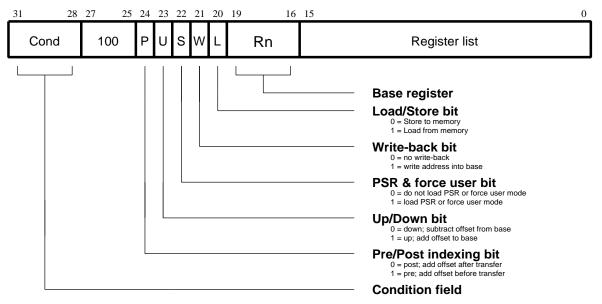

| Cond  | 1 0 0    | Р  | U   | ļ                                      | s  | W   | L  | Rn    |            | Regist      | er List   |           |     | Block Data Transfer             |

| Cond  | 1 0 1    | L  |     |                                        |    |     |    |       | offse      | t           |           |           |     | Branch                          |

| Cond  | 1 1 0    | Р  | U   | I                                      | Ν  | W   | L  | Rn    | CRd        | CP#         |           | off       | set | Coproc Data Transfer            |

| Cond  | 1 1 1    | 0  |     | С                                      | PC | Opc | ;  | CRn   | CRd        | CP#         | СР        | 0         | CRm | Coproc Data Operation           |

| Cond  | 1 1 1    | 0  | С   | P                                      | Ор | С   | L  | CRn   | Rd         | CP#         | СР        | 1         | CRm | Coproc Register Transfer        |

| Cond  | 1 1 1    | 1  |     |                                        |    |     |    |       | ignored by | / processor |           |           |     | Software Interrupt              |

**Figure 8: Instruction Set Summary**

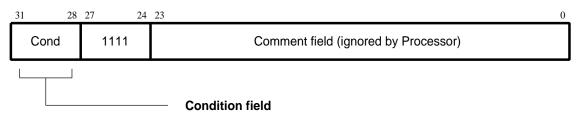

#### 4.2 The Condition Field

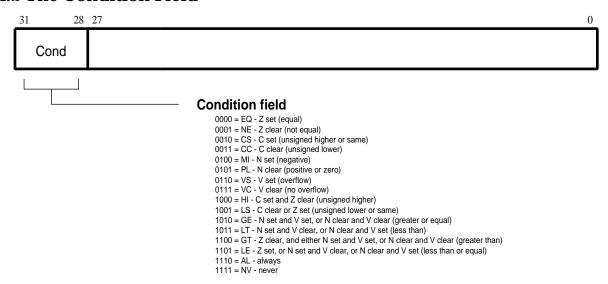

**Figure 9: Condition Codes**

All ARM7DI instructions are conditionally executed, which means that their execution may or may not take place depending on the values of the N, Z, C and V flags in the CPSR. The condition encoding is shown in *Figure 9: Condition Codes*.

If the *always* (AL) condition is specified, the instruction will be executed irrespective of the flags. The *never* (NV) class of condition codes shall not be used as they will be redefined in future variants of the ARM architecture. If a NOP is required it is suggested that MOV R0,R0 be used. The assembler treats the absence of a condition code as though *always* had been specified.

The other condition codes have meanings as detailed in *Figure 9: Condition Codes*, for instance code 0000 (EQual) causes the instruction to be executed only if the Z flag is set. This would correspond to the case where a compare (CMP) instruction had found the two operands to be equal. If the two operands were different, the compare instruction would have cleared the Z flag and the instruction will not be executed.

#### 4.3 Branch and Branch with link (B, BL)

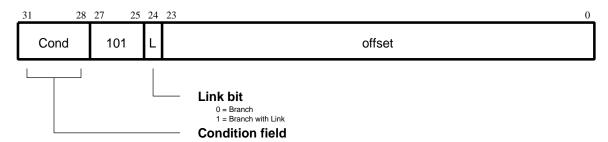

The instruction is only executed if the condition is true. The various conditions are defined at the beginning of this chapter. The instruction encoding is shown in *Figure 10: Branch Instructions*.

Branch instructions contain a signed 2's complement 24 bit offset. This is shifted left two bits, sign extended to 32 bits, and added to the PC. The instruction can therefore specify a branch of +/- 32Mbytes. The branch offset must take account of the prefetch operation, which causes the PC to be 2 words (8 bytes) ahead of the current instruction.

**Figure 10: Branch Instructions**

Branches beyond +/- 32Mbytes must use an offset or absolute destination which has been previously loaded into a register. In this case the PC should be manually saved in R14 if a Branch with Link type operation is required.

#### 4.3.1 The link bit

Branch with Link (BL) writes the old PC into the link register (R14) of the current bank. The PC value written into R14 is adjusted to allow for the prefetch, and contains the address of the instruction following the branch and link instruction. Note that the CPSR is not saved with the PC.

To return from a routine called by Branch with Link use MOV PC,R14 if the link register is still valid or LDM Rn!,{..PC} if the link register has been saved onto a stack pointed to by Rn.

#### 4.3.2 Instruction Cycle Times

Branch and Branch with Link instructions take 2S + 1N incremental cycles, where S and N are as defined in *Section 5.1: Cycle types* on page 71.

#### 4.3.3 Assembler syntax

#### B{L}{cond} < expression>

{L} is used to request the Branch with Link form of the instruction. If absent, R14 will not be affected by the instruction.

{cond} is a two-character mnemonic as shown in *Figure 9: Condition Codes* (EQ, NE, VS etc). If absent then AL (ALways) will be used.

<expression> is the destination. The assembler calculates the offset.

Items in {} are optional. Items in <> must be present.

#### 4.3.4 Examples

```

here

BAL

; assembles to OxEAFFFFFE (note effect of PC offset)

here

В

there

; ALways condition used as default

R1,#0

; compare R1 with zero and branch to fred if R1

CMP

BEQ

fred

; was zero otherwise continue to next instruction

sub+ROM ; call subroutine at computed address

BL

ADDS

R1,#1

; add 1 to register 1, setting CPSR flags on the

BLCC

sub

; result then call subroutine if the C flag is clear,

; which will be the case unless R1 held 0xfffffffff

```

## **Instruction Set - Data processing**

#### 4.4 Data processing

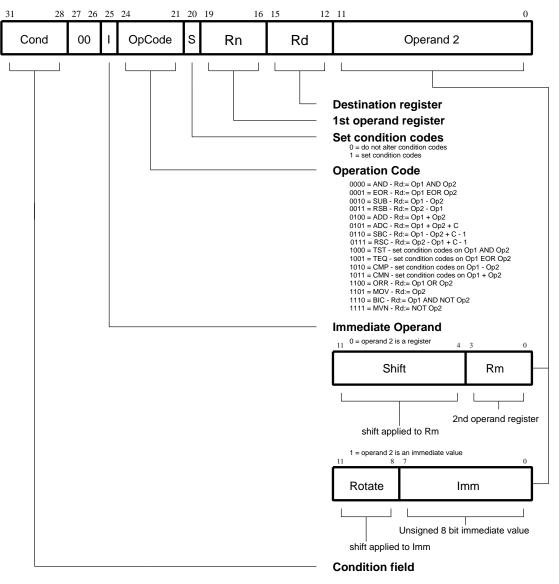

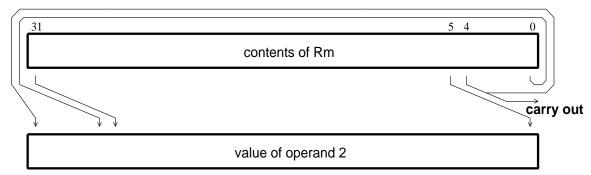

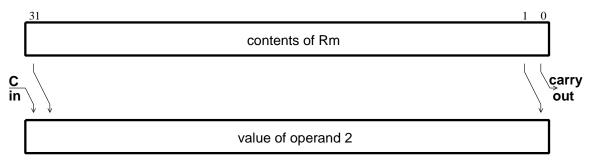

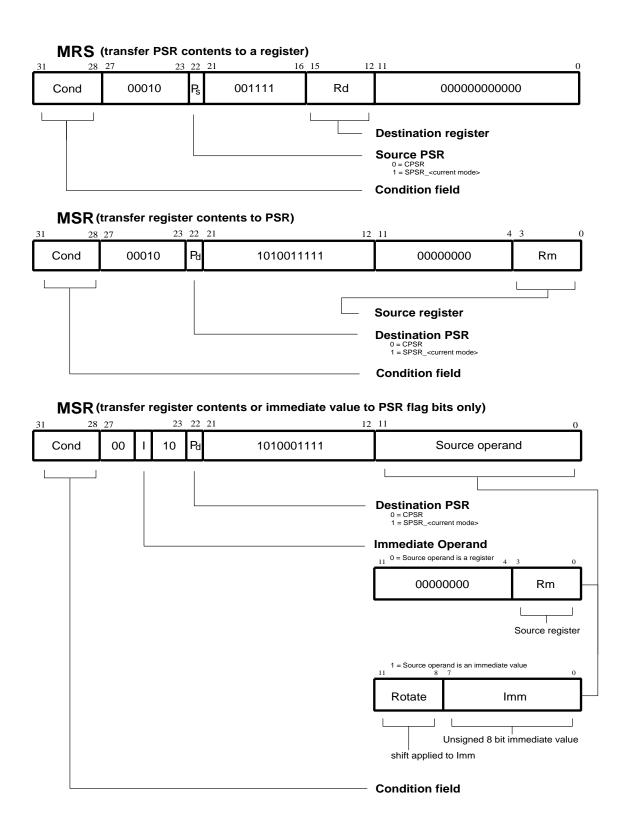

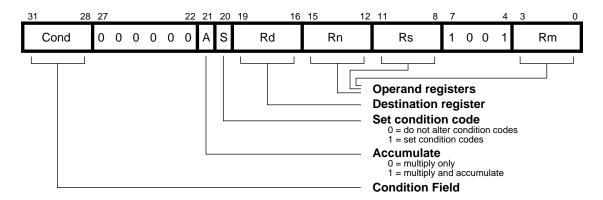

The instruction is only executed if the condition is true, defined at the beginning of this chapter. The instruction encoding is shown in *Figure 11: Data Processing Instructions*.

The instruction produces a result by performing a specified arithmetic or logical operation on one or two operands. The first operand is always a register (Rn). The second operand may be a shifted register (Rm) or a rotated 8 bit immediate value (Imm) according to the value of the I bit in the instruction. The condition codes in the CPSR may be preserved or updated as a result of this instruction, according to the value of the S bit in the instruction. Certain operations (TST, TEQ, CMP, CMN) do not write the result to Rd. They are used only to perform tests and to set the condition codes on the result and always have the S bit set. The instructions and their effects are listed in *Table 4: ARM Data Processing Instructions*.

**Figure 11: Data Processing Instructions**

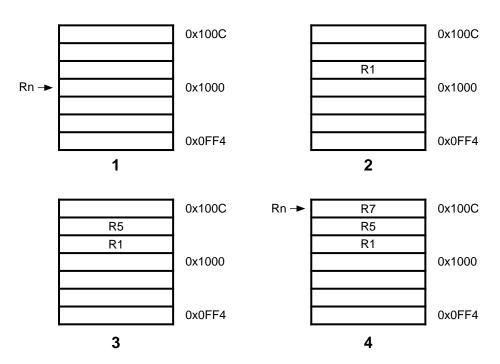

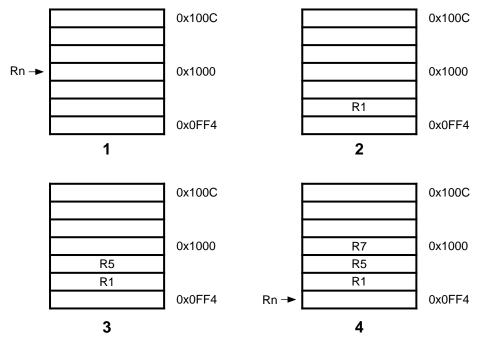

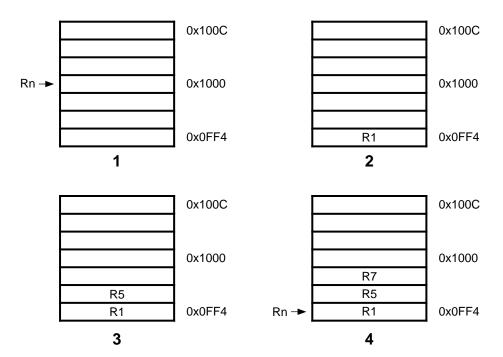

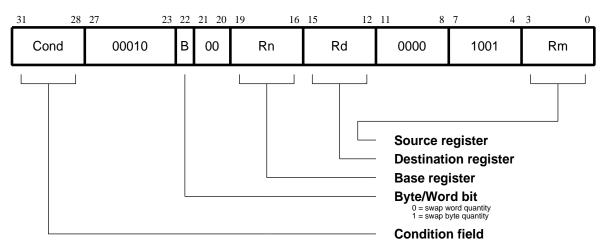

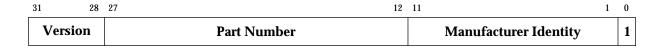

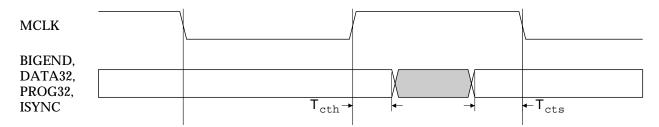

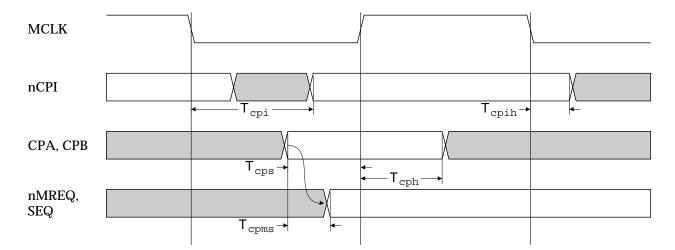

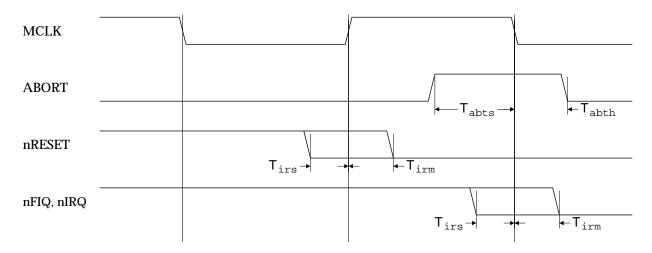

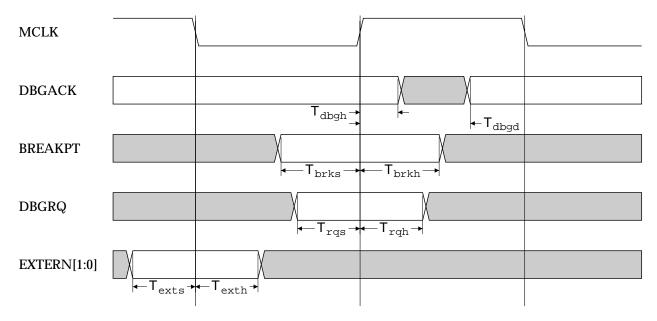

#### 4.4.1 CPSR flags