# RealView Compilation Tools

Version 2.0

**Developer Guide**

# RealView Compilation Tools Developer Guide

Copyright © 2002, 2003 ARM Limited. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

#### **Change History**

| Date           | Issue | Change                     |

|----------------|-------|----------------------------|

| August 2002    | A     | Release 1.2                |

| January 2003   | В     | Release 2.0                |

| September 2003 | С     | Release 2.0.1 for RVDS 2.0 |

#### **Proprietary Notice**

Words and logos marked with ® or ™ are registered trademarks or trademarks owned by ARM Limited. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

#### **Confidentiality Status**

This document is Open Access. This document has no restriction on distribution.

#### **Product Status**

The information in this document is final (information on a developed product).

#### Web Address

http://www.arm.com

# Contents

# **RealView Compilation Tools Developer Guide**

|           | Prefa | ace                                                     |      |

|-----------|-------|---------------------------------------------------------|------|

|           |       | About this book                                         | v    |

|           |       | Feedback                                                | i)   |

| Chapter 1 | Intro | oduction                                                |      |

| -         | 1.1   | About the RVCT Developer Guide                          | 1-2  |

|           | 1.2   | General programming issues                              |      |

|           | 1.3   | Developing for the ARM processors                       |      |

| Chapter 2 | Emb   | edded Software Development                              |      |

| -         | 2.1   | About embedded software development                     | 2-2  |

|           | 2.2   | Default RVCT behavior in the absence of a target system | 2-4  |

|           | 2.3   | Tailoring the C library to your target hardware         |      |

|           | 2.4   | Tailoring the image memory map to your target hardware  | 2-13 |

|           | 2.5   | Reset and initialization                                |      |

|           | 2.6   | Further memory map considerations                       | 2-33 |

| Chapter 3 | Usin  | g the Procedure Call Standard                           |      |

|           | 3.1   | About the ARM-Thumb Procedure Call Standard             | 3-2  |

|           | 3.2   | Register roles and names                                |      |

|           | 3.3   | The stack                                               |      |

|           | 3.4   | Parameter passing                                       |      |

|           |       |                                                         |      |

|           | 3.5   | Stack limit checking                                  | 3-11 |

|-----------|-------|-------------------------------------------------------|------|

|           | 3.6   | Read-only position independence                       | 3-14 |

|           | 3.7   | Read-write position independence                      | 3-15 |

|           | 3.8   | Interworking between ARM and Thumb states             |      |

|           | 3.9   | Floating-point options                                | 3-17 |

| Chapter 4 | Inter | working ARM and Thumb                                 |      |

|           | 4.1   | About interworking                                    | 4-2  |

|           | 4.2   | Assembly language interworking                        |      |

|           | 4.3   | C and C++ interworking and veneers                    |      |

|           | 4.4   | Assembly language interworking using veneers          |      |

| Chapter 5 | Mixii | ng C, C++, and Assembly Language                      |      |

| -         | 5.1   | Using the inline assembler                            | 5-2  |

|           | 5.2   | Using the embedded assembler                          |      |

|           | 5.3   | Differences between inline and embedded assembly code | 5-15 |

|           | 5.4   | Accessing C global variables from assembly code       |      |

|           | 5.5   | Using C header files from C++                         |      |

|           | 5.6   | Calling between C, C++, and ARM assembly language     |      |

| Chapter 6 | Hand  | dling Processor Exceptions                            |      |

| •         | 6.1   | About processor exceptions                            | 6-2  |

|           | 6.2   | Determining the Processor State                       |      |

|           | 6.3   | Entering and leaving an exception                     |      |

|           | 6.4   | Handling the Exception                                |      |

|           | 6.5   | Installing an exception handler                       |      |

|           | 6.6   | SWI handlers                                          |      |

|           | 6.7   | Interrupt handlers                                    | 6-27 |

|           | 6.8   | Reset handlers                                        | 6-36 |

|           | 6.9   | Undefined Instruction handlers                        | 6-37 |

|           | 6.10  | Prefetch Abort handler                                | 6-38 |

|           | 6.11  | Data Abort handler                                    | 6-39 |

|           | 6.12  | Chaining exception handlers                           | 6-41 |

|           | 6.13  | System mode                                           | 6-43 |

| Chapter 7 | Debu  | ug Communications Channel                             |      |

| -         | 7.1   | About the Debug Communications Channel                | 7-2  |

|           | 7.2   | Target transfer of data                               |      |

|           | 7.3   | Polled debug communications                           |      |

|           | 7.4   | Interrupt-driven debug communications                 |      |

|           | 7.5   | Access from Thumb state                               |      |

|           | 7.6   | Semihosting                                           | 7-10 |

|           | Glos  | ssary                                                 |      |

|           |       |                                                       |      |

# **Preface**

This preface introduces the *RealView Compilation Tools v2.0 Developer Guide*. It contains the following sections:

- About this book on page vi

- Feedback on page ix.

#### About this book

This book provides tutorial information on writing code targeted at the ARM family of processors.

#### Intended audience

This book is written for all developers writing code for the ARM. It assumes that you are an experienced software developer, and that you are familiar with the ARM development tools described in the *RealView Compilation Tools v2.0 Essentials Guide*.

#### Using this book

This book is organized into the following chapters:

#### Chapter 1 Introduction

Read this chapter for an introduction to *RealView Compilation Tools* (RVCT).

## Chapter 2 Embedded Software Development

Read this chapter for details of how to develop embedded applications with RVCT. It describes the default RVCT behavior in the absence of a target system, and how to tailor the C library and image memory map to your target system.

#### Chapter 3 Using the Procedure Call Standard

Read this chapter for details of how to use the *ARM-Thumb Procedure Call Standard*. Using this standard makes it easier to ensure that separately compiled and assembled modules work together.

#### Chapter 4 Interworking ARM and Thumb

Read this chapter for details of how to change between ARM state and Thumb® state when writing code for processors that implement the Thumb instruction set.

#### Chapter 5 Mixing C, C++, and Assembly Language

Read this chapter for details of how to write mixed C, C++, and ARM assembly language code. It also describes how to use the ARM inline and embedded assembler from C and C++.

#### Chapter 6 Handling Processor Exceptions

Read this chapter for details of how to handle the various types of exception supported by ARM processors.

#### Chapter 7 Debug Communications Channel

Read this chapter for a description of how to use the *Debug Communications Channel* (DCC).

#### Typographical conventions

The following typographical conventions are used in this book:

monospace Denotes text that can be entered at the keyboard, such as commands, file

and program names, and source code.

monospace Denotes a permitted abbreviation for a command or option. The

underlined text can be entered instead of the full command or option

name.

monospace italic

Denotes arguments to commands and functions where the argument is to

be replaced by a specific value.

monospace bold

Denotes language keywords when used outside example code.

italic Highlights important notes, introduces special terminology, denotes

internal cross-references, and citations.

**bold** Highlights interface elements, such as menu names. Also used for

emphasis in descriptive lists, where appropriate, and for ARM processor

signal names.

#### **Further reading**

This section lists publications from both ARM Limited and third parties that provide additional information on developing code for the ARM family of processors.

ARM periodically provides updates and corrections to its documentation. See http://www.arm.com for current errata sheets and addenda, and the ARM Frequently Asked Questions.

#### **ARM** publications

This book contains general information on developing applications for the ARM family of processors. Refer to the following books in the RVCT document suite for information on other components:

• RealView Compilation Tools v2.0 Essentials Guide (ARM DUI 0202)

- RealView Compilation Tools v2.0 Assembler Guide (ARM DUI 0204)

- RealView Compilation Tools v2.0 Compiler and Libraries Guide (ARM DUI 0205)

- RealView Compilation Tools v2.0 Linker and Utilities Guide (ARM DUI 0206).

The following additional documentation is provided with RealView Compilation Tools:

- ARM FLEXIm License Management Guide (ARM DUI 0209). This is supplied in DynaText and PDF format.

- ARM ELF specification (SWS ESPC 0003). This is supplied as a PDF file, ARMELF.pdf, in install\_directory\Documentation\Specifications\1.0\release\platform\PDF.

- TIS DWARF 2 specification. This is supplied as a PDF file, TIS-DWARF2.pdf, in install\_directory\Documentation\Specifications\1.0\release\platform\PDF.

- ARM-Thumb Procedure Call Standard specification. This is supplied as a PDF file, ATPCS.pdf, in

install\_directory\Documentation\Specifications\1.0\release\platform\PDF.

In addition, refer to the following documentation for specific information relating to ARM products:

- RealView ARMulator ISS v1.3 User Guide (ARM DUI 0207)

- Multi-ICE v2.2 User Guide (ARM DUI 0048), or later version

- *ARM Reference Peripheral Specification* (ARM DDI 0062)

- the ARM datasheet or technical reference manual for your hardware device.

### Other publications

The following book gives general information about the ARM architecture:

ARM System-on-chip Architecture (second edition), Furber, S., (2000). Addison Wesley. ISBN 0-201-67519-6.

#### **Feedback**

ARM Limited welcomes feedback on both RealView Compilation Tools, and its documentation.

#### Feedback on RealView Compilation Tools

If you have any problems with RealView Compilation Tools, contact your supplier. To help them provide a rapid and useful response, give:

- your name and company

- the serial number of the product

- details of the release you are using

- details of the platform you are running on, such as the hardware platform, operating system type and version

- a small standalone sample of code that reproduces the problem

- a clear explanation of what you expected to happen, and what actually happened

- the commands you used, including any command-line options

- sample output illustrating the problem

- the version string of the tool, including the version number and date.

#### Feedback on this book

If you notice any errors or omissions in this book, send email to errata@arm.com giving:

- the document title

- the document number

- the page number(s) to which your comments apply

- a concise explanation of the problem.

General suggestions for additions and improvements are also welcome.

Preface

# Chapter 1 Introduction

This chapter introduces the  $RealView^{\text{\tiny M}}$  Compilation Tools (RVCT). It contains the following sections:

- *About the RVCT Developer Guide* on page 1-2

- *General programming issues* on page 1-5

- Developing for the ARM processors on page 1-10.

| —— Note |  |

|---------|--|

|---------|--|

The examples given in this document use single-dashes for the options to the compiler, assembler and linker. In RVCT v2.0 you can specify command-line keywords using double dashes --, for example --partial. However, the single-letter options in the compiler, for example -E, do not have double-dash equivalents.

The single-dash command-line options used in previous versions of ADS and RVCT are still supported for backwards-compatibility.

# 1.1 About the RVCT Developer Guide

This book contains information that helps you with specific issues when developing code for the ARM family of RISC processors. In general, the chapters in this book assume that you are using the *RealView Compilation Tools* (RVCT) to develop your code.

RVCT consists of a suite of tools, together with supporting documentation and examples, that enable you to write and build applications for the ARM family of RISC processors. You can use RVCT to build C, C++, or ARM assembly language programs.

The RVCT toolkit consists of the following major components:

- command-line development tools

- utilities

- supporting software.

See Further reading on page vii for a list of the RVCT documentation.

#### 1.1.1 Example code

The code for many of the examples in this book is located in the directory:

install\_directory\RVCT\Examples\2.0\release\platform

where *install\_directory* is the directory where you installed RVCT v2.0, and *platform* is either windows or unix. For clarity, this directory is referred to as *Examples\_directory* in the rest of this document.

In addition, the directory contains example code that is not described in this book. Read the readme.txt in each example directory for more information. The examples are installed in the following subdirectories:

| asm      | This directory contains some examples of ARM assembly language programming. The examples are used in the <i>RealView Compilation Tools v2.0 Assembler Guide</i> .       |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| срр      | This directory contains some simple C++ examples. In addition, the subdirectory rw contains the Rogue Wave manual and tutorial examples.                                |

| databort | This directory contains design documentation and example code for a standard data abort handler.                                                                        |

| dcc      | This directory contains example code that demonstrates how to use the Debug Communications Channel. The example is described in Chapter 7 Debug Communications Channel. |

cached\_dhry This directory contains examples to routines to initialize cache and

TCMs, built around the Dhrystone example.

dhry This directory contains source for Dhrystone.

dhryansi This directory contains an ANSI C version of Dhrystone.

emb\_sw\_dev This directory contains the example projects referenced in Chapter 2

Embedded Software Development. The following subdirectories are

included:

buildn Batch and make files to build the example projects.

dhry Source files for the Dhrystone benchmarking program. This

program provides the code base for the example projects in the

individual buildn directories.

source All other source files needed to build the example projects.

include User defined header files.

scatter Scatter files used to build the example projects.

embedded This directory contains source code examples that show how to write

code for ROM. The examples are targeted at the ARM Integrator<sup>™</sup> board.

explasm This directory contains additional ARM assembly language examples.

fft\_5te Fast Fourier Transform code optimized for ARM architecture v5TE.

inline This directory contains examples that show how to use the inline

assembler when compiling ARM C and C++ code. The examples are

described in Chapter 5 Mixing C, C++, and Assembly Language.

interwork This directory contains examples that show how to interwork between

ARM code and Thumb code. The examples are described in Chapter 4

Interworking ARM and Thumb.

mmugen This directory contains the source and documentation for the MMUgen

utility. This utility can generate MMU pagetable data from a rules file that

describes the virtual to physical address translation required.

picpid This directory contains an example of how to write position-independent

code. See the readme.txt for a detailed description.

sorts This directory contains example code that compares an insertion sort,

shell sort, and the quick sort used in the ARM C libraries.

swi This directory contains an example SWI handler.

unicode This directory contains example code that enables you to test the

multibyte character support in RVCT v2.0.

vfpsupport This directory contains example code for enabling and carrying out

Vector Floating Point (VFP) operations. Also included are various utility

files for configuring the debug system when using VFP.

## 1.2 General programming issues

The ARM family of processors are RISC processors. Many of the programming strategies that give efficient code are generic to RISC processors. As with many RISC processors, the ARM family of processors are designed to access aligned data, that is, words that lie on addresses that are multiples of four, halfwords that lie on addresses that are multiples of two. This data is located on its natural size boundary.

ARM compilers normally align global variables to these natural size boundaries so that these items can be accessed efficiently using the LDR and STR instructions.

This contrasts with most CISC architectures where instructions are available to directly access unaligned data. Therefore, you must take care when porting legacy code from CISC architectures to the ARM processors. Accesses to unaligned data can be expensive in code size or performance.

The following sections discuss the programming issues in more detail:

- Using the ARM-Thumb Procedure Call Standard efficiently

- Unaligned pointers

- *Unaligned fields in structures* on page 1-6

- *Unaligned LDR for accessing halfwords* on page 1-8

- *Porting code and detecting unaligned accesses* on page 1-9.

# 1.2.1 Using the ARM-Thumb Procedure Call Standard efficiently

Under the *ARM-Thumb Procedure Call Standard* the ARM compiler passes the first four integer-sized function parameters in registers r0 to r3. Additional parameters are passed on the stack. This means that:

- it is more efficient to pass large parameters, such as **structs**, by reference

- it is more efficient to restrict functions to four or fewer integer-sized parameters, where possible.

# 1.2.2 Unaligned pointers

The ARM compiler expects normal C pointers to point to an aligned word in memory, because this enables the compiler to generate more efficient code.

For example, if the pointer int \* is used to read a word, the ARM compiler uses an LDR instruction in the generated code. This works as expected when the address is a multiple of four (that is, on a word boundary). However, if the address is not a multiple of four, then an LDR instruction returns a rotated result rather than performing a true unaligned word load. The rotated result depends on the offset and endianness of the system.

If your code loads data from a pointer that points to the address 0x8006, for example, then you might expect to load the contents of bytes from 0x8006, 0x8007, 0x8008, and 0x8009. However, on an ARM processor, this access loads the rotated contents of bytes from 0x8004, 0x8005, 0x8006, and 0x8007.

Therefore, if you want to define a pointer to a word that can be at any address (that is, that can be at a non-natural alignment) then you must specify this using the \_\_packed qualifier when defining the pointer:

\_\_packed int \*pi; // pointer to unaligned int

The ARM compiler does not then use an LDR, but generates code that correctly accesses the value regardless of the alignment of the pointer. This generated code is a sequence of byte accesses or, depending on the compile options, variable alignment-dependent shifting and masking. Therefore a performance and code size penalty is incurred.

You must not access memory-mapped peripheral registers using \_\_packed, because the ARM compiler can use multiple memory accesses to retrieve the data. Therefore, nearby locations can be accessed, which might correspond to other peripheral registers. When bitfields are used, the ARM compiler currently accesses the entire container, not just the field specified.

### 1.2.3 Unaligned fields in structures

In the same way that global variables are located on their natural size boundary, so are the fields in a structure. This means that the compiler often has to insert padding between fields to ensure that fields are aligned. Compile with -W+s to generate a warning when the compiler inserts padding.

Sometimes, you might not want this to occur. You can use the \_\_packed qualifier to create structures without padding between fields, and these structures require unaligned accesses.

If the ARM compiler knows the alignment of a particular structure, it can work out whether or not the fields it is accessing are aligned within a packed structure. In these cases, the compiler carries out the more efficient aligned word or halfword accesses, where possible. Otherwise, the compiler uses multiple aligned memory accesses (LDR, STR, LDM, and STM) combined with fixed shifting and masking to access the correct bytes in memory.

Whether these accesses to unaligned elements are done inline or by calling a function is controlled by using the compiler options -0space (default, calls a function) and -0time (do unaligned access inline).

#### For example:

1. Create a file foo.c that contains:

```

__packed struct mystruct {

int aligned_i;

short aligned_s;

int unaligned_i;

};

struct mystruct S1;

int foo (int a, short b)

{

S1.aligned_i=a;

S1.aligned_s=b;

return S1.unaligned_i;

}

```

2. Compile this using armcc -c -0time foo.c. The code produced is:

```

MOV

r2, r0

LDR

r0, |L1.84|

MOV

r12, r2, LSR #8

STRB

r2,[r0,#0]

STRB

r12,[r0,#1]

MOV

r12, r2, LSR #16

r12,[r0,#2]

STRB

MOV

r12, r2, LSR #24

STRB

r12,[r0,#3]

MOV

r12, r1, LSR #8

STRB

r1,[r0,#4]

STRB

r12,[r0,#5]

ADD

r0, r0, #6

r3, r0, #3

BIC

AND

r0, r0, #3

LDMIA

r3,\{r3,r12\}

MOV

r0, r0, LSL #3

MOV

r3, r3, LSR r0

RSB

r0, r0, #0x20

ORR

r0, r3, r12, LSL r0

ВХ

٦r

```

However, you can give the compiler more information to enable it to know which fields are aligned and which are not. To do this you must declare non-aligned fields as \_\_packed, and remove the \_\_packed attribute from the **struct** itself. This is the recommended approach, and the only way of guaranteeing fast access to naturally aligned members within the **struct**. It is also clearer which fields are non-aligned, but care is needed when adding or deleting fields from the **struct**.

3. Now modify the definition of the structure in foo.c to:

```

struct mystruct {

int aligned_i;

short aligned_s;

__packed int unaligned_i;

};

struct mystruct S1;

```

4. Compile foo.c and the following, more efficient code, is generated:

```

MOV

r2.r0

r0,|L1.32|

LDR

STR

r2,[r0,#0]

STRH

r1,[r0,#4]

r0,{r3,r12}

LDMIB

MOV

r0, r3, LSR #16

ORR

r0, r0, r12, LSL #16

BX

1r

```

The same principle applies to unions. Use the \_\_packed attribute on the components of the union that will be unaligned in memory.

| ——Note |  |

|--------|--|

|        |  |

Any \_\_packed object accessed through a pointer has unknown alignment, even packed structures.

# 1.2.4 Unaligned LDR for accessing halfwords

In some circumstances the ARM compiler can intentionally generate unaligned LDR instructions. In particular, the compiler does this to load halfwords from memory. This is because by using an appropriate address the required halfword can be loaded into the top half of a register and then shifted down to the bottom half. This requires only one memory access whereas doing the same operation using LDRB instructions requires two memory accesses, plus instructions to merge the two bytes. On ARM architecture v3 and earlier, this is typically done for any halfword loads. On ARMv4 and later, this is done less often because dedicated halfword load instructions exist, but unaligned LDR instructions might still be generated. For instance to access an unaligned short within a packed structure.

Such unaligned LDR instructions are only generated by the RVCT compiler if you enable them using the --memaccess +L41 compiler option.

#### 1.2.5 Porting code and detecting unaligned accesses

Legacy C code for other architectures (for example, x86 CISC) might perform accesses to unaligned data using pointers that do not work on ARM processors. This is non-portable code, and such accesses must be identified and corrected to work on RISC architectures, which expect aligned data.

Identifying the unaligned accesses can be difficult, because the use of load or store operations with unaligned addresses gives incorrect behavior. It is difficult to trace which part of the C source is causing the problem.

ARM processors with full *Memory Management Units* (MMUs), for example, the ARM920T<sup>™</sup>, support optional alignment checking, where the processor checks every access to ensure it is correctly aligned. The MMU raises a Data Abort if an incorrectly aligned access occurs.

For simple cores such as the ARM7TDMI®, it is recommended that alignment-checking be implemented within the ASIC/ASSP. You can do this with an additional hardware block that is external to the ARM core, and that monitors the access size and the least significant bits of the address bus for every data access. You can configure the ASIC/ASSP to raise the ABORT signal in the case of an unaligned access. ARM Limited recommends that such logic is included on ASIC/ASSP devices where code is ported from other architectures.

If the system is configured to abort on unaligned accesses, a Data Abort exception handler must be installed. When an unaligned access occurs, the Data Abort handler is entered, and this can identify the erroneous data access instruction, which is located at (r14-8).

When identified, you must fix the data access by changing the C source. These changes can be made conditional using the following:

```

#ifdef __arm

#define PACKED __packed

#else

#define PACKED

#endif

:

PACKED int *pi;

:

```

It is best to minimize accesses to unaligned data because of code size and performance overheads.

# 1.3 Developing for the ARM processors

This book gives information and example code for some of the most common ARM programming tasks. The following sections summarize the subject of each chapter:

- Embedded Software Development

- Using the Procedure call standards on page 1-11

- Interworking ARM and Thumb code on page 1-11

- Mixing C, C++, and Assembly Language on page 1-12

- Handling Processor Exceptions on page 1-12.

#### 1.3.1 Embedded Software Development

Many applications written for ARM-based systems are embedded applications that are contained in ROM and execute on reset. There are a number of factors that you must consider when writing embedded operating systems, or embedded applications that execute from reset without an operating system, including:

- address remapping, for example initializing with ROM at address 0x0000, then remapping RAM to address 0x0000

- initializing the environment and application

- linking an embedded executable image to place code and data in specific locations in memory.

The ARM core usually begins executing instructions from address 0x0000 at reset. For an embedded system, this means that there must be ROM at address 0x0000 when the system is reset. Typically, however, ROM is slow compared to RAM, and often only 8 or 16 bits wide. This affects the speed of exception handling. Having ROM at address 0x0000 means that the exception vectors cannot be modified. A common strategy is to remap ROM to RAM and copy the exception vectors from ROM to RAM after startup. See *ROM/RAM remapping* on page 2-25 for more information.

After reset, an embedded application or operating system must initialize the system, including:

- initializing the execution environment, such as exception vector, stacks, and I/O peripherals

- initializing the application, for example copying initial values of nonzero writable data to the writable data region and zeroing the ZI data region.

See *Initialization sequence* on page 2-23 for more information.

Embedded systems often implement complex memory configurations. For example, an embedded system might use fast, 32-bit RAM for performance-critical code, such as interrupt handlers and the stack, slower 16-bit RAM for application RW data, and ROM for normal application code. You can use the linker scatter-loading mechanism to construct executable images suitable for complex systems. For example, a scatter-load description file can specify the load address and execution address of individual code and data regions. See Chapter 2 *Embedded Software Development* for a series of worked examples, and for information on other issues that affect embedded applications, such as semihosting.

#### 1.3.2 Using the Procedure call standards

The ARM-Thumb Procedure Call Standard (ATPCS) defines register usage and stack conventions that must be followed to enable separately compiled and assembled modules to work together. There are a number of variants on the base standard. The ARM compiler always generates code that conforms to the selected ATPCS variant. The linker selects an appropriate standard C or C++ library to link with, if required.

When developing code for the ARM, you must select an appropriate ATPCS variant. For example, if you are writing code that interworks between ARM and Thumb state you must select the --apcs /interwork option in the compiler and assembler.

If you are writing code in C or C++, you must ensure that you have selected compatible ATPCS options for each compiled module.

If you are writing your own assembly language routines, you must ensure that you conform to the appropriate ATPCS variant. See Chapter 3 *Using the Procedure Call Standard* for more information.

If you are mixing C and assembly language, ensure that you understand the ATPCS implications.

# 1.3.3 Interworking ARM and Thumb code

If you are writing code for ARM processors that support the Thumb 16-bit instruction set, you can mix ARM and Thumb code as required. If you are writing C or C++ code you must compile with the --apcs /interwork option. The linker detects when an ARM function is called from Thumb state, or a Thumb function is called from ARM state and alters call and return sequences, or inserts interworking veneers to change processor state as necessary.

If you are writing assembly language code you must ensure that you comply with the interworking ATPCS variant. There are several ways to change processor state, depending on the target architecture version. See Chapter 4 *Interworking ARM and Thumb* for more information.

#### 1.3.4 Mixing C, C++, and Assembly Language

You can mix separately compiled and assembled C, C++, and ARM assembly language modules in your program. You can write small assembly language routines within your C or C++ code. These routines are compiled using the inline or embedded assembler of the ARM compiler. However, there are a number of restrictions to the assembly language code you can write if you are using the inline or embedded assembler. These restrictions are described in:

- Differences between the inline assembler and armasm on page 5-7

- Restrictions on embedded assembly on page 5-13.

In addition, Chapter 5 Mixing C, C++, and Assembly Language gives general guidelines and examples of how to call between C, C++, and assembly language modules.

#### 1.3.5 **Handling Processor Exceptions**

The ARM processor recognizes the following exception types:

#### Reset

Occurs when the processor reset pin is asserted. This exception is only expected to occur for signaling power-up, or for resetting as if the processor has powered up. A soft reset can be done by branching to the reset vector, 0x0000.

#### **Undefined Instruction**

Occurs if neither the processor, or any attached coprocessor, recognizes the currently executing instruction.

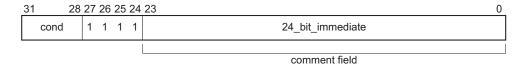

#### **Software Interrupt (SWI)**

This is a user-defined interrupt instruction. It enables a program running in User mode, for example, to request privileged operations that run in Supervisor mode, such as an RTOS function.

#### Prefetch Abort

Occurs when the processor attempts to execute an instruction that has been prefetched from an illegal address. An illegal address is one at which memory does not exist, or one that the memory management subsystem has determined is inaccessible to the processor in its current mode.

**Data Abort** Occurs when a data transfer instruction attempts to load or store data at an illegal address.

#### Interrupt (IRQ)

Occurs when the processor external interrupt request pin is asserted (LOW) and IRQ interrupts are enabled (the I bit in the CPSR is clear).

#### Fast Interrupt (FIQ)

Occurs when the processor external fast interrupt request pin is asserted (LOW) and FIQ interrupts are enabled (the F bit in the CPSR is clear). This exception is typically used where interrupt latency must be kept to a minimum.

In general, if you are writing an application such as an embedded application that does not rely on an operating system to service exceptions, you must write handlers for each exception type.

In cases where an exception type can have more than one source, for example SWI or IRQ interrupts, you can chain exception handlers for each source. See *Chaining exception handlers* on page 6-41 for more information.

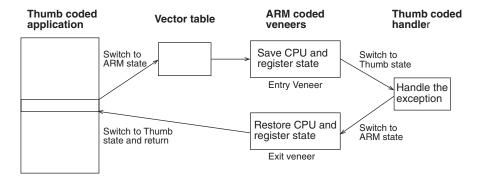

On Thumb-capable processors, the processor switches to ARM state when an exception is taken. You can either write your exception handler in ARM code, or use a veneer to switch to Thumb state. See *The return address and return instruction* on page 6-9 for more information.

Introduction

# Chapter 2 **Embedded Software Development**

This chapter describes how to develop embedded applications with RVCT, with or without a target system present. It contains the following sections:

- About embedded software development on page 2-2

- Default RVCT behavior in the absence of a target system on page 2-4

- Tailoring the C library to your target hardware on page 2-10

- Tailoring the image memory map to your target hardware on page 2-13

- Reset and initialization on page 2-23

- Further memory map considerations on page 2-33.

# 2.1 About embedded software development

Most embedded applications are initially developed in a prototype environment with resources that differ from those available in the final product. Therefore, it is important to consider the processes involved in moving an embedded application from one that relies on the facilities of the development or debugging environment to a system that runs standalone on target hardware.

When developing embedded software using RVCT, you must consider the following:

- How the C library uses hardware.

- Some C library functionality executes by using debug environment resources. If used, you must re-implement this functionality to make use of target hardware.

- RVCT has no inherent knowledge of the memory map of any given target. You

must tailor the image memory map to the memory layout of the target hardware.

- An embedded application must perform some initialization before the main application can be run. A complete initialization sequence requires code that you implement as well as RVCT C library initialization routines.

### 2.1.1 Example code

To illustrate the topics covered in this chapter, associated example projects are provided. The code for the Dhrystone builds described in this chapter is in the directory <code>Examples\_directory</code>\emb\_sw\_dev. Each build is in a separate directory, and provides an example of the techniques discussed in successive sections of this chapter. Specific information regarding each build can be found in the Example code sections.

The Dhrystone benchmarking program provides the code base for the example projects. Dhrystone was chosen because it enables many of the concepts described in this chapter to be illustrated.

The example projects are tailored to run on the ARM Integrator development platform. However, the principles illustrated by the examples apply to any target hardware.

| —— Note ———                                                                             |

|-----------------------------------------------------------------------------------------|

| The focus of this chapter is not specifically the Dhrystone program, but the steps that |

| must be taken to enable it run on a fully standalone system. For further discussion of  |

| Dhrystone as a benchmarking tool, see Application Note 93 - Benchmarking with           |

| ARMulator. You can find the ARM Application Notes in the Documentation area of the      |

| ARM website at http://www.arm.com.                                                      |

#### Running the Dhrystone builds on an Integrator

To run the Dhrystone builds described in this chapter on an Integrator, you must:

- Perform ROM/RAM remapping. To achieve this, run the Boot Monitor by setting switches 1 and 4 on, then reset the board.

- Set top\_of\_memory to 0x40000, or fit a DIMM memory module. If this is not done, the stack, which defaults to 0x80000, might not be in valid memory.

To set top of memory in RealView Debugger, for example, open the Connection Properties for the connection. In the Advanced\_Information\Default\ARM\_config group, set Top\_memory to the required value, then save the settings.

# 2.2 Default RVCT behavior in the absence of a target system

When you begin working on software for an embedded application, you might not be aware of the full technical specifications of the target hardware. For example, you might not know the details of target peripheral devices, the memory map, or even the processor itself.

To enable you to proceed with software development before such details are known, the RVCT tools have a default behavior that enables you to start building and debugging application code immediately. It is useful to be aware of this default behavior, so that you appreciate the steps necessary to move from a default build to a fully standalone application.

### 2.2.1 Semihosting

In the RVCT C Library, support for some ISO C functionality is provided by the host debugging environment. The mechanism that provides this functionality is known as *semihosting*.

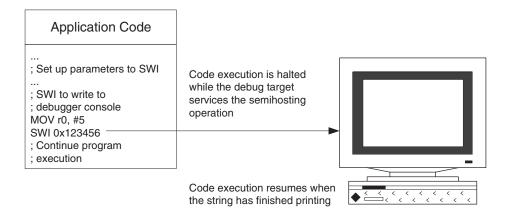

Semihosting is implemented by a set of defined software interrupt (SWI) operations. When a semihosting SWI is executed, the debug agent identifies it and briefly suspends program execution. The semihosting operation is then serviced by the debug agent before code execution is resumed. Therefore, the task performed by the host itself is transparent to the program.

Figure 2-1 shows an example of semihosting operation, which prints a string to the debugger console.

Figure 2-1 Example semihosting operation

\_\_\_\_\_ Note \_\_\_\_\_

For more information on semihosting, see the chapter on Semihosting in the *RealView Compilation Tools v2.0 Compiler and Libraries Guide*.

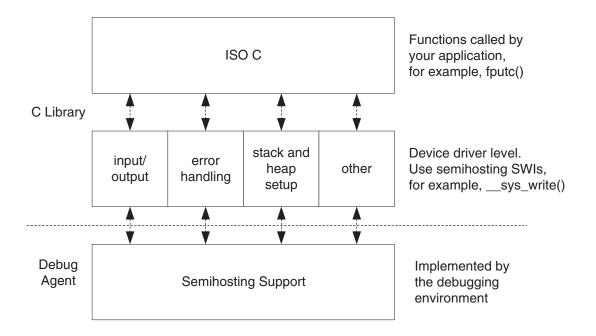

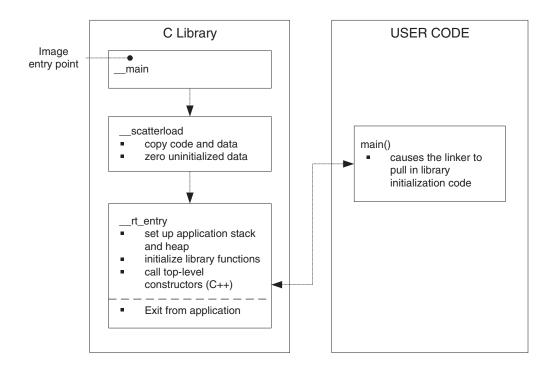

#### 2.2.2 C library structure

Conceptually, the C library can be divided into functions that are part of the ISO C Language specification, and functions that provide support to the ISO C language specification. This is illustrated in Figure 2-2.

Figure 2-2 C library structure

Support for some ISO C functionality is provided by the host debugging environment at the device driver level of support functions.

For example, the RVCT C library implements the ISO C printf() family of functions by writing to the debugger console window. This functionality is provided by calling \_\_sys\_write(). This is a support function that executes a semihosting SWI, that results in a string being written to the console.

#### 2.2.3 Default memory map

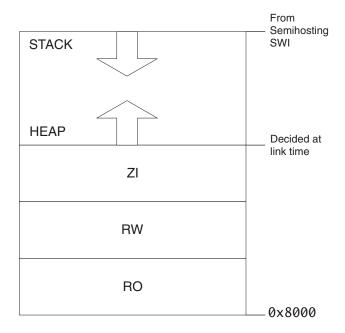

In an image where you have not described the memory map, RVCT places code and data according to a default memory map, as shown in Figure 2-3.

Figure 2-3 Default memory map

The default memory map can be described as follows:

- The image is linked to load and run at address 0x8000. All RO (Read Only) sections are placed first, followed by RW (Read-Write) sections then ZI (Zero-Initialized) sections.

- The heap follows directly on from the top of the ZI section, so the exact location is decided at link time.

- The stack base location is provided by a semihosting operation during application startup. The value returned by this semihosting operation depends on the debug environment:

- ARMulator returns the value set in the configuration file peripherals.ami. The

default is 0x08000000.

- Multi-ICE returns the value of the debugger internal variable top\_of\_memory. The

default is 0x00080000.

#### 2.2.4 Linker placement rules

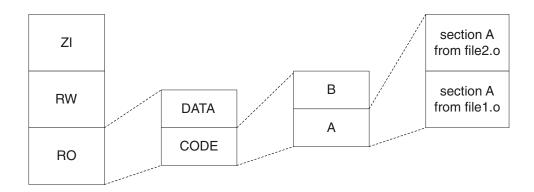

The linker observes a set of rules, shown in Figure 2-4, to decide where in memory code and data is located.

Figure 2-4 Linker placement rules

The image is organized first of all by attribute - RO at the lowest memory address, then RW, then ZI. Within each attribute code precedes the data.

From there, the linker places input sections alphabetically by name. Input section names correspond with assembler AREA directives.

In input sections, code and data from individual objects are placed in the order the object files are specified on the linker command line.

ARM Limited does not recommend relying on these rules for precise placement of code and data. Instead, you must use the scatter-loading mechanism for full control of placement of code and data. See *Tailoring the image memory map to your target hardware* on page 2-13.

#### 2.2.5 Application startup

In most embedded systems, an initialization sequence executes to setup the system before the main task is executed.

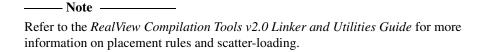

The default RVCT initialization sequence is shown in Figure 2-5.

Figure 2-5 Default RVCT initialization sequence

At a high level, the initialization sequence can be divided into three functional blocks. \_\_main branches directly to \_\_scatterload. \_\_scatterload is responsible for setting the run-time image memory map, whereas \_\_rt\_entry (run-time entry) is responsible for initializing the C library.

\_\_scatterload carries out code and data copying, and zeroing of ZI data. This step is always done for zeroing of ZI data and RW data is unchanged.

\_\_scatterload branches to \_\_rt\_entry. This sets up the application stack and heap, initializes library functions and their static data, and calls any constructors of globally declared objects (C++ only).

\_\_rt\_entry then branches to main(), the entry to your application. When the main application has finished executing, \_\_rt\_entry shuts down the library, then hands control back to the debugger.

The function label main() has a special significance in RVCT. The presence of a main() function forces the linker to link in the initialization code in \_\_main and \_\_rt\_entry. Without a function labeled main() the initialization sequence is not linked in, and as a result, some standard C library functionality is not supported.

## 2.2.6 Example code for Build 1

Build 1 is a default build of the Dhrystone Benchmark. Therefore, it adheres to the default RVCT behavior described in this section. See *Running the Dhrystone builds on an Integrator* on page 2-3, and the example build files in <code>Examples\_directory\emb\_sw\_dev\build1</code>.

# 2.3 Tailoring the C library to your target hardware

By default the C library makes use of semihosting to provide device driver level functionality, enabling a host computer to act as an input and an output device. This is useful because development hardware often does not have all the input and output facilities of the final system.

# 2.3.1 Retargeting the C library

You can provide your own implementation of C Library functions that make use of target hardware, and that are automatically linked in to your image in favor of the C library implementations. This process, known as retargeting the C library, is shown in Figure 2-6.

Figure 2-6 Retargeting the C library

For example, you might have a peripheral I/O device such as a UART, and you might want to override the library implementation of fputc(), that writes to the debugger console, with one that outputs to the UART. Because this implementation of fputc() is linked in to the final image, the entire printf() family of functions print out to the UART.

An example implementation of fputc() is shown in Example 2-1 on page 2-11.

The example redirects the input character parameter of fputc() to a serial output function sendchar(), that is assumed to be implemented in a separate source file. In this way, fputc() acts as an abstraction layer between target dependent output and the C library standard output functions.

#### Example 2-1 Implementation of fputc()

```

extern void sendchar(char *ch);

int fputc(int ch, FILE *f)

{    /* e.g. write a character to an UART */

char tempch = ch;

sendchar(&tempch);

return ch;

}

```

### 2.3.2 Avoiding C library semihosting

In a standalone application, you are unlikely to support semihosting SWI operations. Therefore, you must be certain that no C library semihosting functions are being linked into your application.

To ensure that no functions that use semihosting SWIs are linked in from the C library, you must import the symbol \_\_use\_no\_semihosting\_swi. This can be done in any C or assembler source file in your project as follows:

- In an assembler module, use the IMPORT directive:

IMPORT \_\_use\_no\_semihosting\_swi

If functions that use semihosting SWIs are still being linked in, the linker reports the following error:

```

Error: L6200E: Symbol __semihosting_swi_guard multiply defined (by use_semi.o and use_no_semi.o).

```

To identify these functions, link using the -verbose option. In the resulting output, C library functions are tagged with \_\_I\_use\_semihosting\_swi, for example.

```

Loading member sys_exit.o from c_a__un.l.

definition: _sys_exit

reference: __I_use_semihosting_swi

```

2.3.3

|            | You must provide your own implementations of these functions.                                                                                                                                                                                                                                                                |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | Note                                                                                                                                                                                                                                                                                                                         |

|            | The linker does not report any semihosting SWI-using functions in the your application code. An error only occurs if a semihosting SWI-using function is linked in from the C library.                                                                                                                                       |

|            | A full list of C library functions that use semihosting SWIs is available in the <i>RealView Compilation Tools v2.0 Compiler and Libraries Guide</i> .                                                                                                                                                                       |

| Example co | ode for Build 2                                                                                                                                                                                                                                                                                                              |

|            | Build 2 of the example uses the hardware of the Integrator platform for clocking and string I/O. See the example build files in <i>Examples_directory</i> \emb_sw_dev\build2.                                                                                                                                                |

|            | The following changes have been made to Build 1 of the example project:                                                                                                                                                                                                                                                      |

|            | C Library Retargeting                                                                                                                                                                                                                                                                                                        |

|            | A retargeted layer of ISO C functions has been added. These include standard input/output functionality, clock functionality, as well as some additional error signaling and program exit.                                                                                                                                   |

|            | Target Dependent Device Driver                                                                                                                                                                                                                                                                                               |

|            | A device driver layer that interacts directly with target hardware peripherals has been added.                                                                                                                                                                                                                               |

|            | See Running the Dhrystone builds on an Integrator on page 2-3.                                                                                                                                                                                                                                                               |

|            | The symboluse_no_semihosting_swi is not imported into this project. This is because a semihosting SWI is executed during C library initialization to set up the application stack and heap location. Retargeting stack and heap setup is covered in detail in <i>Placing the stack and heap</i> on page 2-18.                |

|            | Note                                                                                                                                                                                                                                                                                                                         |

|            | To see the output, a terminal or terminal emulator (such as Hyperterminal) must be connected to serial port A. The serial port settings must be set to 38400 baud, no parity, 1 stop bit and no flow control. The terminal must be configured to append line feeds to incoming line ends, and echo typed characters locally. |

|            |                                                                                                                                                                                                                                                                                                                              |

# 2.4 Tailoring the image memory map to your target hardware

In your final embedded system, without semihosting functionality, you are unlikely to use the default memory map provided by RVCT. Your target hardware usually has several memory devices located at different address ranges. To make the best use of these devices, you must have separate views of memory at load and run-time.

## 2.4.1 Scatter-loading

Scatter-loading enables you to describe the load-time and run-time location of code and data in memory in a textual description file known as a *scatter-loading description file*. The file is passed to the linker on the command line using the -scatter option. For example:

armlink -scatter scat.scf file1.o file2.o

The scatter-loading description file describes to the linker the desired location of code and data at both load-time and run-time, in terms of addressed memory regions.

# Scatter-loading regions

Scatter-loading regions fall into two categories:

- Load Regions that contain application code and data at reset and load time.

- Execution Regions that contain code and data while the application is executing.

One or more execution regions are created from each load region during application startup.

All code and data in the image falls into exactly one load region, and one execution region.

During startup, C library initialization code in \_\_main carries out the copying and zeroing of code and data necessary to move from the image load view to the execute view.

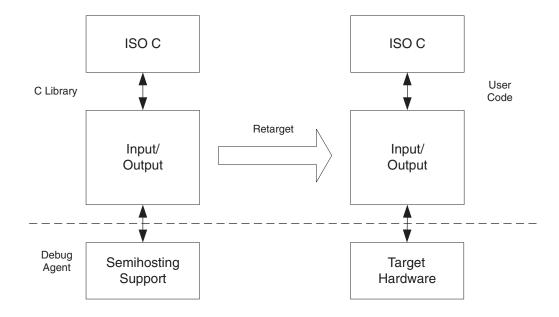

## 2.4.2 Scatter-loading description file syntax

The scatter-loading description file syntax reflects the functionality provided by scatter-loading itself. Figure 2-7 shows the file syntax.

A region is defined by a header tag that contains, as a minimum, a name for the region and a start address. Optionally, a maximum length and various attributes can be added.

Figure 2-7 Scatter-loading description file syntax

The contents of the region depend on the type of region:

- Load regions must contain at least one execution region. In practice, there are usually several execution regions per load region.

- Execution regions must contain at least one code or data section, unless a region is declared with the EMPTY attribute (see *Using the scatter-file EMPTY attribute* on page 2-37). Non-EMPTY regions usually contain source or library object files. The wildcard (\*) syntax can be used to group all sections of a given attribute not specified elsewhere in the scatter-loading description file.

# 2.4.3 Scatter-loading description file example

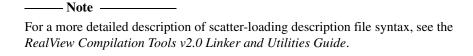

Figure 2-8 illustrates a simple example of scatter-loading.

This example has one load region containing all code and data, starting at address zero. From this load region two execution regions are created. One contains all RO code and data, which executes at the same address at which it is loaded. The other is at address 0x10000, which contains all RW and ZI data.

Figure 2-8 Simple scatter-loading example

Example 2-2 shows the description file that describes the above memory map.

Example 2-2 Simple scatter-loading description file

```

ROM_LOAD 0x0000 0x4000

{

ROM_EXEC 0x0000 0x4000; Root region

{

* (+R0); All code and constant data

}

```

## 2.4.4 Placing objects in a scatter-loading description file

For most images, you control the placement of specific code and data sections, rather than grouping all attributes together as in the previous example. You can do this by specifying individual objects directly in the description file, instead of relying only on the wildcard syntax.

The ordering of objects in a description file execution region does not affect their ordering in the output image. The linker placement rules described in *Linker placement rules* on page 2-7 apply to each execution region.

To override the standard linker placement rules, you can use the +FIRST and +LAST scatter-loading directives. Example 2-3 shows a scatter-loading description file that places the vector table at the beginning of an execution region. In the example, the area Vect in vectors o is placed at address 0x0000. Refer to the *RealView Compilation Tools v2.0 Linker and Utilities Guide* for further information on placing objects in scatter-loading description files.

## Example 2-3 Placing a section

```

ROM_LOAD 0x0000 0x4000

{

ROM_EXEC 0x0000 0x4000

{

vectors.o (Vect, +FIRST)

* (+RO)

}

; more exec regions...

}

```

## 2.4.5 Root regions

A *root region* is an execution region with a load address that is the same as its execution address. Each scatter-loading description file must have at least one root region.

One restriction placed on scatter-loading is that the code and data responsible for creating execution regions, for example, copying and zeroing code and data, cannot itself be copied to another location. As a result, the following sections must be included in a root region:

- \_\_main.o that contains the code that copies code and data

- Region\$\$Table and ZISection\$\$Table sections containing the addresses of the code and data to be copied.

Because these sections are attributed as read-only, they are grouped by the \* (+R0) wildcard syntax. As a result, if \* (+R0) is specified in a non-root region, these sections must be explicitly declared in a root region. This is shown in Example 2-4.

Example 2-4 Specifying a root region

Failing to include \_\_main.o, Region\$\$Table, and ZISection\$\$Table in a root region results in the linker generating the following error messages:

```

Error: L6202E: Section Region$$Table cannot be assigned to a non-root region.

Error: L6202E: Section ZISection$$Table cannot be assigned to a non-root region.

```

## 2.4.6 Placing the stack and heap

Scatter-loading provides a method for specifying the placement of code and statically allocated data in your image. This section covers how to place the application stack and heap.

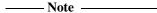

The application stack and heap are setup during C library initialization. You can tailor stack and heap placement by retargeting the routine responsible for stack and heap setup. In the RVCT C library, this routine is \_\_user\_initial\_stackheap().

Figure 2-9 shows the C library initialization process with a retargeted \_\_user\_initial\_stackheap().

Figure 2-9 Retargeting \_\_user\_initial\_stackheap()

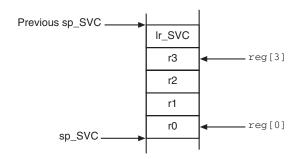

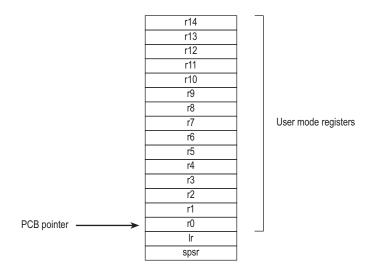

\_\_user\_initial\_stackheap() can be coded in C or ARM assembler. It must return the following parameters:

- heap base in r0

- stack base in r1

- heap limit in r2, if required

- stack limit in r3, if required.

You must re-implement \_\_user\_initial\_stackheap() if you are scatter-loading your image. Otherwise, the linker generates the following error:

Error: L6218E: Undefined symbol Image\$\$ZI\$\$Limit (referred from sys\_stackheap.o)

## 2.4.7 Run-time memory module

RVCT provides two possible run-time memory models:

- One-region model, which is the default

- Two-region model on page 2-20.

In both run-time memory models, the stack grows unchecked by default. You can choose to enable software stack checking in your image by compiling all modules with the compiler option --apcs /swst. If you are using a two-region model, you must also specify a stack limit in your implementation of \_\_user\_initial\_stackheap().

Enabling software stack checking introduces a substantial code size and performance overhead, because the value of the stack pointer must be checked against the stack limit with each function call. It also uses register r10, so is not generally recommended for embedded systems.

Both these examples are suitable for the Integrator system.

# One-region model

In the default, *one-region model*, the application stack and heap grow towards each other in the same region of memory. In this case, the heap is checked against the value of the stack pointer when new heap space is allocated (that is, when malloc() is called).

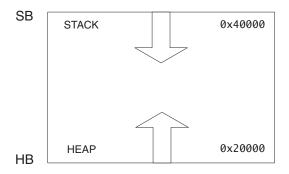

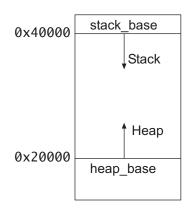

Example 2-5 and Figure 2-10 on page 2-20 show an example of \_\_user\_initial\_stackheap() implementing a simple one-region model, where the stack grows downwards from address 0x40000, and the heap grows upwards from 0x20000. The routine loads the appropriate values into the registers r0 and r1, and then returns. r2 and r3 remain unchanged, because a heap limit and stack limit are not used in a one-region model.

#### Example 2-5 One-region model routine

```

EXPORT __user_initial_stackheap

__user_initial_stackheap

LDR r0, =0x20000 ;HB

```

```

LDR r1, =0x40000 ;SB; r2 not used (HL); r3 not used (SL)

MOV pc, lr

```

Figure 2-10 One-region model

# Two-region model

Your system design might require the stack and heap to be placed in separate regions of memory. For instance you might have a small block of fast RAM that you want to reserve for stack use only. To inform RVCT that you want to use a *two-region model*, you must import the symbol \_\_use\_two\_region\_memory using the assembler IMPORT directive. The heap is then checked against a dedicated heap limit, that is set up by \_\_user\_initial\_stackheap().

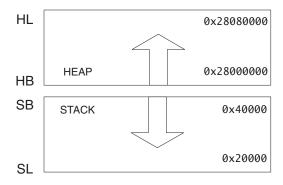

Example 2-6 and Figure 2-11 on page 2-21 show an example of implementing a two-region model. The stack grows downwards from 0x40000 towards a limit of 0x20000. To make use of this stack limit, all modules using this implementation must be compiled for software stack checking. The heap grows upwards from 0x28000000 to 0x28080000.

#### **Example 2-6 Two-region model routine**

```

IMPORT __use_two_region_memory

EXPORT __user_initial_stackheap

__user_initial_stackheap

LDR r0, =0x28000000 ;HB

LDR r1, =0x40000 ;SB

```

```

LDR r2, =0x28080000 ;HL

LDR r3, =0x20000 ;SL

MOV pc, 1r

```

Figure 2-11 Two-region model

# 2.4.8 Example code for Build 3

Build 3 of the example implements scatter-loading, and contains a retargeted \_\_user\_initial\_stackheap(). See the example build files in Examples\_directory\emb\_sw\_dev\build3.

The following modifications have been made to Build 2 of the example project:

#### **Scatter-loading**

A simple scatter-loading description file is passed to the linker.

## **Retargeted** \_\_user\_initial\_stackheap()

You have the option of selecting either a one-region or a two-region implementation. The default build is one-region. You can select the two-region implementation by defining two\_region at the build step.

#### **Avoiding C library Semihosting**

The symbol \_\_use\_no\_semihosting\_swi is imported into this build, because there are no longer any C library semihosting functions present in the image.

See Running the Dhrystone builds on an Integrator on page 2-3.

| Note                                                                                   |

|----------------------------------------------------------------------------------------|

| To avoid using semihosting for clock(), this is retargeted to read the Real Time Clock |

| (RTC) on the Integrator AP. This has a resolution of one second, so the results from   |

| Dhrystone are not precise. This mechanism is improved in Build 4.                      |

## 2.5 Reset and initialization

This chapter has so far assumed that execution begins at \_\_main, the entry point to the C library initialization routine. In fact, any embedded application on your target hardware performs some system-level initialization at startup. This section describes this in more detail.

# 2.5.1 Initialization sequence

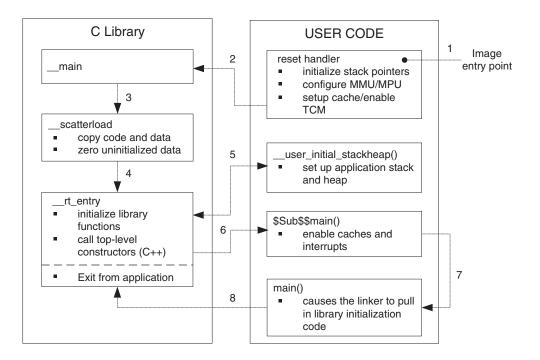

Figure 2-12 shows a possible initialization sequence for an ARM-based embedded system.

Figure 2-12 Initialization sequence

The reset handler in Figure 2-12 executes immediately on system startup. The block of code labeled \$Sub\$\$main() executes immediately before entering the main application.

The reset handler is a short module coded in assembler that is executed on system reset. As a minimum, your reset handler initializes stack pointers for the modes that your application is running in. For cores with local memory systems, such as caches, *Tightly Coupled Memories* (TCMs), *Memory Management Units* (MMUs) and *Memory*

*Protection Units* (MPUs), some configuration must be done at this stage in the initialization process. After executing, the reset handler typically branches to \_\_main to begin the C library initialization sequence.

There are some components of system initialization, for example the enabling of interrupts, that are generally performed after the C library initialization code has finished executing. The block of code labeled \$Sub\$\$main() performs these tasks immediately before the main application begins executing.

See *The vector table* for a more detailed description of the various components of the initialization sequence.

#### 2.5.2 The vector table

All ARM systems have a *vector table*. The vector table does not form part of the initialization sequence, but it must be present for any exception to be serviced.

The code in Example 2-7 imports the various exception handlers, that might be coded in other modules. The vector table is a list of branch instructions to the various exception handlers.

The FIQ handler is placed at address 0x1C directly. This avoids having to execute a branch to the FIQ handler, so optimizing FIQ response time.

## **Example 2-7 Importing exception handlers**

```

AREA Vectors, CODE, READONLY

IMPORT Reset_Handler

; import other exception handlers

; ...

ENTRY

B Reset_Handler

B Undefined_Handler

B SWI_Handler

B Prefetch_Handler

B Data_Handler

B Data_Handler

NOP; Reserved vector

B IRQ_Handler

; FIQ_Handler will follow directly

END

```

The vector table is marked with the label ENTRY. This label informs the linker that this code is a possible entry point, and so it cannot be removed from the image at link time. You must select one of the possible image entry points as the true entry point to your application using the -entry linker option. Refer to the *RealView Compilation Tools v2.0 Linker and Utilities Guide* for more information.

# 2.5.3 ROM/RAM remapping

You must consider what sort of memory your system has at address 0x0000, the address of the first instruction executed.

| ——— Note |  |

|----------|--|

|----------|--|

This section assumes that the ARM core begins fetching instructions at 0x0000, which is the norm for ARM core based systems. However, some ARM cores can be configured to begin fetching instructions from 0xFFFF0000.

There has to be a valid instruction at 0x0000 at startup, so you must have non-volatile memory located at 0x0000 at the moment of reset.

One way to achieve this is to have ROM located at 0x0000. However, there are some drawbacks to this configuration. Access speeds to ROM are generally slower than to RAM, and your system might suffer if there is too great a performance penalty when branching to exception handlers. Also, locating the vector table in ROM does not enable you to modify it at run time.

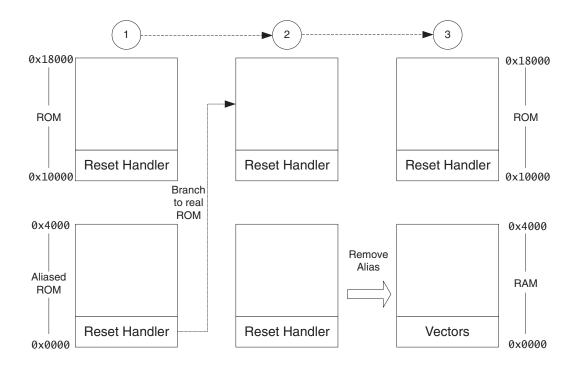

Another solution is shown in Figure 2-13 on page 2-26. ROM is located at address 0x10000, but this memory is aliased to zero by the memory controller at reset. Following reset, code in the reset handler branches to the real address of ROM. The memory controller then removes the aliased ROM, so that RAM is shown at address 0x0000. In \_\_main, the vector table is copied into RAM at 0x0000, so that exceptions can be serviced.

Figure 2-13 ROM/RAM remap

Example 2-8 on page 2-27 shows how you might implement ROM/RAM remapping in an ARM assembler module. The constants shown here are specific to the Integrator platform, but the same method is applicable to any platform that implements ROM/RAM remapping in a similar way.

The first instruction is a jump from aliased ROM to real ROM. This can be done because the label Instruct\_2 is located at the real ROM address.

After this step, the alias of ROM is removed by inverting the remap bit of the Integrator Core Module control register.

This code is normally executed immediately after system reset. Remapping must be completed before C library initialization code can be executed.

| —— Note ———                                                        |             |

|--------------------------------------------------------------------|-------------|

| In systems with MMUs, remapping can be implemented through MMU cor | ıfiguration |

| at system startup.                                                 |             |

## Example 2-8 ROM/RAM remapping

```

; --- Integrator CM control reg

CM_ctl_req

EQU 0x1000000C

; Address of CM Control Register

Remap_bit

EOU 0x04

; Bit 2 is remap bit of CM_ctl

ENTRY

: Code execution starts here on reset

; On reset, an alias of ROM is at 0x0, so jump to 'real' ROM.

pc, =Instruct_2

LDR

Instruct_2

; Remap by setting Remap bit of the CM_ctl register

r1, =CM_ctl_reg

LDR

LDR

r0, [r1]

ORR

r0, r0, #Remap_bit

STR

r0, [r1]

; RAM is now at 0x0.

; The exception vectors must be copied from ROM to RAM (in __main)

; Reset_Handler follows on from here

```

# 2.5.4 Local memory setup considerations

Many ARM processor cores have on-chip memory systems, such as MMUs or MPUs. These devices are normally setup and enabled during system startup. Therefore, the initialization sequence of cores with local memory systems requires special consideration.

As described in this chapter, C library initialization code in \_\_main is responsible for setting up the execution time memory map of the image. Therefore, the run-time memory view of the processor core must be set up before branching to \_\_main. This means that any MMU or MPU must be set up and enabled in the reset handler.

TCMs must also be enabled before branching to \_\_main (normally before MMU/MPU setup), because you generally want to scatter-load code and data into TCMs. You must be careful that you do not have to access memory that is masked by the TCMs when they are enabled.

You also risk problems with cache coherency if caches are enabled before branching to \_\_main. Code in \_\_main copies code regions from their load address to their execution address, essentially treating instructions as data. As a result, some instructions can be cached in the data cache, in which case they are not visible to the instruction path.

To avoid these coherency problems, enable caches after the C library initialization sequence finishes executing.

## 2.5.5 Scatter-loading and memory setup

In a system where the reset-time memory view of the core is altered, either through ROM/RAM remapping or MMU configuration, the scatter-loading description file must describe the image memory map after remapping has taken place.

The description file in Example 2-9 relates to the example in *ROM/RAM remapping* on page 2-25 after remapping.

#### Example 2-9

```

ROM_LOAD 0x10000 0x8000

{

ROM_EXEC 0x10000 0x8000

{

reset_handler.o (+RO, +FIRST) ; executed on hard reset

...

}

RAM 0x0000 0x4000

{

vectors.o (+RO, +FIRST) ; vector table copied from ROM to RAM at zero

...

}

}

```

The load region ROM\_LOAD is placed at 0x10000, because this indicates the load address of code and data after remapping has occurred.

## 2.5.6 Stack pointer initialization

As a minimum, your reset handler must assign initial values to the stack pointers of any execution modes that are used by your application.

In Example 2-10, the stacks are located at stack\_base. This symbol can be a hard coded address, or it can be defined in a separate assembler source file and located by a scatter-loading description file. Details of how this is done are given in *Placing the stack and heap in the scatter-loading description file* on page 2-34.

The example allocates 256 bytes of stack for FIQ and IRQ mode, but you can do the same for any other execution mode. To set up the stack pointers, enter each mode (interrupts disabled) and assign the appropriate value to the stack pointer. To make use of software stack checking, you also have to set up a stack limit here.

Stack pointer and stack limit values set up in the reset handler are automatically passed as parameters to \_\_user\_initial\_stackheap() by C library initialization code. Therefore, these values must not be modified by \_\_user\_initial\_stackheap().

## Example 2-10 Initializing stack pointers

```

; --- Amount of memory (in bytes) allocated for stacks

Len_FIQ_Stack

EQU

256

Len_IRQ_Stack

EOU

256

Offset_FIQ_Stack

EQU

Offset_IRQ_Stack

EQU

Offset_FIQ_Stack + Len_FIQ_Stack

Reset Handler

; stack_base could be defined above, or located in a description file

LDR

r0, stack_base :

; Enter each mode in turn and set up the stack pointer

CPSR_c, #Mode_FIQ:OR:I_Bit:OR:F_Bit

MSR

SUB

sp, r0, #Offset_FIQ_Stack

MSR

CPSR_c, #Mode_IRQ:OR:I_Bit:OR:F_Bit

SUB

sp, r0, #Offset_IRQ_Stack

; Set up stack limit if needed

LDR

r10, stack_limit

```

Example 2-11 shows an implementation of \_\_user\_initial\_stackheap() that you can use with the stack pointer setup shown in Example 2-10 on page 2-29.

#### Example 2-11

```

IMPORT heap_base

EXPORT __user_initial_stackheap()

__user_initial_stackheap()

; heap base could be hard coded, or placed by description file

LDR    r0,=heap_base

; r1 contains SB value

MOV    pc,lr

```

#### 2.5.7 Hardware initialization

In general, it is beneficial to separate all system initialization code from the main application. However, some components of system initialization, for example enabling of caches and interrupts, must occur after executing C library initialization code.

You can make use of the \$Sub and \$Super function wrapper symbols to effectively insert a routine that is executed immediately before entering the main application. This mechanism enables you to extend functions without altering the source code.

Example 2-12 shows how \$Sub and \$Super can be used in this way. The linker replaces the function call to main() with a call to \$Sub\$\$main(). From there you can call a routine that enables caches, and another to enable interrupts.