# **Application Note 133**

## Using VFP with RVDS

Document number: ARM DAI 0133C Issued: July 2008 Copyright ARM Limited 2004-2008

Copyright © 2004-2008 ARM Limited. All rights reserved.

## Application Note 133 Using VFP with RVDS

Copyright © 2004-2008 ARM Limited. All rights reserved.

## **Release information**

The following changes have been made to this Application Note:

| Date           | Issue | Change                                                                                                                                                                                                                                                           |

|----------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| September 2004 | А     | First release for RVDS 2.1                                                                                                                                                                                                                                       |

| December 2005  | В     | Revised for RVDS 2.2 SP1 and RVDS 3.0:<br>- Deprecated VFP1v1 and VFP10rev0<br>- Removed all references to controlbuffer_h.s<br>- Updated examples for ARM1136JF-S<br>- Updated RVD screenshots for ARM1136JF-S<br>- Added references to ARMv7, VFPv3, Cortex-A8 |

| July 2008      | С     | Revised for RVDS 3.1 and 4.0:<br>- Added references to Cortex-A9, Cortex-R4F, VFPv3-D16<br>- Added references tofp16_format switch andfp16 data type<br>- Removed references to obsolete CM10rev0                                                                |

## **Proprietary notice**

Words and logos marked with <sup>®</sup> or <sup>™</sup> are registered trademarks or trademarks owned by ARM Limited. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

## **Confidentiality status**

This document is Open Access. This document has no restriction on distribution.

## Feedback on this Application Note

If you have any comments on this Application Note, please send email to errata@arm.com giving:

- the document title

- the document number

- the page number(s) to which your comments refer

- an explanation of your comments.

General suggestions for additions and improvements are also welcome.

Change history

## **Table of Contents**

| 1 | Intro                                  | duction                                                                                                                                                                                                                   | 2                          |

|---|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|   | 1.1<br>1.2<br>1.3<br>1.4               | Floating-point support<br>VFP variants<br>What does the application note cover?<br>Patches                                                                                                                                | 2<br>3                     |

| 2 | Prod                                   | ucing Code to Run on a VFP System                                                                                                                                                                                         | 4                          |

|   | 2.1<br>2.2<br>2.3                      | Using the compiler<br>Using the assembler<br>Floating point linkage and thefpu option                                                                                                                                     | 6                          |

| 3 | VFP                                    | System Initialization                                                                                                                                                                                                     | 9                          |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6 | Provide the VFP Support Code<br>Install the VFP support code<br>Set up the undefined mode stack<br>Enable VFP<br>Installation routine<br>FPSCR settings                                                                   | 9<br>9<br>11<br>12<br>13   |

| 4 | RunF                                   | Fast Mode Initialisation                                                                                                                                                                                                  | 15                         |

| 5 | Debu                                   | ugger Setup for VFP                                                                                                                                                                                                       | 17                         |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6 | Configuring RVISS (ARMulator) for VFP in RVD<br>Configuring ISSM for VFP in RVD<br>Enabling VFP registers in RVD<br>Configuring ARMulator for VFP in AXD<br>Configuration of AXD for VFP<br>Enabling VFP registers in AXD | 20<br>21<br>22<br>23       |

| 6 | Exan                                   | nple application using VFP                                                                                                                                                                                                | 26                         |

| 7 | VFP                                    | Support Code                                                                                                                                                                                                              | 27                         |

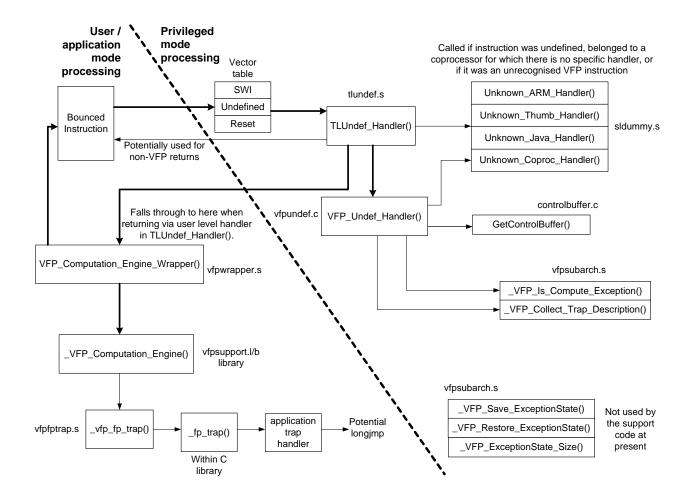

|   | 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6 | Features of the VFP Support Code<br>Overview of processing a bounced VFP instruction<br>Processing a bounced VFP instruction<br>Context switching VFP state<br>VFP Computation Engine<br>VFP Subarchitecture Support      | 27<br>29<br>30<br>35<br>35 |

| 8 | Refe                                   | rences                                                                                                                                                                                                                    | 39                         |

|   |                                        |                                                                                                                                                                                                                           |                            |

## 1 Introduction

## 1.1 Floating-point support

The ARM processor core does not contain floating-point hardware. Instead floating-point can be done in one of three ways:

- The software floating-point library (fplib), supplied as part of the RealView Developer Suite C library, provides functions that can be called to implement floating-point operations using no additional hardware. This is the default tools option and most systems have historically made use of this.

- 2) A hardware coprocessor attached to the ARM processor core that implements a number of instructions that provide the required floating-point operations. To date ARM has produced three such coprocessor architectures:

- Floating-point Accelerator (FPA), as used for example in the ARM7500FE. This is now obsolete.

- Vector Floating-Point (VFP), which was originally developed as part of the ARM10 program. This implements IEEE floating-point and supports single and double precision, but not extended precision.

- Floating Point Unit (FPU), introduced with the Cortex-A9 and Cortex-R4F. This implements support for single and double precision as well as halfprecision conversion. Vector operations are not supported in hardware.

- 3) Software Floating-Point Emulation (FPE), where code is still generated to use coprocessor floating-point instructions, but the actual coprocessor hardware does not exist in the system to implement them. Instead an emulation of the coprocessor is provided as system support code which is attached to the ARM processor core's undefined instruction trap.

In some cases, implementation of floating-point requires a combination of VFP/FPA/FPU hardware (to execute the common cases) and software (to deal with the uncommon and exceptional cases). This does not apply for VFPv3 or in "RunFast" mode where software (in the form of support code) is not required to handle uncommon or exceptional cases. See section 4 for more details on "RunFast" mode.

## 1.2 VFP variants

VFP is a floating-point architecture which can provide both single and double precision operations. Many operations may also take place in scalar form or in vector form. At the time of writing several versions of the architecture have been implemented:

- VFPv1 was implemented in the VFP10 revision 0 silicon (as provided by the ARM10200). Support for this was deprecated in RVDS 2.1 and removed from RVDS 2.2 onwards.

- VFPv2 has been implemented in the VFP10 revision 1 (as provided by the ARM10200E), the VFP9-S (as available as a separately licensable option for ARM926/946/966) and the VFP11 (as provided in the ARM1136JF-S and ARM1176JZF-S).

- VFPv3 is backwards compatible with VFPv2 except that VFPv3 cannot trap floatingpoint exceptions and therefore requires no software support code. VFPv3 is implemented on ARM architecture v7 and later (e.g. Cortex-A8). Some VFPv3 variants are:

- VFPv3U is an implementation of VFPv3 that can trap floating-point exceptions and requires software support code.

- VFPv3-D32 is an implementation of VFPv3 that provides 32 double-precision registers. VFPv3-D32 is implied for NEON targets, e.g. Cortex-A8 and Cortex-A9.

- VFPv3-D16 is an implementation of VFPv3 that provides 16 double-precision registers rather than 32. VFPv3-D16 is implemented for ARM architecture v7 and later (e.g. Cortex-A9 and Cortex-R4F)

- VFPv3 can be extended by the half-precision extensions that provide conversion functions in both directions between half-precision floating-point (fp16 – see later) and single-precision floating-point.

In addition particular implementations may provide implementation-specific functionality. For example, the VFP coprocessor hardware can include extra registers describing an exceptional condition. These registers are not described in the VFP architecture, yet the operating system needs to know about them when handling the exception, and sometimes when saving VFP context.

This extra functionality is known as the *subarchitecture* of the implementation. This must be relied upon only by system software, and only as described in this application note. Functions that depend on subarchitecture functionality should also be separated from the main body of the system software, so that it is easy to change to another VFP implementation. All other software must only rely upon the general architectural definition of the VFP architecture contained in the *ARM Architecture Reference Manual*.

## 1.3 What does the application note cover?

This application note contains the following:

- 1. An explanation of how to build floating-point code to run on a VFP-based system.

- 2. An explanation of how to set up a system so that the VFP can execute code.

- 3. A description of how to set up the debug tools so that VFP code can be loaded and executed.

- 4. A description of how to set up a system and software components to operate the VFP in RunFast mode.

- 5. Application test code which can be used to check that the VFP Support Code has been successfully installed into a system.

- 6. A description of an implementation of the software components required to provide a normal working VFP system. These software components are commonly referred to as the VFP Support Code. The modifiable portions of the support code are provided with this application note. Two unmodifiable libraries, vfpsupport.l and vfpsupport.b are supplied with RVDS.

This application note and the accompanying example code are written for use with RealView Developer Suite (RVDS) 2.1 and later. Differences which occur between RVDS 2.1, 2.2, 3.0, 3.1, and 4.0 are noted.

For information on using VFP with ADS 1.2 refer to Application Note 98, VFP Support Code, available for download from the ARM website.

## 1.4 Patches

It is advisable to update your tools to the latest versions as these updates will contain fixes to known problems. These updates are available from the downloads section of the Technical Support area on the ARM website.

## 2 Producing Code to Run on a VFP System

## 2.1 Using the compiler

## 2.1.1 --fpu name

By default the compiler generates code that makes calls to a software floating-point library routine in order to carry out floating-point operations. To make use of VFP instructions instead you must use appropriate compiler options to modify the code generated:

| fpu vfp                                        | This is a synonym forfpu vfpv2.                                                                                                                                                                                                                             |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| fpu vfpv1<br>(RVDS 2.1 only)                   | Selects hardware vector floating-point unit conforming to architecture VFPv1, such as the VFP10 rev 0. This option is deprecated in RVDS 2.1 and support was removed in RVDS 2.2.                                                                           |

| fpu vfpv2                                      | Selects hardware vector floating-point unit conforming to architecture VFPv2, such as the VFP10 rev 1 or VFP11.                                                                                                                                             |

|                                                | Note that if you select this option and also compile withthumb, then the compiler will actually generate ARM code for floating-point using functions.                                                                                                       |

| fpu vfpv3                                      | Selects hardware vector floating-point unit conforming to architecture VFPv3                                                                                                                                                                                |

| (RVDS 3.0 and later)                           | VFPv3 is backwards compatible with VFPv2 except that VFPv3 cannot trap floating-point exceptions.                                                                                                                                                           |

| fpu vfpv3_d16<br>(RVDS 4.0 and later)          | Selects hardware vector floating-point unit conforming to architecture VFPv3-<br>D16.                                                                                                                                                                       |

| fpu vfpv3_fp16<br>(RVDS 4.0 and later)         | Selects hardware vector floating-point unit that implements the VFPv3 half-<br>precision architecture.                                                                                                                                                      |

| fpu vfpv3_d16_fp16<br>(RVDS 4.0 and later)     | Selects hardware vector floating-point unit conforming to architectures VFPv3 half-precision and VFPv3-D16.                                                                                                                                                 |

| fpu softvfp+vfp                                | Synonym forfpu softvfp+vfpv2                                                                                                                                                                                                                                |

| fpu softvfp+vfpv2                              | Selects a floating-point library with software floating-point linkage that can use VFPv2 instructions. Select this option if you are interworking Thumb code with ARM code on a system that implements a VFP unit. If you select this option:               |

|                                                | <ul> <li>Compiling withthumb behaves in a similar way tofpu softvfp except<br/>that it links with floating-point libraries that contain VFP instructions.</li> </ul>                                                                                        |

|                                                | <ul> <li>Compiling witharm option behaves in a similar way tofpu vfpv2<br/>except that functions pass and return floating-point arguments and<br/>results in the same way as they would forfpu softvfp, but use VFP<br/>instructions internally.</li> </ul> |

| fpu softvfp+vfpv3<br>(RVDS 3.0 and later)      | Selects a floating-point library with software floating-point linkage that uses VFPv3 instructions.                                                                                                                                                         |

| fpu softvfp+vfpv3_fp16<br>(RVDS 4.0 and later) | Selects a floating-point library with software floating-point linkage that uses VFPv3 instructions with half-precision floating-point extension support.                                                                                                    |

| fpu softvfp+vfpv3_d16<br>(RVDS 4.0 and later)         | Selects a floating-point library with software floating-point linkage that uses VFPv3-D16 instructions.                                                |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| fpu<br>softvfp+vfpv3_d16_fp16<br>(RVDS 4.0 and later) | Selects a floating-point library with software floating-point linkage that uses VFPv3-D16 instructions with half-precision floating extension support. |

For more details of which compiler options to use in particular circumstances, please see section 2.3.

- **Note** The compiler only generates scalar floating-point operations. If you want to use the VFP's vector operations, then you must do this using assembly code.

- **Note** Some of the compiler's --cpu options imply a floating-point unit. So, for example, if you select --cpu ARM1136JF-S, this implies --fpu vfpv2. For RVCT 3.0 and later, specifying a --fpu setting overrides the floating-point unit implied by --cpu.

## 2.1.2 --fpmode model

Specifies the floating-point conformance, and sets library attributes and floating-point optimizations. Different libraries may be selected depending on the model chosen.

| fpmode std          | IEEE finite values with denormals flushed to zero, round-to-<br>nearest and no exceptions. It is C and C++ compatible. This is<br>the default option.                                                                                                                                                                      |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| fpmode ieee_full    | All facilities, operations and representations guaranteed by the IEEE standard are available in single and double precision.<br>Modes of operation can also be selected dynamically at run-<br>time.                                                                                                                       |

| fpmode ieee_fixed   | IEEE standard with round-to-nearest and no inexact exception.                                                                                                                                                                                                                                                              |

| fpmode ieee_no_fenv | IEEE standard with round-to-nearest and no exceptions. This mode is compatible with the Java floating-point arithmetic model.                                                                                                                                                                                              |

| fpmode fast         | Perform more aggressive floating-point optimizations that<br>might cause a small loss of accuracy to provide a significant<br>performance increase. This option results in behavior that is<br>not fully ISO C and C++ standard-compliant, however<br>numerically robust floating-point programs will behave<br>correctly. |

**Note** "--fpmode std" and "--fpmode fast" set the Flush-to-Zero and Default-NaN bits and clears the exceptions in the FPSCR (see section 3.6 for more details). These settings conform to RunFast mode. However, initialization code is still required to enable the VFP. See section 4 for more details.

## 2.1.3 --fp16\_format

Introduced in RVDS 4.0, this option enables the use of half-precision (16-bit) floatingpoint numbers and sets the format of variables marked with the new \_\_\_fp16 data type.

Half-precision floating-point numbers are provided as an optional extension to the VFPv3 architecture. If the VFPv3 coprocessor is not available, or if a VFPv3 coprocessor is used that does not have this extension, they are supported through the floating-point library fplib.

| fp16_format=none        | This is the default setting. It is equivalent to not specifying a format and means that the compiler will fault use of thefp16 data type. |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| fp16_format=ieee        | Half-precision binary floating-point format defined by IEEE 745r, a revision to the IEEE 754 standard.                                    |

| fp16_format=alternative | An alternative tofp16_format=ieee that provides additional range, but has no NaN or infinity values.                                      |

**Note** Also introduced in RVDS 4.0 are a set of fp16-based intrinsics that implement common NEON operations with half-precision floating-point values. A full listing of the available fp16-based intrinsics can be found in the RVCT Compiler Reference Guide.

## 2.2 Using the assembler

By default, the assembler faults the use of VFP instructions. To enable the assembly of VFP instructions, appropriate options need to be used. These options enable the use of VFP instructions in ARM or Thumb-2 code and modify the build attributes to enable the linker to determine the compatibility between object files, and to select appropriate libraries. They do not modify the code that is actually generated.

## 2.2.1 --fpu name

This option determines the target FPU architecture. *name* options are the same as for the compiler.

## 2.2.2 --fpmode model

This option selects the target floating-point model. Different libraries may be selected depending on the model chosen. *model* options are the same as for the compiler.

## 2.3 Floating point linkage and the -- fpu option

The following guidelines can be used to help you select the most suitable floating-point build options to use for your application.

## 2.3.1 Floating point linkage

How floating point arguments are passed into (and returned from) functions is called the "floating point linkage". There are two different types of floating point linkage available in RVDS : "hardware" and "software" floating point linkage.

With hardware floating point linkage, floating point arguments and return values are passed in VFP coprocessor registers. For this to be possible the target must have a VFP coprocessor present and be executing an instruction set that supports coprocessor instructions (ARM or Thumb-2).

With software floating point linkage, floating point arguments and return values are passed in ARM integer registers. This means it can be used on any ARM, with or without a VFP coprocessor. It can also be used from any instruction set (ARM, Thumb or Thumb-2) as it does not require access to a VFP coprocessor to pass arguments.

It is not possible to mix functions built with different floating point linkage because the arguments will be held in different physical registers.

You must choose the most appropriate linkage based on your needs. Hardware linkage offers improved performance as arguments and return values do no need to be

transferred between the VFP coprocessor register and the ARM registers on function calls, but can only be exploited when explicitly targeting a device known to contain VFP hardware. Software linkage (all code built with --fpu softvfp, --fpu softvfp+vfpv2 or --fpu softvfp+vfpv3) is more commonly used for code not specifically targeted at a particular processor.

**Note** Note: If software floating point linkage is being used, both the calling function and the called function must either be compiled using --fpu softvfp+vfpv2 or --fpu softvfp+vfpv3 or declared using the \_\_\_\_\_softfp keyword. The \_\_\_\_\_softfp keyword allows software floating-point linkage to be specified on a function by function basis rather than across the whole file as is the case with --fpu softvfp+vfpv2 or --fpu softvfp+vfpv3. See the description of \_\_\_\_\_softfp in the RVCT Compilers and Libraries Guide or the RVCT Compiler Reference Guide for more information.

## 2.3.2 ARM state only floating-point (ARMv6 and earlier)

If all of your floating-point processing is done in ARM state code and none is done in Thumb state code then:

- Build your ARM code with --fpu vfpv2 (if you are using VFP9-S, VFP10 rev 1 or VFP11)

- Build your Thumb code with --fpu none. This ensures that no floating-point operations take place in Thumb code.

## 2.3.3 ARM and Thumb floating-point (ARMv6 and earlier)

The Thumb instruction set in ARMv6 and earlier does not support coprocessor instructions and this means you cannot access the VFP coprocessor register in code compiled for Thumb. Therefore you must either compile for the ARM instruction set or use software floating point linkage.

- Compiling with --fpu vfpv2 will use hardware VFP linkage and therefore any functions that use floating point types will be compiled as ARM code to allow access to the VFP registers.

- Compiling with --fpu softvfp+vfpv2 will use software floating point linkage. When

compiling for the ARM instruction set the compiler will generate VFP instructions

inline and pass parameters in ARM registers. When compiling for Thumb (--thumb)

the compiler will generate Thumb code with calls to floating point support libraries to

perform the floating point operations. At link time, the linker will normally then link-in a

version of the floating point support library that contains hardware VFP instructions to

perform the floating point operation.

The choice of options that provides the best code size/performance depends upon the code being compiled. For example, there is a trade-off between compiling --fpu softvfp+vfpv2 (as opposed to --fpu vfpv2) to obtain Thumb code and the corresponding inclusion of library code. It is best to experiment with different options to find the combination which provides the required code size/performance attributes.

## 2.3.4 ARM and/or Thumb-2 floating-point (ARMv7, RVDS 3.0 and later)

VFP is directly accessible from both the ARM and Thumb-2 instruction set on ARMv7 processors with VFPv3 such as Cortex-A8. This allows you to use Thumb-2 for your entire application, without needing to switch to ARM state to perform VFP operations. To do this, build your code with --thumb and one of the following options:

- --fpu vfpv3

- --fpu vfpv3\_fp16

- --fpu vfpv3\_d16

• --fpu vfpv3\_d16\_fp16

Alternatively, you can build your code for ARM only with --arm and one of the above options.

To build code that is compatible with other code that specifies software floating-point linkage, use one of the following options:

- --fpu softvfp+vfpv3

- --fpu softvfp+vfpv3\_fp16

- --fpu softvfp+vfpv3\_d16

- --fpu softvfp+vfpv3\_d16\_fp16

## **3 VFP System Initialization**

To use VFP in your application, there are a number of steps that must be carried out before floating-point operations can be executed. These steps might need to be done in your initialization code, or may be done by your operating system.

- 1. Ensure the VFP Support Code is part of the system software.

- 2. Install the VFP Support Code on to the undefined instruction vector.

- 3. Ensure that there is a valid stack for undefined mode.

- 4. Enable the VFP coprocessor by setting the VFPEnable bit in the VFP's FPEXC register. For architecture V6 processors, coprocessor bits CP10 and CP11 in the Coprocessor Access Control Register also need setting. Note that at reset the VFP coprocessor will be disabled.

These steps are discussed in more detail in the following subsections.

**Note** If you wish to operate the VFP coprocessor in RunFast mode the initialization required is different, see section 4 for more details.

## 3.1 Provide the VFP Support Code

Provided with this application note is an implementation of the modifiable portions of the RVDS VFP Support Code that can be used in your system. In the past, earlier implementations have been provided, for example as part of the ARM Firmware Suite. We now advise the use of the code provided with this application note in conjunction with the libraries vfpsupport.I and vfpsupport.b supplied in the library directory of RVDS. In some applications VFP Support Code is linked-in as part of the image. In other applications it may be provided linked-in as part of the system environment or operating system.

**Note** VFP Support Code is not needed in VFPv3-based systems, except for VFPv3U or when performing vector operations on a VFPv3-D16 - contact your supplier for more information.

## 3.2 Install the VFP support code

Trying to execute VFP instructions not implemented by the VFP hardware or executing "exceptional cases" causes the ARM to take an undefined instruction exception. This is sometimes known as *bouncing* the instruction. The VFP support code must therefore be installed on to the undefined instruction vector before floating-point operations take place.

In an embedded application, initialization code installs the VFP Support Code into the vector table along with the other exception handlers (typically using scatterloading).

Alternatively during early development work, a simple patch function can be called to install an appropriate branch instruction into the undefined instruction vector table entry. The following assembler code example shows how this can be done. This assumes that

- the VFP Support Code is located in memory within the first 32MB of memory so that a branch instruction can be used

- high vectors are disabled

- address 0 is writable in the current mode (determined by MMU access permissions)

If caches are enabled the predefine WANT\_CACHE\_FLUSH should be used to flush the caches after the patching of the vector table.

```

0x4 ; address of undefined instruction vector

UNDEF_VECTOR

EQU

; (hivecs not handled)

Install_VFPHandler FUNCTION

; Install VFP handler onto undefined instruction

; TLUndef_Handler must be reachable via BL from UNDEF_VECTOR.

ADR

r0, TLUndef_Handler_Offset

r1, [r0]

LDR

r0, r0, r1

ADD

r0, r0, #UNDEF_VECTOR+8 ; allow for vector address and PC offset

SUB

MOV

r0, r0, LSR #2

ORR

r0, r0, #0xea000000

; bit pattern for Branch always

r1, #UNDEF_VECTOR

MOV

IF ARCH_V6_OR_LATER :LAND: {ENDIAN} = "big" :LAND: :LNOT: :DEF: ENDIAN_BE_32

REV

r0, r0

ENDIF

STR

r0, [r1]

; If we have separate data and instruction caches then we need to clean the

; data cache and invalidate the instruction cache.

; If we have a branch target cache we need to invalidate that as well.

IF : DEF: WANT CACHE FLUSH

; This code is known to work with ARM926, ARM946, ARM1020, ARM1022

; ARM1026 and ARM1136 cores.

;

; For other cores the following may need to be modified.

; Please check the TRM for your core.

CACHE_ADDR_SBZ EQU 0x7 ; these bits "should be zero" when cleaning/invalidating

; by virtual address, v6 doesn't have SBZ bits

UNDEF_VECTOR_CACHE_LINE EQU (UNDEF_VECTOR :AND: :NOT:CACHE_ADDR_SBZ)

MOV r1, #UNDEF_VECTOR_CACHE_LINE

MCR p15, 0, r1, c7, c10, 1 ; clean D cache at 'r1'

MCR p15, 0, r1, c7, c5, 1 ; invalidate I cache at 'r1'

MOV r0,#0

MCR p15, 0, r0, c7, c10, 4 ; drain write buffer

IF ARCH_V6_OR_LATER

MOV r1, #UNDEF_VECTOR

MCR p15, 0, r1, c7, c5, 7; invalidate branch target cache at 'r1'

ENDIF

ENDIF

ВX

LR

; return from subroutine

TLUndef_Handler_Offset

TLUndef_Handler - TLUndef_Handler_Offset

DCD

```

ENDFUNC

## 3.3 Set up the undefined mode stack

As at least some of the VFP Support Code executes in undefined instruction mode, it is necessary to have an undefined mode stack set up. In a fully embedded system that runs from reset, then this is likely to have been done within the initialization code.

In the case of early development code downloaded via a debugger, then a simple function can be called to set up the stack. The following assembler code example shows how this can be done. Note that this must be executed in a privileged mode.

```

Mode_UNDEF

EQU

; bit pattern for undefined mode

0x1B

IF :DEF: SETUP_UNDEF_STACK

EXPORT Setup_Undef_Stack

Setup_Undef_Stack FUNCTION

; Now set up a stack for undefined mode

MRS

r0, CPSR

; get CPSR value

MOV

r1, r0

; take a working copy

r1,r1, #Mode_UNDEF

; set mode bits for Undefined mode

ORR

MSR

CPSR_c, r1

; change to undefined mode

IF :DEF: RWPI

LDR

r2, UNDEF_Stack_Offset

SP, r2, r9

ADD

ELSE

SP, =UNDEF_Stack

LDR

; set up the stack pointer

ENDIF

CPSR_c, r0

; change back to the original mode

MSR

ΒХ

LR

; return from subroutine

ENDFUNC

IF :DEF: RWPI

UNDEF_Stack_Offset DCDO UNDEF_Stack

ENDIF

ENDIF

IF :DEF: SETUP UNDEF STACK

; Location for undefined-mode stack

UNDEF_STACK, NOINIT, ALIGN=3

AREA

%

; Only two words will be used

8

UNDEF_Stack

EOU .

ENDIF

END

The support code runs largely in SVC mode and only a small amount of stack space is

```

**Note** The support code runs largely in SVC mode and only a small amount of stack space is required for undefined mode operation. This means that you also have to ensure that you have the SVC mode stack set up (though this is normally the case). See section 7 for more details.

## 3.4 Enable VFP

On all systems, it will be necessary to enable the VFP by setting the VFPEnable (EN) bit in the VFP's FPEXC register. Until this is done, the VFP coprocessor is disabled and any other access to the VFP causes an undefined instruction exception. On pre-v7 cores, you will also need to reset the EX bit in this register to clear any pending exceptions. This operation must be carried out in a privileged mode.

The following assembler code example shows how this can be done:

```

VFPEnable EQU 0x40000000

Enable_VFP FUNCTION

; Enable VFP itself

MOV r0,#VFPEnable

FMXR FPEXC, r0 ; FPEXC = r0

BX LR

ENDFUNC

```

Note The new UAL equivalent of FMXR is VMSR.

#### 3.4.1 Architecture V6 and later

Due to changes made in V6 and later architectures in the way in which the VFP coprocessor interfaces with the core processor, the VFP support code has some conditional actions which apply only to architecture V6 or later (such as VFP11). Coprocessors CP10 and CP11 must be enabled by setting bits 20-23 (b1111 gives full read/write access) of the Coprocessor Access Control Register. For more information please refer to the technical reference manual of the ARM processor core that you are using.

```

VFPEnable

0x4000000

EQU

GBLL ARCH_V6_OR_LATER

;Create global variable

IF "6" <= {ARCHITECTURE} ; ok until architecture 10</pre>

ARCH_V6_OR_LATER SETL {TRUE}

ELSE

ARCH_V6_OR_LATER SETL {FALSE}

ENDIF

Enable_VFP FUNCTION

IF ARCH_V6_OR_LATER

MRC p15, 0, r1, c1, c0, 2 ; r1 = Access Control Register

ORR r1, r1, #(0xf << 20) ; enable full access for p10,11

MCR p15, 0, r1, c1, c0, 2 ; Access Control Register = r1

MOV r1, #0

MCR p15, 0, r1, c7, c5, 4 ; flush prefetch buffer because of FMXR below

; and CP 10 & 11 were only just enabled

ENDIF

; Enable VFP itself

MOV

r0,#VFPEnable

FPEXC, r0

FMXR

; FPEXC = r0

```

Note The new UAL equivalent of FMXR is VMSR.

LR

ВΧ

ENDFUNC

## 3.5 Installation routine

One important point to note about the preceding steps is that they must all be carried out *before* the C library's floating-point initialization takes place. This is done by the library routine  $_{fp\_init()}$ .

The easiest way to do this is to write a simple function that calls the required routines described in sections 3.1-3.5 *before* \_fp\_init() is executed. This is done using the linker's *\$Sub\$\$* and *\$Super\$\$* functionality, which is detailed in the *RVCT Linker Guide*. The following C code example shows how this can be done:

```

#ifdef __cplusplus

#define EXTERN_C extern "C"

#else

#define EXTERN_C extern

#endif

#ifdef SETUP_UNDEF_STACK

EXTERN_C void Setup_Undef_Stack (void);

#endif

#ifdef PATCH_UNDEF_VECTOR

EXTERN_C void Install_VFPHandler (void);

#endif

EXTERN_C void Enable_VFP (void);

EXTERN_C void $Super$$_fp_init(void);

// Call $Sub$$_fp_init() in place of original _fp_init()

EXTERN_C void $Sub$$_fp_init(void)

{

#ifdef PATCH_UNDEF_VECTOR

Install_VFPHandler();

#endif

#ifdef SETUP_UNDEF_STACK

Setup_Undef_Stack();

#endif

Enable_VFP();

$Super$$_fp_init(); // Call original _fp_init()

}

```

## 3.6 FPSCR settings

The Floating-Point Status and Control Register (FPSCR) holds control bits that affect the way the VFP operates. The FPSCR is usually set by the C library initialization code depending on the compilation options selected. However you may wish to modify the FPSCR contents within your code (for example to change the vector length if you are using vector floating-point calculations).

The FPSCR contains:

- N, Z, C and V condition flags resulting from the most recent FP comparison

- Alternative Half-Precision (VFPv3-D16 only)

- Default NaN mode control

- Flush-to-zero mode control

- Rounding mode control

- Vector length/stride control

- Exception status and control.

For more information on these options please refer to the Technical Reference Manual of the VFP unit that you are using. The following assembler code example shows how to set the rounding mode, it is not included in the VFP example code provided by this application note but illustrates how VFP options can be set.

RZ\_Enable EQU 2\_11:SHL:22

; Bit pattern to enable Round towards zero mode

EXPORT Round\_Towards\_Zero

Round\_Towards\_Zero FUNCTION

FMRX r0, FPSCR ; Read current status

ORR r0, r0, #RZ\_Enable

FMXR FPSCR, r0 ; FPSCR = r0

BX LR

ENDFUNC

Note The new UAL equivalents of FMRX and FMXR are VMRS and VMSR respectively.

## 4 RunFast Mode Initialisation

This mode is applicable to VFP9-S, VFP10 rev1, VFP11 and VFPv3-based coprocessors.

Hardware floating-point calculations are considerably faster than software calculations. However, VFP coprocessors still require support code for handling of exceptional cases (such as subnormal numbers). In many applications the additional accuracy and IEEE 754 standard compliance provided by the support code are unimportant. In these applications execution speed can be increased and program size reduced by configuring the VFP in RunFast mode.

RunFast mode is not configured by setting a single register bit. It is the combination of the following conditions:

- The VFP coprocessor is in flush-to-zero mode.

- The VFP coprocessor is in default NaN mode.

- All exception bits are cleared.

In RunFast mode the VFP coprocessor:

- Processes subnormal operands as positive zeros

- Processes input NaNs as default NaNs

- Processes results that are tiny before rounding, that is, between the positive and negative minimum normal values for the destination precision, as positive zeros.

- Returns the IEEE 754 standard for operations that overflow, operations which are considered as invalid, and for divide-by-zero cases, fully in hardware and without additional latency.

- Process all operations in hardware without trapping to support code.

In order to activate RunFast mode, all that is required is to set bits 24 and 25 of the FPSCR, clear the exception bits and activate the VFP. If the code is compiled using "--fpmode std" or "--fpmode fast" bits 24 and 25 of the FPSCR are automatically set and the exceptions cleared by the C runtime library. The RunFast\_Enable function is included for completeness should you wish to enable RunFast mode when using a different --fpmode option.

AREA RunFast, CODE, READONLY

| VFPEnable      | EQU       | 0x4000000              |

|----------------|-----------|------------------------|

| RF_Enable      | EQU       | 2_11:SHL:24            |

| ; Bit p        | pattern t | to enable RunFast mode |

| ; FPSCH        | R [24] -  | Flush to Zero mode     |

| ; FPSCH        | २ [25] -  | Default NaN mode       |

|                |           |                        |

| EXPORT         | RunFast   | t_Enable               |

|                |           |                        |

| RunFast_Enable | FUNCTION  | N                      |

|                |           |                        |

| MOV            | r0,#RF_   | _Enable                |

| FMXR           | FPSCR,    | r0 ; FPSCR = r0        |

| BX             | LR        |                        |

| ENDFUNC        | 2         |                        |

```

EXPORT Enable_VFP

Enable_VFP FUNCTION

; Enable VFP itself

MOV r0,#VFPEnable

FMXR FPEXC, r0 ; FPEXC = r0

BX LR

ENDFUNC

END

```

Note The new UAL equivalent of FMXR is VMSR.

As with normal VFP support when using V6 or later coprocessors, RunFast mode requires extra code for Architecture V6 or later (such as coprocessor VFP11) because of the changes to the coprocessor interface. Coprocessors cp10 and cp11 must be enabled by setting bits 20-23 (b1111 gives full read/write access) of the Coprocessor Access Control Register. For more information please refer to the technical reference manual of the ARM11 or Cortex processor that you are using. The example code below shows how this may be done.

Enable\_VFP FUNCTION

```

if "6" <= {ARCHITECTURE}

MRC p15, 0, r1, c1, c0, 2 ; r1 = Access Control Register

ORR r1, r1, #(0xf << 20) ; enable full access for p10,11

MCR p15, 0, r1, c1, c0, 2 ; Access Control Register = r1

MOV r1, #0

MCR p15, 0, r1, c7, c5, 4 ; flush prefetch buffer because of FMXR below

; and CP 10 & 11 were only just enabled

endif

; Enable VFP itself

MOV

r0,#VFPEnable

FPEXC, r0

; FPEXC = r0

FMXR

ΒХ

LR

ENDFUNC

```

Note The new UAL equivalent of FMXR is VMSR.

## 5 Debugger Setup for VFP

## 5.1 Configuring RVISS (ARMulator) for VFP in RVD

The RVISS (ARMulator) provides models of the VFP architecture that can run VFP instructions. However as these model the architecture rather than specific implementations, they cannot be used to accurately benchmark the floating-point performance that will be obtained in a real system.

In RVD an ARMulator connection can be established in two different ways, either by using the RealView connection broker (recommended) or the Remote Debug Interface (RDI). If you have a multi-core license, the connection broker allows more than one ARMulator to operate in a single instantiation of RVD (See the RVISS User Guide provided with RVDS).

## 5.1.1 Connecting to RVISS via RealView Connection Broker

To do this navigate to:

## RVDS 2.1File $\rightarrow$ Connection $\rightarrow$ Connect to targetRVDS 2.2:Target $\rightarrow$ Connect to Target

This opens the Connection Control window, you must start a new ARMulator Simulator by clicking on the crosses navigate to: **+ Server + localhost.**

To configure the new device right click on the new\_ARM option and select "Configure Device Info". Select the required Processor and VFP type and click "OK". Then, in the Connection Control Window, place a tick by "new arm" to start the simulator.

## RVDS 3.0: Target → Connect to Target

Click on localhost in the Connection Control Window, then click "Open Target Access". Right click on new\_arm which should now have appeared in the expanded tree and select Configure. In the Configuration Window select the required Processor and VFP type and click OK. Re-open the Connection Control Window, select "new\_arm" and click Connect to start the simulator.

| 🙆 ARMulator Configuratio                                                                                                      | n X                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processor<br>ARM1026EJ<br>ARM10200E<br>ARM1136J-S<br>ARM1136J-S_BE32<br>ARM1136J-S_BE32<br>ARM1136J-S_BE32<br>ARM1136J-S_REV1 | Additional Modules<br>Floating Point:<br>No FPU<br>VFPv2<br>VFPv2 (Fast-mode)<br>FPA (limited support)<br>MMU/PU Initialization:<br>Default Page-Tables |

| Clock<br>C Emulated Speed:<br>Real-time<br>Debug Endian: C Little<br>Start Endian: C Debug End                                | C Big<br>lian C Hardware Endian                                                                                                                         |

## Select an appropriate Processor and FPU setting

To emulate a vfpv2 FPU on an ARM9, first select the processor needed (e.g. ARM926EJ-S) and then select VFPv2. VFPv2 (Fastmode) is a VFP model that does not bounce to support code.

If a vfpv2 FPU is to be included for an ARM10, for example the ARM1020E, the variant including the VFP10, e.g. ARM10200E should be chosen and the "No FPU" setting should be selected. ARM11 processors have variants including an "F" in the name symbolising that it includes an FPU. Once again when choosing one of these processors, for example ARM1136JF-S, the "No FPU" setting should be selected.

If you select a processor containing an FPU and then an FPU model is chosen explicitly, the behaviour of the ARMulator can be unpredictable.

## RVDS 3.1 and onward: Target → Connect to Target

Expand RealView Instruction Set Simulator (RVISS) in the Connection Control Window, then right click on one of the RVISS connections and select Configure. In the Configuration Window select the required Processor and VFP type and click OK. Go back to the Connection Control Window, select the RVISS connection you configured and click Connect to start the simulator.

| 🚱 rvdebug.brd - Connect to Target                                                                                                              |           |                                 |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------|--|

| Eile ⊻iew ⊆onnection <u>H</u> elp                                                                                                              |           |                                 |  |

| 🗄 🐲 💱 🖤 🐚 🚔 Grouped By 🛛 Config                                                                                                                | uration 💌 |                                 |  |

| Name                                                                                                                                           | State     |                                 |  |

| RealView Instruction Set Simulator (RVISS     RVISS_1     RVISS_2     RVISS_2     RealView ICE     SoC Designer     ARM Ltd. Direct Connection | )         | Add<br>Add<br>Add<br>Add<br>Add |  |

| Connection Modes Connect :                                                                                                                     |           |                                 |  |

## 5.1.2 Connecting to RVISS via Remote Debug Interface

To do this within RVD navigate to:

#### **RVDS 2.1:** File $\rightarrow$ Connection $\rightarrow$ Connect to target

#### **RVDS 2.2:** Target $\rightarrow$ Connect to Target

This will open the Connection Control window. Click on the cross next to the ARM-A-RR item to expand the RDI targets tree.

If an ARMulator item does not appear, right click on the ARM-A-RR item and select "Add/Edit/Remove devices". If an ARMulator option appears in the window that opens ensure that the corresponding check box is ticked. If ARMulator does not appear click "Add DLL..." and open:

"Install\_directory\RVARMulator\ARMulator\vers\build\platform\ARMulate.dll"

where *Install\_directory, vers, build*,and *platform* are specific to your installation (e.g. "C:\Program Files\ARM", vers 1.41, build 253 and win\_32-pentium).

To configure the ARMulator right click on the ARMulator item and select "Configure Device Info...". The configuration dialogue is the same as that used in AXD, see section 5.3 below.

#### RVDS 3.0 onwards:

RDI has been deprecated in RVDS 3.0, use connection broker instead.

## 5.1.3 Vector Catch

The VFP Support Code is installed on to the undefined instruction vector table entry, so unless you are using RunFast mode, it is also necessary to ensure that the debugger is not trapping undefined instructions using its "vector\_catch" function.

To do this navigate to:

| RVDS 2.1: | Debug $\rightarrow$ Simple Breakpoints $\rightarrow$ Processor events |

|-----------|-----------------------------------------------------------------------|

|-----------|-----------------------------------------------------------------------|

#### RVDS 2.2 onwards: Debug → Processor Exceptions

and clear the "Undefined" tick box.

To alter vector\_catch on ARMulator connected via RDI or Multi-ICE navigate to:

| RVDS 2.1: | View $\rightarrow$ Pane Views $\rightarrow$ Registers. |

|-----------|--------------------------------------------------------|

|           |                                                        |

RVDS 2.2: View  $\rightarrow$  Registers.

**RVDS 3.0 onwards:** RDI has been deprecated in RVDS 3.0, use connection broker instead.

In the register pane select the debug tab. Vector\_catch default value is 0x13B to disable "Undefined" set the value to 0x139 (i.e. clear the 0x002 bit).

## 5.2 Configuring ISSM for VFP in RVD

Introduced in RVD 3.0, ISSM provides models for the Cortex family of processors. When connected to a ISSM that supports VFP, a VFP tab will be displayed in the Register window.

## 5.2.1 Connecting to ISSM

To do this within RVD navigate to:

#### Target → Connect to target

to open the Connection Control window and start a new ISSM configuration by clicking on the "Add" button. This will open the Model Configuration Utility window.

| Models<br>SSM_ARM_Cortex-A8.cadi<br>SSM_ARM_Cortex-M1.cadi<br>SSM_ARM_Cortex-M3.cadi<br>SSM_ARM_Cortex-R4.cadi | Devices<br>ARM ISSM Cortex-A8 |                              |   |         |         |  |

|----------------------------------------------------------------------------------------------------------------|-------------------------------|------------------------------|---|---------|---------|--|

|                                                                                                                | Parameters of 'ARM_Co         | rtex-A8_0 (ARM_Cortex-A8)'   |   | 0       | (v—sa   |  |

|                                                                                                                | Parameter                     | Value                        |   | Туре    | <b></b> |  |

|                                                                                                                | vinithi                       | False                        | - | Bool    |         |  |

|                                                                                                                | cfgte                         | False                        |   | Bool    |         |  |

|                                                                                                                | cfgend0                       | False                        |   | Bool    |         |  |

|                                                                                                                | cfgnmfi                       | False                        |   | Bool    |         |  |

|                                                                                                                | cp15sdisable                  | False                        |   | Bool    |         |  |

|                                                                                                                | cpexist                       | 0xc00                        |   | Numeric |         |  |

|                                                                                                                | siliconid                     | 0x41000000                   |   | Numeric |         |  |

|                                                                                                                | I2_cachesize                  | 0x100                        |   | Numeric |         |  |

|                                                                                                                | 11_cachesize                  | 0x20                         |   | Numeric |         |  |

|                                                                                                                | fast_invalidate               | 0x0                          |   | Numeric |         |  |

|                                                                                                                | warn-undefined                | False                        |   | Bool    |         |  |

|                                                                                                                | warn-extra                    | False                        |   | Bool    |         |  |

|                                                                                                                | ISSEmnon                      | False                        |   | Bool    |         |  |

| Browse                                                                                                         | Description: Let exception    | vectors start at 0xFFFF0000. |   |         |         |  |

|                                                                                                                |                               |                              |   | ок      | Cancel  |  |

Select which core you want to connect to from the "Models" menu on the left side of the configuration utility and click "OK". In the Connection Control window, double click on the ISSM configuration you created to connect to the ISSM.

**Note** Some ISSMs such as the Cortex-A8 allow you to disable the VFP unit from the Model Configuration Utility window. Make sure that the VFP unit is enabled.

The ISSMs do not support vector catch, so you will not need to disable the vector catch logic before running your application.

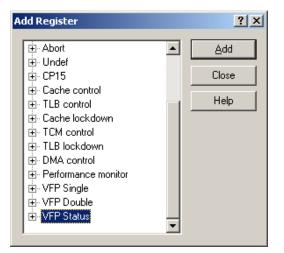

## 5.3 Enabling VFP registers in RVD

Normally RVD will automatically display the registers present in the target to which you have connected. However, if connecting to a target processor using RealView ICE or Multi-ICE, For certain targets RVD may occasionally fail to display the VFP registers.

If connecting with RealView ICE, RVD can be manually told that the target processor has a VFP unit. To do this right click on the RealView ICE entry in connection control, then click Configure Device Info. This opens the RVConfig window. Select the core you wish to connect to, then click on Device Properties. In the Device Properties window, select the VFP item as shown below.

| Device Properties                                             | × |

|---------------------------------------------------------------|---|

| Device Name : ARM1136JF-S                                     |   |

| Template Version : 1:0:0<br>Options :                         | ~ |

| Embedded Trace Macrocell (ETM)<br>Embedded Trace Buffer (ETB) |   |

| I ✔ Vector Floating Point (VFP)                               |   |

|                                                               |   |

|                                                               |   |

|                                                               |   |

| <u>QK</u> <u>Cancel H</u> elp                                 |   |

## 5.3.1 Enabling VFP registers in RVD when connected to a Versatile PB926EJ-S using Multi-ICE

RVD does not display VFP registers when Multi-ICE is connected to a Versatile PB926EJ-S. When Multi-ICE is auto-configured an ARM926EJ-S is detected however this definition does not contain a VFP as standard (the Integrator/CM926EJ-S does not have a VFP).

A workaround for this problem is to use the vfp.xml provided in the \util directory of the VFP examples. When copied into the same directory as the version of armperip.xml that is used by RVD, vfp.xml overrides the existing definition of the ARM926EJ-S to include a VFPv2.

Copy vfp.xml to the \RVD\Core\version#\release#\platform\bin directory of your ARM installation. If the above is not successful you may need to copy vfp.xml to an alternative directory containing armperip.xml

## 5.4 Configuring ARMulator for VFP in AXD

The ARMulator provides models of the VFP architecture that can run VFP instructions. However as these model the architecture rather than specific implementations, they cannot be used to accurately benchmark the floating-point performance that will be obtained in a real system.

AXD supports the debugging of ARM7, 9 and 10 processors only, not ARM11 or later (use RVD instead).

AXD was deprecated in RVDS 3.0, and removed from RVDS 3.1..

AXD supports debugging with DWARF2 debug tables only, not DWARF3. The RVCT 3.0 compilation tools generate debug images with DWARF3 debug tables by default. To use AXD, compile with --dwarf2.

Within AXD select the "Options -> Configure Target" menu. Then ensure that "ARMUL" is the selected target and click on the Configure button. This displays the ARMulator Configuration dialog box.

You can then change the Processor and Floating-Point Coprocessor settings to match your requirements:

| Processor         ⊻ariant:       ARM926EJ-S         Clock         © Emulated Speed:         © Beal-time         Options         □ Eloating Point Emulation         Debug Endian         © Little © Big         Start target Endian         © Debug Endian         © Debug Endian         © Hardware Endian         Memory Map File         © Map File         Browse         Floating Point Coprocessor         FPU:       NO_FPU         MMU/PU Initialization         Pagetab DEFAULT_PAGETABLES       Image: Start Pagetab DEFAULT_PAGETABLES                                                                                                                                                                                                                                                                                                                                                 | Ilator Configuration                              | × |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|---|

| Clock Clock Emulated Speed: Beal-time Options Floating Point Emulation Debug Endian Debug Endian Debug Endian Debug Endian Debug Endian Memory Map File Map File Browse Floating Point Coprocessor FPU: NO_FPU MMU/PU Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Processor                                         |   |

| ○ Emulated Speed:         ● Beal-time         Options         □ Eloating Point Emulation         Debug Endian         ● Little ○ Big         Start target Endian         ● Debug Endian         ● Map File         ● Map File | Variant: ARM926EJ-S                               |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Clock                                             |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | C Emulated Speed:                                 |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ,                                                 |   |

| Debug Endian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Options                                           |   |

| Ittle       Big         Start target Endian       Image: Debug Endian         Image: Debug Endian       Image: Hardware Endian         Memory Map File       Image: Map File         Image: Map File       Image: Browse         Floating Point Coprocessor       Image: Browse         FIDebug Point Coprocessor       Image: Plue         Image: MMU/PU Initialization       Image: Mage: Plue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Eloating Point Emulation                          |   |

| Start target Endian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Debug Endian                                      |   |

| Debug Endian     Hardware Endian  Memory Map File      Map File      Browse  Floating Point Coprocessor  FPU: NO_FPU  MMU/PU Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ● Little C Big                                    |   |

| Memory Map File   Map File  Map File  Floating Point Coprocessor  FPU: NO_FPU  MMU/PU Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Start target Endian                               |   |

| No Map File     Map File     Browse  Floating Point Coprocessor  FPU: NO_FPU  MMU/PU Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ● <u>D</u> ebug Endian C H <u>a</u> rdware Endian |   |

| Map File         Browse         Floating Point Coprocessor         FPU:       NO_FPU         MMU/PU Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Memory Map File                                   |   |

| Browse       Floating Point Coprocessor       FPU:       NO_FPU       MMU/PU Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | No Map File                                       |   |

| Floating Point Coprocessor FPU: NO_FPU MMU/PU Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | O <u>M</u> ap File                                |   |

| FPU: NO_FPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Browse                                            |   |

| MMU/PU Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Floating Point Coprocessor                        |   |