# Cycle Model Compiler

Version 9.1.0

**User Manual**

Non-Confidential

# Cycle Model Compiler User Manual

Copyright © 2017 ARM Limited. All rights reserved.

#### **Release Information**

The following changes have been made to this document.

#### **Change History**

| Date          | Issue | Confidentiality  | Change           |

|---------------|-------|------------------|------------------|

| February 2016 | A     | Non-Confidential | Update for 8.1   |

| May 2016      | В     | Non-Confidential | Update for 8.2   |

| June 2016     | С     | Non-Confidential | Update for 8.2.1 |

| July 2016     | D     | Non-Confidential | Update for 8.2.2 |

| August 2016   | Е     | Non-Confidential | Update for 8.3.0 |

| November 2016 | F     | Non-Confidential | Update for 9.0.0 |

| February 2017 | G     | Non-Confidential | Update for 9.1.0 |

|               |       |                  |                  |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of ARM Limited ("ARM"). No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, ARM makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version shall prevail.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to ARM's customers is not intended to create or refer to any partnership relationship with any other company. ARM may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any signed written agreement specifically covering this document with ARM, then the signed written agreement prevails over and supersedes the conflicting provisions of these terms.

Words and logos marked with  $^*$  or  $^{\text{m}}$  are registered trademarks or trademarks of ARM Limited or its affiliates in the EU and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. You must follow the ARM trademark usage guidelines http://www.arm.com/about/trademarks/guidelines/index.php.

Copyright © ARM Limited or its affiliates. All rights reserved. ARM Limited. Company 02557590 registered in England. 110 Fulbourn Road, Cambridge, England CB1 9NJ.

In this document, where the term ARM is used to refer to the company it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

# Contents

| Chapter 1.<br>Introduction to the Cycle Model Compiler                                                                                                          |                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Validation Methodology Compiler Inputs What is a Cycle Model? Using a Cycle Model The Cycle Model API RTL Remodeling Tasks                                      |                      |

| Chapter 2. Getting Started with the Cycle Model Compiler                                                                                                        |                      |

| Setting up the Example Environment The Example Hardware Design Verilog Twocounter Example The Makefile Running the Example Cycle Model Compiler Output Files    | 12<br>12<br>12<br>13 |

| Chapter 3.<br>Cycle Model Compiler Command Line Options                                                                                                         |                      |

| Command Syntax Command Options General Compile Control Input File Control Module Control Net Control Verilog- and SystemVerilog-Specific Options Output Control |                      |

| Chapter 4. Cycle Model Compiler Directives                                                                                                                      |                      |

| Using Directives Using a Directives File Embedding Directives in Comments Net Control Module Control Flattening                                                 |                      |

| Output Control                                                                                                                                                  | 50                   |

# Chapter 5. Language Support

| Verilog Support                                                                 | 52 |

|---------------------------------------------------------------------------------|----|

| General Constructs                                                              |    |

| Hierarchical References                                                         | 54 |

| Net Types                                                                       | 56 |

| Gate-level Constructs                                                           | 58 |

| Behavioral Constructs                                                           | 59 |

| Switch-level Constructs                                                         | 61 |

| User-Defined Primitives                                                         | 62 |

| Synthesizable Subset                                                            | 63 |

| Z State Propagation                                                             | 63 |

| Exponent Operator Support                                                       | 65 |

| SystemVerilog Support                                                           | 66 |

| Supported Constructs                                                            | 66 |

| Constructs with Limited Support                                                 |    |

| Support for New Data Types                                                      | 70 |

| Appendix A.                                                                     |    |

| Dumping Waveforms in Different Environments                                     |    |

| Waveform Dumping Implementation Notes                                           | 71 |

| Basic C/C++ Testbench                                                           | 72 |

| SystemC Environment                                                             | 73 |

| Appendix B.                                                                     |    |

| Using DesignWare Replacement Modules                                            |    |

| Replacing DesignWare Modules                                                    | 75 |

| List of Replacement Modules for DesignWare                                      |    |

| Troubleshooting                                                                 |    |

| Appendix C.                                                                     |    |

| Using Profiling to Find Performance Problems                                    |    |

| Types of Performance Problems                                                   | 79 |

| Locating the RTL Source of a Profiling Hotspot                                  |    |

| Using the Hierarchy File                                                        |    |

| Commenting Out the Problem Function                                             |    |

| Confirming that the Identified Calling Code Leads to the Profiling Hotspot      |    |

| Re-writing RTL to Improve Performance                                           |    |

| Example 1: A Simple Library Cell as a Profiling Hotspot                         |    |

| Example 2: Infrequently Occurring Architectures/Modules as Profiling Hotspots . |    |

| Example 3: Profiling is an Iterative Process                                    | 82 |

| Summary                                                                         | 83 |

# Introduction to the Cycle Model Compiler

This chapter provides an overview of the Cycle Model Compiler product and how it fits into the ARM Cycle Model system validation workflow.

# 1.1 Validation Methodology

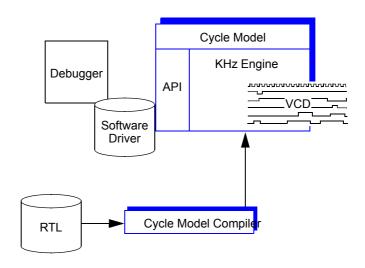

ARM Cycle Model tools provide an integrated environment that places system validation in parallel with the hardware development flow, as shown in Figure 1.1. The Cycle Model Compiler takes an RTL hardware model and creates a high-performance linkable object, called the Cycle Model, that is cycle and register accurate. The Cycle Model provides an API for interfacing with your validation environment.

Figure 1.1 Validation Environment

# 1.2 Compiler Inputs

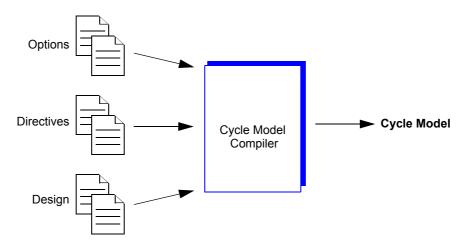

A Cycle Model is exclusive to ARM and can be generated only by the Cycle Model Compiler. The Cycle Model Compiler reads the following files, in order, and generates a Cycle Model for the design.

- 1. Options files Contain command options that provide control and guidance to the Cycle Model Compiler.

- 2. Directives files Contain directives that control how the Cycle Model Compiler interprets and builds a Cycle Model.

3. Verilog® design and library files – *Golden* RTL of the hardware design.

Figure 1.2 Generating a Cycle Model

For more details about the Cycle Model Compiler command-line options and directives see Chapter 3 and Chapter 4 respectively.

# 1.3 What is a Cycle Model?

A Cycle Model is a high-performance linkable software object that is generated by the Cycle Model Compiler directly from RTL design files. The Cycle Model contains a cycle and register-accurate model of the hardware design in the form of a software object file, header file, and supporting binary database. *By default*, the Cycle Model Compiler generates these files in the current working directory ( . / ) as listed below:

- libdesign.a Cycle Model object library (Linux) libdesign.lib Cycle Model object library (Windows)

- libdesign.h Cycle Model header file

- libdesign.symtab.db database with information about all internal signals

- libdesign.io.db a subset of libdesign.symtab.db that includes top-level inputs, outputs, inouts, and those signals marked as observable or depositable (to the external environment)

In general, when integrating the Cycle Model into a simulation environment, you should use the symtab.db. The io.db file is provided for use if you are passing your Cycle Model on to a third-party customer and you want to restrict the visibility of your design.

For information about the Cycle Model Compiler output files, see "Cycle Model Compiler Output Files" on page 2-15.

# 1.3.1 Using a Cycle Model

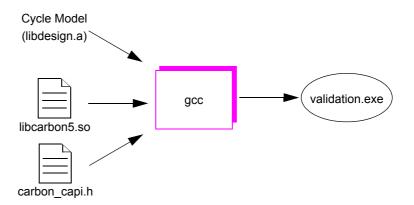

Cycle Model files must be linked with a standard software compiler, such as gcc or Microsoft® Visual C++TM, before they can be run in the software test environment. The following files are required to create a proper executable:

- libdesign.a-Cycle Model

- libdesign.h-Cycle Model header file

- libcarbon5.so-Cycle Model shell

- carbon capi.h API header file

Note that libcarbon5.so and carbon capi.h are provided in the installation package.

The following file is required in a Windows environment:

• libdesign.lib - Windows static library implementation

In addition, the .db file must be accessible to the Cycle Model at runtime (it should be located in the same directory as the validation executable).

Figure 1.3 Generating an Executable Model

The Cycle Model is controlled by your software test environment. A software program, such as a driver, can communicate with the hardware model directly through sockets, through the Cycle Model API, or through an Instruction Set Simulator (ISS). For embedded software—where the software is loaded into a hardware memory model—a software debugger may be linked to the embedded software through the Cycle Model API.

# 1.4 The Cycle Model API

The Cycle Model API provides the C functions necessary to link a Cycle Model into a software test environment. You can access the value of any net in the design—including memories—deposit values on nets, dump signal waveforms, and supply time and timescale information to the design.

The Cycle Model API is "handle" based—meaning that in order to query and manipulate a specific design structure in a Cycle Model, you must use its handle or ID (rather than the full HDL path name). Following are the primary reference structures that provide access into a Cycle Model.

- CarbonObjectID Provides the context for a design, and is used to run the design's core function(s).

- CarbonWaveID Provides signal waveform dump control. Standard Verilog VCD and Debussy's FSDB formats are supported.

- CarbonNetID Used to access nets in the design. API functions allow you to examine signal values, deposit values on signals, and force signals to specific values.

- CarbonMemoryID Used to access memories in the design. API functions allow you to examine memory values and deposit values into memories.

See the *Cycle Model API Reference Manual* for detailed information about all API files and functions.

# 1.5 RTL Remodeling Tasks

There are certain hardware constructs that the Cycle Model Compiler does not currently support; they must be remodeled using supported constructs.

#### Phase-Locked Loops

PLLs implement behavior that occurs without cycle dependencies, and therefore are not supported. Designs that use PLLs must be modeled to bypass the PLL and drive the generated clocks from the external environment via the API, or to provide pass-through logic. The Cycle Model API will be able to drive PLL-generated clocks without needing to bring the clock to a primary input.

#### **Memories**

Vendor-provided memory libraries often use behavioral constructs that the Cycle Model Compiler does not support. These memories need to be remodeled using constructs supported by ARM.

#### **Low-level Constructs & Gate-level Modeling**

Though the Cycle Model Compiler supports gate-level constructs, the use of high-level Verilog constructs generally yields higher performance Cycle Models and is highly recommended. A common example of a gate-level construct that can be improved with high-level modeling is a pad cell.

The above remodeling is required for proper Cycle Model Compiler function. Tips for additional remodeling that can improve performance can be found in the *RTL Style Guide*.

# Getting Started with the Cycle Model Compiler

This chapter shows you how to compile a design with the Cycle Model Compiler from the appropriate input files and then link the resulting software executable to a testbench. For a complete list of system requirements, see the *Cycle Model Studio Installation Guide* (ARM DUI.

# 2.1 Setting up the Example Environment

To obtain the source files for this example, perform the following steps:

1. Using syntax appropriate to your shell, make sure that the following environment variables are set.

```

CARBON_HOME =<install dir>

PATH =$CARBON_HOME/bin:$PATH

where <install dir> is the installation directory.

```

2. Create a working directory for your experiments. For example:

```

mkdir ~/cycle_model_experiment

cd ~/cycle model experiment

```

3. Copy the example files into your local work directory.

```

cp -r $CARBON HOME/examples/twocounter ./twocounter

```

4. Change to the twocounter directory.

```

cd twocounter

```

The files in this directory include the following:

- Makefile

- Makefile.shared

- Makefile.notes

- twocounter.v HDL code for the design

- twocounter.c-C code for test harness

- twocounter.gold expected output for test harness

# 2.2 The Example Hardware Design

This example is a simple design with two counters driven by two clocks.

# 2.2.1 Verilog Twocounter Example

Note: To run the Verilog version with SystemVerilog, use the -sverilog command line switch.

```

module twocounter(clk1, clk2, reset1, reset2, out1, out2);

input clk1, clk2, reset1, reset2;

output [31:0] out1, out2;

reg [31:0] out1, out2;

always @(posedge clk1)

if (reset1)

out1 <= 32'b0;

else

out1 <= out1 + 32'd1;

always @(posedge clk2)

if (reset2)

out2 <= 32'b0;

else

out2 <= out2 + 32'd3;</pre>

```

endmodule

# 2.3 The Makefile

Before you run any of the examples, examine the Makefile. This is typically how the validation process is run, rather than invoking each tool separately. This Makefile uses variables to invoke the Cycle Model Compiler, to invoke GNU compilers, and to access a list of link libraries. Using these variables in your projects' Makefiles will help ensure smooth operation, and facilitate future product upgrades. The Makefile does the following:

- 1. Compiles the design file into a Cycle Model using the Cycle Model Compiler.

- 2. Compiles the software harness into a software harness object using gcc.

- 3. Links the Cycle Model with the software harness object using g++ to produce a software validation executable.

- 4. Invokes the software validation executable to generate run-time output.

- 5. Compares the run-time output with the expected values (twocounter.gold file).

Note: The CARBON\_LIB\_LIST make variable links the program so that LD\_LIBRARY\_PATH overrides -rpath, therefore, a single GCC version should be used within your environment to

avoid library conflicts. While a Cycle Model itself has no dependencies on compiler libraries,

custom code compiled with the ARM-provided GCC may. If this code is integrated into an

environment that uses a different version of GCC (for example, a third-party tool), runtime

errors may occur. In environments such as this, it is recommended that the GCC provided by

the third-part tool be used to compile the custom code.

Following is an excerpt from the Makefile.

```

# Makefile for twocounter example.

#

# Notes on Makefile variable definitions are in

# $(CARBON_HOME)/examples/twocounter/Makefile.notes

#

# Common Makefile for all languages, platforms.

include $(CARBON_HOME)/examples/twocounter/Makefile.common

# Makefile targets for twocounter example.

twocounter.exe: twocounter.o libtwocounter.a

$(CARBON_LINK) twocounter.o -o twocounter.exe \

libtwocounter.a $(CARBON_LIB_LIST)

twocounter.o: twocounter.c libtwocounter.a

$(CARBON_CC) -c twocounter.c -I$(CARBON_HOME)/include

# The following line is found in Makefiles when the top module

# is written in Verilog

libtwocounter.a: twocounter.v

$(CARBON_CBUILD) twocounter.v -o libtwocounter.a

```

Note: If you want to test the installation, you can simply run the Makefile with the Linux make command.

# 2.4 Running the Example

In this example, you first create a Cycle Model from your design and then create and test a validation executable using your Cycle Model. For an example using C-models and Cycle Models, see the *Cycle Model API Reference Manual*.

1. To compile a Cycle Model for this design, issue the following command:

```

make libtwocounter.a

```

You could also compile the Cycle Model using the cbuild command:

```

Verilog: cbuild twocounter.v -o libtwocounter.a.

```

```

SystemVerilog: cbuild twocounter.v -sverilog -o \

libtwocounter.a

```

The -o option specifies a name for the Cycle Model Compiler output files; the .a extension generates a traditional object archive.

The Cycle Model Compiler compiles a Cycle Model object for the specified design. The following message is generated upon successful completion of the compilation (provided the -q command option has not been specified):

```

Note 111: Successfully created libtwocounter.

```

The Cycle Model Compiler creates many output files; for a description of the important files, see "Cycle Model Compiler Output Files" on page 2-15.

If you examine libtwocounter.cmd, you can see that it executed the cbuild command as given above.

Note that if a compilation is unsuccessful, the Cycle Model Compiler generates a message that indicates which phase the error occurred in, as well as the number of warning, error, and alert messages:

Note 110: There were errors during the <phase name> phase, cannot continue. 0 warnings, 1 errors, and 1 alerts detected.

2. Examine the twocounter.c file. This file contains Cycle Model API code that will direct the executable in test. Notice that the header file libtwocounter.h is explicitly included—this header file is part of the generated Cycle Model and is required for linking the object into a test environment.

The Cycle Model is explicitly instantiated with the <code>carbon\_twocounter\_create</code> command. This provides context for the design and is used to run the design's core functions. This is followed by a series of functions that exercise the nets—values are deposited on nets and then examined on a schedule.

3. To compile the software harness using gcc, issue the following command:

#### make twocounter.o

The file twocounter.c will be compiled into a software harness object.

4. To link the Cycle Model to the software harness object and create a software validation executable using g++, issue the following command:

#### make twocounter.exe

5. Once the software validation executable has been generated, you can run it with the Cycle Model engine. Issue the following command:

#### make twocounter.out

The results of the tests, which are directed by the software harness, will be output to the twocounter.out file:

```

0: clk1=1 reset1=1 clk2=1 reset2=1 out1=0 out2=0

100: clk1=1 reset1=1 clk2=1 reset2=1 out1=0 out2=0

200: clk1=1 reset1=1 clk2=1 reset2=1 out1=0 out2=0

300: clk1=1 reset1=1 clk2=1 reset2=1 out1=0 out2=0

400: clk1=1 reset1=1 clk2=1 reset2=1 out1=0 out2=0

500: clk1=1 reset1=1 clk2=1 reset2=1 out1=0 out2=0

600: clk1=1 reset1=1 clk2=1 reset2=1 out1=0 out2=0

700: clk1=0 reset1=1 clk2=1 reset2=1 out1=0 out2=0

800: clk1=0 reset1=1 clk2=0 reset2=1 out1=0 out2=0

```

6. To compare this output with the contents of twocounter.gold, use the following command:

#### make twocounter

You can see that the hardware design is behaving as expected.

7. If you would like to rerun the example, you can use the following command to clean up the twocounter directory:

#### make clean

# 2.5 Cycle Model Compiler Output Files

The Cycle Model Compiler writes many files to the working directory. You may find the following files useful for interpreting the Cycle Model:

| File                                     | Description                                                                                                                                                                                                                                                                        |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ./libtwocounter.a<br>./libtwocounter.lib | The Cycle Model file. The type of file created depends on which extension is specified with the -o option (*.a is the default). The .a file is for Linux, the .lib file is for Windows.                                                                                            |

| ./libtwocounter.h                        | Cycle Model header file.                                                                                                                                                                                                                                                           |

| ./libtwocounter.symtab.db                | Database containing information about <i>all</i> internal signals.                                                                                                                                                                                                                 |

| ./libtwocounter.io.db                    | Database containing information about <i>only</i> those IOs marked as <i>observable</i> (to the external environment). Used instead of the *.symtab.db file if you are passing your Cycle Model to a third-party customer, and you want to restrict the visibility of your design. |

| ./libtwocounter.cmd                      | All commands passed to Cycle Model Compiler, including those passed on the command line and those passed in a command file.                                                                                                                                                        |

| ./libtwocounter.dir                      | All directives that were parsed during the compile, including those in a directives file and any embedded (inline) directives.                                                                                                                                                     |

| ./libtwocounter.hierarchy                | Table of every module instance in the design and its corresponding RTL file.                                                                                                                                                                                                       |

| ./libtwocounter.designHierarchy          | The instance hierarchy, with the architecture name, for all the design units used in the design. It also includes the library for each design unit, the location of the design unit, and the ports and generics used.                                                              |

| ./libtwocounter.warnings                 | Warnings encountered during the compile.                                                                                                                                                                                                                                           |

| ./libtwocounter.errors                   | Errors encountered during the compile. If the compilation succeeds, this file is created anyway, but is empty.                                                                                                                                                                     |

| ./libtwocounter.suppress                 | Messages suppressed during the compile.                                                                                                                                                                                                                                            |

In addition, the Cycle Model Compiler writes the following files that are used by the Cycle Model Compiler or the Cycle Model development team. Assuming the compilation finished successfully, you may ignore these files:

- lib<design>.clocks

- lib<design>.cmodel.dir

- lib<design>.congruence

- lib<design>.costs

- lib<design>.cycles

- lib<design>.dclcycles

- lib<design>.drivers

- lib<design>.flattening

- lib<design>.init.v

- lib<design>.latches

- lib<design>.netvec

- lib<design>.parameters

- lib<design>.prof

- lib<design>.scheduleStatistics

- lib<design>.vfiles

- .carbon.lib<design> This directory contains files used internally and can be safely deleted when you are cleaning up your compiled files.

# Cycle Model Compiler Command Line Options

This chapter provides detailed information about the cbuild command-line syntax and options. You can use these options, along with directives, to provide control and guidance to the Cycle Model Compiler. See Chapter 4 for information about directives.

# 3.1 Command Syntax

The cbuild command invokes the Cycle Model Compiler. It compiles the design files, libraries, and directives that you specify into a Cycle Model. The command syntax is as follows:

```

cbuild [options] <design file list>

```

Where <design file list> is the list of design files you want to include in the compile. A Cycle Model may be compiled from several design and library files. When you invoke the Cycle Model Compiler, list all necessary design files and referenced library files. In addition, you *may* want to specify the top-level module in a Verilog or SystemVerilog design (see "-vlogTop <string>" on page 3-28).

Note that the Cycle Model Compiler processes files in the following order:

- 1. Command options files (specified with the -f option)

- 2. Directives files (specified with the -directive option)

- 3. Design and library files

If any errors are encountered during the compile, they are displayed to standard output. The error will consist of an error number and a brief error description.

# 3.2 Command Options

As a general rule, command options are processed in the order that they are specified on the command line (whether explicitly or within an options file, see "-f|-F <string>" on page 3-21). If an option is defined multiple times, the Cycle Model Compiler generates a warning at each successive encounter and will ultimately use the value of the last one specified.

All options must include any special characters (for example, -, \_, +, etc.) that appear in the option name—spaces are not allowed *within* an option name. Also note that all options are case sensitive.

The table below lists the available categories of Cycle Model Compiler options:

| Compiler Option                             | Location  |

|---------------------------------------------|-----------|

| General Compile Control                     | page 3-18 |

| Input File Control                          | page 3-21 |

| Module Control                              | page 3-22 |

| Net Control                                 | page 3-24 |

| Verilog- and SystemVerilog-Specific Control | page 3-28 |

| Output Control                              | page 3-32 |

# 3.2.1 General Compile Control

#### -h|-help

Use this option to print the documentation for compiler options. The compiler help information displays, and then the compiler exits.

#### -lica

Use this option to enable license queuing for the Cycle Model Compiler. When specified, the Cycle Model Compiler waits for a license to become available rather than exiting immediately if all licenses are in use.

# -loopUnrollLimit <integer>

Use this option to set the maximum number of loop iterations allowed for static elaborated loops (FOR, GENERATE FOR, WHILE, FOREVER, DO). The default value is 5000.

Use this option in the event the compiler emits errors related to the loop count limit; for example:

foo.v:22: Error 51066: loop count limit of 5000 exceeded; condition is never false

### -j <integer>

Use this option to limit the number of parallel make sub-jobs—the number of Cycle Model compilations running in parallel. The default value is 4. Set this value to 1 for serial runs.

Note: You may set this option to any positive integer value you want, however the Cycle Model Compiler performance may not be optimal if it is set too high. Also note that you may need to use a smaller number if the compile process produces errors that point to a possible memory issue.

#### -multi-thread

Use this option to generate a thread-safe Cycle Model. Enable this option if you want the generated Cycle Model to be used in a multi-threaded environment. Multi-threading is supported in the Cycle Model API, *with some exceptions*. Note that using this option may impact the performance of the resulting Cycle Model.

If you are generating a Cycle Model for Windows and linking with the multi-threaded Windows libraries (library names ending in MT.lib or MTD.lib) it is recommended that you use this option.

Caution: Consult your ARM Cycle Models Applications Engineer for guidance when using this option.

### -O <string>

Use this option to control the design optimization level—higher optimizations may result in a faster Cycle Model. The optimization levels are defined in the following table. Note that the *s* value is case sensitive, meaning that *S* is *not* equivalent to *s*.

| Level | Passes to g++ | Optimizations                                                                                                |

|-------|---------------|--------------------------------------------------------------------------------------------------------------|

| 0     | -O0           | None                                                                                                         |

| 1     | -O1           | Basic                                                                                                        |

| 2     | -O2           | Advanced (the default setting)                                                                               |

| 3     | -O3           | Advanced, aggressive inlining                                                                                |

| S     | -Os           | Generates a smaller code size for the Cycle Model, which can improve performance for <i>certain</i> designs. |

### -phaseStats

Use the -phaseStats option to print the time and memory statistics for each compile phase.

### -profileGenerate

You can use this option with the -profileUse option to generate more efficient (faster) Cycle Models as follows:

- 1. Run the Cycle Model Compiler using -profileGenerate.

- 2. Link using gcc's -fprofile-generate option.

- 3. Run the Cycle Model in your simulation environment.

- 4. Rerun the Cycle Model Compiler using the -profileUse option.

Note: This option and the -profileUse option are not related to the -profile option. The -profileGenerate and -profileUse options result in a more efficient Cycle Model, but the output is not displayed for your analysis.

Note: The flow with -profileGenerate and -profileUse options is currently NOT supported with Windows.

# -profileUse

Recompile using feedback from profile directed optimization. As shown in the flow above, use this option after compiling with -profileGenerate and linking with gcc's -fprofile-generate option and simulating the Cycle Model in your validation environment. This option reuses much of the previous compilation, so HDL changes and many of the Cycle Model Compiler options are ignored.

#### -clockGlitchDetect

#### -noClockGlitchDetect

The default behavior is to create a model that supports glitch detection (-ClockGlitchDetect). This provides a way to use glitch detection when the model is run, which enables the names of internal clocks to be reported from the model. When glitch detection is disabled at compile time (using -noClockGlitchDetect), there is no way to enable it at runtime in the resulting model.

#### -annotateCode

Use this option to annotate the generated C++ code for C++ fault diagnosis. By default, both HDL and implementation annotations are disabled. An HDL annotation associates a location in the generated C++ model with a file name and line number in the HDL design. An implementation annotation associates a location in the generated C++ model with a location in the Cycle Model Compiler implementation. Please consult with your ARM Cycle Models Applications Engineer before using this option.

#### -topLevelParam <parameter/generic>=<value>

Use this option to specify new values for Verilog parameters of top-level modules. By default, the Cycle Model Compiler compiles parameters using their default values.

You can specify this option multiple times to account for all the parameters and generics in the top level design unit. Any parameters and generics not specified using this option retain their default values. For parameters, the case of the parameter name has to match.

Note: If special characters, such as single or double quotes, are to be used as part of the value for the parameter, you must use the Escape sequence (backslash) before the special character; for example, -topLevelParam ABC=20\'h1234. This allows the compiler to properly convert and store the value. This method works both on the command line and within a -f file.

Errors are generated under the following conditions:

- If a parameter or generic specified using this option does not exist in the top-level module.

- If the top-level module does not have any parameters.

# 3.2.2 Input File Control

### -f | -F <string>

Use this option to specify a command file name from which the Cycle Model Compiler reads command-line options. The compiler treats these options as if they have been entered on the command line. Note that options specified in files are cumulative. Enter the full path or relative file name after the -f. There is no restriction on file naming.

The syntax of the file is simply a white-space separated list of options and arguments; each option does not need to be specified on a new line. The file may also contain comments that use any of the following delimiters: # (shell), # or # ... # (C++ style).

The file may also include entries that include environment variable expansion, as follows:

| \$varname   | Supported. The variable name must be followed by a space or a recognized delimiter.                                                                                                                   |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \${varname} | Supported. Curly braces can be used in cases where there is no recognized delimiter.                                                                                                                  |

| \$(varname) | Not supported. Parenthesis are not recognized as valid delimiters for environment variables. This follows the same rules as the tesh, csh, bash, and sh shells, as well as the nc and mti simulators. |

For example, the following items show valid variables usage in a command file:

```

$TEST_DIR/test1.v - valid because / is a recognized delimiter

${TEST_DIR}test1.v - the curly braces are required because no / is used

${TEST_DIR}/test1.v - the curly braces are not required in this case, but

they are ignored when not needed

```

Note that the environment variable TEST\_DIR must be defined before the Cycle Model Compiler uses the environment variable or you will receive an error.

### -directive <string>

Use this option to include a directives file on the command line. Multiple instances of the -directive option are allowed. Note that directives specified in files are cumulative. The syntax of a directives file is line oriented—each directive and its values must be specified on its own line. Enter the full path or relative file name after the -directive. There is no restriction on file naming, however it is standard to use a '.dir' or '.dct' suffix for directives files. See Chapter 4 for more information about directives.

#### -attributeFile <string>

Use this option to specify a file name from which the Cycle Model Compiler will read Cycle Model attributes. These attributes are used by the generated model at runtime. In general, the attribute file is generated by Cycle Model Studio and should *not* be edited.

#### -showParseMessages

If you specify this option, the Cycle Model Compiler writes messages to stdout as it analyzes HDL source files. The current source file being analyzed is printed, and the modules found within each source file are printed. This can be useful during initial model compilation when you want to ensure that the Cycle Model Compiler uses the correct source files.

#### Example output:

```

Note 20001: Analyzing source file "test.v" ... test.v:1: Note 20004: Analyzing module (top). test.v:5: Note 20004: Analyzing module (child). Note 20025: 0 error(s) 0 warning(s).

```

# 3.2.3 Module Control

# -tristate <string>

Use this option to set how tristate data will appear in waveforms. You can set tristate mode to one of the following values: 1, 0, x, and z. Note that the value is case insensitive. The following table defines the tristate propagation and waveform display for each tristate mode. Note that X/Z propagation will *always* result in x and z=don't care.

| Setting     | Tristate Propagation / Waveform Display     |

|-------------|---------------------------------------------|

| -tristate 0 | don't care / 0                              |

| -tristate 1 | don't care / 1                              |

| -tristate z | don't care / Z                              |

| -tristate x | don't care / don't care (the default value) |

Setting this option to x provides the best Cycle Model performance; setting it to z provides maximum visibility into the model.

### -checkpoint

# -noCheckpoint

By default, -checkpoint is enabled, causing the Cycle Model Compiler to generate checkpoint save/restore support in the compiled Cycle Model. API functions can then be used to save and restore a given state of the Cycle Model during validation runtime. To disable this option, use -noCheckpoint.

#### -noFlatten

By default, the Cycle Model Compiler flattens design modules into their instantiating parent module based on the value of -flattenThreshold (see next). Use this option to disable flattening completely. This can improve design visibility, but may produce a slower Cycle Model.

Note that you may use the directives described in "Flattening" on page 4-48 to conditionally or unconditionally flatten modules. However, these directives are effective only if this option has *not* been specified.

### -flattenThreshold <integer>

Use this option to specify the largest child module that will be considered for flattening into their parent module. The size of a module is computed based on the number of assignment statements (blocking and non-blocking) contained within that module. The default value is 25.

In general, threshold values between 10 and 50 yield the best results. However, the *best* threshold is really *design dependent*, so recompiling your design with different values will help determine the optimal value.

### -flattenParentThreshold <integer>

Modules that are too large can decrease the performance of your model. Use this option to specify the maximum parent module size during flattening. Once a module reaches the size specified in this option, no more children will be flattened into the module unless the child modules are tiny (see -flattenTinyThreshold). The default value is 10000.

# -flattenTinyThreshold <integer>

Use this option to flatten modules of this size or smaller, even if their parent modules have reached the limit defined in -flattenParentThreshold. The default value is 10. This value should be less than the value specified in -flattenThreshold.

#### -inlineTasks

Use this option to replace all task and function calls with the contents of the called task or function. This option may enable further optimization, resulting in a faster Cycle Model. However, be aware that inlining large tasks/functions that have multiple calls may increase the size of the Cycle Model and therefore produce a slower model.

To inline selected tasks or functions, see the -inlineSingleTaskCalls option (next) and the inline directive (see page 4-48).

Tasks with hierarchical referrers are not considered for inlining; for example, if module a calls task x through the hierarchical path a.b.x, then no call of x is inlined.

Note: Using the -inlineTasks option on designs that require a great deal of memory to compile may cause a memory allocation error. For these cases, we recommend using the inline directive.

#### -inlineSingleTaskCalls

Use this option to inline any tasks and functions that have only a single call. In other words, if a task or function is only called once, that call is replaced with the contents of the task or function. This option may enable further optimization, resulting in a faster Cycle Model.

Tasks and functions with hierarchical referrers are not considered for inlining; for example, if module a calls task x through the hierarchical path a.b.x, then no call of x is inlined.

#### 3.2.4 Net Control

#### -<u>Q</u>

Use this option to increase visibility of design nets for debugging purposes. Note that not *all* nets in the design will be preserved. Dead nets—nets that do not reach primary outputs—are not livened by this option. See "observeSignal < list of signals>" on page 4-43 for more information about making signals observable.

# -waveformDumpSizeLimit <integer>

Use this option to specify the maximum size (in bits) of design elements that should be dumped to waveform files. The default value is 1024 bits. Set this value to 0 in order to dump all waveforms; regardless of size. This is an alternative to the carbonDumpSizeLimit() API function, although the API function has precedence if both are specified. Multiple instances of this option are allowed.

### -memoryCapacity <integer>

Use this option to specify the total amount of runtime memory (in bytes) allocated to memories. The default value is 4194304 (4Mb). Memories which cause the model to require more than this amount of space will be coded as sparse memories. By default, memories use a fast array based representation. Sparse memories use a memory-efficient, hash table based implementation. A value of 0 will generate only sparse memories. A value of -1 will not generate any sparse memories

*Note:* This option replaces the -sparseMemoryThreshold option.

### -bufferedMemoryThreshold <integer>

Use this option to set the threshold size to allow larger memories to be buffered. The default is 16384 bits.

The following code example causes the Cycle Model Compiler to encounter a scheduling conflict because it wants to schedule the flop that writes to data *before* it schedules the flop that writes to out.1.

In this case, data could race through.

```

module top (out1, out2, clk, rst, en, in);

output [3:0] out1, out2;

input clk, rst;

input [3:0] en, in;

req [3:0] data [1:0];

// Put all the inputs into a memory

always @ (posedge clk or posedge rst)

begin

if (rst)

begin

data[0] <= 4'b0;

data[1] <= 4'b0;

end

else

begin

data[0] <= en;

```

```

data[1] <= in;

end

end

// Create a clock from the enable

wire [3:0] ren = data[0];

wire dclk = clk & ren[0];

req [3:0] out2;

always @ (posedge dclk)

out2 <= data[1];

// Use those clocks and the data

reg [3:0] out1;

always @ (posedge clk)

begin

out1 <= data[1];

end

endmodule

```

The Cycle Model Compiler resolves this scheduling conflict by introducing a delay in the data before it gets to out1. However, for performance reasons it only does so if the memory is 16384 bits or less. If the memory is larger than 16384 bits, then the Cycle Model Compiler issues an alert. For example:

```

bufmem.v:57 top.out1: Alert 1054: A memory `top.data` that is written as part of clock logic is read in a flop; the conflict could not be resolved. See the documentation for -bufferedMemoryThreshold for information on this problem.

```

There are three options for dealing with this alert. The first option is to demote the alert to a warning if the race condition does not matter. The second is to increase the buffer memory threshold using this option. Lastly, you can remodel the above code by writing to the data memory in different always blocks for the clock enable and data portions.

#### -no-OOB

Use this option to disable checking for out-of-bounds bit references. This means the Cycle Model Compiler should not check for such references. As a result, the Cycle Model runtime will be faster.

Warning: If you specify this option, the Cycle Model will exhibit unpredictable behavior during runtime if there are out-of-bounds bit references in your design.

Consider the following:

```

wire [7:0] value;

wire [7:0] index;

. . .

result = value [index];

```

If index can take on a value larger than 7, this may produce incorrect answers when -no-oob is specified. The index values greater than 7 are out of bounds.

#### -checkOOB

Use this option to generate warning messages during validation runtime if any out-of-bounds bit or memory references are made. Ideally, you would use -checkOOB to ensure that your design has no out-of-bounds references and then recompile using -no-OOB to generate a Cycle Model with a faster execution time.

If -checkoob detects any out-of-bounds references, fix the out-of-bounds references in your design as necessary and then recompile with -no-oob. The warning message generated by -checkoob does not pinpoint the name of the vector or memory containing the out-of-bounds reference, but gives the following information to help your search:

- Whether the out-of-bounds access occurs on a read or write

- Whether the accessed object is a memory, register, wire, or net.

- The declared range of the object.

- The invalid index value.

#### -noCoercePorts

Use this option to disable port analysis (as described in the following paragraphs). Note that turning off the port analysis functionality disables the Cycle Model Compiler's ability to process complex bidirectional ports.

# Port Analysis:

By default, the Cycle Model Compiler performs a design-wide port analysis and may alter port directions based on the characteristics of the design. In particular, these modifications may occur when the declared port directions do not model the flow of data within the design. For example:

```

wire data;

sub s0(en1,data,out1);

sub s1(en2,data,out2);

...

module sub(en,data,ndata);

input en;

output data;

output ndata;

assign data = en ? 1'b1 : 1'bz;

assign ndata = ~data;

endmodule

```

In this design, the sub.data wire has multiple drivers. Converting sub.data from output to inout properly models the fact that a value written in the s0 instance can be read in the s1 instance, and vice-versa.

# **Primary Ports:**

The assumption today is that a unidirectional primary port is a stronger statement than a bidirectional primary port. This means that a user-declared primary input must at least behave as an input. A user-declared primary output must at least behave as an output. Therefore, inputs/outputs may be coerced to inouts, but not to output/input.

Primary inouts are handled differently—their bidirectional nature is considered a weaker statement, therefore coercion from inout to either directional port type is allowed.

#### Per-bit Port Behavior:

Port analysis may determine that all bits in a primary port do not behave in a uniform fashion. If this occurs, different bits may be identified as having different port direction. For example:

```

module top(a,out1,out2);

input [1:0] a;

output out1,out2;

pullsub p0(a[0],out1);

assign out2 = a[1];

endmodule

module pullsub(in,out);

input in;

output out;

pullup(in);

assign out = in;

endmodule

```

In this design, the top. a net will be split into two components. The a [0] bit will be converted to a bidirectional port to reflect the fact that it is driven by the model. The a [1] component of top. a remains an input.

#### -sanitizeCheck

Use this option to check for dirty writes. After every write to a net, it will check for non-zero bits outside the declared size of the net. This helps to detect out-of-bound reads/writes permitted by the -no-oob flag in order to help diagnose problems.

#### 3.2.4.1 Port Vectorization

To improve runtime performance, the Cycle Model Compiler replaces selected scalar ports and scalar local variables with a vector port or local nets.

#### -doNetVec

Enable port vectorization. Port vectorization is *on* by default.

### -noNetVec

Disable port vectorization. You might want to turn off port vectorization if you suspect that 1) a modeling error has resulted from port vectorization, or 2) port vectorization has broken visibility for some signals. In either of these cases, you should initiate a bug report with ARM.

#### **Three Options for Vectorizing Primary Ports**

The following three options are mutually exclusive. The default is -netVecThroughPrimary.

Note: -netVec line options have been replaced by -netVec. If used, a warning message will appear notifying you to switch to the -netVec options.

#### -netVecPrimary

Vectorize the primary ports of the design.

Warning:

This option breaks visibility of any primary ports that are vectorized. When scalar primary ports are combined into vectorized ports, the original port names are replaced with a new vectorized port name. At the moment, you cannot make any Cycle Model API calls (such as observeSignal or depositSignal) using either the old or new port names.

# -netVecThroughPrimary

Do not vectorize the primary ports; however, allow vectorization opportunities inferred between the primary ports to propagate down the module hierarchy (default).

# -nonetVecThroughPrimary

Do not infer any vectorization opportunities from the primary ports and do not allow propagation of opportunities through the primary ports.

# -netVecMinCluster <integer>

Specifies the minimum size of a vector created during net vectorization.

#### -verboseNetVec

Output information on the vectorized nets.

### -reportNetVec <filename>

Write a report to the specified <filename>, enumerating the vectorizations discovered by port vectorization.

# 3.2.5 Verilog- and SystemVerilog-Specific Options

The following options are for use only with Verilog and SystemVerilog design files.

### -sverilog

This option enables SystemVerilog compilation mode. All Verilog files encountered during compilation will be treated as SystemVerilog source files. All Verilog command line options work with SystemVerilog, provided -sverilog is specified.

## -vlogTop <string>

Use this option to specify the top-most module in the Verilog design hierarchy. The Cycle Model Compiler parses *only* the specified module and its descendents. If you do not specify this option, all modules from the top down in the given design are compiled.

*Note:* Currently, only one top-level module is supported.

### -v <string>

Use the -v option to specify a Verilog source library file. The Cycle Model Compiler scans the file for module definitions that have not been resolved in the specified design files. Enter the full path or relative file name after the -v. For example:

cbuild -v ../library/vendor.lib 2clock.v

Note: Without this option, the Cycle Model Compiler processes only those library modules that are explicitly referenced by the Verilog source files.

### -y <string>

Use the -y option to specify a library directory. The Cycle Model Compiler scans the directory for module definitions that have not been resolved in the specified design and library files. Enter the full or relative directory path after the option. For example:

```

cbuild -y library/cells 2clock.v

```

This command references the library directory /library/cells for input design files.

Note: The file names within the specified library directory must match the module names that are being searched for.

In the event two subdirectories contain a file with the same name and the top level design file in the current directory uses a single instance of that file, the Cycle Model Compiler uses the definition of the file from the directory that appears first on the command line:

```

cbuild -q -y foo -y bar +libext+.v test.v

```

In the above case, the definition of the file from the foo directory is used.

#### +libext+<ext1>+...

Use the +libext+ option to specify extensions on the files you want to reference in a library directory. Note that this option has the default value of '.v'. However, if you specify this option on the command line then the default is replaced.

To specify multiple extensions, enter the list of extensions after the option linked with plus signs (+). For example:

```

cbuild -y library/cells +libext+.v 2clock.v

```

This command references the library directory library/cells, but uses *only* those files in that directory with the extension '.v'.

Note that only one +libext+ option can appear on the command line, however it can specify multiple extensions. For example, +libext++.v+.vlog+, indicates that there are three possible extensions: a null string, '.v', and '.vlog'.

#### +incdir+<path1>+...

Use the +incdir+ option to specify the directories in which the Cycle Model Compiler should search for include files. Enter the list of relative or absolute paths, linked with plus signs (+). The paths will be searched in the order specified. (Note that -incdir can be used by NC-Verilog simulation users to specify a single directory.)

You can enter multiple +incdir+ options on the command line. If there is a conflict between values in include files, the last one encountered will be used.

#### -2001

Use this option to enable Verilog-2001 compilation mode. This includes partial support for Verilog-2005 (IEEE Std 1364-2005) language features (refer to "General Constructs" on page 5-52 for supported constructs). All files encountered during the compilation are treated as Verilog 2001. Note that you may also use -2000 or -v2k to enable this compilation mode—these three options are equivalent.

#### -u

Use this option to convert all identifiers in all referenced Verilog files to upper case. Performing this option makes the design insensitive to identifiers' case.

Note: All references to Verilog identifiers in options and identifiers within directives must be changed to upper case.

For example, when using -u:

-vlogTop top should be changed to -vlogTop TOP

# +define+<string>

Use the +define+ option to specify Verilog macros to be used during compilation. Enter the variables with values, linked with plus signs (+). Syntax:

```

+define+<var1>+<var2>+ ... +<varN>=<value>

```

Note that an equals sign (=) in effect terminates the string. That is, anything after the equals sign will be treated as part of the value of the variable with which it is associated. For example:

```

cbuild 2clock.v +define+WORD_LENGTH=8

```

In this example, whenever 'WORD\_LENGTH appears in the Verilog text, it will be replaced with 8. Note that the <value> parameter is optional. For example:

```

cbuild 2clock.v +define+MYDEF

```

will make 'ifdef MYDEF statements true in the code.

The following example is equivalent to placing 'define var val statements in the code.

```

cbuild 2clock.v +define+var=val

```

Multiple +define+ options can be specified on the command line. Later +define+ options take precedence over earlier ones.

- +mindelay

- +typdelay

- +maxdelav

Use these options to specify the use of the minimum, typical, or maximum value respectively for all expressions.

*Note:* These options have no real effect—they are provided only for compatibility.

# -pragma\_prefix <string>

When embedding directives in comments, use this option to specify the prefix used for:

- Synthesis-specific compiler directives, such as translate\_off/translate\_on and full case/parallel case.

- Cyle Model-specific compiler directives, such as observeSignal and depositSignal. (For a complete list, see "Embedding Directives in Comments" on page 4-41.)

This option takes a single string argument. To specify multiple prefixes, you must specify -pragma\_prefix multiple times. Subsequent prefix specifications do not cancel earlier ones.

For example, to make the following signal observable:

```

reg a; // myPrefix observeSignal

```

you must include the following on the command line:

```

-pragma prefix myPrefix

```

If you do not use this option to specify a prefix, the synthesis and directives are ignored for all prefixes except carbon. The Cycle Model Compiler automatically recognizes the prefix carbon.

### -synth\_prefix <string>

This option is the same as the -pragma prefix option.

### -enableOutputSysTasks

By default, the Cycle Model Compiler issues a warning and ignores the following system tasks. Use this option to enable support for these system tasks *throughout* your design. Note that using this option may impact the performance of the resulting Cycle Model.

- \$display

- \$fclose

- \$fdisplay

- \$fflush

- \$fopen

- \$fwrite

- \$sformat

- \$write

A system task that appears within an edge-sensitive always block is scheduled with that clock. For example, the system task in the following example is scheduled with clk.

```

always @(posedge clk)

$display (a1, a2);

```

Note that the values displayed from calls to \$time functions may not match the times that are generated by a Verilog simulator. This can result in the following example output. Notice that in the Cycle Model Compiler output the time does not appear to change, but it does display identical values to the Verilog output for the out variable.

```

source verilog

always @(posedge clk) begin

begin

a = 1;

b = 0;

out = a

$display("a time: %t a=%b b=%b out=%b", $time, a, b, out);

a = 0;

out = #10 b;

$display("b time: %t a=%b b=%b out=%b", $time, a, b, out);

#10 $display("c time: %t a=%b b=%b out=%b", $time, a, b, out);

verilog

a time: 0 a=1 b=0 out=1

b time:10 a=0 b=0 out=0

c time:20 a=0 b=0 out=0

carbon

a time: 0 a=1 b=0 out=1

b time: 0 a=0 b=0 out=0

c time: 0 a=0 b=0 out=0

```

Note that you may enable or disable output system tasks by module using the directives described in "Module Control" on page 4-46.

### -topModuleListDumpFile <string>

Use this option to specify the name of the file into which the Cycle Model Compiler will place the names of the top level modules of the Verilog design.

# 3.2.6 Output Control

Warning: Do not edit any files that are generated by the Cycle Model Compiler. Doing so will result in unexpected behavior or failure of subsequent processes.

#### -o <string>

Use this option to specify the name of the compiled Cycle Model. The default is ./libde-sign.a. Use the appropriate extension for the operating system on which you will run the compiled design:

- a generates a Linux archive

- .lib generates a Windows library

Enter the full path or relative file name after -o. You may use alphanumeric characters, period (.), hyphen (-), underscore (\_), and plus sign (+) characters in your specification (either on the command line or within a Makefile). You *must* use the lib prefix for the file name. Do not use white spaces in the string, and do not use existing system library names (for example, libc, libm, carbon).

The Cycle Model Compiler creates additional files whose base names are the same as that used for the Cycle Model. For a list of output files created by Cycle Model Compiler, see "Cycle Model Compiler Output Files" on page 2-15.

Note: If your next step after creating the Cycle Model involves a new working directory, the following files must be copied to that working directory:

- 1) The Cycle Model (\*.a or \*.lib) file

- 2) The header (\*.h) file

\$CARBON\_HOME/examples/twocounter/Makefile.cygwin shows how to use Visual Studio 2013 to compile and link a testbench with a Cycle Model that was built using the Windows cross-development tools. The Makefile assumes you have a Windows machine with the Cygwin environment installed.

Note that you can use the -o option to direct model output for multiple platforms from the same directory substructure. For example, if you specify -o Linux/obj/libtest.a on the command line, the Cycle Model Compiler writes the output files to the Linux/obj directory.

### -noFullDB | -nodb

This option can be used with -embedIODB to turn off generation of the .symtab.db. Only the .io.db will be created and embedded into the library.

#### -embedIODB

By default, the Cycle Model Compiler creates and embeds the .symtab.db file into the Cycle Model, eliminating the need to search for it during runtime. This option additionally creates and embeds the .io.db file into the generated libdesign.\*library file. This option is enabled by default.

Note: The component for SystemC and Cycle Model Validation currently require the full database.

# -profile

Use this option to enable block profiling of the Cycle Model. This is sample-based profiling that records information, approximately 100 times/second, about which HDL block or Cycle Model API function is currently executing. Due to sampling, the data is an estimate only, but serves to give a rough idea of which blocks take the most time during your validation run.

Note: To enable profiling of Cycle Model API functions, a profile-enabled version of the library must be used. This library is selected by using \$(CARBON\_PROFILE\_LIB\_LIST) instead of \$(CARBON\_LIB\_LIST) in the Makefile used to link the executable.

# To use profiling:

1. Add the -profile option to the command line during compilation.

The Cycle Model Compiler creates a file named lib<design>.prof containing compile-time information needed for profiling. During simulation, ARM tracks how many samples occur in each block and writes this data to carbon\_profile.dat when the simulation ends.

2. Following simulation, run carbon profile at the command prompt.

The carbon profile command reads carbon\_profile.dat and all files matching \*.prof and corresponding \*.hierarchy files in the current directory. You can override which files are read by specifying specific files on the command line when you issue the carbon profile command.

The profiling results are sent to standard output.

Subsequent compilation runs overwrite the lib<design>.prof file and lib<design>.hierarchy file, and subsequent simulations overwrite the carbon profile.dat file.

Following is sample output using the carbon profile command:

| # Cum % Time Type Parent Location    Scale   S | Profiling da | ta collected May 21 200 | 10 00.03                 |                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------|--------------------------|-------------------------|

| Storm   Time   Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _            | •                       | 00:03                    |                         |

| 35.7 35.7 6.63 carbonSchedule 30.1 65.8 5.58 carbonDeposit 1.5 83.2 3.24 cOutside of Carbon> 2.4 85.6 0.44 carbonReadMemFile 1.8 87.4 0.33 AlwaysBlock sub profile1.v:26 1.2 88.6 0.23 AlwaysBlock flop profile1.v:53 1.0 89.7 0.19 AlwaysBlock flop profile1.v:77 0.9 90.6 0.17 (none) (none) 0.9 91.4 0.16 AlwaysBlock flop profile1.v:77 0.9 92.3 0.16 AlwaysBlock flop profile1.v:85 0.8 94.0 0.15 AlwaysBlock flop profile1.v:89 0.8 94.0 0.15 AlwaysBlock flop profile1.v:73 0.8 94.7 0.14 AlwaysBlock flop profile1.v:45 0.6 95.4 0.12 AlwaysBlock flop profile1.v:45 0.6 95.0 0.11 AlwaysBlock flop profile1.v:45 0.5 96.5 0.10 AlwaysBlock flop profile1.v:45 0.5 97.0 0.10 AlwaysBlock flop profile1.v:61 0.5 97.0 0.10 AlwaysBlock flop profile1.v:61 0.5 97.0 0.10 AlwaysBlock flop profile1.v:61 0.5 98.7 0.10 AlwaysBlock flop profile1.v:61 0.5 99.1 0.10 AlwaysBlock flop profile1.v:61 0.5 99.1 0.10 AlwaysBlock flop profile1.v:61 0.5 99.6 0.00 AlwaysBlock flop profile1.v:61 0.5 99.1 0.10 AlwaysBlock flop profile1.v:105 0.5 98.7 0.10 AlwaysBlock flop profile1.v:105 0.5 99.1 0.09 AlwaysBlock flop profile1.v:73 0.5 99.6 0.09 AlwaysBlock flop profile1.v:73 0.7 99.1 0.09 AlwaysBlock flop profile1.v:75 0.5 99.6 0.09 AlwaysBlock flop profile1.v:75 0.7 90.6 0.09 AlwaysBlock flop profile1.v:75 0.8 90.6 0.09 AlwaysBlock flop profile1.v:75 0.7 90.6 0.00 0.00 13.47 0.250 0.00 0.00 top (top) profile1.v:17 1 0.10 0.00 0.00 13.47 0.250 0.00 0.00 top (top) profile1.v:77 0 0.10 0.00 0.00 0.00 0.00 0.00 0.00 0.                                                                                                                                                       | _            |                         | Darent                   | Location                |

| 30.1   65.8   5.58   carbonDeposit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |                         | rarciic                  | Hocacion                |