# Integrator/IM-PD1 User Guide

Copyright © 2001-2003. All rights reserved. ARM DUI 0152E

## Integrator/IM-PD1 User Guide

Copyright © 2001-2003. All rights reserved.

#### **Release Information**

| Date          | Issue | Change                                                 |

|---------------|-------|--------------------------------------------------------|

| June 2001     | А     | Initial issue                                          |

| July 2001     | В     | Corrections to Table 3-3 on page 3-7.                  |

| July 2001     | С     | Corrections to Appendix A.                             |

| December 2001 | D     | Minor corrections to Chapter 3<br>Changes to Chapter 4 |

| December 2003 | Е     | Minor corrections to Chapter 3                         |

#### **Proprietary Notice**

Words and logos marked with <sup>®</sup> or <sup>™</sup> are registered trademarks or trademarks owned by ARM Limited, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

#### **Confidentiality Status**

This document is Open Access. This document has no restriction on distribution.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

#### **Conformance Notices**

This section contains conformance notices.

#### Federal Communications Commission Notice

This device is test equipment and consequently is exempt from part 15 of the FCC Rules under section 15.103 (c).

#### CE Declaration of Conformity

# CE

The system should be powered down when not in use.

The Integrator generates, uses, and can radiate radio frequency energy and may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment causes harmful interference to radio or television reception, which can be determined by turning the equipment off or on, you are encouraged to try to correct the interference by one or more of the following measures:

- ensure attached cables do not lie across the card

- reorient the receiving antenna

— Note ———

- increase the distance between the equipment and the receiver

- connect the equipment into an outlet on a circuit different from that to which the receiver is connected

- consult the dealer or an experienced radio/TV technician for help

It is recommended that wherever possible Shielded interface cables be used.

# Contents Integrator/IM-PD1 User Guide

|               | Prefa           | ace                                                          |      |

|---------------|-----------------|--------------------------------------------------------------|------|

|               |                 | About this book                                              | viii |

|               |                 | Feedback                                                     |      |

| Chapter 1     | Intro           | oduction                                                     |      |

| •             | 1.1             | About the Integrator/IM-PD1                                  | 1-2  |

|               | 1.2             | Interface module features and architecture                   |      |

|               | 1.3             | Links                                                        |      |

|               | 1.4             | Care of modules                                              |      |

| Chapter 2     | Getting Started |                                                              |      |

| -             | 2.1             | Setting up the logic module                                  | 2-2  |

|               | 2.2             | Fitting the interface module                                 |      |

|               | 2.3             | Connecting Multi-ICE or other JTAG equipment                 |      |

| Chapter 3 Har |                 | Iware Reference                                              |      |

| -             | 3.1             | Differences in signal naming between supported logic modules | 3-2  |

|               | 3.2             | Smart card interface                                         |      |

|               | 3.3             | IrDA interface                                               | 3-6  |

|               | 3.4             | UART interface                                               | 3-7  |

|               | 3.5             | USB interface                                                |      |

|               | 3.6             | Audio CODEC                                                  |      |

|               |                 |                                                              |      |

|            | 3.7    | MMC and SD flash card interface | 3-14 |

|------------|--------|---------------------------------|------|

|            | 3.8    | Display interface               | 3-17 |

|            | 3.9    | Touchscreen controller          | 3-21 |

|            | 3.10   | Backlight control               | 3-23 |

|            | 3.11   | Push buttons                    | 3-24 |

|            | 3.12   | Buzzer                          | 3-25 |

| Chapter 4  | Refere | nce Design Example              |      |

|            |        | About the design example        | 4-2  |

|            |        | Design example                  |      |

| Appendix A | Signal | Descriptions                    |      |

| ••         | A.1    | EXPA                            | A-2  |

|            |        | EXPB                            |      |

|            |        | EXPIM                           |      |

|            |        | Logic analyzer connector        |      |

| Appendix B | Mecha  | nical Specification             |      |

| • •        |        | Mechanical information          | B-2  |

# Preface

This preface introduces the Integrator/IM-PD1 interface module and its user documentation. It contains the following sections:

- About this book on page viii

- *Feedback* on page xii.

## About this book

This book provides user information for the ARM<sup>®</sup> Integrator/IM-PD1 interface module. It describes the major and how to use the interface module with an Integrator development platform.

#### Intended audience

This book is written for all developers who are using the Integrator/IM-PD1 interface module with an Integrator/LM-XCV600E+ or LM-EP20K600E+ logic module to develop ARM-based devices. It assumes that you are an experienced developer, and that you are familiar with the ARM development tools.

#### Using this book

This book is organized into the following chapters:

#### **Chapter 1** Introduction

Read this chapter for an introduction to the Integrator/IM-PD1 interface module. This chapter describes the main features of the interface module and identifies the main components.

#### **Chapter 2** Getting Started

Read this chapter for information about preparing the interface module for use with a logic module.

#### Chapter 3 Hardware Reference

Read this chapter for a description of the interface module hardware.

#### Chapter 4 Reference Design Example

Read this chapter for a description of the example logic module configuration supplied that allows you to experiment with the interface module.

#### **Appendix A** Signal Descriptions

Read this appendix for connector pinout information.

#### **Appendix B** Mechanical Specification

Refer to this appendix for mechanical details of the Integrator/IM-PD1.

## **Typographical conventions**

| italic            | Highlights important notes, introduces special terminology, denotes internal cross-references, and citations.                                             |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| bold              | Highlights interface elements, such as menu names. Denotes<br>ARM processor signal names. Also used for terms in descriptive<br>lists, where appropriate. |

| monospace         | Denotes text that can be entered at the keyboard, such as commands, file and program names, and source code.                                              |

| <u>mono</u> space | Denotes a permitted abbreviation for a command or option. The<br>underlined text can be entered instead of the full command or<br>option name.            |

| monospace italic  | Denotes arguments to commands and functions where the argument is to be replaced by a specific value.                                                     |

| monospace bold    | Denotes language keywords when used outside example code.                                                                                                 |

The following typographical conventions are used in this book:

### **Further reading**

This section lists publications from both ARM Limited and third parties that provide additional information on developing code for the ARM family of processors.

ARM periodically provides updates and corrections to its documentation. See http://www.arm.com for current errata sheets and addenda.

See also the ARM Frequently Asked Questions list on the ARM website.

## **ARM** publications

.

The following documents provide information about related Integrator products:

- ARM Integrator/AP User Guide (ARM DUI 0098)

- ARM Integrator/ CM920T-ETM User Guide (ARM DUI 0149)

- ARM Integrator/CM9x0T and CM7x0T User Guide (ARM DUI 0157)

- ARM Integrator/CM7TDMI User Guide (ARM DUI 0126)

- Integrator/CM946E-S Integrator/CM966E-S User Guide (ARM DUI 0138).

- ARM Integrator/LM-XCV600E+ LM-EP20K600E+ User Guide (ARM DUI 0146)

The following publication provide information about ARM PrimeCell devices that can be used to control the interfaces described in this manual:

- ARM PrimeCell UART (PL011) Technical Reference Manual (ARM DDI 0183)

- ARM PrimeCell Synchronous Serial Port Master and Slave (PL022) Technical Reference Manual (ARM DDI 0171)

- ARM PrimeCell Advanced Audio CODEC Interface (PL041) Technical Reference Manual (ARM DDI 0173).

- ARM PrimeCell GPIO (PL061) Technical Reference Manual (ARM DDI 0187)

- ARM PrimeCell Color LCD Controller (PL110) Technical Reference Manual (ARM DDI 0161).

- ARM PrimeCell Smartcard Interface (PL130) Technical Reference Manual (ARM DDI 0148)

- ARM PrimeCell Vectored Interrupt Controller (PL190) Technical Reference Manual (ARM DDI 0181)

- ARM PrimeCell Multimedia Card Interface (PL181) Technical Reference Manual (ARM DDI 0205).

The following publications provide reference information about ARM architecture:

- AMBA Specification (ARM IHI 0011)

- ARM Architectural Reference Manual (ARM DDI 0100).

The following publications provide information about the ARM Developer Suite:

- *Getting Started* (ARM DUI 0064)

- ADS Tools Guide (ARM DUI 0067)

- ADS Debuggers Guide (ARM DUI 0066)

- ADS Debug Target Guide (ARM DUI 0058)

- ADS Developer Guide (ARM DUI 0056)

- ADS CodeWarrior IDE Guide (ARM DUI 0065).

The following publication provides information about Multi-ICE:

• *Multi-ICE User Guide* (ARM DUI 0048).

## Other publications

This section lists relevant documents published by third parties:

• *LM4549 AC '97 Rev 2.1 Codec with Sample Rate Conversion and National 3D Sound Data sheet* (DS101035) available at:

http://www.national.com/pf/LM/LM4549.html

• *IRMS6400 and IRMT6400 4 Mb/s Infrared Data Transceiver Data sheet* (IRMS6400/IRMT6400) available at:

http://www.infineon.com/cmc\_upload/0/000/019/200/IRMS\_T6400.pdf

• *PDIUSBP11A Universal Serial Bus Transceiver Data sheet* (853-2008 21712) available at:

http://www-us6.semiconductors.com/acrobat/data sheets/PDIUSBP11A\_2.pdf

• DAC-Controlled Boost/Inverter LCD Bias Supply with Internal Switch Data sheet (19-1327) available at:

http://pdfserv.maxim-ic.com/arpdf/MAX686.pdf

# Feedback

ARM Limited welcomes feedback on both the Integrator/IM-PD1 and its documentation.

### Feedback on this document

If you have any comments on this book, please send email to errata@arm.com giving:

- the document title

- the document number

- the page number(s) to which your comments apply

- a concise explanation of your comments.

General suggestions for additions and improvements are also welcome.

#### Feedback on the Integrator/IM-PD1

If you have any comments or suggestions about this product, please contact your supplier giving:

- the product name

- an explanation of your comments.

# Chapter 1 Introduction

This chapter introduces the Integrator/IM-PD1. It contains the following sections:

- About the Integrator/IM-PD1 on page 1-2

- Interface module features and architecture on page 1-4

- Links on page 1-7

- *Care of modules* on page 1-8.

# 1.1 About the Integrator/IM-PD1

The Integrator/IM-PD1 is an interface module that is designed to be used in conjunction with the Integrator/LM-XCV600E+ or LM-EP20K600E+ and future compatible logic modules. It provides standard interfaces to enable you to make external connections to PrimeCell<sup>™</sup> or your own peripherals implemented in the logic module FPGA.

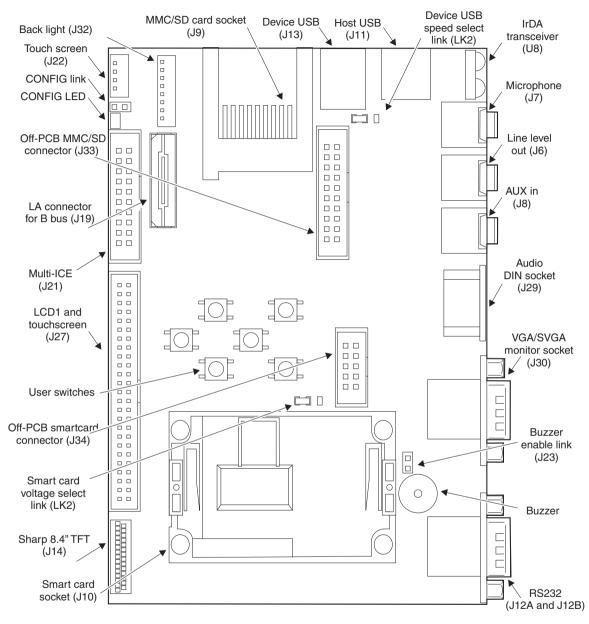

Figure 1-1 on page 1-3 shows the layout of the Integrator/IM-PD1.

Circuit diagrams of the Integrator/IM-PD1 and third party data sheets are available as pdf files after installation from the CDROM.

Figure 1-1 Integrator/IM-PD1 layout

# 1.2 Interface module features and architecture

This section describes the main features of the interface module and its architecture.

## 1.2.1 Features

The main features of the interface module are as follows:

- display support:

- interface to 8.4 inch Sharp color full VGA LCD

- generic interface to LCD with touch screen

- video DAC to support the connection of a VGA or SVGA PC monitor.

- USB type A (host) and type B (device) interfaces

- audio CODEC

- combined *MultiMedia Card* (MMC) and SD card interface

- smartcard socket

- two serial RS232 transceivers

- IrDA transceiver

- Multi-ICE connector

- logic analyzer connector connected to the B bus

- six push buttons

- buzzer.

## 1.2.2 Architecture

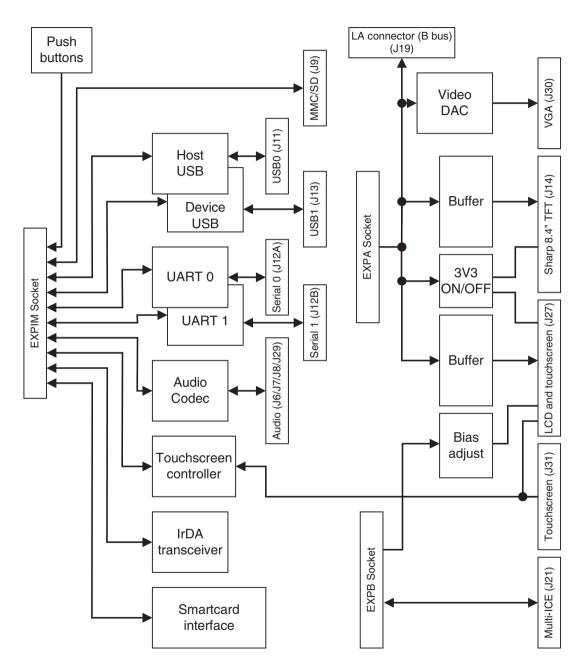

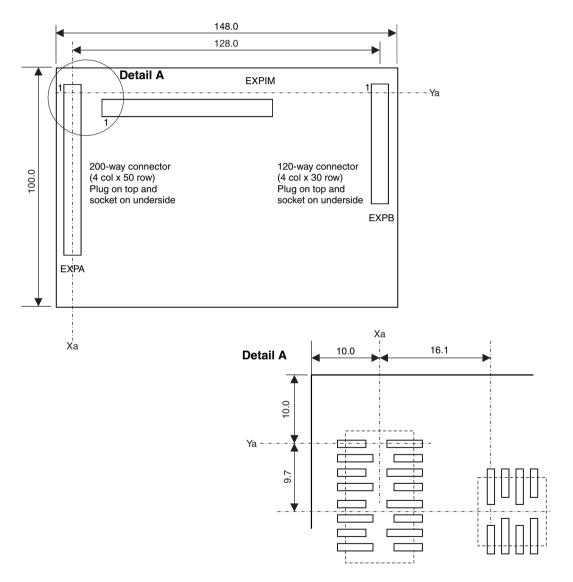

Figure 1-2 on page 1-6 shows the architecture of the interface module. The routing of the various interface signals from the logic module is as follows:

- The peripheral input/output devices are connected to the FPGA on the logic module using the EXPIM socket that connects to EXPIM plug on the logic module.

- The display interfaces are connected to the FPGA on the logic module using the B bus pins on the EXPA socket and one F bus pin on the EXPB socket. The logic module FPGA supplies the pixel data and control signals for the display interface buffers. The B bus can be monitored with a logic analyzer connected to J19.

#### \_\_\_\_\_ Note \_\_\_\_\_

٠

If the logic module is mounted in the EXPA/EXPB position on an Integrator/AP, the pins marked F bus connect to the GPIO bus on the Integrator/AP. This bus is routed between the system controller FPGA on the motherboard and the FPGA on the logic module. These signals are available for your own applications.

If the logic module is mounted in the HDRA/HDRB position on the motherboard, these pins connect to the F bus that is routed between any modules in the stack. there are no signals from the motherboard present on these pins.

The Multi-ICE connector enables you to gain access to the JTAG signals on the modules in the stack on which the interface module is mounted.

### Figure 1-2 Integrator/IM-PD1 block diagram

# 1.3 Links

The interface module provides four links:

- CONFIG link J22

- Buzzer enable link J23

- USB device port speed select link LK1

- Smartcard voltage select link LK2.

### 1.3.1 CONFIG link J22

The CONFIG link is a jumper type link that is used to enable and disable config mode.

Fitting the CONFIG link places the modules in the stack, onto which the interface module is mounted, into CONFIG mode (there are no components on the interface module that use Multi-ICE). This mode enables you to reprogram the FPGA image in the configuration flash on the logic module(s) in the stack using Multi-ICE (see the user guide for the logic module).

The CONFIG LED lights to indicate that the stack is in CONFIG mode.

### 1.3.2 Buzzer enable link J23

The buzzer enable link is a jumper type link used to connect and disconnect the buzzer (see *Buzzer* on page 3-25).

### 1.3.3 USB device port speed select link LK1

The USB speed select link is a soldered link that is used to set the operating speed of the USB device port (see *USB interface* on page 3-10).

### 1.3.4 Smartcard voltage select link LK2

The smartcard voltage select link is a soldered link that is used to set the operating voltage of the smartcard interface (see *Smart card interface* on page 3-3).

# 1.4 Care of modules

This section contains advice about how to prevent damage to your Integrator modules.

—— Caution ———

To prevent damage to your Integrator system, observe the following precautions:

- When removing a core or logic module from a motherboard, or when separating modules, take care not to damage the connectors. Do not apply a twisting force to the ends of the connectors. Loosen each connector first before pulling on both ends of the module at the same time.

- Use the system in a clean environment and avoid debris fouling the connectors on the underside of the PCB. Blocked holes can cause damage to connectors on the motherboard or module below. Visually inspect the module to ensure that connector holes are clear before mounting it onto another board.

- Observe *ElectroStatic Discharge* (ESD) precautions when handling any Integrator board.

# Chapter 2 Getting Started

This chapter describes how to set up and start using the logic module. It contains the following sections:

- *Setting up the logic module* on page 2-2

- *Fitting the interface module* on page 2-3

- Connecting Multi-ICE or other JTAG equipment on page 2-5.

# 2.1 Setting up the logic module

Before the interface module can be used it is necessary to load the required peripheral controllers into the logic module FPGA to drive the interfaces. The interface module is supplied with an example configuration that provides PrimeCell peripherals for supported logic modules.

The logic module user guide describes how to download new FPGA configurations.

When the interface module is fitted to the logic module, there is no access to the manufacturer-specific FPGA programming tool connector. This means that the logic module FPGA must be configured from flash or directly using the Multi-ICE connector if the logic module supports direct Multi-ICE configuration.

# 2.2 Fitting the interface module

The interface module is designed to be mounted on top of a logic module and provides connectivity for peripherals in the logic module FPGA. The interface module can be installed at the top of a stack of up to four logic modules. However, it only provides interface connections for the logic module immediately beneath it.

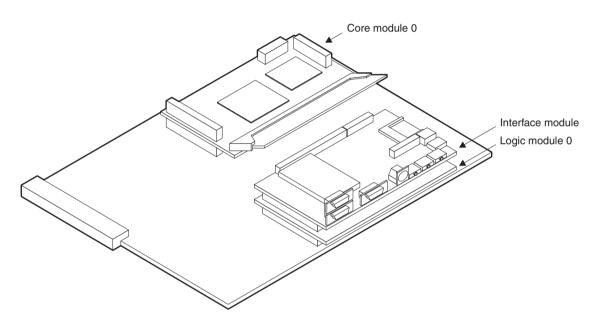

Figure 2-1 shows an example system comprising a core module and logic module attached to an Integrator/AP (see the *Integrator/AP User Guide* for more details) with interface module installed on top of the logic module.

Figure 2-1 Assembled Integrator/AP development system

## 2.2.1 Using the Integrator/IM-PD1 without an Integrator/AP motherboard

This option uses a core module at the bottom of a stack of one or more other modules. One logic module must be included that provides the system control function (for example, a system bus arbiter) normally provided by the motherboard.

—— Note ———

Module stacking without a motherboard is supported by later core module types that have a link similar to LK3 on the logic module. At the time of publication supporting core modules are:

- Integrator/CM9x6E-S (rev C and later)

- Integrator/CM9x0T-ETM (rev C and later)

- Integrator/CM10200 (rev C and later).

For up to date information about core module support for this stacking option, refer to the ARM web site.

To use this option:

- on the core module at the bottom of the stack, set the link to the appropriate position (see the user guide for your core module).

- on any logic modules, set LK3 to the C-D position.

- on one logic module, program and enable the CLK2 clock generator (see ARM Integrator/LM-XCV600E+ LM-EP20K600E+ User Guide).

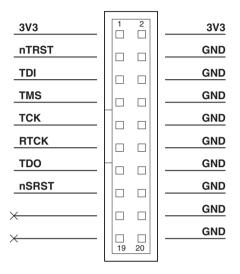

#### 2.3 **Connecting Multi-ICE or other JTAG equipment**

- Note

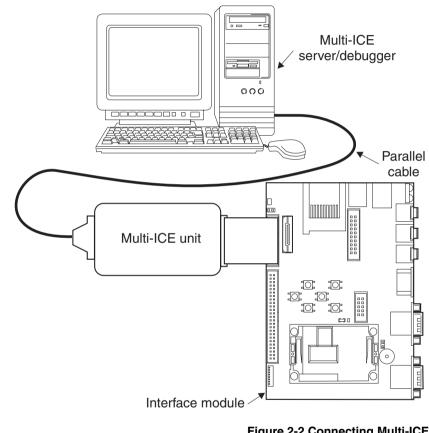

JTAG equipment, such as Multi-ICE, is connected to the 20-way box header, as shown in Figure 2-2. Connect the JTAG equipment to the interface module at the top of the logic module stack. Refer to the logic module user guide for a description of the JTAG system.

Figure 2-2 Connecting Multi-ICE

There are no components on the interface module that use the JTAG signals. The connector provides you with access to the JTAG signals on the modules below.

Getting Started

# Chapter 3 Hardware Reference

This chapter describes the hardware on the interface module. The descriptions assume that PrimeCell peripherals are being used to control these interfaces. This chapter contains the following sections:

- Differences in signal naming between supported logic modules on page 3-2

- Smart card interface on page 3-3

- *IrDA interface* on page 3-6

- UART interface on page 3-7

- USB interface on page 3-10

- Audio CODEC on page 3-12

- MMC and SD flash card interface on page 3-14

- Display interface on page 3-17

- Touchscreen controller on page 3-21

- Backlight control on page 3-23

- Push buttons on page 3-24

- *Buzzer* on page 3-25.

# 3.1 Differences in signal naming between supported logic modules

The Integrator/LM-XCV600E+ and Integrator/LM-EP20K600E+ logic module types route the signals between the FPGA and the interface module differently as follows:

- the LM-XCV600E+ is fitted with a Xilinx FPGA and routes the interface module **ABANK[12:0]** signals to bank 0 on the FPGA and the **BBANK[57:0]** signals to bank 1 on the FPGA.

- the LM-EP20K600E+ is fitted with an Altera FPGA and routes the interface module **ABANK[12:0]** signals to bank 5 on the FPGA and the **BBANK[57:0]** signals to bank 6 on the FPGA.

The logic module output voltage on these banks is adjustable. Ensure that the logic module selection link is set to the 3V3 position.

\_\_\_\_\_Note \_\_\_\_\_

These pin assignments are contained in the example pin constraints file on the CD that accompanies the interface module.

## 3.2 Smart card interface

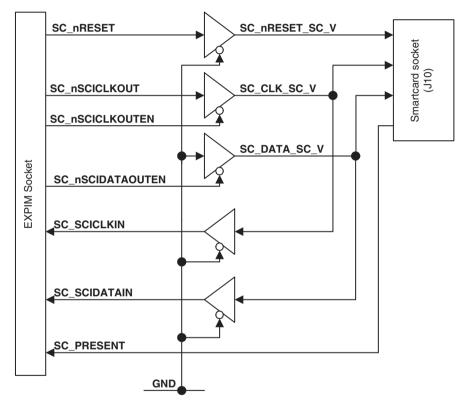

Figure 3-1 shows the architecture of the *Smart Card Interface* (SCI). This provides a suitable interface for the PrimeCell SCI (PL130) or similar peripheral. The diagram shows the tristate buffers that are used to provide the interface between the SCI and the card itself. An additional 10-way box header, J34, is provided to enable you to monitor the signals or to connect an off-board smartcard connector.

#### Figure 3-1 Smart card interface

You can set the SCI to operate at 3.3V or at 5V by setting the solder link LK2. The default setting is 5V.

| Signal name      | EXPIM connector | Description                     |

|------------------|-----------------|---------------------------------|

| SC_SCICLKIN      | IM_BBANK34      | Clock input to controller       |

| SC_SCIDATAIN     | IM_BBANK35      | Serial data input to controller |

| SC_nSCIDATAOUTEN | IM_BBANK36      | Data output enable              |

| SC_nSCICLKOUTEN  | IM_BBANK37      | Clock buffer output control     |

| SC_SCICLKOUT     | IM_BBANK38      | Clock output from controller    |

| SC_nRESET        | IM_BBANK39      | Reset to card                   |

| SC_PRESENT       | IM_BBANK40      | Card detect signal              |

The signals associated with the SCI are assigned to the EXPIM socket pins as shown in Table 3-1.

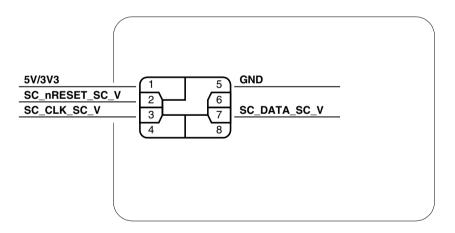

Figure 3-2 shows the signal assignment of a smartcard. Pins 4 and 8 are not connected and are omitted on some cards.

### Figure 3-2 Smartcard contacts assignment

Table 3-1 Smartcard signal assignment

The smart card is inserted into the smartcard socket with the contacts face down.

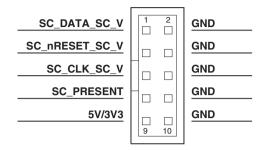

Figure 3-3 on page 3-5 shows the pinout of the connector J34. This can be used to connect to an off-PCB smart card device.

Figure 3-3 J34 pinout

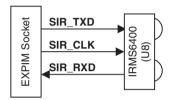

# 3.3 IrDA interface

Figure 3-4 shows the infrared interface suitable for use with a PrimeCell UART (PL011) or similar peripheral.

The example IRMS6400 is an IrDA compatible transceiver produced by the Infineon Technologies Corp.

Figure 3-4 IrDA interface

The signals associated with the infrared interface are assigned on the EXPIM socket pins as shown in Table 3-1 on page 3-4.

| Signal name | EXPIM connector | Description   |

|-------------|-----------------|---------------|

| SIR_SCLK    | IM_BBANK55      | Serial clock  |

| SIR_TXD     | IM_BBANK56      | Transmit data |

| SIR_RXD     | IM_BBANK57      | Receive data  |

# 3.4 UART interface

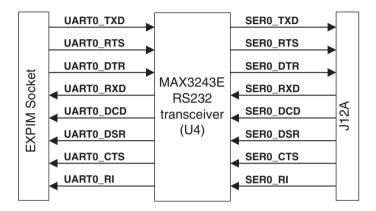

The interface module provides two serial transceivers suitable for use with the PrimeCell UART (PL011) or other similar peripherals. Figure 3-5 shows the architecture of one UART interface channel.

#### Figure 3-5 Serial interface (one channel)

The signals associated with the UART interface are assigned to the EXPIM socket pins as shown in Table 3-3.

| Signal name | EXPIM connector | Description         |

|-------------|-----------------|---------------------|

| UART0_TXD   | IM_BBANK47      | Transmit data       |

| UART0_RTS   | IM_BBANK48      | Ready to send       |

| UART0_DTR   | IM_BBANK49      | Data terminal ready |

| UART0_CTS   | IM_BBANK50      | Clear to send       |

| UART0_DSR   | IM_BBANK51      | Data set ready      |

| UART0_DCD   | IM_BBANK52      | Data carrier detect |

| UART0_RXD   | IM_BBANK53      | Receive data        |

| UART0_RI    | IM_BBANK54      | Ring indicator      |

| UART1_TXD   | IM_ABANK0       | Transmit data       |

| Signal name | EXPIM connector | Description         |

|-------------|-----------------|---------------------|

| UART1_RTS   | IM_ABANK1       | Ready to send       |

| UART1_DTR   | IM_ABANK2       | Data terminal ready |

| UART1_CTS   | IM_ABANK3       | Clear to send       |

| UART1_DSR   | IM_ABANK4       | Data set ready      |

| UART1_DCD   | IM_ABANK5       | Data carrier detect |

| UART1_RXD   | IM_ABANK6       | Receive data        |

| UART1_RI    | IM_ABANK7       | Ring indicator      |

Table 3-3 Serial interface signal assignment (continued)

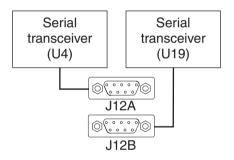

Figure 3-6 shows the assignment of the two serial interfaces to the 9-pin D-type male connector at J12.

#### Figure 3-6 Serial interface connector assignment

Figure 3-7 on page 3-9 shows the pin numbering for a 9-pin D-type male connector and Table 3-4 on page 3-9 shows the signal assignment for the two connectors.

The pinout shown in Figure 3-7 on page 3-9 is configured as a *Data Terminal Equipment* (DTE) device.

Figure 3-7 Serial connector pinout

## Table 3-4 Serial plug signal assignment

| Pin | J12A     | J12B     |

|-----|----------|----------|

| 1   | SER0_DCD | SER1_DCD |

| 2   | SER0_RX  | SER1_RX  |

| 3   | SER0_TX  | SER1_TX  |

| 4   | SER0_DTR | SER1_DTR |

| 5   | SER0_GND | SER1_GND |

| 6   | SER0_DSR | SER1_DSR |

| 7   | SER0_RTS | SER1_RTS |

| 8   | SER0_CTS | SER1_CTS |

| 9   | SER0_RI  | SER1_RI  |

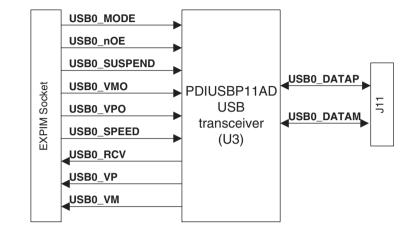

## 3.5 USB interface

Figure 3-8 shows one of the two USB interfaces.

#### Figure 3-8 USB interface (one channel)

USB0 provides a USB host interface and connects through the type A connector J11. USB1 provides a USB device interface and connects through the type B connector J13.

The signals associated with the USB interfaces are assigned to the EXPIM socket pins as shown in Table 3-5.

|              | ····· · · · · · · · · · · · · · · · · |                        |

|--------------|---------------------------------------|------------------------|

| Signal name  | EXPIM connector                       | Description            |

| USB0_VM      | IM_BBANK16                            | Gated version of D-    |

| USB0_VP      | IM_BBANK17                            | Gated version of D+    |

| USB0_RCV     | IM_BBANK18                            | Receive data           |

| USB0_SUSPEND | IM_BBANK19                            | Suspend for power save |

| USB0_nOE     | IM_BBANK20                            | Output enable          |

| USB0_VMO     | IM_BBANK21                            | Differential input –   |

| USB0_VPO     | IM_BBANK22                            | Differential input +   |

| USB0_MODE    | IM_BBANK23                            | Mode                   |

Table 3-5 Serial interface signal assignment

| Signal name  | EXPIM connector | Description            |

|--------------|-----------------|------------------------|

| USB0_SPEED   | IM_BBANK24      | Edge rate control      |

| USB1_VM      | IM_BBANK25      | Gated version of D-    |

| USB1_VP      | IM_BBANK26      | Gated version of D+    |

| USB1_RCV     | IM_BBANK27      | Receive data           |

| USB1_SUSPEND | IM_BBANK28      | Suspend for power save |

| USB1_nOE     | IM_BBANK29      | Output enable          |

| USB1_VMO     | IM_BBANK30      | Differential input –   |

| USB1_VPO     | IM_BBANK31      | Differential input +   |

| USB1_MODE    | IM_BBANK32      | Mode                   |

| USB1_SPEED   | IM_BBANK33      | Edge rate control      |

Table 3-5 Serial interface signal assignment (continued)

Configure the device USB interface to operate at slow or full speed by moving the soldered link LK1. The two settings are:

**Full speed** Fit link in position A-B (default).

**Slow speed** Fit link in position B-C.

— Note —

For a full description of the USB signals refer to the datasheet for the Philips PDIUSBP11AD transceiver.

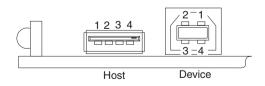

The two USB interfaces provide different types of USB connector manufactured by Berg. Figure 3-9 identifies the connectors for the host and device interfaces and shows how the pins are numbered.

Figure 3-9 Identifying the USB connectors

# 3.6 Audio CODEC

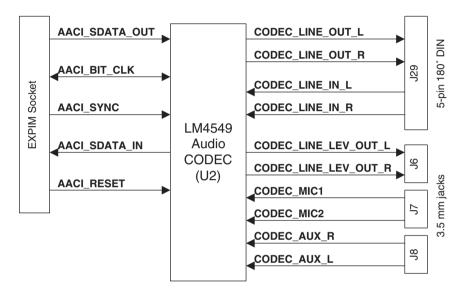

The interface module provides a National Semiconductors LM4549 audio CODEC. The audio CODEC is compatible with AC'97 Rev 2.1, is PC98 compliant, and features sample rate conversion and analog 3D sound. The CODEC can be driven with a PrimeCell AACI (PL041) or similar peripheral. Figure 3-10 shows the audio CODEC.

### Figure 3-10 Audio interface

The signals associated with the audio CODEC interface are assigned to the EXPIM socket pins as shown in Table 3-6.

| Signal name    | EXPIM connector | Description                                |

|----------------|-----------------|--------------------------------------------|

| AACI_SDATA_OUT | IM_ABANK8       | Serial data from AACI to the CODEC         |

| AACI_BIT_CLK   | IM_ABANK9       | Clock from the CODEC                       |

| AAC_SYNC       | IM_ABANK10      | Frame synchronization signal from the AACI |

| AACI_SDATA_IN  | IM_ABANK11      | Serial data from the CODEC to the AACI     |

| AACI_RESET     | IM_ABANK12      | Reset signal from the PrimeCell AACI       |

|                |                 |                                            |

#### Table 3-6 Audio CODEC signal assignment

— Note ———

For a description of the audio CODEC signals, refer to the LM4549 datasheet available from National Semiconductors.

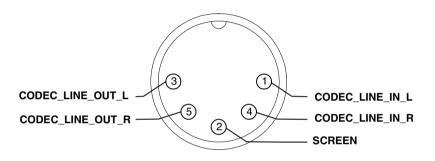

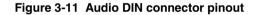

The interface module provides three jack plugs that allow you to connect to the microphone and auxiliary inputs, and line level output on the CODEC. Stereo inputs and outputs are also provided by a 5-pin 180° DIN socket. Figure 3-11 shows the pinout of the DIN socket.

A cable is supplied with the interface module to enable you to connect audio devices with phono sockets to the DIN socket. This cable is shown in Figure 3-11.

Figure 3-12 Supplied audio cable

For correct operation of the CODEC interface, you must mute the PC Beep input by setting bit 15 in the PC Beep register within the CODEC (see the LM4549 datasheet available from National Semiconductors).

- Note

# 3.7 MMC and SD flash card interface

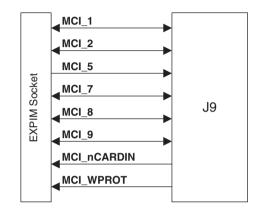

Figure 3-13 shows the MMC and SD flash card interface that can be driven as both an MMC or SD interface. A suitable MMC interface is the PrimeCell MMCI (PL181).

#### Figure 3-13 MMC/SD

The function of the interface signals depend on whether an MMC or SD card is fitted. Both card types default to MMC but the SD card has an additional operating mode called widebus mode. Table 3-7 shows the use of the signals for both modes of operation.

| Signal name | EXPIM connector | Widebus mode                                                                               | MMC mode                                                                                   |

|-------------|-----------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| nMCI_ON     | IM_BBANK7       | <ul> <li>Controls card power:</li> <li>LOW = power ON</li> <li>HIGH = power OFF</li> </ul> | <ul> <li>Controls card power:</li> <li>LOW = power ON</li> <li>HIGH = power OFF</li> </ul> |

| MCI_1       | IM_BBANK8       | Card detect/Data(3)                                                                        | Chip select (active LOW)                                                                   |

| MCI_2       | IM_BBANK9       | Command/Response                                                                           | Command/Response                                                                           |

| MCI_5       | IM_BBANK10      | CLK                                                                                        | CLK                                                                                        |

| MCI_7       | IM_BBANK11      | Data(0)                                                                                    | Data                                                                                       |

| MCI_8       | IM_BBANK12      | Data(1)                                                                                    | not used                                                                                   |

#### Table 3-7 MMC/SD interface signals

| Signal name | EXPIM connector | Widebus mode                      | MMC mode                          |

|-------------|-----------------|-----------------------------------|-----------------------------------|

| MCI_9       | IM_BBANK13      | Data(2)                           | not used                          |

| MCI_nCARDIN | IM_BBANK14      | Card presence detect (active LOW) | Card presence detect (active LOW) |

| MCI_WPROT   | IM_BBANK15      | Card write-protection detect      | Card write-protection detect      |

Table 3-7 MMC/SD interface signals (continued)

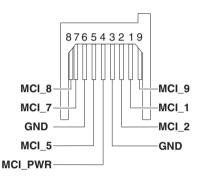

The MMC/SD card socket (J9) provides nine pins that connect to a card when it is inserted into the socket. Figure 3-14 shows the pin numbering and signal assignment. In addition the socket contains switches that operated are by card insertion and provide signaling on the MCI\_nCARDIN and MCI\_WPROT signals.

#### Figure 3-14 MMC/SD card socket pin numbering

The MMC card uses seven pins, and the SD card uses all nine pins. The additional pins are located as shown in Figure 3-14 with pin 9 next to pin 1 and pins 7 and 8 spaced more closely together than the other pins. Figure 3-15 shows an MMC card, with the contacts face up.

#### Figure 3-15 MMC card

Insert the card into the socket with the contacts face down. Cards are normally labelled on the top surface and provide an arrow to indicate the correct way to insert them.

Remove the card by gently pressing it into the socket. It springs back and can be removed. This ensures that the card detection switches within the socket operate correctly.

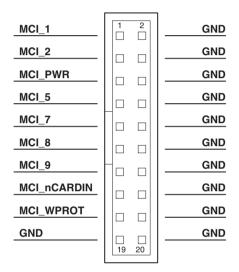

The connector J33 enables you to access the signals for debugging or to an off-PCB card socket. The pinout of J33 is shown in Figure 3-16.

Figure 3-16 J33 pinout

# 3.8 Display interface

The interface module provides a display interface with outputs for a:

- VGA or SVGA monitor connected to J30

- Sharp LQ084V1DG21 8.4 inch TFT VGA LCD panel connected to J14

- Generic LCD and touchscreen connector.

A suitable peripheral for driving these types of display is the PrimeCell CLCD controller (PL110).

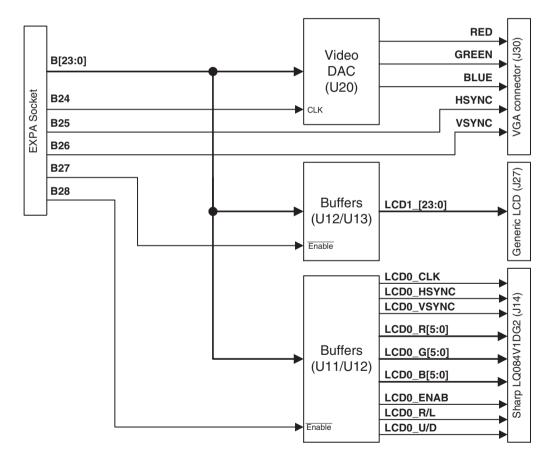

Figure 3-17 shows the architecture of the display interface. The diagram shows the signals used to provide pixel data and for buffer control. B27 is used to enable the signals on J27 and B28 is used to enable the buffers for the Sharp display signals on J14.

## Figure 3-17 Display interfaces

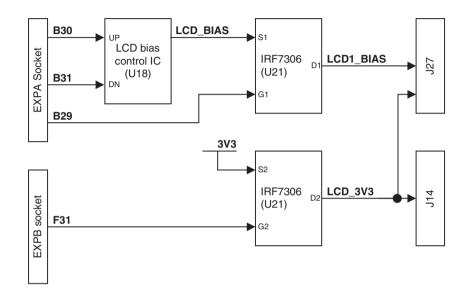

The interface module provides two power outputs for the display interfaces as shown in Figure 3-18. These are:

- LCD1\_BIAS

- LCD\_3V3.

Figure 3-18 LCD1 power supply control

**LCD1\_BIAS** is a variable supply controlled by the MAX686 DAC IC (U18) and switched ON and OFF by the MOSFET switch (U21). **LCD1\_BIAS** is varied between 11.5V and 24V in 64 steps using the inputs on pins B30 and B31 on the EXPA socket. These are edge-triggered inputs. The MAX686 is reset to the midpoint by a power-on reset. The MOSFET switch is controlled by the input from B29.

**LCD\_3V3** is fixed level power output that is controlled by a second MOSFET switch within U21. The switch is controlled by the input on the pin F31 on the EXPB connector.

The interface module provides two connectors. One (J14) is a dedicated connector for a 8.4 inch Sharp LCD display and the second (J27) provides a generic interface. Figure 3-19 on page 3-20 shows the pinout of connector J27.

—— Note ———

If the logic module is mounted in the EXPA/EXPB position on an Integrator/AP, the pins marked F bus connect to the GPIO bus on the Integrator/AP. This bus is routed between the system controller FPGA on the motherboard and the FPGA on the logic module. These signals are available for your own applications.

If the logic module is mounted in the HDRA/HDRB position on the motherboard, these pins connect to the F bus that is routed between any modules in the stack. there are no signals from the motherboard present on these pins.

The release note provided with the shipped example provides information on how the signals shown in Figure 3-19 on page 3-20 are connected to the PrimeCell.

If you intend to use anything other than the shipped example then signal allocation is a user decision.

| LCD1_0    |       | GND        |

|-----------|-------|------------|

| LCD1_1    |       | LCD1_2     |

| GND       |       | LCD1_3     |

| LCD1_4    |       | GND        |

| LCD1_5    |       | LCD1_6     |

| GND       |       | LCD1_7     |

| LCD1_8    |       | GND        |

| LCD1_9    |       | LCD1_10    |

| GND       |       | LCD1_11    |

| LCD1_12   |       | GND        |

| LCD1_13   |       | LCD1_14    |

| GND       |       | LCD1_15    |

| LCD1_16   |       | GND        |

| LCD1_17   |       | LCD1_18    |

| GND       |       | LCD1_19    |

| LCD1_20   |       | GND        |

| LCD1_21   |       | LCD1_22    |

| GND       |       | LCD1_23    |

| TS_XP     |       | GND        |

| TS_YP     |       | TS_XN      |

| GND       |       | TS_YN      |

| LCD1_BIAS |       | GND        |

| LCD1_3V3  |       | <u>3V3</u> |

| GND       |       | <u>5V</u>  |

| 12V       |       | BL_ADJ     |

| l         | 49 50 | J          |

## Figure 3-19 J27 pinout

\_\_\_\_\_Note \_\_\_\_\_

The LCD1[23:0] signals are 3V3 buffered versions of B[23:0], see the schematic diagram for more details.

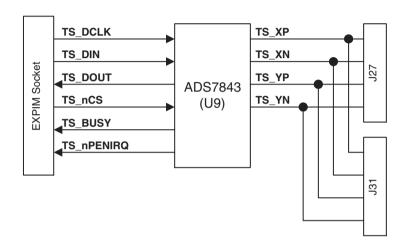

# 3.9 Touchscreen controller

The touchscreen interface is designed to connect to a 4-wire resistive touchscreen. It can be driven by the PrimeCell SSP (PL021), PrimeCell SSP (PL022), or similar peripheral.

Figure 3-20 shows the touch-screen interface. The signals to the touchscreen are routed to the 50-pin connector J27 and also to J31.

The touch-screen interface uses an Analog Devices ADS7843 (U9) controller to provide an interface with a 4-wire resistive touch screen. It communicates with the host using a serial interface. The host interface signals are shown in Table 3-8.

| Signal name | EXPIM connector | Description                     |

|-------------|-----------------|---------------------------------|

| TS_DIN      | IM_BBANK41      | Serial data input to controller |

| TS_nCS      | IM_BBANK42      | Controller chip select          |

| TS_DCLK     | IM_BBANK43      | Clock input to controller       |

| TS_DOUT     | IM_BBANK44      | Data output from controller     |

| TS_BUSY     | IM_BBANK45      | Busy indicator from controller  |

| TS_nPENIRQ  | IM_BBANK46      | Interrupt from controller       |

Figure 3-21 shows the pinout of the connector J31.

Figure 3-21 J31 pinout

# 3.10 Backlight control

The interface module provides an adjustable LCD backlight voltage controlled by the  $2k\Omega$  potentiometer R153. This enables you to adjust the **BL\_ADJ** output between 0V and 2.5V. This is available from the connector J32.

Figure 3-22 shows the pinout of J32.

Figure 3-22 Backlight connector pinout

# 3.11 Push buttons

The interface module is fitted with six push buttons. These can be monitored using a PrimeCell GPIO (PL061) or other suitable peripheral. Each switch is a normally open type and is connected to the EXPIM connector through inverters so that pressing the button drives the associated input to the GPIO HIGH.

Table 3-9 shows the assignment of the push button inputs to the EXPIM connector.

| EXPIM connector | Description                                                   |

|-----------------|---------------------------------------------------------------|

| IM_BBANK1       | Input from S1                                                 |

| IM_BBANK2       | Input from S2                                                 |

| IM_BBANK3       | Input from S3                                                 |

| IM_BBANK4       | Input from S4                                                 |

| IM_BBANK5       | Input from S5                                                 |

| IM_BBANK6       | Input from S6                                                 |

|                 | IM_BBANK1<br>IM_BBANK2<br>IM_BBANK3<br>IM_BBANK4<br>IM_BBANK5 |

#### Table 3-9 Push button interface signal assignment

# 3.12 Buzzer

The buzzer on the interface module can be driven with a PrimeCell GPIO (PL061) or other suitable peripheral. The buzzer is connected to the drain of a MOSFET device within U17 and the gate is controlled by an output from the GPIO. Enable the buzzer inserting fitting the jumper J23. Disable the buzzer by removing jumper J23.

The signal assignment is shown in Table 3-10.

| Signal name | EXPIM connector | Description                   |

|-------------|-----------------|-------------------------------|

| nBUZZER     | IM_BBANK0       | Controls power to the buzzer: |

|             |                 | • LOW = power ON              |

|             |                 | • HIGH = power OFF.           |

Table 3-10 Buzzer interface signal assignment

Hardware Reference

# Chapter 4 Reference Design Example

This chapter describes how to set up and start using the logic module. It contains the following sections:

- *About the design example* on page 4-2

- *Design example* on page 4-3.

# 4.1 About the design example

This chapter describes the reference design example supplied with the interface module. The interface module is not fitted with any programmable devices because it is intended to provide interfaces for peripherals instantiated into a logic module FPGA.

A VHDL example is supplied for the Integrator/LM-XCV2000E and LM-EP20K1000E logic modules with PrimeCell peripherals instantiated into the FPGA design. This example is designed to operate with the logic module mounted on a suitable motherboard, for example the Integrator/AP. If you are using your own peripheral designs, the example will help you become familiar with using the interface module.

# 4.1.1 About PrimeCells

The interface module is supplied with executable software that demonstrates the functionality of the PrimeCells included in the design example.

The ARM PrimeCells are a range of synthesizable peripherals that are ideally suited for use in ARM-based designs. The interface module is supplied with an FPGA image containing PrimeCell peripherals for each supported interface on the board and the accompanying CD contains documentation for them.

HDL and device source code for the PrimeCell peripherals are not supplied with the interface module. You must license the PrimeCell peripherals to obtain the source code.

# 4.2 Design example

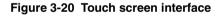

The interface module design example is supplied in VHDL. The example is an AHB design with an APB subsystem. The PrimeCell peripherals are instantiated in the top-level VHDL file.

# 4.2.1 Example architecture

The architecture of the example is shown in Figure 4-1. The interface module is provided with an example and release notes that define the clock sources, interrupt assignments, memory map, and peripherals.

Figure 4-1 Design example

\_\_\_\_ Note \_\_\_\_\_

The example FPGA image shipped with the board does not contain all of the peripherals shown in Figure 4-1 on page 4-3.

# Universal serial bus

Connectors and circuitry are provided for the two USB boxes shown in Figure 4-1 on page 4-3. However, there are no USB PrimeCells currently available from ARM Limited. These blocks can be licensed from other IP providers.

# Vectored interrupt controller

The PrimeCell PL190 *Vectored Interrupt Controller* (VIC) provides a software interface to the interrupt system. In an ARM system, two levels of interrupt are available:

- Fast Interrupt Request (FIQ) for fast, low latency interrupt handling

- *Interrupt ReQuest* (IRQ) for more general interrupts.

Only a single FIQ source at a time is generally used in a system, to provide a true low-latency interrupt. This has the following benefits:

- You can execute the interrupt service routine directly without determining the source of the interrupt.

- Interrupt latency is reduced. You can use the banked registers available for FIQ interrupts more efficiently, because a context save is not required.

There are 32 interrupt lines. The VIC uses a bit position for each different interrupt source. The software can control each request line to generate software interrupts.

# 4.2.2 Supplied VHDL files

Table 4-1 provides a summary description of the supplied VHDL (.vhd) files. A more detailed description of each block is included within the files in the form of comments.

## Table 4-1 VHDL file descriptions

| File                    | Description                                                                                                                                                                                                                                                                                                                                                  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| AHBTop.vhd              | This file is the top-level VHDL that instantiates all of the PrimeCells for the example. The VHDL for the PrimeCells themselves are not supplied but are available from ARM as separate products.                                                                                                                                                            |  |

| AHBDecoder.vhd          | The decoder block provides the high-speed peripherals with select lines. These are generated from the address lines and the module ID (position in stack) signals from the motherboard. The Integrat family of boards uses a distributed address decoding system (see <i>Address assignment of logic modules</i> on page 4-7).                               |  |

| AHBDefaultSlave.<br>vhd | This block provides a default slave response when the logic module address space is addressed but the address does not correspond to any of the instantiated peripherals.                                                                                                                                                                                    |  |

| AHBMux8S1M.vhd          | This is the AHB multiplexor that connects the read data buses and the <b>HRESP</b> and <b>HREADY</b> signals from all of the slaves to the AHB master.                                                                                                                                                                                                       |  |

| AHBZBTRAM.vhd           | High-speed peripherals require SSRAM controller block to support word, halfword, and byte operations to the SSRAM on the logic module.                                                                                                                                                                                                                       |  |

| AHB2APB.vhd             | This is the bridge block required to connect APB peripherals to the AMBA AHB bus. It produces the peripheral select signals for each of the APB peripherals.                                                                                                                                                                                                 |  |

| APBRegs.vhd             | <ul> <li>The APB register peripheral provides memory-mapped registers that you can use to:</li> <li>configure the two clock generators</li> <li>write to the user LEDs on the logic module</li> <li>read the user switch inputs on the logic module.</li> <li>It also latches the pressing of the push button to generate an expansion interrupt.</li> </ul> |  |

| BuildOptions.vhd        | This file defines generation of the PrimeCells in the example and allows control over the synthesis so<br>that PrimeCells can be included or excluded. It also specifies the base address of all the peripherals                                                                                                                                             |  |

The VHDL files provided are only for information and will not build without additional components that can be licensed separately.

\_\_\_\_\_ Note \_\_\_\_\_

# 4.2.3 Loading the FPGA image

Multi-ICE configuration files, the progcards utility, and the FPGA images for the supported logic modules are available after installation from the CDROM. Refer to the Logic Module User Guide for programming information.

# 4.2.4 Example memory map

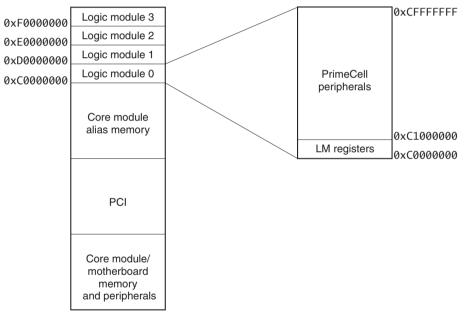

The supplied examples set up the memory map for the logic module as shown in Figure 4-2. This shows the locations to which logic modules are assigned by the main address decoder on the motherboard. The diagram also shows how the example decodes the address space for the logic module when it is LMO (bottom of the stack). Refer to the release notes shipped with the example for more information.

#### Figure 4-2 Integrator system memory map

The Integrator system implements a distributed address decoding scheme in which each core or logic module is responsible for decoding its own address space. It is important when implementing a logic module design, to ensure that the module responds to all memory accesses in the appropriate memory region (see the user guide for your motherboard).

– Note –

# 4.2.5 Address assignment of logic modules

You can mount up to four logic modules on an Integrator/AP motherboard. The base address of each logic module depends on its position in the stack. This defines the value of bits [31:28] of the address of devices on the logic module as shown in Table 4-2.

#### Table 4-2 Logic module addresses

| Position   | Bits 31:28 |  |

|------------|------------|--|

| 0 (bottom) | 0xC        |  |

| 1          | 0xD        |  |

| 2          | 0xE        |  |

| 3 (top)    | 0xF        |  |

## 4.2.6 Example memory map

The addresses in Table 4-3 assume that there is one logic module present in position 0 (bottom) of the expansion stack on the Integrator/AP. If the logic module is present at any other position, then the top four bits of the address decoding will change.

| Peripheral        | Clock source | VIC<br>Interrupt | Base<br>address | Reference                                                                                       |

|-------------------|--------------|------------------|-----------------|-------------------------------------------------------------------------------------------------|

| Control registers | n/a          | 0                | 0xC0000000      | <i>Example APB register peripheral</i> on page 4-8                                              |

| UART 0            | 1/4 CLK2     | 1                | 0xC0100000      | ARM PrimeCell UART (PL011) Technical<br>Reference Manual                                        |

| UART 1            | 1/4 CLK2     | 2                | 0xC0200000      | ARM PrimeCell UART (PL011) Technical<br>Reference Manual                                        |

| SSP               | 1/64 CLK2    | 3                | 0xC0300000      | ARM PrimeCell Synchronous Serial Port<br>Master and Slave (PL022) Technical<br>Reference Manual |

| GPIO 0            | n/a          | 4                | 0xC0400000      | ARM PrimeCell GPIO (PL061) Technical<br>Reference Manual                                        |

#### Table 4-3 Address map

#### Table 4-3 Address map

| Peripheral | Clock source | VIC<br>Interrupt | Base<br>address | Reference                                                                             |

|------------|--------------|------------------|-----------------|---------------------------------------------------------------------------------------|

| GPIO 1     | n/a          | 5                | 0xC0500000      | ARM PrimeCell GPIO (PL061) Technical<br>Reference Manual                              |

| SCI        | 1/4 CLK2     | 6                | 0xC0600000      | ARM PrimeCell Smartcard Interface<br>(PL130) Technical Reference Manual               |

| MMCI       | n/a          | 7 and 8          | 0xC0700000      | ARM PrimeCell Multimedia Card Interface<br>(PL181) Technical Reference Manual         |

| AACI       | AACIBITCLK   | 9                | 0xC0800000      | ARM PrimeCell Advanced Audio CODEC<br>Interface (PL041) Technical Reference<br>Manual |

| CLCD       | CLK1         | 11               | 0xC1000000      | ARM PrimeCell Color LCD Controller<br>(PL110) Technical Reference Manual              |

| SSRAM      | n/a          | n/a              | 0xC2000000      | SSRAM on page 4-12                                                                    |

| VIC        | n/a          | n/a              | 0xC3000000      | ARM PrimeCell Vectored Interrupt<br>Controller (PL190) Technical Reference<br>Manual  |

| PIB        | n/a          | n/a              | 0xCFFFFF00      | Peripheral Information Block, PIB on page 4-12                                        |

# 4.2.7 Example APB register peripheral

Table 4-4 shows the mapping of the logic module control registers. The addresses shown are offsets from the base addresses shown in Figure 4-2 on page 4-6.

# Table 4-4 Logic module registers

| Offset address | Name    | Туре       | Function                      |

|----------------|---------|------------|-------------------------------|

| 0×0000000      | LM_OSC1 | Read/write | Oscillator 1 divisor register |

| 0x0000004      | LM_OSC2 | Read/write | Oscillator 2 divisor register |

| 0x0000008      | LM_LOCK | Read/write | Oscillator lock register      |

| 0x000000C      | LM_LEDS | Read/write | User LEDs control register    |

| Offset address | Name       | Туре       | Function                       |

|----------------|------------|------------|--------------------------------|

| 0x0000010      | LM_INT     | Read/write | Push button interrupt register |

| 0x0000014      | LM_SW      | Read       | Switches register              |

| 0x0000018      | LM_CONTROL | Read/write | Control register               |

#### Table 4-4 Logic module registers

## **Oscillator divisor registers**

The oscillator registers control the frequency of the clocks generated by the two clock generators on the logic module.

Before writing to the oscillator registers, you must unlock them by writing the value 0x0000A05F to the LM\_LOCK register. After writing the oscillator register, relock them by writing any value other than 0x0000A05F to the LM\_LOCK register.

Table 4-5 describes the oscillator register bits.

#### Table 4-5 LM\_OSCx registers

| Bits  | Name | Access     | Function                                                                                    |

|-------|------|------------|---------------------------------------------------------------------------------------------|

| 18:16 | OD   | Read/write | Output divider:                                                                             |

|       |      |            | • 000 = divide by 10                                                                        |

|       |      |            | • 001 = divide by 2                                                                         |

|       |      |            | • 010 = divide by 8                                                                         |

|       |      |            | • 011 = divide by 4                                                                         |

|       |      |            | • 100 = divide by 5                                                                         |

|       |      |            | • $101 = \text{divide by } 7$                                                               |

|       |      |            | • $110 = \text{divide by } 9$                                                               |

|       |      |            | • $111 = $ divide by 6.                                                                     |

| 15:9  | RDW  | Read/write | Reference divider word. Defines the binary value of the R[6:0] pins of the clock generator. |

| 8:0   | VDW  | Read/write | VCO divider word. Defines the binary value of the V[8:0] pins of the clock generator.       |

|       |      |            | — Note                                                                                      |

The default values set **CLK1** to 25MHz and **CLK2** to 48MHz.

The reference divider (R[6:0]) and VCO divider (V[8:0]) are used to calculate the output frequency as follows:

Frequency = 48MHz  $\cdot \frac{(V[8:0] + 8)}{(R[6:0] + 2) \cdot OD}$

You must also observe the operating range limits:

$10MHz < 48MHz \cdot \frac{(V[8:0] + 8)}{(R[6:0] + 2)}$

R[6:0]<118

\_\_\_\_\_ Note \_\_\_\_\_

You can calculate values for the clock control signals using the ICS525 calculator on the Integrated Circuit Systems website at:

http://www.icst.com/products/ics525inputForm.html.

# Oscillator lock register

The lock register is used to control access to the oscillator registers, allowing them to be locked and unlocked. This mechanism prevents the oscillator registers from being overwritten accidently. Table 4-6 describes the lock register bits.

#### Table 4-6 LM\_LOCK register

| Bits | Name    | Access     | Function                                                                                                                                                                      |

|------|---------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16   | LOCKED  | Read       | <ul> <li>This bit indicates if the oscillator registers are locked or unlocked:</li> <li>0 = unlocked</li> <li>1 = locked.</li> </ul>                                         |

| 15:0 | LOCKVAL | Read/write | Write the value 0x0000A05F to this register to enable write accesses to the oscillator registers.<br>Write any other value to this register to lock the oscillator registers. |

## User LEDs control register

The LEDs register is used to control the user LEDs on the logic module. Writing a 0 to a bit lights the associated LED.

# Push button interrupt register

The push button interrupt register contains 1 bit. It is a latched indication that the push button on the logic module has been pressed. The output from this register is used to drive an input to the interrupt controller. Table 4-7 describes the operation of this register.

#### Table 4-7 LM\_INT register

| Bits | Name   | Access | Function                                                                                                                                 |

|------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | LM_INT | Read   | This bit when SET is a latched indication that the push button has been pressed.                                                         |

|      |        | Write  | Write 0 to this register to CLEAR the latched indication.<br>Writing 1 to this register has the same effect as pressing the push button. |

## Switches register

This register is used to read the setting of the 8-way DIP switch on the logic module. A 0 indicates that the associated switch element is CLOSED (ON).

## **Control register**

This register controls the multiplexors that are used to select the display type.

Table 4-8 describes the operation of this register.

#### Bits Name Access Function 7:3 RESERVED \_ \_ 2 DISPLAY ENABLE Read/write This bit enables and disables the selected display: 0 = DISABLED• 1 = ENABLED (default). • 1:0DISPLAY SELECT Read/write These bits control the display outputs: 00 =Sharp 8.4 inch display (default) • 01= VGA/SVGA monitor 16bpp • 10 = LCD1 connector • 11 = VGA/SVGA monitor 24bpp. •

## Table 4-8 LM\_CONTROL register

## 4.2.8 SSRAM

The example design instantiates a 1MB block of SRAM at 0xC2000000. This memory is physically located on the logic module.

## 4.2.9 Peripheral Information Block, PIB

The FPGA image contains a ROM block that provides information on the peripherals present. PrimeCell number, base address and PrimeCell revision number is given. The information stored in the PIB will become more advanced in future releases.

The ROM block is situated at the top of the memory map allocated to the logic module. There are up to 32 words of information stored. For example, a logic module at the bottom of the stack will have the PIB present at 0xCFFFFF00 to 0xCFFFFFF.

Format:

0x00000000 - no entry, ignore. Check next address.

else

0xaabbbbcc

where:

| aa   | bits 31:28 depend on the position in the stack                                                                                                                                                              |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | bits 27:20 of the PrimeCell base address                                                                                                                                                                    |

|      | bits 19:0 are zero                                                                                                                                                                                          |

| bbbb | PrimeCell number, for example 0041 = AACI (PL041)                                                                                                                                                           |

|      | If a peripheral is not a PrimeCell, then a value 0xFF <i>bb</i> will be assigned, where <i>bb</i> is just a unique look-up value. The value 0xFFFF is used as a special case to indicate FPGA build number. |

| cc   | PrimeCell revision, for example $11 = v1.1$                                                                                                                                                                 |

For example, 0x48004111 would be an AACI rev 1.1 with base address 0xC4800000, assuming the logic module is in bottom position.

The last word in the ROM is used to hold the FPGA build number in the format  $0 \times FFFFFab$ , where the build revision is *a*.*b*

A utility read\_pib.axf is provided that reads the PIB and lists the peripherals present. This also displays the FPGA build number.

# Appendix A Signal Descriptions

This appendix describes the Integrator/IM-PD1 interface connectors and signal connections. It contains the following sections:

- EXPA on page A-2

- EXPB on page A-4

- EXPIM on page A-7

- *Logic analyzer connector* on page A-9.

# A.1 EXPA

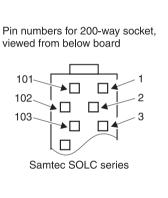

Figure A-1 shows the how the pins on the EXPA socket on the on underside of the interface module are numbered.

|                |     |      |     |          | 1                 |

|----------------|-----|------|-----|----------|-------------------|

| 1              | A0  | GND  | GND | D0       | 101               |

| 2<br>3<br>4    | A1  |      | D1  |          | 102<br>103        |

| 4<br>5         | A3  | A2   | GND | D2       | 104<br>105        |

| 6<br>7         |     | GND  | D4  | D3       | 106<br>107        |

| 8              |     | A5   |     | D5       | 108               |

| 9              | A6  | GND  | GND |          | 109               |

| 10<br>11       | A7  |      | D7  |          | 110<br>111        |

| 12<br>13       | A9  | A8   | GND | D8       | 112<br>113        |

| 14<br>15       | A10 | GND  | D10 | D9       | 114<br>115        |

| 16             |     | A11  |     | D11      | 116               |

| 17<br>18       | A12 | GND  | GND | D12      | 117<br>118        |

| 19<br>20       | A13 |      | D13 |          | 119<br>120        |

| 21             | A15 |      | GND |          | 121               |

| 22<br>23       | A16 | GND  | D16 | D15      | 122<br>123        |

| 24<br>25       |     | A17  |     | D17      | 124<br>125        |

| 26             | A18 | GND  | GND | D18      | 126               |

| 27<br>28       | A19 | A20  | D19 | D20      | 127<br>128        |

| 29             | A21 |      | GND |          | 129               |

| 30<br>31       | A22 | GND  | D22 | D21      | 130<br>131        |

| 32<br>33       | A24 | A23  | GND | D23      | 132<br>133        |

| 34             |     | GND  |     | D24      | 134               |

| 35<br>36       | A25 | A26  | D25 | D26      | 135<br>136        |

| 37<br>38       | A27 | GND  | GND | D27      | 137<br>138        |

| 39             | A28 |      | D28 |          | 139               |

| 40<br>41       | A30 | A29  | GND | D29      | 140<br>141        |

| 42<br>43       | A31 | GND  | D31 | D30      | 142<br>143        |

| 44             |     | B0   |     | CO       | 144               |

| 45<br>46       | B1  | GND  | GND | C1       | 145<br>146        |

| 47<br>48       | B2  | B3   | C2  | C3       | 147<br>148        |

| 49             | B4  |      | GND |          | 149               |

| 50<br>51       | B5  | GND  | C5  | C4       | 150<br>151        |

| 52<br>53       | B7  | B6   | GND | C6       | 152<br>153        |

| 54<br>55       |     | GND  | C8  | C7       | 154<br>155        |

| 56             |     | B9   |     | C9       | 156               |

| 57<br>58       | B10 | GND  | GND | C10      | 157<br>158        |

| 59<br>60       | B11 | B12  | C11 | C12      | 159<br>160        |

| 61             | B13 |      | GND |          | 161               |

| 62<br>63       | B14 | GND  | C14 | C13      | 162<br>163        |

| 64<br>65       | B16 | B15  | GND | C15      | 164<br>165        |

| 66             |     | GND  |     | C16      | 166               |

| 67<br>68       | B17 | B18  | C17 | C18      | 167<br>168        |

| 69             | B19 | GND  | GND |          | 169               |

| 70<br>71<br>72 | B20 | 0.10 | C20 |          | 170<br>171        |

| 73             | B22 | B21  | GND | C21      | 172<br>173        |

| 74<br>75       | B23 | GND  | C23 | C22      | 174<br>175        |

| 76             |     | B24  |     | C24      | 176               |

| 77<br>78       |     | GND  | GND | C25      | 177<br>178<br>179 |

| 79             | B26 | B27  | C26 | C27      | 179<br>180        |

| 80<br>81       | B28 |      | GND |          | 181<br>182        |

| 82<br>83       | B29 |      | C29 | C28      | 183               |

| 84<br>85       | B31 | B30  |     | C30      | 184<br>185        |

| 86             |     | GND  |     | C31      | 186               |

| 87<br>88       | 5V  | 3V3  | 3V3 | 12V      | 187<br>188        |

| 89<br>90       | 5V  | 3V3  | 3V3 | 12V      | 189<br>190        |

| 91             | 5V  |      | 3V3 |          | 191               |

| 92<br>93<br>94 | 5V  | 3V3  | 3V3 | 12V      | 192<br>193        |

| 94<br>95       |     | 3V3  | 3V3 | 12V      | 194<br>195        |

| 96             |     | 3V3  |     | 12V      | 196               |

| 97<br>98       | 5V  | 3V3  | 3V3 | 12V      | 197<br>198        |

| 99<br>100      | 5V  | 3V3  | 3V3 | 12V      | 199<br>200        |

|                |     |      |     | <u> </u> |                   |

|                |     |      |     |          |                   |

Figure A-1 EXPA socket pin numbering

The signals present on the EXPA connector are described in Table A-1.

# Table A-1 AHB signal assignment

| Pin label | Signal   | Description                                                                                                                                         |

|-----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| A[31:0]   | Not used | -                                                                                                                                                   |

| B[31:0]   | B[31:0]  | These signals connect to the FPGA on the logic module. They are used to carry display interface signals (see <i>Display interface</i> on page 3-17) |

| C[31:0]   | Not used | -                                                                                                                                                   |

| D[31:0]   | Not used | -                                                                                                                                                   |

# A.2 EXPB

Figure A-2 shows the pin numbers of the EXPB socket on the underside of the interface module.

| 1        | HO   |     | GND  |                     | 61         |

|----------|------|-----|------|---------------------|------------|

| 2        |      | GND | GIND | F0                  | 62         |

| 3        | H1   |     | F1   |                     | 63         |

| 4        |      | H2  |      | F2                  | 64         |

| 5        | H3   |     | GND  |                     | 65         |

| 6        |      | GND |      | F3                  | 66         |

| 7<br>8   | H4   |     | F4   |                     | 67         |

| 9        | H6   | H5  | GND  | F5                  | 68<br>69   |

| 10       |      | GND | GND  | F6                  | 70         |

| 11       | H7   |     | F7   |                     | 71         |

| 12       |      | H8  |      | F8                  | 72         |

| 13       | H9   |     | GND  |                     | 73         |

| 14       |      | GND |      | F9                  | 74         |

| 15       | H10  |     | F10  | <b></b>             | 75         |

| 16<br>17 | H12  | H11 | GND  | F11                 | 76<br>77   |

| 18       |      | GND | GND  | F12                 | 78         |

| 19       | H13  |     | F13  |                     | 79         |

| 20       |      | H14 |      | F14                 | 80         |

| 21       | H15  |     | GND  |                     | 81         |

| 22       |      | GND |      | F15                 | 82         |

| 23       | H16  |     | F16  | <b>E</b> 4 <b>7</b> | 83         |

| 24<br>25 | H18  | H17 | GND  | F17                 | 84<br>85   |

| 26       |      | GND | GND  | F18                 | 86         |

| 27       | H19  |     | F19  |                     | 87         |

| 28       |      | H20 |      | F20                 | 88         |

| 29       | H21  |     | GND  |                     | 89         |

| 30       |      | GND |      | F21                 | 90         |

| 31       | H22  |     | F22  |                     | 91         |

| 32<br>33 | H24  | H23 | GND  | F23                 | 92<br>93   |

| 34       | 1127 | GND | GIND | F24                 | 94         |

| 35       | H25  |     | F25  |                     | 95         |

| 36       |      | H26 |      | F26                 | 96         |

| 37       | H27  |     | GND  |                     | 97         |

| 38       |      | GND |      | F27                 | 98         |

| 39<br>40 | H28  | H29 | F28  | <b>E</b> 20         | 99<br>100  |

| 40       | H30  | H29 | GND  | F29                 | 100        |

| 42       |      | GND |      | F30                 | 102        |

| 43       | H31  |     | F31  |                     | 103        |

| 44       |      | JO  |      | J8                  | 104        |

| 45       | J1   |     | GND  |                     | 105        |

| 46       |      | GND |      | J9                  | 106        |

| 47<br>48 | J2   | J3  | J10  | J11                 | 107<br>108 |

| 40<br>49 | J4   |     | GND  | JII                 | 108        |

| 50       |      | GND |      | J12                 | 110        |

| 51       | J5   |     | J13  |                     | 111        |

| 52       |      | J6  |      | J14                 | 112        |

| 53       | J7   |     | J16  |                     | 113        |

| 54       |      | GND |      | J15                 | 114        |

| 55<br>56 | 5V   | 3V3 | -12V | 12V                 | 115<br>116 |

| 50<br>57 | 5V   | 013 | -12V | 121                 | 117        |

| 58       |      | 3V3 | Y    | 12V                 | 118        |

| 59       | 5V   |     | -12V |                     | 119        |

| 60       |      | 3V3 |      | 12V                 | 120        |