# ARM<sup>®</sup> Compiler toolchain

Version 5.02

**Using the Linker**

Copyright © 2010-2012 ARM. All rights reserved. ARM DUI 0474H (ID070912)

### ARM Compiler toolchain Using the Linker

#### Copyright © 2010-2012 ARM. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

| Date              | Issue | Confidentiality  | Change                                                     |

|-------------------|-------|------------------|------------------------------------------------------------|

| 28 May 2010       | А     | Non-Confidential | ARM Compiler toolchain v4.1 Release                        |

| 30 September 2010 | В     | Non-Confidential | Update 1 for ARM Compiler toolchain v4.1                   |

| 28 January 2011   | С     | Non-Confidential | Update 2 for ARM Compiler toolchain v4.1 Patch 3           |

| 30 April 2011     | D     | Non-Confidential | ARM Compiler toolchain v5.0 Release                        |

| 29 July 2011      | Е     | Non-Confidential | Update 1 for ARM Compiler toolchain v5.0                   |

| 30 September 2011 | F     | Non-Confidential | ARM Compiler toolchain v5.01 Release                       |

| 29 February 2012  | G     | Non-Confidential | Document update 1 for ARM Compiler toolchain v5.01 Release |

| 27 July 2012      | Н     | Non-Confidential | ARM Compiler toolchain v5.02 Release                       |

#### **Proprietary Notice**

Words and logos marked with  ${}^{\otimes}$  or  ${}^{\bowtie}$  are registered trademarks or trademarks of ARM in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

Change History

## Contents ARM Compiler toolchain Using the Linker

| Chapter 1 | Conv | ventions and feedback                                               |      |

|-----------|------|---------------------------------------------------------------------|------|

| Chapter 2 | Over | rview of the linker                                                 |      |

| •         | 2.1  | About the linker                                                    | 2-2  |

|           | 2.2  | Linker command-line syntax                                          | 2-4  |

|           | 2.3  | Linker command-line options listed in groups                        |      |

|           | 2.4  | What the linker can accept as input                                 |      |

|           | 2.5  | What the linker outputs                                             |      |

|           | 2.6  | What the linker does when constructing an executable image          |      |

| Chapter 3 | Link | ing models supported by armlink                                     |      |

| •         | 3.1  | Overview of linking models                                          | 3-2  |

|           | 3.2  | Bare-metal linking model                                            |      |

|           | 3.3  | Partial linking model                                               |      |

|           | 3.4  | Base Platform Application Binary Interface (BPABI) linking model    | 3-5  |

|           | 3.5  | Base Platform linking model                                         |      |

|           | 3.6  | SysV linking model                                                  | 3-8  |

|           | 3.7  | Concepts common to both BPABI and SysV linking models               | 3-9  |

| Chapter 4 | Imaç | ge structure and generation                                         |      |

| •         | 4.1  | The image structure                                                 | 4-3  |

|           | 4.2  | Input sections, output sections, regions, and Program Segments      |      |

|           | 4.3  | Load view and execution view of an image                            |      |

|           | 4.4  | Methods of specifying an image memory map with the linker           |      |

|           | 4.5  | Types of simple image                                               |      |

|           | 4.6  | Type 1 image, one load region and contiguous execution regions      | 4-11 |

|           | 4.7  | Type 2 image, one load region and non-contiguous execution regions  |      |

|           | 4.8  | Type 3 image, two load regions and non-contiguous execution regions |      |

|           | 4.9  | Image entry points                                                  | 4-17 |

|            | 4.10  | About specifying an initial entry point                                        | 4-18 |

|------------|-------|--------------------------------------------------------------------------------|------|

|            | 4.11  | Section placement with the linker                                              |      |

|            | 4.12  | Placing sections with FIRST and LAST attributes                                |      |

|            | 4.13  | Section alignment with the linker                                              |      |

|            | 4.14  | Demand paging                                                                  |      |

|            | 4.15  | About ordering execution regions containing Thumb code                         |      |

|            | 4.16  | Overview of veneers                                                            |      |

|            | 4.17  | Veneer sharing                                                                 |      |

|            | 4.18  | Veneer types                                                                   |      |

|            | 4.19  | Generation of position independent to absolute veneers                         |      |

|            | 4.20  | Reuse of veneers when scatter-loading                                          |      |

|            | 4.21  | Using command-line options to control the generation of C++ exception tables . |      |

|            | 4.22  | About weak references and definitions                                          |      |

|            | 4.23  | How the linker performs library searching, selection, and scanning             | 4-35 |

|            | 4.24  | Controlling how the linker searches for the ARM standard libraries             |      |

|            | 4.25  | Specifying user libraries when linking                                         | 4-38 |

|            | 4.26  | How the linker resolves references                                             | 4-39 |

|            | 4.27  | Use of the strict family of options in the linker                              | 4-41 |

| Chapter 5  | llsin | g linker optimizations                                                         |      |

| Siluptor V | 5.1   | Elimination of common debug sections                                           | 5_2  |

|            | 5.2   | Elimination of common groups or sections                                       |      |

|            | 5.3   | Elimination of unused sections                                                 |      |

|            | 5.4   | Elimination of unused virtual functions                                        |      |

|            | 5.5   | About linker feedback                                                          |      |

|            | 5.6   | Example of using linker feedback                                               | -    |

|            | 5.7   | About link-time code generation                                                |      |

|            | 5.8   | Optimization with RW data compression                                          |      |

|            | 5.9   | How the linker chooses a compressor                                            |      |

|            | 5.10  | Overriding the compression algorithm used by the linker                        |      |

|            | 5.11  | How compression is applied                                                     |      |

|            | 5.12  | Working with RW data compression                                               | 5-17 |

|            | 5.13  | Inlining functions with the linker                                             | 5-18 |

|            | 5.14  | Factors that influence function inlining                                       | 5-19 |

|            | 5.15  | Handling branches that optimize to a NOP                                       | 5-21 |

|            | 5.16  | About reordering of tail calling sections                                      |      |

|            | 5.17  | Restrictions on reordering of tail calling sections                            |      |

|            | 5.18  | About merging comment sections                                                 | 5-24 |

| Chapter 6  | Getti | ng information about images                                                    |      |

|            | 6.1   | Linker options for getting information about images                            | 6-2  |

|            | 6.2   | Identifying the source of some link errors                                     |      |

|            | 6.3   | Example of using theinfo linker option                                         |      |

|            | 6.4   | How to find where a symbol is placed when linking                              |      |

| Chapter 7  | ٨٥٥٥  | ssing and managing symbols with armlink                                        |      |

| Chapter I  | 7.1   | ssing and managing symbols with armlink<br>About mapping symbols               | 73   |

|            | 7.1   | Accessing linker-defined symbols                                               |      |

|            | 7.3   | Region-related symbols                                                         |      |

|            | 7.4   | Image\$\$ execution region symbols                                             |      |

|            | 7.5   | Load\$\$ execution region symbols                                              |      |

|            | 7.6   | Load\$\$LR\$\$ load region symbols                                             |      |

|            | 7.7   | Region name values when not scatter-loading                                    |      |

|            | 7.8   | Using scatter files                                                            |      |

|            | 7.9   | Importing linker-defined symbols in C and C++                                  |      |

|            | 7.10  | Importing linker-defined symbols in ARM assembler                              |      |

|            | 7.11  | Section-related symbols                                                        |      |

|            | 7.12  | Image symbols                                                                  |      |

|            | 7.13  | Input section symbols                                                          |      |

|            | 7.14  | Accessing symbols in another image                                             | 7-18 |

|                       | 7.15 | Creating a symdefs file                                                               |             |

|-----------------------|------|---------------------------------------------------------------------------------------|-------------|

|                       | 7.16 | Outputting a subset of the global symbols                                             |             |

|                       | 7.17 | Reading a symdefs file                                                                |             |

|                       | 7.18 | Symdefs file format                                                                   |             |

|                       | 7.19 | What is a steering file?                                                              |             |

|                       | 7.20 | Specifying steering files on the linker command-line                                  |             |

|                       | 7.21 | Steering file command summary                                                         |             |

|                       | 7.22 | Steering file format                                                                  |             |

|                       | 7.23 | Hiding and renaming global symbols with a steering file                               |             |

|                       | 7.24 | Using \$Super\$\$ and \$Sub\$\$ to patch symbol definitions                           |             |

| <b>o</b> l <i>i</i> o |      |                                                                                       |             |

| Chapter 8             |      | g scatter files                                                                       | 0.0         |

|                       | 8.1  | About scatter-loading                                                                 |             |

|                       | 8.2  | When to use scatter-loading                                                           |             |

|                       | 8.3  | Scatter-loading command-line option                                                   |             |

|                       | 8.4  | Images with a simple memory map                                                       |             |

|                       | 8.5  | Images with a complex memory map                                                      |             |

|                       | 8.6  | Linker-defined symbols that are not defined when scatter-loading                      |             |

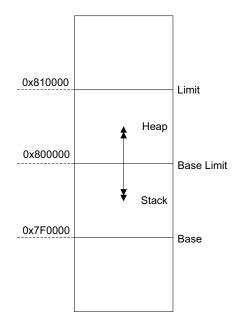

|                       | 8.7  | Specifying stack and heap using the scatter file                                      |             |

|                       | 8.8  | What is a root region?                                                                |             |

|                       | 8.9  | Creating root execution regions                                                       |             |

|                       | 8.10 | Using the FIXED attribute to create root regions                                      |             |

|                       | 8.11 | Placing functions and data at specific addresses                                      |             |

|                       | 8.12 | Placing a named section explicitly using scatter-loading                              |             |

|                       | 8.13 | Placing unassigned sections with the .ANY module selector                             |             |

|                       | 8.14 | Examples of using placement algorithms for .ANY sections                              | 8-28        |

|                       | 8.15 | Example of next_fit algorithm showing behavior of full regions, selectors, ar<br>8-30 | nd priority |

|                       | 8.16 | Examples of using sorting algorithms for .ANY sections                                | 8-32        |

|                       | 8.17 | Selecting veneer input sections in scatter-loading descriptions                       |             |

|                       | 8.18 | Usingattribute((section("name"))) to place code and data                              |             |

|                       | 8.19 | Usingat sections to place sections at a specific address                              |             |

|                       | 8.20 | Restrictions on placingat sections                                                    |             |

|                       | 8.20 | Automatic placement ofat sections                                                     |             |

|                       | 8.22 | Manual placement ofat sections                                                        |             |

|                       | 8.23 |                                                                                       |             |

|                       |      | Placing a key in flash memory usingat                                                 |             |

|                       | 8.24 | Placing a structure over a peripheral register usingat                                |             |

|                       | 8.25 | Placement of sections with overlays                                                   |             |

|                       | 8.26 | About placing ARM C and C++ library code                                              |             |

|                       | 8.27 | Example of placing code in a root region                                              |             |

|                       | 8.28 | Example of placing ARM C library code                                                 |             |

|                       | 8.29 | Example of placing ARM C++ library code                                               |             |

|                       | 8.30 | Example of placing ARM library helper functions                                       |             |

|                       | 8.31 | Reserving an empty region                                                             |             |

|                       | 8.32 | About creating regions on page boundaries                                             |             |

|                       | 8.33 | Overalignment of execution regions and input sections                                 |             |

|                       | 8.34 | Using preprocessing commands in a scatter file                                        |             |

|                       | 8.35 | Expression evaluation in scatter files                                                |             |

|                       | 8.36 | Using expression evaluation in a scatter file to avoid padding                        | 8-61        |

|                       | 8.37 | Equivalent scatter-loading descriptions for simple images                             | 8-62        |

|                       | 8.38 | Type 1 image, one load region and contiguous execution regions                        |             |

|                       | 8.39 | Type 2 image, one load region and non-contiguous execution regions                    | 8-65        |

|                       | 8.40 | Type 3 image, two load regions and non-contiguous execution regions                   |             |

|                       | 8.41 | Scatter file to ELF mapping                                                           |             |

| Chapter 9             | GNU  | Id script support in armlink                                                          |             |

| -                     | 9.1  | About GNU Id script support and restrictions                                          | 9-2         |

|                       | 9.2  | Typical use cases for using ld scripts with armlink                                   |             |

|                       | 9.3  | Important ld script commands that are implemented in armlink                          |             |

|                       | 9.4  | Specific restrictions for using ld scripts with armlink                               |             |

|            | 9.5   | Recommendations for using Id scripts with armlink                     | 9-7   |

|------------|-------|-----------------------------------------------------------------------|-------|

|            | 9.6   | Default GNU ld scripts used by armlink                                |       |

|            | 9.7   | Example GNU Id script for linking an ARM Linux executable             | 9-12  |

|            | 9.8   | Example GNU Id script for linking an ARM Linux shared object          | 9-14  |

|            | 9.9   | Example GNU Id script for linking IdIdpartial object                  | 9-16  |

| Chapter 10 | BPAE  | 3I and SysV shared libraries and executables                          |       |

| •          | 10.1  | About the Base Platform Application Binary Interface (BPABI)          | 10-3  |

|            | 10.2  | Platforms supported by the BPABI                                      |       |

|            | 10.3  | Concepts common to all BPABI models                                   |       |

|            | 10.4  | About importing and exporting symbols for BPABI models                |       |

|            | 10.5  | Symbol visibility for BPABI models                                    |       |

|            | 10.6  | Automatic import and export for BPABI models                          |       |

|            | 10.7  | Manual import and export for BPABI models                             |       |

|            | 10.8  | Symbol versioning for BPABI models                                    |       |

|            | 10.9  | RW compression for BPABI models                                       |       |

|            | 10.10 | Linker options for SysV models                                        |       |

|            | 10.11 | SysV memory model                                                     |       |

|            | 10.12 | Automatic dynamic symbol table rules in the SysV memory model         |       |

|            | 10.13 | Addressing modes in the SysV memory model                             |       |

|            | 10.14 | Thread local storage in the SysV memory model                         |       |

|            | 10.15 | Related linker command-line options for the SysV memory model         |       |

|            | 10.16 | Changes to command-line defaults with the SysV memory model           |       |

|            | 10.17 | Linker options for bare metal and DLL-like models                     |       |

|            | 10.18 | Bare metal and DLL-like memory model                                  |       |

|            | 10.19 | Mandatory symbol versioning in the BPABI DLL-like model               |       |

|            | 10.20 | Automatic dynamic symbol table rules in the BPABI DLL-like model      |       |

|            | 10.21 | Addressing modes in the BPABI DLL-like model                          |       |

|            | 10.22 | C++ initialization in the BPABI DLL-like model                        | 10-26 |

|            | 10.23 | About symbol versioning                                               | 10-27 |

|            | 10.24 | Symbol versioning script file                                         |       |

|            | 10.25 | Example of creating versioned symbols                                 |       |

|            | 10.26 | About embedded symbols                                                |       |

|            | 10.27 | Linker options for enabling implicit symbol versioning                |       |

|            | 10.28 | Related linker command-line options for the BPABI DLL-like model      |       |

| Chapter 11 | Featu | ires of the Base Platform linking model                               |       |

| •          | 11.1  | Restrictions on the use of scatter files with the Base Platform model | 11-2  |

|            | 11.2  | Example scatter file for the Base Platform linking model              |       |

|            | 11.3  | Placement of PLT sequences with the Base Platform model               |       |

| Appendix A | Revis | sions for Using the Linker                                            |       |

## Chapter 1 Conventions and feedback

The following describes the typographical conventions and how to give feedback:

#### **Typographical conventions**

The following typographical conventions are used:

- monospace Denotes text that can be entered at the keyboard, such as commands, file and program names, and source code.

- monospace Denotes a permitted abbreviation for a command or option. The underlined text can be entered instead of the full command or option name.

#### monospace italic

Denotes arguments to commands and functions where the argument is to be replaced by a specific value.

#### monospace bold

- Denotes language keywords when used outside example code.

- *italic* Highlights important notes, introduces special terminology, denotes internal cross-references, and citations.

- **bold** Highlights interface elements, such as menu names. Also used for emphasis in descriptive lists, where appropriate, and for ARM<sup>®</sup> processor signal names.

#### Feedback on this product

If you have any comments and suggestions about this product, contact your supplier and give:

your name and company

- the serial number of the product

- details of the release you are using

- details of the platform you are using, such as the hardware platform, operating system type and version

- a small standalone sample of code that reproduces the problem

- a clear explanation of what you expected to happen, and what actually happened

- the commands you used, including any command-line options

- sample output illustrating the problem

- the version string of the tools, including the version number and build numbers.

#### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- the title

- the number, ARM DUI 0474H

- if viewing online, the topic names to which your comments apply

- if viewing a PDF version of a document, the page numbers to which your comments apply

- a concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

ARM periodically provides updates and corrections to its documentation on the ARM Information Center, together with knowledge articles and *Frequently Asked Questions* (FAQs).

#### Other information

- ARM Information Center, http://infocenter.arm.com/help/index.jsp

- ARM Technical Support Knowledge Articles, http://infocenter.arm.com/help/topic/com.arm.doc.faqs/index.html

- ARM Support and Maintenance, http://www.arm.com/support/services/support-maintenance.php

- ARM Glossary, http://infocenter.arm.com/help/topic/com.arm.doc.aeg0014-/index.html.

## Chapter 2 Overview of the linker

The following topics give an overview of the ARM linker, armlink:

#### Concepts

- *About the linker* on page 2-2

- What the linker can accept as input on page 2-10

- What the linker outputs on page 2-11

- What the linker does when constructing an executable image on page 2-12.

#### Reference

- Linker command-line syntax on page 2-4

- Linker command-line options listed in groups on page 2-5.

## 2.1 About the linker

The linker, armlink, combines the contents of one or more object files with selected parts of one or more object libraries to produce:

- an ARM ELF image

- a partially linked ELF object that can be used as input in a subsequent link step

- ELF files that can be demand-paged efficiently

- a shared object, compatible with the *Base Platform Application Binary Interface* (BPABI) or *System V release 4* (SysV) specification, or a BPABI or SysV executable file.

The linker can:

- link ARM code and 16-bit Thumb<sup>®</sup> and 32-bit Thumb code

- generate interworking veneers to switch processor state when required

- generate inline veneers or long branch veneers, where required, to extend the range of branch instructions

- automatically select the appropriate standard C or C++ library variants to link with, based on the build attributes of the objects it is linking

- enable you to specify the locations of code and data within the system memory map, using either a command-line option or a scatter file

- perform Read/Write data compression to minimize ROM size

- perform unused section elimination to reduce the size of your output image

- control the generation of debug information in the output file

- generate a static callgraph and list the stack usage

- control the contents of the symbol table in output images

- show the sizes of code and data in the output

- use linker feedback to remove individual unused functions

- accept GNU ld scripts, with restrictions.

—— Note ———

A 64-bit version of armlink is provided that can utilize the greater amount of memory available to processes on 64-bit operating systems. It supports all the features that are supported by the 32-bit version of armlink in this release.

#### 2.1.1 See also

#### Tasks

Introducing the ARM Compiler toolchain:

*Changing to the 64-bit linker* on page 2-7.

- *Demand paging* on page 4-23

- About linker feedback on page 5-7

- Chapter 3 Linking models supported by armlink

- Chapter 4 Image structure and generation

- Chapter 5 Using linker optimizations

- Chapter 6 *Getting information about images*

- Chapter 7 Accessing and managing symbols with armlink

- Chapter 8 Using scatter files

- Chapter 9 GNU ld script support in armlink

- Chapter 10 BPABI and SysV shared libraries and executables

- Chapter 11 Features of the Base Platform linking model.

#### Other information

Base Platform ABI for the ARM Architecture, http://infocenter.arm.com/help/topic/com.arm.doc.ihi0037-/index.html

## 2.2 Linker command-line syntax

The command for invoking the linker is:

armlink [options] [input-file-list]

options Linker command-line options.

input-file-list

A space-separated list of objects, libraries, or symbol definitions (symdefs) files.

#### 2.2.1 See also

#### Reference

• Linker command-line options listed in groups on page 2-5.

- *input-file-list* on page 2-87

- Chapter 2 *Linker command-line options*.

## 2.3 Linker command-line options listed in groups

•

See the following command-line options in the Linker Reference:

#### Controlling library files and paths

- --add\_needed, --no\_add\_needed on page 2-6

- --add\_shared\_references, --no\_add\_shared\_references on page 2-7

- *--libpath=pathlist* on page 2-96

- *--library=name* on page 2-97

- *--library type=lib* on page 2-98

- --reduce paths, --no reduce paths on page 2-129

- --runpath=pathlist on page 2-138

- --scanlib, --no\_scanlib on page 2-141

- --search\_dynamic\_libraries, --no\_search\_dynamic\_libraries on page 2-144

- --thumb2 library, --no thumb2 library on page 2-172

- --userlibpath=pathlist on page 2-179.

#### Controlling the linking of object files

- --match=crossmangled on page 2-109

- *--strict* on page 2-156

- --strict\_ph, --no\_strict\_ph on page 2-159

- --strict\_relocations, --no\_strict\_relocations on page 2-160

- *--sysroot=path* on page 2-169

- *--unresolved=symbol* on page 2-176.

#### Controlling the output

- *--base\_platform* on page 2-18

- *--bpabi* on page 2-24

- --combreloc, --no\_combreloc on page 2-33

- *--dll* on page 2-49

- *--ldpartial* on page 2-94

- *--output=filename* on page 2-114

- *--partial* on page 2-119

- --prelink\_support, --no\_prelink\_support on page 2-125

- *--reloc* on page 2-132

- --shared on page 2-146

- *--sysv* on page 2-170.

#### Specifying the image memory map

- --autoat, --no autoat on page 2-17

- *--fpic* on page 2-74

- *--linker\_script=ld\_script* on page 2-100

- *--predefine="string"* on page 2-123

- *--ro\_base=address* on page 2-135

- *--ropi* on page 2-136

- *--rosplit* on page 2-137

- *--rw\_base=address* on page 2-139

- *--rwpi* on page 2-140

- *--scatter=filename* on page 2-142

- *--split* on page 2-154

- --use sysv default script, --no use sysv default script on page 2-178

- --*zi\_base=address* on page 2-193.

#### Controlling debug information in an image

- --bestdebug, --no\_bestdebug on page 2-21

- --compress\_debug, --no\_compress\_debug on page 2-35

- --debug, --no debug on page 2-41

- *--dynamic\_debug* on page 2-50

- --emit\_debug\_overlay\_relocs on page 2-54

- --emit\_debug\_overlay\_section on page 2-55

- --emit\_non\_debug\_relocs on page 2-56

#### Controlling the content of an image

- *--any\_contingency* on page 2-8

- --any\_placement=algorithm on page 2-9

- --any\_sort\_order=order on page 2-11

- *--api, --no\_api* on page 2-12

- *--arm\_linux* on page 2-13

- *--arm\_only* on page 2-15

- --as\_needed, --no\_as\_needed on page 2-16

- --blx\_arm\_thumb, --no\_blx\_arm\_thumb on page 2-22

- --blx thumb arm, --no blx thumb arm on page 2-23

- *--branchnop*, *--no branchnop* on page 2-25

- --comment\_section, --no\_comment\_section on page 2-34

- *--cppinit, --no\_cppinit* on page 2-36

- --*cpu=name* on page 2-38

- *--datacompressor=opt* on page 2-40

- *--device=list* on page 2-42

- *--device=name* on page 2-43

- *--dynamic linker=name* on page 2-51

- --edit=file\_list on page 2-53

- --emit relocs on page 2-57

- *--entry=location* on page 2-58

- --exceptions, --no exceptions on page 2-61

- --exceptions\_tables=action on page 2-62

- --execstack, --no\_execstack on page 2-63

- -export\_all, --no\_export\_all on page 2-64

- --export dynamic, --no export dynamic on page 2-65

- --filtercomment, --no filtercomment on page 2-69

- *--fini=symbol* on page 2-70

- *--first=section id* on page 2-71

- *--force explicit attr* on page 2-72

- --force so throw, --no force so throw on page 2-73

- *--fpu=name* on page 2-76

- --gnu\_linker\_defined\_syms on page 2-77

- --import\_unresolved, --no\_import\_unresolved on page 2-79

- *--init=symbol* on page 2-84

- --inline, --no inline on page 2-85

- -*keep=section id* on page 2-89

- --keep protected symbols on page 2-91

- --largeregions, --no\_largeregions on page 2-92

- *--last=section id* on page 2-93

- --*linux\_abitag=version\_id* on page 2-101

- --locals, --no\_locals on page 2-105

- *--ltcg* on page 2-106

- --max\_visibility=type on page 2-111

- *--merge*, *--no\_merge* on page 2-112

- --muldefweak, --no\_muldefweak on page 2-113

- *--override\_visibility* on page 2-115

- *--pad=num* on page 2-116

- *--paged* on page 2-117

- *--pagesize=pagesize* on page 2-118

- *--pltgot=type* on page 2-121

- *--pltgot opts=mode* on page 2-122

- *--privacy* on page 2-126

- --ref\_cpp\_init, --no\_ref\_cpp\_init on page 2-130

- *--remove, --no\_remove* on page 2-134

- *--soname=name* on page 2-151

- *--sort=algorithm* on page 2-152

- --startup=symbol, --no\_startup on page 2-155

- --strict\_flags, --no\_strict\_flags on page 2-158

- *--symbolic* on page 2-164

- --symver script=filename on page 2-167

- --symver\_soname on page 2-168

- --tailreorder, --no\_tailreorder on page 2-171

- *--tiebreaker=option* on page 2-173

- *--undefined=symbol* on page 2-174

- --undefined\_and\_export=symbol on page 2-175

- --use\_definition\_visibility on page 2-177

- *--vfemode=mode* on page 2-186.

#### **Controlling veneer generation**

- --crosser\_veneershare, --no\_crosser\_veneershare on page 2-39

- --inlineveneer, --no\_inlineveneer on page 2-86

- *--max\_veneer\_passes=value* on page 2-110

- *--piveneer, --no piveneer* on page 2-120

- --veneerinject,--no veneerinject on page 2-180

- --veneer inject type=type on page 2-181

- *--veneer pool size=size* on page 2-182

- --veneershare, --no veneershare on page 2-183.

#### Controlling byte addressing mode

- --*be8* on page 2-19

- *--be32* on page 2-20.

#### Controlling the extraction and presentation of image information

- --callgraph, --no\_callgraph on page 2-26

- --callgraph\_file=filename on page 2-28

- --*callgraph output=fmt* on page 2-29

- *--cgfile=type* on page 2-30

- *--cgsymbol=type* on page 2-31

- *--cgundefined=type* on page 2-32

- --*feedback=filename* on page 2-66

- --feedback image=option on page 2-67

- *--feedback type=type* on page 2-68

- --*info=topic[,topic,...]* on page 2-80

- --*info\_lib\_prefix=opt* on page 2-83

- --list mapping symbols, --no list mapping symbols on page 2-103

- --load addr map info, --no load addr map info on page 2-104

- --mangled, --unmangled on page 2-107

- *--map*, *--no\_map* on page 2-108

- *--section\_index\_display=type* on page 2-145

- --symbols, --no symbols on page 2-165

- *--symdefs=filename* on page 2-166

- *--xref, --no xref* on page 2-190

- --xrefdbg, --no xrefdbg on page 2-191

- --*xref{from*|*to*}=*object(section)* on page 2-192.

#### —— Note ———

With the exception of --callgraph, the linker prints the information you request on the standard output stream, stdout, by default. You can redirect the information to a text file using the --list command-line option.

#### Controlling diagnostic messages

- --*diag\_error=tag[,tag,...]* on page 2-44

- --*diag remark=tag[,tag,...]* on page 2-45

- --*diag\_style=arm*|*ide*|*gnu* on page 2-46

- --*diag\_suppress=tag[,tag,...]* on page 2-47

- --*diag\_warning=tag[,tag,...]* on page 2-48

- *--errors=filename* on page 2-60

- *--list=filename* on page 2-102

- --remarks on page 2-133

- --show full path on page 2-148

- --show parent lib on page 2-149

- *--show sec idx* on page 2-150

- --strict enum size, --no strict enum size on page 2-157

- --strict symbols, --no strict symbols on page 2-161

- --strict visibility, --no strict visibility on page 2-162

- --strict wchar size, --no strict wchar size on page 2-163

- --verbose on page 2-184.

#### Controlling alignment in legacy images

• --legacyalign, --no\_legacyalign on page 2-95.

#### Miscellaneous

- *--cpu=list* on page 2-37

- --eager\_load\_debug, --no\_eager\_load\_debug on page 2-52

- *--fpu=list* on page 2-75

- *--licretry* on page 2-99

- *--project=filename, --no\_project* on page 2-127

- *--reinitialize\_workdir* on page 2-131

- *--show\_cmdline* on page 2-147

- --version number on page 2-185

- --via=filename on page 2-187

- --*vsn* on page 2-188

- *--workdir=directory* on page 2-189.

## 2.4 What the linker can accept as input

Input to armlink consists of one or more object files in ARM ELF. This format is described in the *ELF for the ARM Architecture (ARM IHI 0044)*.

Optionally, the following files can be used as input to armlink:

- one or more libraries created by the librarian, armar

- a symbol definitions file

- a scatter file

- a steering file.

#### 2.4.1 See also

#### Tasks

• Chapter 8 Using scatter files.

Creating Static Software Libraries with armar:

• *Creating a new object library* on page 3-2.

#### Reference

Accessing symbols in another image on page 7-18.

Linker Reference:

- Chapter 3 Linker steering file command reference

- Chapter 4 Formal syntax of the scatter file.

#### **Other information**

• ELF for the ARM Architecture (ARM IHI 0044), http://infocenter.arm.com/help/topic/com.arm.doc.ihi0044-/index.html.

## 2.5 What the linker outputs

Output from armlink can be:

- an ELF executable image

- an ELF shared object

- a partially-linked ELF object

- a relocatable ELF object.

You can use fromelf to convert an ELF executable image to other file formats, or to display, process, and protect the content of an ELF executable image.

#### 2.5.1 See also

#### Concepts

•

- Partial linking model on page 3-4

- Section placement with the linker on page 4-19

- *The image structure* on page 4-3.

Using the fromelf Image Converter:

• Chapter 2 Overview of the fromelf image converter.

## 2.6 What the linker does when constructing an executable image

When you use the linker to construct an executable image, it:

- resolves symbolic references between the input object files

- extracts object modules from libraries to satisfy otherwise unsatisfied symbolic references

- sorts input sections according to their attributes and names, and merges sections with similar attributes and names into contiguous chunks

- removes unused sections

- eliminates duplicate common groups and common code, data, and debug sections

- organizes object fragments into memory regions according to the grouping and placement information provided

- assigns addresses to relocatable values

- generates an executable image.

#### 2.6.1 See also

#### Tasks

- *Elimination of common debug sections* on page 5-2

- *Elimination of unused sections* on page 5-4.

#### Concepts

*The image structure* on page 4-3.

## Chapter 3 Linking models supported by armlink

The following topics describe the linking models supported by the ARM linker, armlink:

- *Overview of linking models* on page 3-2

- Bare-metal linking model on page 3-3

- Partial linking model on page 3-4

- Base Platform Application Binary Interface (BPABI) linking model on page 3-5

- Base Platform linking model on page 3-6

- SysV linking model on page 3-8

- Concepts common to both BPABI and SysV linking models on page 3-9.

## 3.1 Overview of linking models

A linking model is a group of command-line options and memory maps that control the behavior of the linker.

**Bare-metal** This model does not target any specific platform. It enables you to create an image with your own custom operating system, memory map, and, application code if required. Some limited dynamic linking support is available. You can specify additional options depending on whether or not a scatter file is in use.

#### Partial linking

This model produces a platform-independent object suitable for input to the linker in a subsequent link step. It can be used as an intermediate step in the development process and performs limited processing of input objects to produce a single output object.

**BPABI** This model supports the DLL-like *Base Platform Application Binary Interface* (BPABI). It is intended to produce applications and DLLs that can run on a platform OS that varies in complexity. The memory model is restricted according to the BPABI specification.

#### **Base Platform**

This is an extension to the BPABI model to support scatter-loading.

**SysV** This model supports *System V* (SysV) models specified in the ELF used by ARM Linux. The memory model is restricted according to the ELF specification.

Related options in each model can be combined to tighten control over the output.

#### 3.1.1 See also

#### Concepts

- *Bare-metal linking model* on page 3-3

- *Partial linking model* on page 3-4

- Base Platform Application Binary Interface (BPABI) linking model on page 3-5

- Base Platform linking model on page 3-6

- SysV linking model on page 3-8

- Concepts common to both BPABI and SysV linking models on page 3-9.

#### Reference

• Chapter 10 BPABI and SysV shared libraries and executables.

#### Other information

Base Platform ABI for the ARM Architecture, http://infocenter.arm.com/help/topic/com.arm.doc.ihi0037-/index.html

## 3.2 Bare-metal linking model

The bare-metal model focuses on the conventional embedded market where the whole program, possibly including a *Real-Time Operating System* (RTOS), is linked in one pass. Very few assumptions can be made by the linker about the memory map of a bare metal system. Therefore, you must use the scatter-loading mechanism if you want more precise control.

By default, the linker attempts to resolve all the relocations statically. However, it is also possible to create a position-independent or relocatable image. Such an image can be executed from different addresses and have its relocations resolved at load or run-time. This can be achieved using a dynamic model.

With this type of model, you can:

- identify the regions that can be relocated or are position-independent using a scatter file or command-line options.

- identify the symbols that can be imported and exported using a steering file

- identify the shared libraries that are required by the ELF file using a steering file.

You can use the following options with this model:

- --edit=file\_list

- --scatter=file.

You can use the following options when scatter-loading is not used:

- --reloc

- --ro\_base=address

- --ropi

- --rosplit

- --rw\_base=*address*

- --rwpi

- --split

- --zi\_base.

#### 3.2.1 See also

#### Concepts

Methods of specifying an image memory map with the linker on page 4-8.

#### Reference

- *--edit=file\_list* on page 2-53

- --*reloc* on page 2-132

- *--ro base=address* on page 2-135

- *--ropi* on page 2-136

- --rosplit on page 2-137

- *--rw base=address* on page 2-139

- *--rwpi* on page 2-140

- --scatter=filename on page 2-142

- *--split* on page 2-154

- --*zi base=address* on page 2-193

- Chapter 3 Linker steering file command reference.

## 3.3 Partial linking model

Partial linking:

- eliminates duplicate copies of debug sections

- merges the symbol tables into one

- leaves unresolved references unresolved

- merges common data (COMDAT) groups

- generates an object that can be used as input to a subsequent link step.

A single output file is produced that can be used as input to a subsequent link step. If the linker finds multiple entry points in the input files it generates an error because the output file can have only one entry point.

To link with this model, use the --partial command-line option. Other linker command-line options supported by this model are:

- --edit=file\_list

- --exceptions\_tables=action.

— Note —

If you use partial linking, you cannot refer to the component objects by name in a scatter file. Therefore, you might have to update your scatter file.

### 3.3.1 See also

#### Concepts

What is a steering file? on page 7-24.

#### Reference

*Steering file format* on page 7-27.

- *--edit=file\_list* on page 2-53

- *--exceptions\_tables=action* on page 2-62

- *--partial* on page 2-119

- Chapter 3 *Linker steering file command reference*.

## 3.4 Base Platform Application Binary Interface (BPABI) linking model

The *Base Platform Application Binary Interface* (BPABI) is a meta-standard for third parties to generate their own platform-specific image formats. This means that the BPABI model produces as much information as possible without focusing on any specific platform.

Be aware of the following:

- You cannot use scatter-loading. However, the Base Platform linking model is an extension to the BPABI model that supports scatter-loading.

- The model assumes that shared objects cannot throw a C++ exception.

- The default value of the --pltgot option is direct.

- Symbol versioning must be used to ensure that all the required symbols are available at load time.

To link with this model, use the --bpabi command-line option. Other linker command-line options supported by this model are:

- --dll

- --force\_so\_throw, --no\_force\_so\_throw

- --pltgot=type

- --ro\_base=address

- --rosplit

- --rw\_base=address

- --rwpi.

#### 3.4.1 See also

#### Concepts

- Base Platform linking model on page 3-6

- Concepts common to both BPABI and SysV linking models on page 3-9

- About symbol versioning on page 10-27.

#### Reference

Linker Reference:

- *--bpabi* on page 2-24

- --dll on page 2-49

- --force\_so\_throw, --no\_force\_so\_throw on page 2-73

- *--pltgot=type* on page 2-121

- --ro base=address on page 2-135

- *--rosplit* on page 2-137

- *--rw\_base=address* on page 2-139

- *--rwpi* on page 2-140.

#### **Other information**

Base Platform ABI for the ARM Architecture, http://infocenter.arm.com/help/topic/com.arm.doc.ihi0037-/index.html.

## 3.5 Base Platform linking model

Base Platform enables you to create dynamically linkable images that do not have the memory map enforced by the *System V* (SysV) or *Base Platform Application Binary Interface* (BPABI) linking models. It enables you to:

- Create images with a memory map described in a scatter file.

- Have dynamic relocations so the images can be dynamically linked. The dynamic relocations can also target within the same image.

\_\_\_\_ Note \_\_\_\_\_

The BPABI specification places constraints on the memory model that can be violated using scatter-loading. However, because Base Platform is a superset of BPABI, it is possible to create a BPABI conformant image with Base Platform.

To link with the Base Platform model, use the --base\_platform command-line option.

If you specify this option, the linker acts as if you specified --bpabi, with the following exceptions:

• Scatter-loading is available with --scatter, in addition to the following options:

– --dll

- --force\_so\_throw, --no\_force\_so\_throw

- --pltgot=type is restricted to types none or direct

- --ro\_base=address

- --rosplit

- --rw\_base=address

- --rwpi.

- The default value of the --pltgot option is different to that for --bpabi:

- for --base\_platform, the default is --pltgot=none

- for --bpabi the default is --pltgot=direct.

- If you do not use a scatter file, the linker can ensure that the *Procedure Linkage Table* (PLT) section is placed correctly, and contains entries for calls only to imported symbols. If you specify a scatter file, the linker might not be able to find a suitable location to place the PLT.

Each load region containing code might require a PLT section to indirect calls from the load region to functions where the address is not known at static link time. The PLT section for a load region LR must be placed in LR and be accessible at all times to code within LR.

To ensure calls between relocated load regions ar run-time:

- Use the --pltgot=direct option to turn on PLT generation.

- Use the --pltgot\_opts=crosslr option to add entries in the PLT for calls between RELOC load regions. The linker generates a PLT for each load region so that calls do not have to be extended to reach a distant PLT.

Be aware of the following:

- The model assumes that shared objects cannot throw a C++ exception.

- Symbol versioning must be used to ensure that all the required symbols are available at load time.

There are restrictions on the type of scatter files you can use.

### 3.5.1 See also

#### Concepts

- Base Platform Application Binary Interface (BPABI) linking model on page 3-5

- Concepts common to both BPABI and SysV linking models on page 3-9

- Methods of specifying an image memory map with the linker on page 4-8

- *About symbol versioning* on page 10-27

- Restrictions on the use of scatter files with the Base Platform model on page 11-2

- Example scatter file for the Base Platform linking model on page 11-5.

#### Reference

- *--base\_platform* on page 2-18

- *--dll* on page 2-49

- -*force\_so\_throw, --no\_force\_so\_throw* on page 2-73

- *--pltgot=type* on page 2-121

- *--pltgot\_opts=mode* on page 2-122

- --ro\_base=address on page 2-135

- *--rosplit* on page 2-137

- *--rw\_base=address* on page 2-139

- *--rwpi* on page 2-140

- *--scatter=filename* on page 2-142.

## 3.6 SysV linking model

The *System V* (SysV) model produces SysV shared objects and executables. It can also be used to produce ARM Linux compatible shared objects and executables.

Be aware of the following:

- you cannot use scatter-loading

- the model assumes that shared objects can throw an exception

- thread local storage is supported.

To link with this model, use the --sysv command-line option. Other linker command-line options supported by this model are:

- --force\_so\_throw, --no\_force\_so\_throw

- --fpic

- --linux\_abitag=version\_id

- --shared.

#### 3.6.1 See also

#### Concepts

• Concepts common to both BPABI and SysV linking models on page 3-9.

#### Reference

- *--force\_so\_throw, --no\_force\_so\_throw* on page 2-73

- *--fpic* on page 2-74

- --*linux\_abitag=version\_id* on page 2-101

- *--shared* on page 2-146

- *--sysv* on page 2-170.

## 3.7 Concepts common to both BPABI and SysV linking models

For both *Base Platform Application Binary Interface* (BPABI) and *System V* (SysV) linking models, images and shared objects usually run on an existing operating platform.

There are many similarities between the BPABI and the SysV models. For example, both produce a program header that maps the exception tables. The main differences are in the memory model, and in the *Procedure Linkage Table* (PLT) and *Global Offset Table* (GOT) structure, referred to collectively as PLTGOT. There are many options that are common to both models.

#### 3.7.1 Restrictions of the BPABI and SysV

Both the BPABI and SysV models have the following restrictions:

- unused section elimination is turned off for shared libraries and DLLs

- virtual function elimination is turned off

- read write data compression is not permitted

- scatter-loading is not permitted

- \_\_AT sections are not permitted.

—— Note ——

Scatter-loading is supported in the Base Platform linking model.

#### 3.7.2 See also

#### Concepts

- Base Platform Application Binary Interface (BPABI) linking model on page 3-5

- Base Platform linking model on page 3-6

- SysV linking model on page 3-8.

#### Reference

- *--base\_platform* on page 2-18

- --bpabi on page 2-24

- *--dynamic\_debug* on page 2-50

- --force\_so\_throw, --no\_force\_so\_throw on page 2-73

- --runpath=pathlist on page 2-138

- --soname=name on page 2-151

- --symver script=filename on page 2-167

- --symver soname on page 2-168

- *--sysv* on page 2-170.

## Chapter 4 Image structure and generation

The following topics describe the image structure and the functionality available in the ARM linker, armlink, to generate images:

#### Tasks

- Using command-line options to control the generation of C++ exception tables on page 4-31

- Controlling how the linker searches for the ARM standard libraries on page 4-36

- Specifying user libraries when linking on page 4-38.

- *The image structure* on page 4-3

- Input sections, output sections, regions, and Program Segments on page 4-5

- Load view and execution view of an image on page 4-6

- *Methods of specifying an image memory map with the linker* on page 4-8

- *Types of simple image* on page 4-10

- Type 1 image, one load region and contiguous execution regions on page 4-11

- Type 2 image, one load region and non-contiguous execution regions on page 4-13

- Type 3 image, two load regions and non-contiguous execution regions on page 4-15

- *Image entry points* on page 4-17

- About specifying an initial entry point on page 4-18

- Section placement with the linker on page 4-19

- Placing sections with FIRST and LAST attributes on page 4-21

- Section alignment with the linker on page 4-22

- *Demand paging* on page 4-23

- About ordering execution regions containing Thumb code on page 4-25

- Overview of veneers on page 4-26

- Veneer sharing on page 4-27

- *Veneer types* on page 4-28

- Generation of position independent to absolute veneers on page 4-29

- *Reuse of veneers when scatter-loading* on page 4-30

- *About weak references and definitions* on page 4-32

- How the linker performs library searching, selection, and scanning on page 4-35

- *How the linker resolves references* on page 4-39

- Use of the strict family of options in the linker on page 4-41.

### 4.1 The image structure

The structure of an image is defined by the:

- number of its constituent regions and output sections

- positions in memory of these regions and sections when the image is loaded

- positions in memory of these regions and sections when the image executes.

Each link stage has a different view of the image:

#### ELF object file view (linker input)

The ELF object file view comprises input sections. The ELF object file can be:

- a relocatable file that holds code and data suitable for linking with other object files to create an executable or a shared object file

- an executable file that holds a program suitable for execution

- a shared object file that holds code and data in the following contexts:

- the linker processes the file with other relocatable and shared object files to create another object file

- the dynamic linker combines the file with an executable file and other shared objects to create a process image.

- Linker view The linker has two views for the address space of a program that become distinct in the presence of overlaid, position-independent, and relocatable program fragments (code or data):

- The load address of a program fragment is the target address that the linker expects an external agent such as a program loader, dynamic linker, or debugger to copy the fragment from the ELF file. This might not be the address at which the fragment executes.

- The execution address of a program fragment is the target address where the linker expects the fragment to reside whenever it participates in the execution of the program.

If a fragment is position-independent or relocatable, its execution address can vary during execution.

#### ELF image file view (linker output)

The ELF image file view comprises Program Segments and output sections:

- a load region corresponds to a Program Segment

- an execution region corresponds to up to three output sections:

- RO section

- RW section

- ZI section.

One or more execution regions make up a load region.

——Note -

With armlink, the maximum size of a Program Segment is 2GB.

When describing a memory view:

- the term *root region* is used to describe a region that has the same load and execution addresses

- load regions are equivalent to ELF segments.

| ELF image file view                                                   | Linker view          | ELF object file view               |

|-----------------------------------------------------------------------|----------------------|------------------------------------|

| ELF Header                                                            | ELF Header           | ELF Header                         |

| Program Header Table                                                  | Program Header Table | Program Header Table<br>(optional) |

| Segment 1 (Load Region 1)                                             | Load Region 1        | Input Section 1.1.1                |

|                                                                       |                      | Input Section 1.1.2                |

| Output sections 1.1                                                   |                      |                                    |

| Output sections 1.2                                                   | Execution Region 1   | Input Section 1.2.1                |

|                                                                       |                      |                                    |

| Output sections 1.3                                                   |                      | Input Section 1.3.1                |

|                                                                       |                      | Input Section 1.3.2                |

| Segment 2 (Load Region 2)                                             | Load Region 2        |                                    |

|                                                                       |                      | Input Section 2.1.1                |

| Output section 2.1                                                    | Execution Region 2   | Input Section 2.1.2                |

|                                                                       |                      | Input Section 2.1.3                |

|                                                                       |                      |                                    |

|                                                                       |                      | Input Section n                    |

| Section Header Table<br>(optional) Section Header Table<br>(optional) |                      | Section Header Table               |

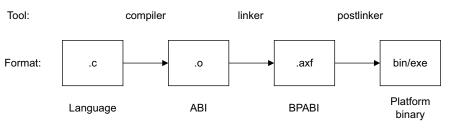

The following figure shows the relationship between the views at each link stage:

#### Figure 4-1 Relationship between sections, regions, and segments

#### 4.1.1 See also

#### Tasks

Introducing the ARM Compiler toolchain:

• *Changing to the 64-bit linker* on page 2-7.

- Input sections, output sections, regions, and Program Segments on page 4-5

- Load view and execution view of an image on page 4-6.

## 4.2 Input sections, output sections, regions, and Program Segments

An object or image file is constructed from a hierarchy of input sections, output sections, regions, and Program Segments:

#### **Input section**

An input section is an individual section from an input object file. It contains code, initialized data, or describes a fragment of memory that is not initialized or that must be set to zero before the image can execute. These properties are represented by attributes such as RO, RW and ZI. These attributes are used by armlink to group input sections into bigger building blocks called output sections and regions.

#### **Output section**

An output section is a group of input sections that have the same RO, RW, or ZI attribute, and that are placed contiguously in memory by the linker. An output section has the same attributes as its constituent input sections. Within an output section, the input sections are sorted according to the section placement rules.

**Region** A region is a contiguous sequence of one, two, or three output sections depending on the contents of the number of sections with different attributes. The output sections in a region are sorted according to their attributes. The RO output section is first, then the RW output section, and finally the ZI output section. A region typically maps onto a physical memory device, such as ROM, RAM, or peripheral.

#### **Program Segment**

A Program Segment corresponds to a load region and contains output sections. Program Segments hold information such as text and data.

— Note —

With armlink, the maximum size of a Program Segment is 2GB.

#### 4.2.1 See also

#### Tasks

Introducing the ARM Compiler toolchain:

*Changing to the 64-bit linker* on page 2-7.

- The image structure on page 4-3

- *Methods of specifying an image memory map with the linker* on page 4-8

- Section placement with the linker on page 4-19.

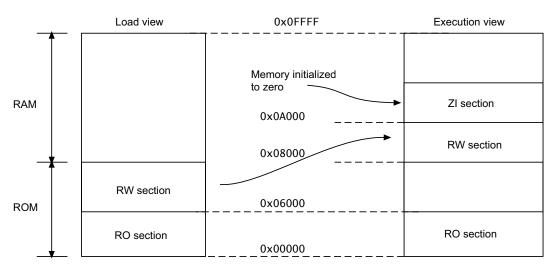

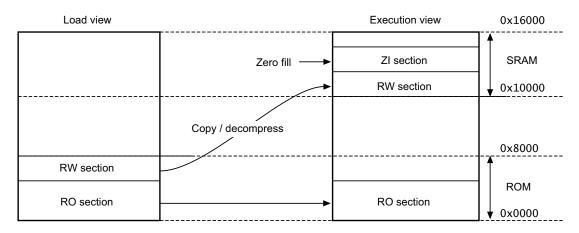

### 4.3 Load view and execution view of an image

Image regions are placed in the system memory map at load time. Before you can execute the image, you might have to move some of its regions to their execution addresses and create the ZI output sections. For example, initialized RW data might have to be copied from its load address in ROM to its execution address in RAM.

The memory map of an image has the following distinct views:

- Load view Describes each image region and section in terms of the address where it is located when the image is loaded into memory, that is, the location before image execution starts.

- **Execution view** Describes each image region and section in terms of the address where it is located during image execution.

The following figure shows these views:

#### Figure 4-2 Load and execution memory maps

The following table compares the load and execution views:

#### Table 4-1 Comparing load and execution views

| Load            | Description                                                                                                                                                                                                       | Execution            | Description                                                                                            |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------|

| Load<br>address | The address where a section or region is<br>loaded into memory before the image<br>containing it starts executing. The load<br>address of a section or a non-root region<br>can differ from its execution address | Execution<br>address | The address where a section or region is<br>located while the image containing it is<br>being executed |

| Load region     | A region in the load address space                                                                                                                                                                                | Execution region     | A region in the execution address space                                                                |

#### 4.3.1 See also

- The image structure on page 4-3

- Input sections, output sections, regions, and Program Segments on page 4-5

- Methods of specifying an image memory map with the linker on page 4-8

Section placement with the linker on page 4-19.

•

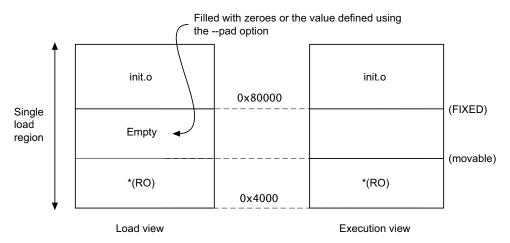

# 4.4 Methods of specifying an image memory map with the linker

An image can consist of any number of regions and output sections. Regions can have different load and execution addresses. To construct the memory map of an image, armlink must have information about:

- how input sections are grouped into output sections and regions

- where regions are to be located in the memory maps.

Depending on the complexity of the memory maps of the image, there are two ways to pass this information to armlink:

#### Using command-line options

The following options can be used for simple cases where an image has only one or two load regions and up to three execution regions:

- --first

- --last

- --ro\_base

- --rw\_base

- --ropi

- --rwpi

- --split

- --rosplit

- --zi\_base.

These options provide a simplified notation that gives the same settings as a scatter-loading description for a simple image.

#### Using a scatter file

A scatter file is a textual description of the memory layout and code and data placement. It is used for more complex cases where you require complete control over the grouping and placement of image components. To use a scatter file, specify --scatter=filename at the command-line.

— Note —

You cannot use --scatter with the other memory map related command-line options.

| Scatter file Equivalent command-line optio |                                 | Equivalent command-line options |

|--------------------------------------------|---------------------------------|---------------------------------|

|                                            |                                 | •                               |

|                                            | init.o (INIT, +FIRST)<br>*(+RO) | first=init.o(init)              |

| }                                          |                                 |                                 |

| RAM<br>{                                   | 0x400000                        | rw_base=0x400000                |

| }                                          | *(+RW)                          |                                 |

| -                                          | 0x405000                        | zi_base=0x405000                |

| , i                                        | *(+ZI)                          |                                 |

| }<br>}                                     |                                 |                                 |

Table 4-2 Comparison of scatter file and equivalent command-line options

## 4.4.1 See also

# Tasks

• Chapter 8 Using scatter files.

## Concepts

- *The image structure* on page 4-3

- Input sections, output sections, regions, and Program Segments on page 4-5

- Load view and execution view of an image on page 4-6

- *Types of simple image* on page 4-10.

# Reference

- *--first=section\_id* on page 2-71

- *--last=section\_id* on page 2-93

- *--ro\_base=address* on page 2-135

- *--ropi* on page 2-136

- --rosplit on page 2-137

- *--rw\_base=address* on page 2-139

- *--rwpi* on page 2-140

- *--scatter=filename* on page 2-142

- *--split* on page 2-154

- --*zi\_base=address* on page 2-193.

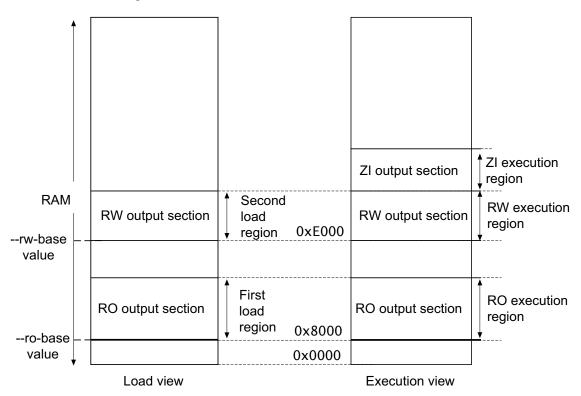

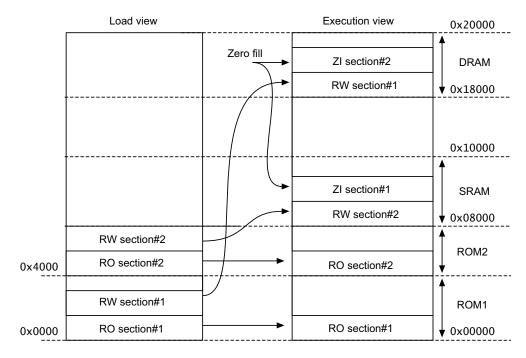

# 4.5 Types of simple image

A simple image consists of a number of input sections of type RO, RW, and ZI. These input sections are collated to form the RO, RW, and ZI output sections. Depending on how the output sections are arranged within load and execution regions, there are three basic types of simple image:

- Type 1One region in load view, three contiguous regions in execution view. Use the<br/>--ro\_base option to create this type of image.

- Type 2One region in load view, three non-contiguous regions in execution view. Use the<br/>--ro\_base and --rw\_base options to create this type of image.

- Type 3Two regions in load view, three non-contiguous regions in execution view. Use<br/>the --ro\_base, --rw\_base, and --split options to create this type of image.

In all the simple image types:

- the first execution region contains the RO output section

- the second execution region contains the RW output section (if present)

- the third execution region contains the ZI output section (if present).

These execution regions are referred to as the RO, the RW, and the ZI execution region.

However, you can also use the --rosplit option for a Type 3 image. This option splits the default load region into two RO output sections, one for code and one for data.

You can also use the --zi\_base command-line option to specify the base address of a ZI execution region for Type 1 and Type 2 images. This option is ignored if you also use the --split command-line option that is required for Type 3 images.

You can also create simple images with scatter files.

#### 4.5.1 See also

#### Concepts

- *Type 1 image, one load region and contiguous execution regions* on page 4-11

- *Type 2 image, one load region and non-contiguous execution regions* on page 4-13

- *Type 3 image, two load regions and non-contiguous execution regions* on page 4-15

- Equivalent scatter-loading descriptions for simple images on page 8-62.

#### Reference

- --ro base=address on page 2-135

- *--rosplit* on page 2-137

- *--rw base=address* on page 2-139

- *--scatter=filename* on page 2-142

- *--split* on page 2-154

- --zi base=address on page 2-193.

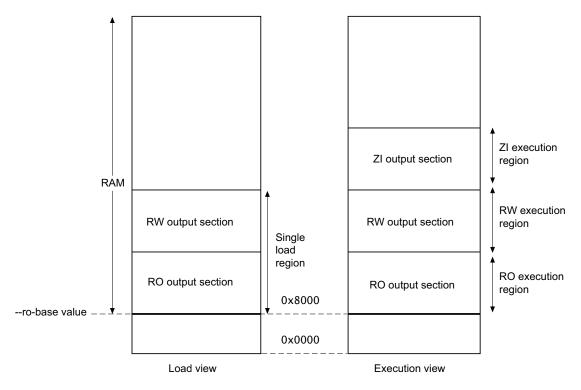

# 4.6 Type 1 image, one load region and contiguous execution regions

A Type 1 image consists of a single load region in the load view and three execution regions placed contiguously in the memory map. This approach is suitable for systems that load programs into RAM, for example, an OS bootloader or a desktop system.

Figure 4-3 Simple type 1 image

Use the following command for images of this type:

armlink --ro\_base 0x8000

—— Note ——

0x8000 is the default address, so you do not have to specify --ro\_base for the example.

## 4.6.1 Load view

The single load region consists of the RO and RW output sections, placed consecutively. The RO and RW execution regions are both root regions. The ZI output section does not exist at load time. It is created before execution, using the output section description in the image file.

## 4.6.2 Execution view

The three execution regions containing the RO, RW, and ZI output sections are arranged contiguously. The execution addresses of the RO and RW execution regions are the same as their load addresses, so nothing has to be moved from its load address to its execution address. However, the ZI execution region that contains the ZI output section is created at run-time.

Use armlink option --ro\_base *address* to specify the load and execution address of the region containing the RO output. The default address is 0x8000.

Use the --zi\_base command-line option to specify the base address of a ZI execution region.

## 4.6.3 See also

## Concepts

- *The image structure* on page 4-3

- Input sections, output sections, regions, and Program Segments on page 4-5

- Load view and execution view of an image on page 4-6.

## Reference

- *--ro\_base=address* on page 2-135

- --*zi\_base=address* on page 2-193.

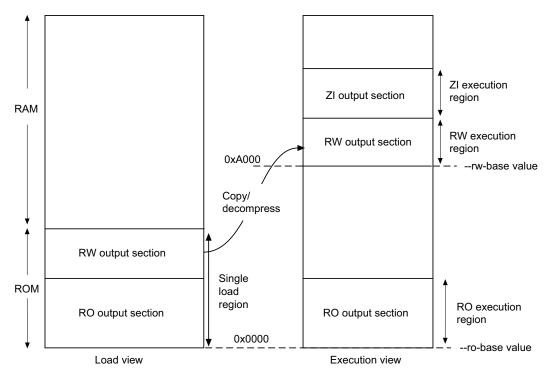

# 4.7 Type 2 image, one load region and non-contiguous execution regions

A Type 2 image consists of a single load region, and three execution regions in execution view. The RW execution region is not contiguous with the RO execution region. This approach is used, for example, for ROM-based embedded systems, where RW data is copied from ROM to RAM at startup:

Figure 4-4 Simple type 2 image

Use the following command for images of this type:

armlink --ro\_base 0x0 --rw\_base 0xA000

#### 4.7.1 Load view

In the load view, the single load region consists of the RO and RW output sections placed consecutively, for example, in ROM. Here, the RO region is a root region, and the RW region is non-root. The ZI output section does not exist at load time. It is created at runtime.

#### 4.7.2 Execution view

In the execution view, the first execution region contains the RO output section and the second execution region contains the RW and ZI output sections.

The execution address of the region containing the RO output section is the same as its load address, so the RO output section does not have to be moved. That is, it is a root region.

The execution address of the region containing the RW output section is different from its load address, so the RW output section is moved from its load address (from the single load region) to its execution address (into the second execution region). The ZI execution region, and its output section, is placed contiguously with the RW execution region.

Use armlink options --ro\_base *address* to specify the load and execution address for the RO output section, and --rw\_base *exec\_address* to specify the execution address of the RW output section. If you do not use the --ro\_base option to specify the address, the default value of 0x8000 is used by armlink. For an embedded system, 0x0 is typical for the --ro\_base value. If you do not use the --rw\_base option to specify the address, the default is to place RW directly above RO (as in a Type 1 image).

Use the --zi\_base command-line option to specify the base address of a ZI execution region.

— Note —

The execution region for the RW and ZI output sections cannot overlap any of the load regions.

## 4.7.3 See also

# Concepts

- *The image structure* on page 4-3

- Input sections, output sections, regions, and Program Segments on page 4-5

- Load view and execution view of an image on page 4-6

- *Type 1 image, one load region and contiguous execution regions* on page 4-11.