# ARM<sup>®</sup> Compiler toolchain

Version 5.0

**Using the Assembler**

# ARM Compiler toolchain Using the Assembler

Copyright © 2010-2011 ARM. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

#### **Change History**

| Date              | Issue | Confidentiality  | Change                                           |

|-------------------|-------|------------------|--------------------------------------------------|

| May 2010          | A     | Non-Confidential | ARM Compiler toolchain v4.1 Release              |

| 30 September 2010 | В     | Non-Confidential | Update 1 for ARM Compiler toolchain v4.1         |

| 28 January 2011   | С     | Non-Confidential | Update 2 for ARM Compiler toolchain v4.1 Patch 3 |

| 30 April 2011     | D     | Non-Confidential | ARM Compiler toolchain v5.0 Release              |

| 29 July 2011      | Е     | Non-Confidential | Update 1 for ARM Compiler toolchain v5.0         |

| 30 September 2011 | F     | Non-Confidential | ARM Compiler toolchain v5.01 Release             |

#### **Proprietary Notice**

Words and logos marked with  $^*$  or  $^{\text{m}}$  are registered trademarks or trademarks of ARM $^*$  in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

# Contents

# **ARM Compiler toolchain Using the Assembler**

| Chapter 1 | Conv | ventions and feedback                                               |      |

|-----------|------|---------------------------------------------------------------------|------|

| Chapter 2 | Over | rview of the Assembler                                              |      |

| -         | 2.1  | About the ARM Compiler toolchain assemblers                         | 2-2  |

|           | 2.2  | Key features of the assembler                                       |      |

|           | 2.3  | How the assembler works                                             | 2-4  |

|           | 2.4  | Directives that can be omitted in pass 2 of the assembler           | 2-6  |

| Chapter 3 | Over | view of the ARM Architecture                                        |      |

| -         | 3.1  | About the ARM architecture                                          | 3-2  |

|           | 3.2  | ARM, Thumb, and ThumbEE instruction sets                            | 3-3  |

|           | 3.3  | Changing between ARM, Thumb, and ThumbEE state                      | 3-4  |

|           | 3.4  | Processor modes, and privileged and unprivileged software execution | 3-5  |

|           | 3.5  | Processor modes in ARMv6-M and ARMv7-M                              |      |

|           | 3.6  | NEON technology                                                     | 3-7  |

|           | 3.7  | VFP coprocessor                                                     | 3-8  |

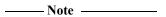

|           | 3.8  | ARM registers                                                       | 3-9  |

|           | 3.9  | General-purpose registers                                           | 3-11 |

|           | 3.10 | Register accesses                                                   | 3-12 |

|           | 3.11 | Predeclared core register names                                     | 3-13 |

|           | 3.12 | Predeclared extension register names                                | 3-14 |

|           | 3.13 | Predeclared XScale register names                                   | 3-15 |

|           | 3.14 | Predeclared coprocessor names                                       | 3-16 |

|           | 3.15 | Program Counter                                                     | 3-17 |

|           | 3.16 | Application Program Status Register                                 | 3-18 |

|           | 3.17 | The Q flag                                                          | 3-19 |

|           | 3.18 | Current Program Status Register                                     |      |

|           | 3.19 | Saved Program Status Registers (SPSRs)                              | 3-21 |

|           | 3.20 | Instruction set overview                                            | 3-22 |

| Chapter 4 Chapter 5 | 4.1<br>4.2<br>4.3<br>4.4                               | Access to the inline barrel shifter  Cture of Assembly Language Modules  Syntax of source lines in assembly language  Literals  ELF sections and the AREA directive  An example ARM assembly language module  ng ARM Assembly Language  Unified Assembler Language | 4-2<br>4-4<br>4-5 |

|---------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| ·                   | 4.1<br>4.2<br>4.3<br>4.4<br><b>Writi</b><br>5.1<br>5.2 | Syntax of source lines in assembly language  Literals  ELF sections and the AREA directive  An example ARM assembly language module  ng ARM Assembly Language                                                                                                      | 4-4<br>4-5        |

| Chapter 5           | 4.2<br>4.3<br>4.4<br><b>Writi</b><br>5.1<br>5.2        | Literals  ELF sections and the AREA directive  An example ARM assembly language module  ng ARM Assembly Language                                                                                                                                                   | 4-4<br>4-5        |

| Chapter 5           | 4.3<br>4.4<br><b>Writi</b><br>5.1<br>5.2               | ELF sections and the AREA directive                                                                                                                                                                                                                                | 4-5               |

| Chapter 5           | 4.4<br><b>Writi</b><br>5.1<br>5.2                      | An example ARM assembly language module  ng ARM Assembly Language                                                                                                                                                                                                  |                   |

| Chapter 5           | <b>Writi</b> 5.1 5.2                                   | ng ARM Assembly Language                                                                                                                                                                                                                                           | 4-6               |

| Chapter 5           | 5.1<br>5.2                                             |                                                                                                                                                                                                                                                                    |                   |

|                     | 5.2                                                    | Unified Assembler Language                                                                                                                                                                                                                                         |                   |

|                     |                                                        | Offilied Assembler Language                                                                                                                                                                                                                                        | 5-3               |

|                     | E 3                                                    | Subroutines calls                                                                                                                                                                                                                                                  |                   |

|                     |                                                        | Load immediates into registers                                                                                                                                                                                                                                     |                   |

|                     | 5.4                                                    | Load immediate values using MOV and MVN                                                                                                                                                                                                                            |                   |

|                     | 5.5                                                    | Load 32-bit values to a register using MOV32                                                                                                                                                                                                                       |                   |

|                     | 5.6                                                    | Load immediate 32-bit values to a register using LDR Rd, =const                                                                                                                                                                                                    |                   |

|                     | 5.7                                                    | Literal pools                                                                                                                                                                                                                                                      |                   |

|                     | 5.8                                                    | Load addresses into registers                                                                                                                                                                                                                                      |                   |

|                     | 5.9                                                    | Load addresses to a register using ADR                                                                                                                                                                                                                             |                   |

|                     | 5.10                                                   | Load addresses to a register using ADRL                                                                                                                                                                                                                            |                   |

|                     | 5.11<br>5.12                                           | Load addresses to a register using LDR Rd, =label                                                                                                                                                                                                                  |                   |

|                     |                                                        | Other ways to Load and store registers                                                                                                                                                                                                                             |                   |

|                     | 5.13                                                   | Load and store multiple register instructions                                                                                                                                                                                                                      |                   |

|                     | 5.14<br>5.15                                           | Load and store multiple instructions available in ARM and Thumb  Stack implementation using LDM and STM                                                                                                                                                            |                   |

|                     | 5.16                                                   | Stack operations for nested subroutines                                                                                                                                                                                                                            |                   |

|                     | 5.17                                                   | Block copy with LDM and STM                                                                                                                                                                                                                                        |                   |

|                     | 5.18                                                   | Memory accesses                                                                                                                                                                                                                                                    |                   |

|                     | 5.19                                                   | Read-Modify-Write procedure                                                                                                                                                                                                                                        |                   |

|                     | 5.20                                                   | Optional hash                                                                                                                                                                                                                                                      |                   |

|                     | 5.21                                                   | Use of macros                                                                                                                                                                                                                                                      |                   |

|                     | 5.22                                                   | Test-and-branch macro example                                                                                                                                                                                                                                      |                   |

|                     | 5.23                                                   | Unsigned integer division macro example                                                                                                                                                                                                                            |                   |

|                     | 5.24                                                   | Instruction and directive relocations                                                                                                                                                                                                                              |                   |

|                     | 5.25                                                   | Symbol versions                                                                                                                                                                                                                                                    |                   |

|                     | 5.26                                                   | Frame directives                                                                                                                                                                                                                                                   |                   |

|                     | 5.27                                                   | Exception tables and Unwind tables                                                                                                                                                                                                                                 |                   |

|                     | 5.28                                                   | Assembly language changes after RVCTv2.1                                                                                                                                                                                                                           |                   |

| Chapter 6           | Conc                                                   | lition Codes                                                                                                                                                                                                                                                       |                   |

|                     | 6.1                                                    | Conditional instructions                                                                                                                                                                                                                                           | 6-2               |

|                     | 6.2                                                    | Conditional execution in ARM state                                                                                                                                                                                                                                 |                   |

|                     | 6.3                                                    | Conditional execution in Thumb state                                                                                                                                                                                                                               | 6-4               |

|                     | 6.4                                                    | Updates to the ALU status flags                                                                                                                                                                                                                                    | 6-5               |

|                     | 6.5                                                    | Condition code suffixes                                                                                                                                                                                                                                            |                   |

|                     | 6.6                                                    | Condition code meanings                                                                                                                                                                                                                                            | 6-8               |

|                     | 6.7                                                    | Benefits of using conditional execution                                                                                                                                                                                                                            | 6-10              |

|                     | 6.8                                                    | Illustration of the benefits of using conditional instructions                                                                                                                                                                                                     |                   |

|                     | 6.9                                                    | Optimization for execution speed                                                                                                                                                                                                                                   | 6-14              |

| Chapter 7           | Using                                                  | g the Assembler                                                                                                                                                                                                                                                    |                   |

|                     | 7.1                                                    | Assembler command line syntax                                                                                                                                                                                                                                      | 7-2               |

|                     | 7.2                                                    | Assembler commands listed in groups                                                                                                                                                                                                                                |                   |

|                     | 7.3                                                    | Specify command line options with an environment variable                                                                                                                                                                                                          |                   |

|                     | 7.4                                                    | Using stdin to input source code to the assembler                                                                                                                                                                                                                  |                   |

|                     | 7.5                                                    | Built-in variables and constants                                                                                                                                                                                                                                   |                   |

|                     | 7.6                                                    | Versions of armasm                                                                                                                                                                                                                                                 | 7-13              |

|                     | 7.7                                                    | Diagnostic messages                                                                                                                                                                                                                                                | 7-14              |

|                     | 7.8                                                    | Interlocks diagnostics                                                                                                                                                                                                                                             | 7-15              |

|           | 7.9          | IT block generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7-16 |

|-----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|           | 7.10         | Thumb branch target alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7-17 |

|           | 7.11         | Thumb code size diagnostics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7-18 |

|           | 7.12         | ARM and Thumb instruction portability diagnostics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7-19 |

|           | 7.13         | Instruction width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7-20 |

|           | 7.14         | 2 pass assembler diagnostics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7-21 |

|           | 7.15         | Using the C preprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7-22 |

|           | 7.16         | Address alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7-24 |

|           | 7.17         | Instruction width selection in Thumb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7-25 |

| Chapter 8 | Sym          | bols, Literals, Expressions, and Operators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

|           | 8.1          | Symbol naming rules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8-3  |

|           | 8.2          | Variables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8-4  |

|           | 8.3          | Numeric constants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

|           | 8.4          | Assembly time substitution of variables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

|           | 8.5          | Register-relative and PC-relative expressions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8-7  |

|           | 8.6          | Labels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

|           | 8.7          | Labels for PC-relative addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

|           | 8.8          | Labels for register-relative addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

|           | 8.9          | Labels for absolute addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8-11 |

|           | 8.10         | Local labels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _    |

|           | 8.11         | Syntax of local labels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

|           | 8.12         | String expressions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

|           | 8.13         | String literals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|           | 8.14         | Numeric expressions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |