# ARM<sup>®</sup> RealView<sup>®</sup> ESL API v2.0 Developer's Guide

Copyright © 2007 ARM Limited. All rights reserved. ARM DUI 0359B

## ARM RealView ESL API v2.0 Developer's Guide

Copyright © 2007 ARM Limited. All rights reserved.

#### **Release Information**

Change history

| Description  | Issue | Confidentiality  | Change                                                                                                                                  |

|--------------|-------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| January 2007 | А     | Non-confidential | New document based on ARM RealView SoC<br>Designer 6.1 Developer's Guide and updated to<br>reflect version 1.1 of the RealView ESL API. |

| June 2007    | В     | Non-confidential | Updated for ESL API version 2.0. Mx_naming conventions replaced with CASI, CADI, and CAPI.                                              |

#### **Proprietary Notice**

Words and logos marked with<sup>®</sup> or <sup>™</sup> are registered trademarks or trademarks owned by ARM Limited, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

# Contents ARM RealView ESL API v2.0 Developer's Guide

#### Preface

| About this document | х  |

|---------------------|----|

| Feedback xi         | ii |

| Chapter 1 | Intro | duction                                            |      |

|-----------|-------|----------------------------------------------------|------|

| -         | 1.1   | Overview                                           | 1-2  |

|           | 1.2   | ESL API interface layers                           | 1-3  |

|           | 1.3   | Theory of operation                                | 1-5  |

|           | 1.4   | Components                                         |      |

|           | 1.5   | Connections                                        | 1-7  |

|           | 1.6   | Cycle based scheduling                             | 1-17 |

|           | 1.7   | Simulation stages                                  | 1-21 |

|           | 1.8   | Organizing source files for components and systems |      |

|           | 1.9   | Overview of component creation                     |      |

|           | 1.10  | Working with component ports                       | 1-28 |

|           | 1.11  | Checklist for components                           | 1-36 |

|           | 1.12  | CAInterface extensions                             | 1-41 |

| Chapter 2 | The ( | Cycle Accurate Simulation Interface                |      |

|           | 2.1   | Class overview                                     |      |

|           | 2.2   | The CASIModule class                               | 2-10 |

|           | 2.3   | The CASIPortIF class                               |      |

|            | 2.4   | The clock interface classes                   | 2-41  |

|------------|-------|-----------------------------------------------|-------|

|            | 2.5   | The transaction interface classes             | 2-52  |

|            | 2.6   | The signal interface classes                  | 2-91  |

|            | 2.7   | The component factory class CASIFactory       | 2-100 |

|            | 2.8   | The save/restore interface CASISaveRestore    |       |

|            | 2.9   | Integrating CASI models into OSCI SystemC     |       |

| Chapter 3  | The   | Cycle Accurate Debug Interface                |       |

| -          | 3.1   | Introduction                                  | 3-2   |

|            | 3.2   | Defining a CADI interface                     | 3-12  |

|            | 3.3   | The CADIDisassembler class                    |       |

|            | 3.4   | The CADIProfiling class                       |       |

|            | 3.5   | The CADICallback class                        |       |

|            | 3.6   | CADIBroker                                    | 3-68  |

|            | 3.7   | The CADISimulationFactory class               | 3-73  |

|            | 3.8   | CADI data structures                          |       |

|            | 3.9   | Accessing the debug interface from sc_main()  |       |

| Chapter 4  | The   | Cycle Accurate Profiling Interface            |       |

|            | 4.1   | Introduction to CAPI                          | 4-2   |

|            | 4.2   | The CAPI classes                              |       |

|            | 4.3   | The CAPIRegistry class                        |       |

|            | 4.4   | The CAPICallback class                        |       |

|            | 4.5   | CAPI data structures                          |       |

|            | 4.6   | Accessing CAPI                                |       |

|            | 4.7   | Example CAPI implementation                   |       |

| Chapter 5  | The   | CASI Memory Map Interface                     |       |

|            | 5.1   | CASIMMI interfaces                            | 5-2   |

|            | 5.2   | Sample implementation                         |       |

| Appendix A | Stati | c Scheduling of Communication Functions       |       |

|            | A.1   | Introduction to combinatorial path scheduling | Δ-2   |

|            | A.2   | Specifying the combinatorial path             |       |

|            | A.3   | Error checking                                |       |

|            | A.4   | Example implementation                        |       |

| Appendix B | AME   | A <sup>™</sup> AHB TLM Specification for CASI |       |

|            | B.1   | Introduction                                  | B-2   |

|            | B.2   | AHB control signals                           |       |

|            | B.3   | Implementation details for AHB interfaces     |       |

| Appendix C | AME   | BA® AXI TLM Specification for CASI            |       |

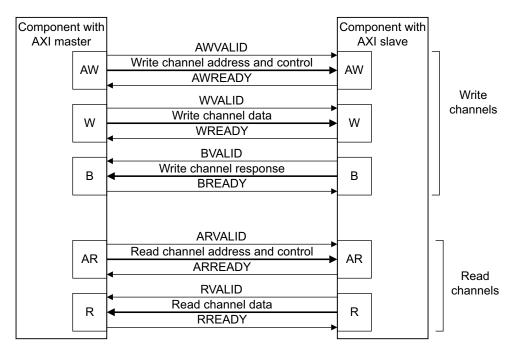

| rr         | C.1   | Introduction to AXI                           | C-2   |

|            | C.2   | Introduction to the CASI TLM for AXI          |       |

|            | C.3   | ESL API implementation of the AXI TLM         |       |

|            | 2.0   |                                               |       |

# List of Tables **ARM RealView ESL API v2.0 Developer's Guide**

|           | Change history                                  | ii   |

|-----------|-------------------------------------------------|------|

|           |                                                 | xi   |

| Table 1-1 | Example AHB to CASI mapping                     | 1-16 |

| Table 1-2 | Example AHB implementation                      | 1-16 |

| Table 1-3 | sc_port classes                                 | 1-29 |

| Table 2-1 | Interface classes                               | 2-3  |

| Table 2-2 | Predefined classes                              | 2-5  |

| Table 2-3 | Interface classes                               | 2-6  |

| Table C-1 | Signals on the write address channel (AW)       | C-3  |

| Table C-2 | Signals on the write data channel (W)           | C-5  |

| Table C-3 | Signals in the write response channel (B)       | C-5  |

| Table C-4 | Signals on the read address channel (AR)        | C-6  |

| Table C-5 | Signals in the read data channel (R)            | C-7  |

| Table C-6 | Handshake signals and status                    |      |

| Table C-7 | Current transaction and channels for reads      | C-21 |

| Table C-8 | Current transaction and channels for writes     | C-21 |

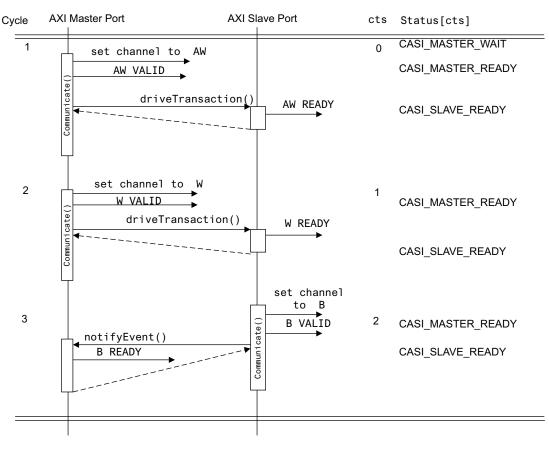

| Table C-9 | Cycle by cycle activity for a write transaction | C-22 |

|           |                                                 |      |

List of Tables

# List of Figures **ARM RealView ESL API v2.0 Developer's Guide**

| Figure 1-1  | Interface layers                                                          | 1-4    |

|-------------|---------------------------------------------------------------------------|--------|

| Figure 1-2  | A sample component with properties, parameters, and ports                 | 1-6    |

| Figure 1-3  | Signal-based communication                                                |        |

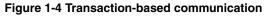

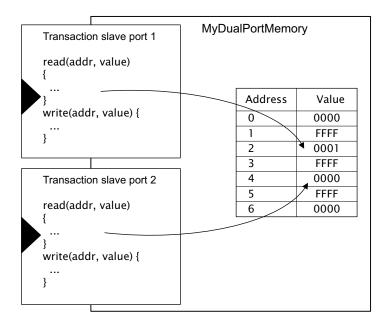

| Figure 1-4  | Transaction-based communication                                           | 1-7    |

| Figure 1-5  | Dual ported memory component with two transaction slave ports             | 1-8    |

| Figure 1-6  | CPU component with separate transaction ports for data and program memory | 1-9    |

| Figure 1-7  | Bus component with a transaction slave and two transaction master ports   | 1-10   |

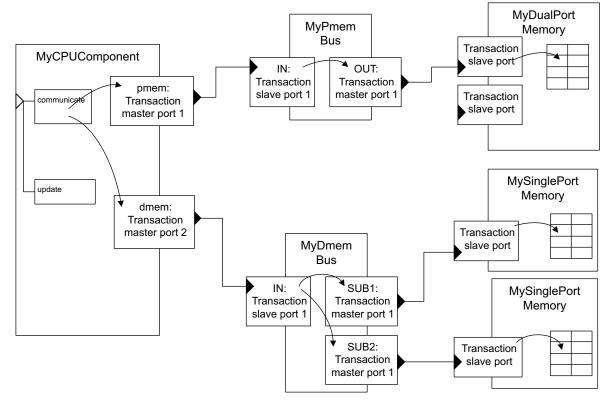

| Figure 1-8  | CPU component connected to memories through bus components                | 1-11   |

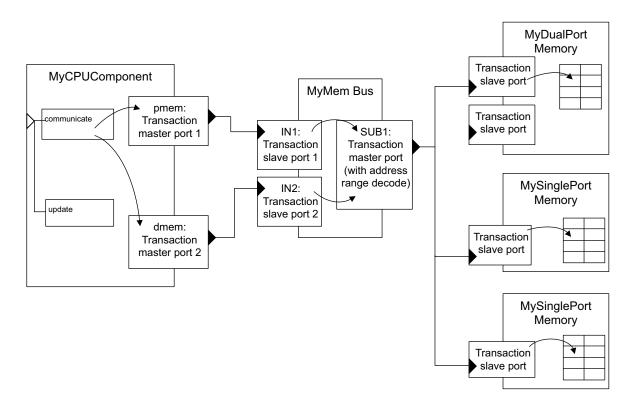

| Figure 1-9  | Single transaction master with multiple slave ports                       | 1-12   |

| Figure 1-10 | Synchronous communication example                                         | . 1-13 |

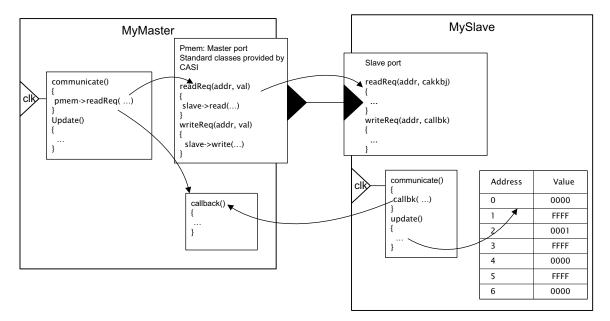

| Figure 1-11 | Asynchronous communication with callback example                          |        |

| Figure 1-12 | Asynchronous communication with shared memory example                     |        |

| Figure 1-13 | Communicate and update phases                                             | . 1-17 |

| Figure 1-14 | CASI schedule example for multiple clocks                                 | 1-20   |

| Figure 1-15 | Mixed synchronous and asynchronous updates                                | 1-20   |

| Figure 1-16 | Stages of simulation                                                      |        |

| Figure 1-17 | Block diagram of a system simulation                                      | 1-24   |

| Figure 1-18 | Files used for the top example                                            | 1-25   |

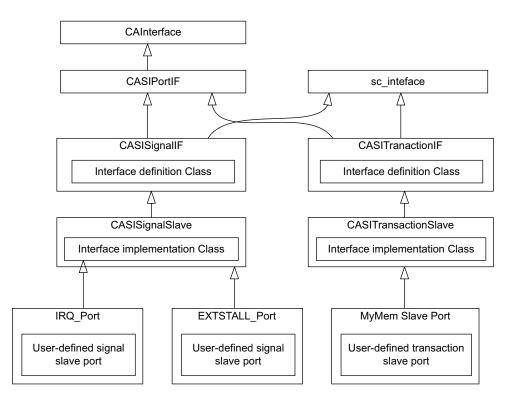

| Figure 1-19 | Class hierarchy showing user defined slave ports                          | . 1-31 |

| Figure 2-1  | Class hierarchy of the interface classes                                  | 2-4    |

| Figure 2-2  | Class hierarchy for the component and clock classes                       | 2-8    |

| Figure 2-3  | Asynchronous transactions using callbacks                                 |        |

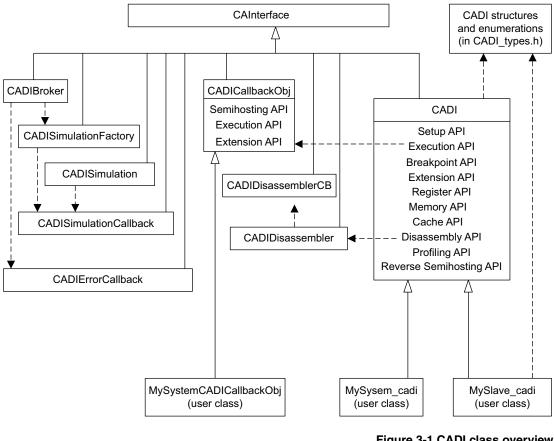

| Figure 3-1  | CADI class overview                                                       | 3-3    |

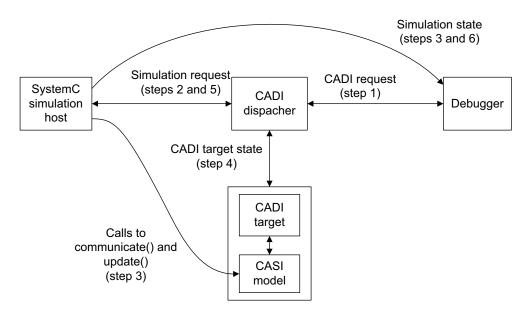

| Figure 3-2  | CADI and CASI interaction                                              | 3-5  |

|-------------|------------------------------------------------------------------------|------|

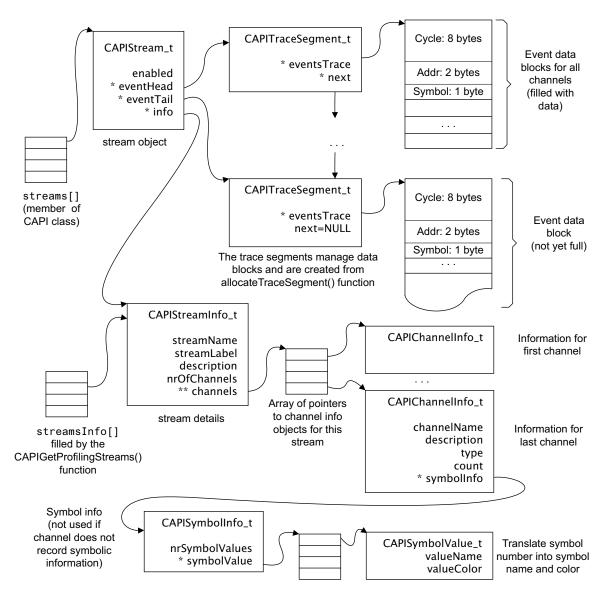

| Figure 4-1  | CAPI data structures and the profiling stream                          | 4-4  |

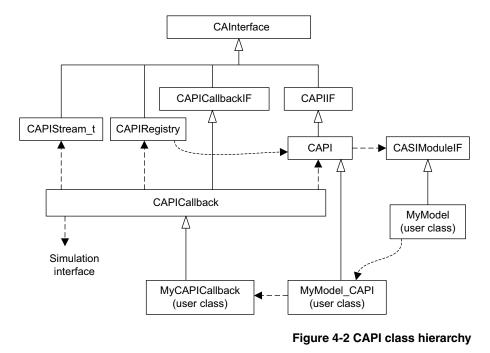

| Figure 4-2  | CAPI class hierarchy                                                   |      |

| Figure A-1  | Standard communicate and update phases                                 | A-2  |

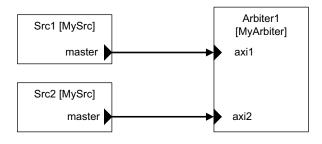

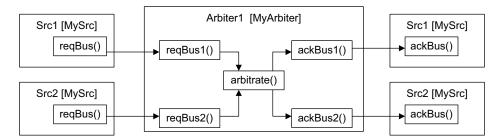

| Figure A-2  | System requiring ordered component communication                       | A-3  |

| Figure A-3  | Statically scheduled communicate and update phases                     | A-4  |

| Figure A-4  | Component connections                                                  | A-7  |

| Figure A-5  | Component function dependency graph                                    |      |

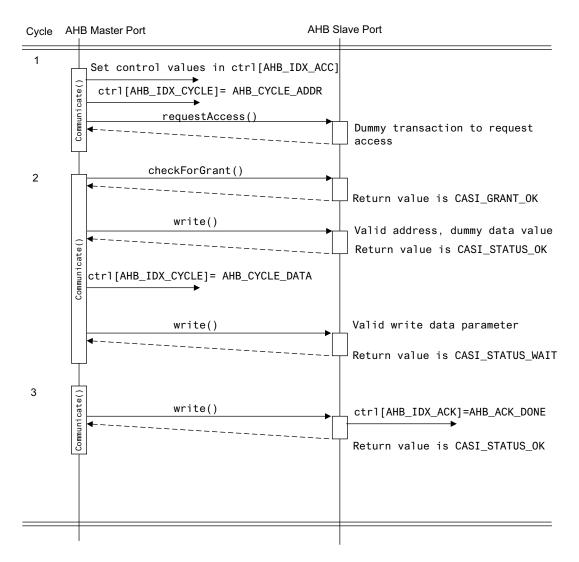

| Figure B-1  | AHB write                                                              | B-5  |

| Figure C-1  | Block diagram of master and slave components connected over an AXI bus | C-3  |

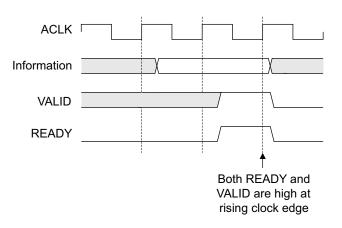

| Figure C-2  | READY and VALID handshake signals                                      | C-8  |

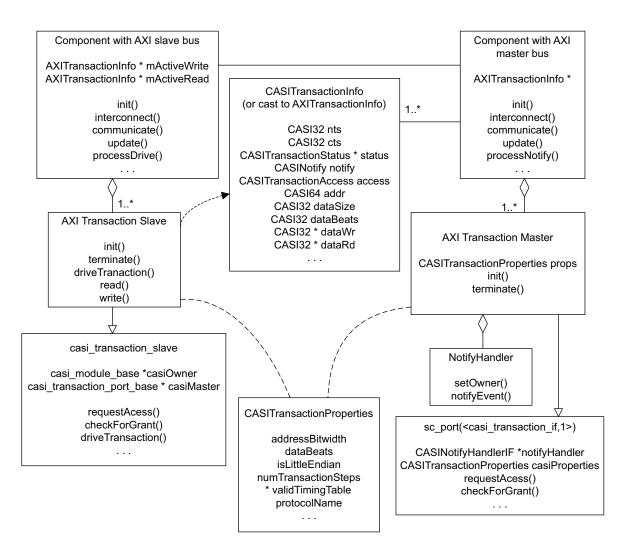

| Figure C-3  | Simplified AXI TLM block diagram                                       | C-9  |

| Figure C-4  | AXI classes C                                                          |      |

| Figure C-5  | Write with no wait states                                              | C-30 |

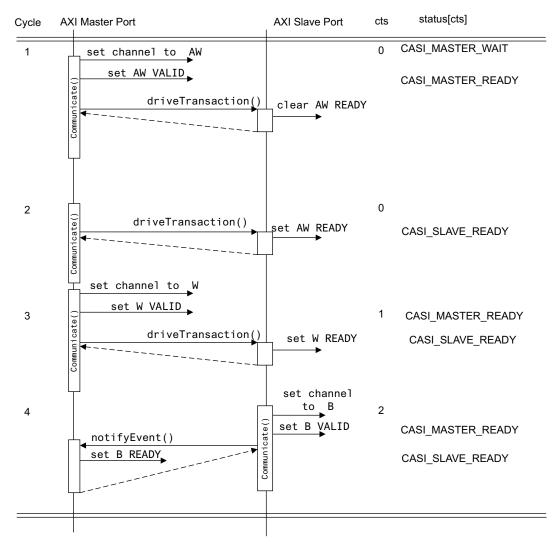

| Figure C-6  | Write with wait state in address channel 0                             | C-31 |

| Figure C-7  | Write with simultaneous AW and W, no wait states C                     | 2-32 |

| Figure C-8  | Write with consecutive AW and W, no wait states C                      | C-33 |

| Figure C-9  | Write with simultaneous AW and W and wait states 0                     | C-34 |

| Figure C-10 | Read with no wait states                                               | C-36 |

| Figure C-11 | Read with single wait state on address step                            | 2-38 |

| Figure C-12 | Read with wait states on both address and data steps C                 | C-40 |

| Figure C-13 | Bus write with ACI                                                     | C-43 |

# Preface

This preface introduces the *ARM RealView ESL API v2.0 Developer's Guide*. It contains the following sections:

- *About this document* on page x

- *Feedback* on page xiii.

## About this document

This document describes the class hierarchy and programming interfaces for version 1.1 of the RealView ESL APIs. It is intended for users writing components that comply with the SystemC and ESL API system interfaces.

#### Intended audience

This document has been written for experienced hardware and software developers to design systems or components.

Users must, however, be familiar with the basic concepts of SystemC (such as sc\_module and sc\_port) and basic concepts of C++ (such as classes and inheritance).

#### Organization

This document is organized into the following chapters:

#### **Chapter 1** Introduction

Read this chapter for an introduction to designing components.

#### Chapter 2 The Cycle Accurate Simulation Interface

This chapter describes the SystemC-based and ESL API simulation interfaces.

#### Chapter 3 The Cycle Accurate Debug Interface

This chapter describes the debug interfaces that enables access to memory values, register values, and code disassembly for each simulation cycle.

#### Chapter 4 The Cycle Accurate Profiling Interface

This chapter describes the profiling interfaces that enable collection of historical data about the memory, register, or port activity.

#### Chapter 5 The CASI Memory Map Interface

This chapter describes the memory map interfaces that enable the memory maps of the components in a system to be configured.

#### **Appendix A Static Scheduling of Communication Functions**

This appendix describes the static scheduling mechanism that is used to enable combinatorial support for communication functions.

#### Appendix B AMBA AHB TLM Specification for CASI

This appendix describes differences between the AHB transaction interface and the generic CASI TLM.

#### Appendix C AMBA AXI TLM Specification for CASI

This appendix describes differences between the AXI transaction interface and the generic CASI TLM.

## **Typographical conventions**

| The following typographical conventions are used in this book: |                                                                                                                                                 |  |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                | Highlights important notes, introduces special terminology, denotes internal cross-references, and citations.                                   |  |

|                                                                | Highlights interface elements, such as menu names. Denotes processor signal names. Also used for terms in descriptive lists, where appropriate. |  |

| •                                                              | Denotes text that can be entered at the keyboard, such as commands, file and program names, and source code.                                    |  |

|                                                                | Denotes a permitted abbreviation for a command or option. The<br>underlined text can be entered instead of the full command or<br>option name.  |  |

| •                                                              | Denotes arguments to commands and functions where the argument is to be replaced by a specific value.                                           |  |

| monospace bold                                                 | Denotes language keywords when used outside example code.                                                                                       |  |

The following typographical conventions are used in this book:

#### Terminology

The following table lists the SystemC terms that are replaced in this document by their corresponding ESL API terms:

| SystemC term | ESL API term | Description                                                                                                       |

|--------------|--------------|-------------------------------------------------------------------------------------------------------------------|

| module       | component    | The models for individual devices, for example, CPU core, memory, bus interface, and I/O.                         |

| port         | master port  | This is a port that generates transactions or signals.                                                            |

| channel      | slave port   | This responds to transactions or signals generated by a master port. SystemC channels are also know as sc_export. |

#### **Further reading**

This section lists related publications by ARM and other companies.

#### **ARM** publications

The following publications provide reference information about the ARM architecture:

- AMBA<sup>™</sup> Specification (ARM IHI 0011)

- ARM Architecture Reference Manual (ARM DDI 0100).

The following publications provide information about related ARM products:

- *RealView<sup>®</sup> SoC Designer Developer's Guide* (ARM DUI 0315)

- *RealView<sup>®</sup> SoC Designer User Guide* (ARM DUI 0316)

- *RealView<sup>®</sup> SoC Designer SystemC Linking Guide* (DUI0360)

- ARM RealView<sup>®</sup> Model Debugger User Guide (DUI0314)

#### **External publications**

The following publications provide additional information on simulation:

- *IEEE 1666™ SystemC Language Reference Manual*, (IEEE Standards Association)

- SPIRIT User Guide, Revision 1.2, SPIRIT Consortium.

# Feedback

ARM welcomes feedback both on the ESL API and on the documentation.

#### Feedback on this document

If you have any comments about this document, send email to errata@arm.com giving:

- the document title

- the document number

- the page number(s) to which your comments refer

- an explanation of your comments.

General suggestions for additions and improvements are also welcome.

Preface

# Chapter 1 Introduction

This chapter describes the main features of SystemC simulation with the classes defined by the *ESL Cycle Accurate Simulation Interfaces* (CASI), the related *Cycle Accurate Debug Interface* (CADI), and *Cycle Accurate Profiling Interface* (CAPI). It contains the following sections:

- Overview on page 1-2

- ESL API interface layers on page 1-3

- Theory of operation on page 1-5

- *Components* on page 1-6

- *Connections* on page 1-7

- Cycle based scheduling on page 1-17

- Simulation stages on page 1-21

- Organizing source files for components and systems on page 1-24

- *Overview of component creation* on page 1-26

- Working with component ports on page 1-28

- Checklist for components on page 1-36

- *CAInterface extensions* on page 1-41.

## 1.1 Overview

The RealView ESL API is a SystemC simulation interface for easy modeling and fast simulation of integrated systems-on-chip with multiple cores, peripherals, and memories. The ESL API consists of the following parts:

- The Cycle Accurate Simulation Interface (CASI)

- The Cycle Accurate Debug Interface (CADI)

- The Cycle Accurate Profiling Interface (CAPI)

CASI consists of a set of communication interfaces based on the SystemC language and supports both transaction level communication and cycle-based simulation modeling.

\_\_\_\_\_ Note \_\_\_\_\_

The CASI scheduler uses a cycle-based approach where the cycle is the finest granularity scheduling element. On each cycle the communicate() and update() functions are called for every clocked model.

Developing all components using the cycle-based interfaces improves the performance of the system.

The ESL API is a SystemC interface and therefore supports event-driven simulation. This document, however, focuses on using the CASI library with the faster cycle-based simulation.

## 1.2 ESL API interface layers

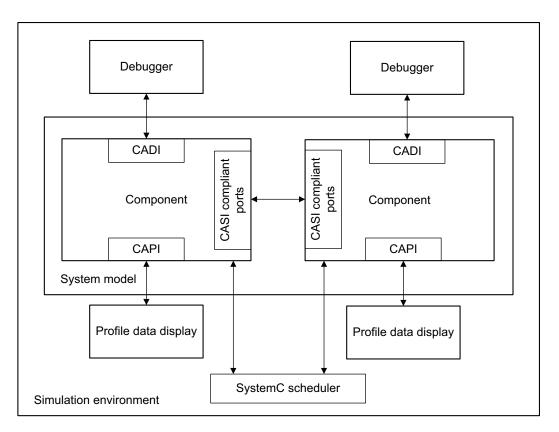

The ESL API provides three layers of interfaces (as shown in Figure 1-1 on page 1-4) and enable:

CASI *Cycle Accurate Simulation Interface* based on SystemC communication library.

The main features of the CASI API are:

- cycle based scheduling for high simulation speed

- direct communication

- optimized transaction based communication

- port-based interconnection

- hierarchical system structures

- event-driven simulation support for full SystemC compatibility

- maximum simulation performance while enabling a high level of accuracy (up to the level of full pin-accuracy) on a cycle-by-cycle basis.

— Note —

The CASIMMI (*Cycle Accurate Simulation Interface - Memory Map Interface*) is used to define and use memory maps for bus master components. See Chapter 5 *The CASI Memory Map Interface* for details on using memory maps.

**CADI** *Cycle Accurate Debug Interface* enables reading and writing memory and register values and also provides the interface to external debuggers.

**CAPI** *Cycle Accurate Profiling Interface* enables collecting historical data from a component and displaying the results in various formats.

CADI and CAPI are additional interfaces not covered by SystemC. Implementing the CADI and CAPI interfaces is optional, but it is recommended for all user-defined components.

#### Figure 1-1 Interface layers

\_\_\_\_\_Note \_\_\_\_\_

The ESL API supports extending the interfaces while maintaining binary compatibility. See *CAInterface extensions* on page 1-41.

# 1.3 Theory of operation

A system consists of components and connections between components. A component might consist of sub-components connected together in a hierarchy.

A simulation of a CASI-compatible system is performed by:

- loading dynamic libraries of components (either standard library components or components that you have created yourself)

- creating instances of the components (for example by using factory function calls)

- connecting the components through standard port interfaces

- connecting the resulting model to a simulation controller that contains the timing and scheduler functionality

- the simulation scheduler clocks the cycle-based models in a lock-step fashion.

For every scheduler clock triggered by the simulation controller, the controller calls the clock interface function of each connected component. All clocked components are completely synchronized with each other.

The clock function of a component can call functions in other interfaces (such as memory interfaces or signal interfaces) to implement communications.

The cycle-based clock generators rely on the OSCI scheduler (which is itself event driven) to generate a cycle-based clock to drive all of the cycle-based components.

The internal behavior of a component is not constrained by the ESL API. It can be anything the designer wishes as long as the interface functions behave as expected by the other components. Correctly implemented system interfaces do not guarantee that the component behaves correctly in a system model. The system interfaces only standardize the way that components communicate with each other.

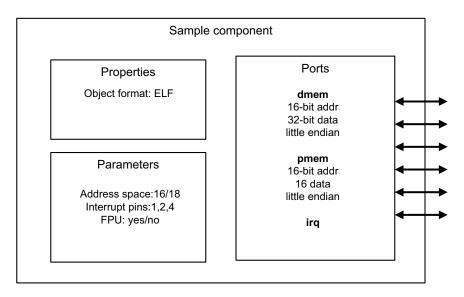

# 1.4 Components

The software duplicates the behavior of the hardware elements and provide ports that can be used for connection to other components.

Each component has properties that determine:

- which connections are allowed

- which type of object files are expected for loading

- whether debug front ends are supported.

Component parameters can be set either at system design time or at simulation time (depending on the type of parameter).

\_\_\_\_\_ Note \_\_\_\_\_

Because parameters are set before the components are connected, components can have:

- configurable size for generic memories

- configurable behavior for peripherals.

Figure 1-2 A sample component with properties, parameters, and ports

# 1.5 Connections

Components provide ports that enable them to be connected together.

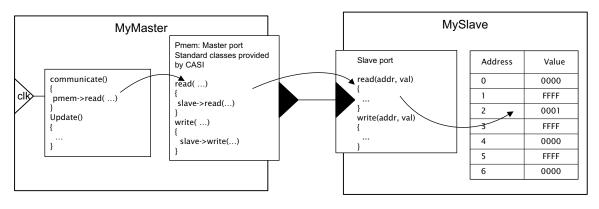

Unlike many other system simulation solutions, the ESL API uses direct communication. One component accesses the shared resources of another component by directly calling a method provided by the owner of the shared resource.

CASI provides two different types of connection:

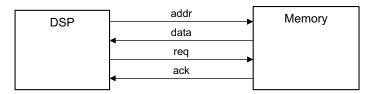

#### Signal based

The signal-based interface is very close to hardware simulators in that it simulates every signal independently.

#### Figure 1-3 Signal-based communication

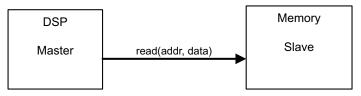

#### **Transaction based**

The transaction-based interface encapsulates a group of signals into one data structure that is manipulated read or write transactions.

Rather than distinguishing input and output ports, the CASI API distinguishes master and slave ports. A master port initiates the transfer and a slave-port responds to the transfer.

In Figure 1-3:

- The DSP component is the signal master for the addr and req signal ports.

- The Memory component is the signal slave for the addr and req signal ports.

- The DSP component is the signal slave for the data and ack signal ports.

- The Memory component is the signal master for the data and ack signal ports.

- Each signal has its own interface function that transmits the signal state.

In Figure 1-4 on page 1-7:

- The component DSP is the transaction master.

- The component Memory is the transaction slave.

- There is only one interface function, read(), that uses data structures to combine all signals into a parameter that can be passed with the single function call.

The data is returned by read() in either:

- the return value of the function

- modified shared memory

- modified memory that was indicated by a passed pointer.

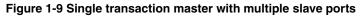

#### 1.5.1 Components with slave ports

A component with one or more slave ports enables other components to access its shared resources. This is, for example, used in memories that provide a transaction slave interface with read() and write() access methods.

#### Figure 1-5 Dual ported memory component with two transaction slave ports

Figure 1-5 shows that the transaction slave ports provide access methods for the internal memory implementation of the component.

#### 1.5.2 Components with master ports

Components with master ports can access connected slaves through well-defined access methods:

- the transaction master interface uses read() and write() methods

- the signal master interface uses driveSignal() and readSignal().

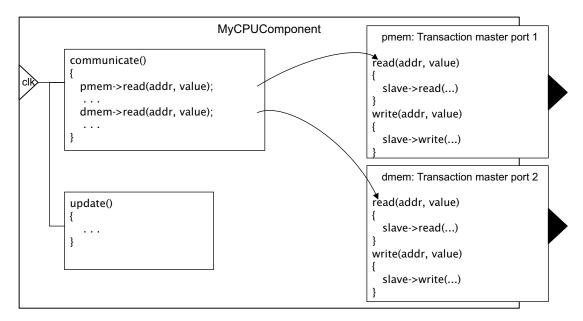

#### Figure 1-6 CPU component with separate transaction ports for data and program memory

Figure 1-6 shows a clocked CPU component with a Harvard architecture that has separate ports for data and program memory. In every clock cycle the component can read or write from memory by calling the appropriate access functions in the master ports. The master port then redirects these calls to the connected components.

#### 1.5.3 Components with master and slave ports

Components can have an unlimited numbers of ports.

It is possible to pass through access calls from slave to master ports as shown in Figure 1-7. This might be required for the implementation of bus type components.

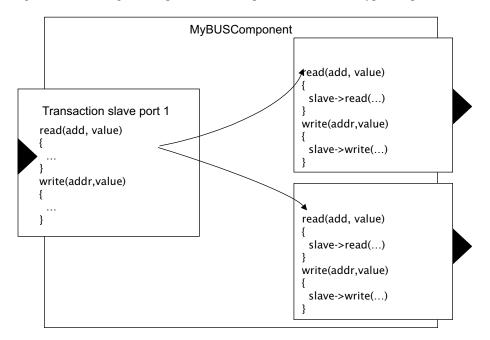

#### Figure 1-7 Bus component with a transaction slave and two transaction master ports

The bus component shown in Figure 1-7 redirects read() and write() calls to different master ports. Redirection might be used, for example, for sub-range decoding.

Figure 1-8 shows a system consisting of multiple components.

#### Figure 1-8 CPU component connected to memories through bus components

The ESL API interfaces enable the user to hide the implementation from the communication. When the CPU components call the read methods in its master ports, it does not know whether it is talking to a bus component or to a memory component directly. This simplifies reconfiguration and architecture exploration.

A single transaction master can drive multiple slaves as shown in Figure 1-9 on page 1-12. The master port, however, must include address decoding code to direct the transaction to the correct slave port.

#### 1.5.4 Synchronous and asynchronous communication

The CASI signal interfaces always use synchronous communication that is accomplished by a single call to driveSignal(). The signal value is passed as a parameter. If a complex interconnection such as a bus is implemented with signals, there must be multiple distinct calls by the components to the driveSignal() functions of each individual signal.

The CASI transaction interface can perform a read or write in a single transaction call. Also, the CASI transaction interfaces are not restricted to single reads and writes. The interface supports protocols that perform burst or block reads of multiple memory locations through a single transaction. For a given communication protocol, AHB or AXI for example, the details are user-defined and must be documented as part of the protocol. The communication schemes that can be used for a transaction model are user defined:

- synchronous

- asynchronous

- asynchronous with shared memory.

#### Synchronous transaction communication

The read() and write() functions enable synchronous access between different models by specifying the control information in the fields:

| addr    | is the address for the read or write    |

|---------|-----------------------------------------|

| value   | is the value read or to be written      |

| control | is control field for the read or write. |

The read() and write() functions are expected to return in the same cycle that they were initiated. The return value indicates the status of the transaction. If they return CASI\_STATUS\_OK, the transaction has finished successfully.

The read() and write() functions can implement multi-cycled transactions. If in the first cycle they return, for example, CASI\_STATUS\_WAIT, then the initiating model calls the read() and write() function again in subsequent cycles, until it receives the CASI\_STATUS\_0K representing the end of this transaction.

The readDbg() and writeDbg() functions provide debug accesses and enable debuggers to read the desired information without advancing the simulation.

#### Figure 1-10 Synchronous communication example

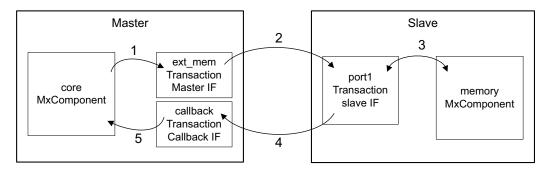

#### Asynchronous transaction communication with callback

The asynchronous readReq() and writeReq() functions enable a communication model where the initiator master model provides a callback function pointer to the slave model. When the slave model is ready to serve the transaction, it calls the callback function and notifies the master that the data is ready.

Figure 1-11 Asynchronous communication with callback example

#### Asynchronous transaction communication with shared memory

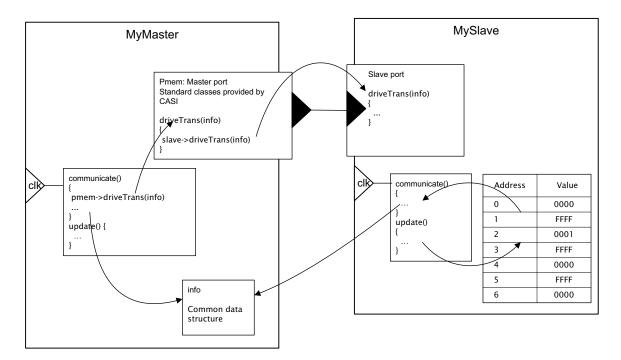

The shared-memory asynchronous functions provide a communication model where the initiating master model calls driveTransaction() providing to the slave a shared-memory data structure. This data structure is used throughout the life of the transaction to communicate the information between the master and the slave models. After the first driveTransaction() function call, no other function calls are required through the transaction, unless a cancelTransaction() is called to cancel the respective transaction. The shared data structure is stored in CASITransactionInfo.

An optional notification callback from a slave to the connected master can be implemented through a CASINotifyHandlerIF object. The notifyEvent() function can be called by the slave to inform the master that the contents of the transaction info data structure has changed. This enables the master to react to the changes in the same cycle.

#### The CASI implementation of the AHB protocol

CASI provides a general framework for model inter-communication, but the details of the communication protocol must be customized to match the actual protocol used. This is done by mapping the protocol fields to the CASI access functions parameters.

For instance, an AHB protocol implemented using the CASI synchronous model assigns AHB-related semantics to the parameters of the read/write functions of the casi\_transaction\_if interface. A example mapping is given in *Example AHB to CASI mapping* on page 1-16.

For details of the AHB protocol implementation for CASI, see the AHB CASI model documentation. Table 1-1 provides some guidance but must not be used as a reference for the AHB transactions description.

| Table 1-1 | Example | AHB to | CASI | mapping |

|-----------|---------|--------|------|---------|

| 14010 1 1 | =nampio |        |      |         |

| Parameter | Use           | Example values                      |

|-----------|---------------|-------------------------------------|

| Addr      | Address       | 0x1A0000000000000 (64-bit unsigned) |

| Value     | Data          | 0xFFFF0001 (32-bit unsigned)        |

| ctr][0]   | Transfer type | BYTE, HWORD, DWORD                  |

| ctr][1]   | Phase         | ADDR, DATA                          |

| ctrl[2]   | ACC           | HBURST, HSIZE, HTRANS               |

| ctrl[3]   | Acknowledge   | DONE, WAIT, ABORT                   |

|           |               |                                     |

A typical communication sequence is listed in Table 1-2.

| Cycle  | Phase | Bus          | Peripheral                                                                                                                                                                                            |

|--------|-------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | ADDR  | port->read() | AHB_ch::read(addr,val,ctrl)                                                                                                                                                                           |

|        |       |              | <pre> if(ctr][1] == ADDR_PHASE) {     //decode read/write type (burst/)     return OK; }</pre>                                                                                                        |

| 1 to N | DATA  | port->read() | AHB_ch::read(addr,val,ctrl)                                                                                                                                                                           |

|        |       |              | <pre>if(ctrl[1] == DATA_PHASE) {     if(waitCount &lt; DELAY)     {         ctrl[3] = WAIT;     }     else     {         val = getData(addr,ctrl);         ctrl[3] = DONE;     }     return OK;</pre> |

|        |       |              | }                                                                                                                                                                                                     |

# 1.6 Cycle based scheduling

Both cycle-based and event-driven simulations are supported:

- cycle-based components are executed on the edges of the clock

- event-driven components are executed based on their sensitivity lists and the events present in the system.

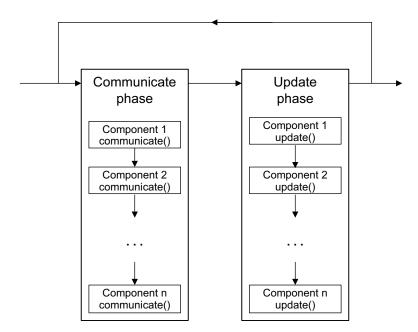

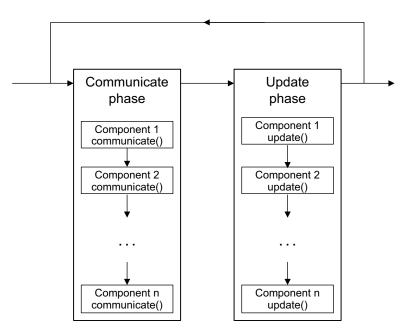

The execution of all cycle-based models happens in a synchronous cycle-based manner. In most cases, a simulation cycle is equivalent to a hardware clock cycle. Each simulation cycle is divided into communicate and update phases. Each clocked component is therefore called twice per cycle as shown in Figure 1-13.

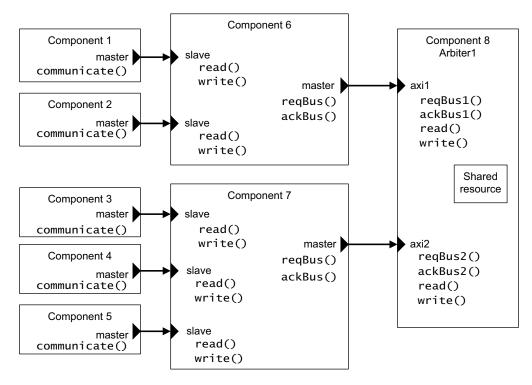

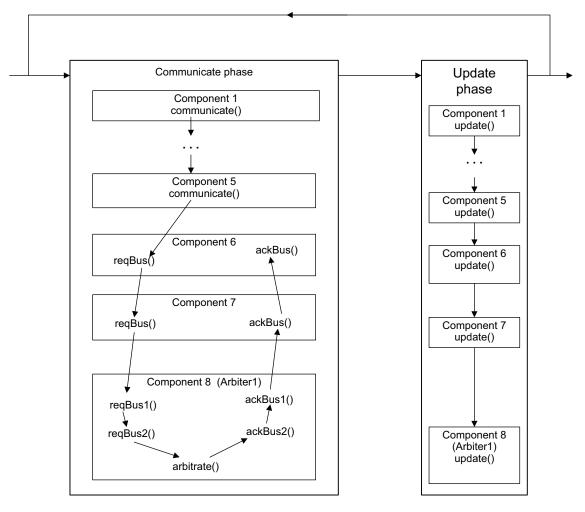

The order in which the component communicate() functions are called cannot be specified by the standard registerClockSlave() function. Some systems, however, require that communication functions are called in a specific order to, for example, control a bus request and acknowledge sequence within the same cycle. For more information on specifying the order of communication functions, see Appendix A *Static Scheduling of Communication Functions*.

- Note

During the communicate phase the components interact and during the update phase shared resources are modified:

#### **Communicate phase**

- perform all inter-component communication

- do not modify shared resources.

#### Update phase

- no communication between components

- update shared resources

- perform writes that were requested to internal components.

The simulation framework can enforce that the interface functions for communication are only called during the communicate stage. The simulation framework cannot, however, guarantee that the writes to shared resources are actually deferred to the update phase.

### \_\_\_\_\_Note \_\_\_\_\_

The communicate and update model is typically used as described in this section and is the recommended way of implementing new components. There are, however, some special cases that do not follow the general model. The communicate phase is called only for the components that are clocked and register themselves to use communicate. It is possible, though not typical, for a component to register itself as a clocked component, but:

- only use update

- only use communicate

- ignore most phases and react, for example, to every fifth clock cycle.

#### 1.6.1 Clocking the simulation

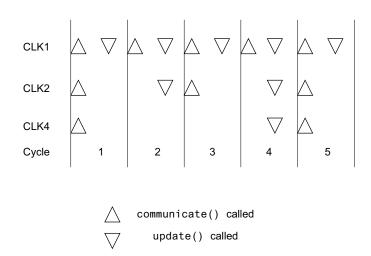

The CASI scheduler supports multiple clocks operating with different frequency. There exists a master clock that defines the fastest clocking granularity. All other clocks are created by dividing the master clock frequency with an integer number. If integer clocks are used, the frequency of the master clock must be the least common multiplier of the frequencies of the actual design clocks.

A single CASI model can have different parts clocked by different clocks. For example, a bus can receive data at one clock frequency and deliver it at a different clock frequency. Each differently clocked part must implement the casi\_clock\_slave\_port\_base interface and provide an appropriate implementation for the communicate() and update() member functions. At the implementation level, the

casi\_model\_base interface does not explicitly specify any communicate/update mechanism. Rather clocked models must create, or inherit from, one or more clock slaves that receive the necessary communicate/update calls.

As a general simulation strategy, the update calls must update the model state based on the most recently communicated data:

- For systems with single clocks, this strategy easily ensured by imposing a temporal ordering between the executions of communicate calls and update calls.

- If multiple clocks are present, ensure the ordering of communicate and update calls by executing the communicate calls at the beginning of a given cycle and the update calls in the last moment before the next cycle begins. This rule is applied for all clocks.

#### **Clocking implementation**

A master clock routine sits at the core of a CASI scheduler implementation and drives the simulation by executing a loop. In each iteration:

- for clocks running at full speed, a communicate phase is executed and that is followed by an update phase.

- For a clock with a frequency n times slower than the master clock:

- The communicate phase is executed during the master clock communication phase in a master clock iteration for which (i mod n) = 0.

- The update phase is executed during the master clock update phase in a master clock iteration for which (i mod n) = (n 1).

A 4 cycle window into the schedule is shown in Figure 1-14 on page 1-20 for a system has the following clocks:

- CLK1 is the master clock

- CLK2 is a clock with half the frequency of the master clock

- CLK4 is a clock with a quarter of the frequency of the master clock.

#### Figure 1-14 CASI schedule example for multiple clocks

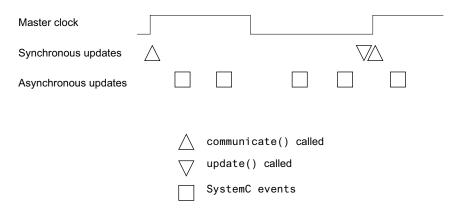

If a CASI scheduler is operated together with a SystemC scheduler, it is important to preserve the communicate/update ordering with respect to SystemC events. Usually this means that the SystemC events relevant for one CASI simulation cycle must occur between the communicate and update phases of the CASI scheduler. The CASI main clock must be appropriately setup to ensure this requirement. This is typically done as shown in Figure 1-15 by:

- 1. the master clock communicate phase occurring on the positive clock edge of an equivalent SystemC clock

- 2. the master clock update phase occurring just before the positive edge of the next cycle.

Figure 1-15 Mixed synchronous and asynchronous updates

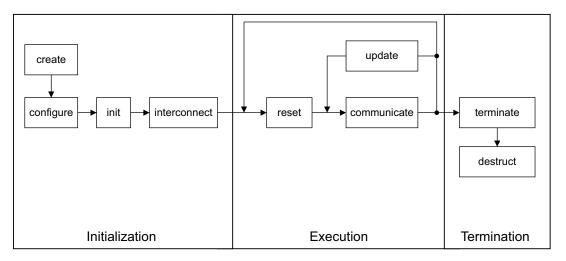

# 1.7 Simulation stages

The simulation of a system is divided into multiple stages that are grouped as initialization, execution, and termination. Figure 1-16 shows the simulation stages and order of execution.

#### Figure 1-16 Stages of simulation

The simulation engine is the only instance that calls the functions that represent these stages. The components can request a reset or a terminate, but it is always the simulation engine that actually makes the call to the top-level component. The different stages are:

#### The create stage

This stage is used to load and instantiate the components. In the C++ implementation this functionality is contained in the constructor of the components:

- If a model causes a segmentation fault in its constructor, the simulation fails on startup.

- If a model allocates large amounts of memory in its constructor, this memory is allocated while creating the design as well. ARM recommends allocating any large amounts of data only in the init() stage of the simulation.

#### The configure stage

•

This stage is used to configure the components by setting parameters. This stage is implemented by the default behavior of the components and is normally not overridden by the individual models.

#### The init stage

This stage is used to initialize the model and allocate memory for its data members if necessary. Because the init stage is positioned after the configure stage, it is possible to initialize components conditionally, the size of a memory for example, based on a parameter.

ARM recommends that model initialization is done in this stage to simplify code in the model constructor. Whatever is allocated in init() must be deleted in terminate().

#### The interconnect stage

In this stage the connections between the components are established. The connections are established once at initialization time only. During execution time, the interconnections cannot be modified. This stage is implemented by the default behavior of the components and is normally not overridden by the individual models.

#### The reset stage

The main purpose of the reset stage is to bring the components into a well-defined state before the actual simulation is started:

- During a soft reset, the models are expected to reset their state. This can be done repeatedly.

- A hard reset is only executed on startup.

During a hard reset the components can, if applicable, load their object files. A core model would, for example, reload an axf image.

#### The communicate and update stages

These two stages represent the cycle-by-cycle behavior of the system. These stages are repeatedly executed until a reset or termination is requested by one of the components or by the user.

#### The terminate stage

This stage can be used for cleanup purposes. It is the counterpart to init. Terminate is called before the component instance is deleted. This stage is reached if:

- one of the components requests termination

- the specified simulation cycle count has been reached

- the simulation is terminated by an external signal.

#### The destructor stage

The destructor is called when the component is deleted after termination.

— Note ——

An object that was created in the init stage must be deleted in the destructor instead of in the terminate stage.

The following virtual functions are defined in CASIModule.h for use by the individual system components to support the simulation phases:

- CASIModule()

- configure()

- init()

- interconnect()

- reset()

- communicate()

- update()

- terminate()

- ~CASImodule().

Each component must re-implement (overload) each of these functions (except for interconnect() where the base implementation might be sufficient).

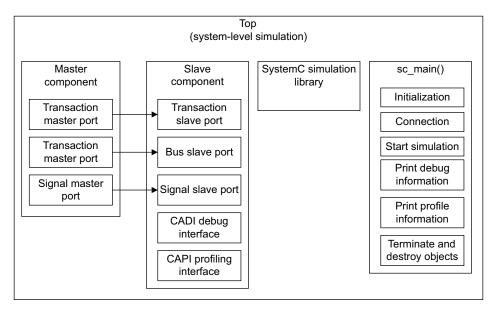

# **1.8** Organizing source files for components and systems

A SystemC example typically has almost all of the code (except for the standard library include files) in a single source file. For ESL API systems, however, there are typically multiple source files where each file provides a specific functionality.

## Figure 1-17 Block diagram of a system simulation

Figure 1-18 Files used for the top example

# **1.9** Overview of component creation

This section describes how to manually create your own components and make them available in a simulation system. The main steps are:

- creating the code with a text editor

- creating a project file for the component

- compiling and linking the code in the project

- editing any configuration options that are necessary to use your project in your simulation environment.

To create a component, implement the CASIModule interface and behavior and define the component resources. Components must define any ports that are required for communication with other components in the system.

Systems are hierarchical representations of hardware systems. A system can be a single component or consist of a hierarchical structure of subsystems and components.

#### 1.9.1 Defining the component class

The component class must inherit from CASIModule. This module provides the necessary base functionality for components. Example 1-1 shows how the component class is entered explicitly:

#### Example 1-1 MyModel class

```

class MyModel : public CASIModule

{

public:

MyModel(CASIModuleIF* parent, const std::string &name);

string getName() { return "MyModel"; }

virtual void interconnect();

virtual void init();

virtual void terminate();

// Interface functions for clocked components

virtual void communicate();

virtual void update();

};

```

Alternatively, the component class can be declared using the CASIModule macro as shown in Example 1-2:

CASIModule(MyModel)

{

//class members

};

# 1.10 Working with component ports

The CASI API distinguishes between master and slave ports:

- master ports are used to access connected slaves

- slave ports provide functions that access shared resources inside the component.

Ports can be created by instantiating the appropriate port classes.

- Master ports are instances of the sc\_port class in SystemC using the transaction or slave interfaces.

- Slave ports are channels implementing the transaction or slave interfaces.

Example 1-3 shows the creation of master and slave ports:

## Example 1-3 Creating two ports

```

sc_port<eslapi::casi_transaction_if, 1>* dram_port =

new sc_port<eslapi::casi_transaction_if> (this, "dram");

registerPort(dram_port, "dram_port");

isrc_SSlave = new isrc_SS( this );

```

registerPort( isrc\_SSlave, "irq\_port" );

\_\_\_\_\_ Note \_\_\_\_\_

The code in Example 1-3 creates one transaction master port and a signal slave port for IRQ:

- The transaction master port class is a generic one that is predefined in the ESL API and uses the casi\_transaction\_if interface.

- The signal slave port is a custom class derived from casi\_signal\_slave specifically for the purpose of controlling the IRQ signal. For Example 1-3, a separate file (for this example, isrc\_SS.cpp) contains the code that implements a slave port and the casi\_signal\_if interface.

#### 1.10.1 Using master ports

The following master ports can be created using the sc\_port SystemC class:

#### Table 1-3 sc\_port classes

| Port type                | sc_port definition                                               |

|--------------------------|------------------------------------------------------------------|

| Signal master ports      | <pre>sc_port<casisignalif, 1=""></casisignalif,></pre>           |

| Transaction master ports | <pre>sc_port<casitransactionif, 1=""></casitransactionif,></pre> |

| Bus master ports         | <pre>sc_port<casitransactionif, 0=""></casitransactionif,></pre> |

Each created master port can communicate with the slave port that is connected to it.

A pointer to any created master port can be obtained by using the findPort() function. For performance reasons, however, it is recommended that you store a pointer for each master point immediately upon creation.

Example 1-4 shows the accessing of memory through a transaction master port.

#### Example 1-4 Reading from a port

uint64\_t addr = 0xFF00; uint32\_t value[1]; uint32\_t ctrl = 0; dram\_port->read(addr, value, &ctrl); cout << "Value " << value << " has been read from address " << addr << endl;</pre>

For performance reasons, the read function of the master port does not check whether a slave port has been connected. This must be done once in the interconnect stage only. Therefore master ports provide the getSlaves() function as shown in Example 1-5:

#### Example 1-5 getSlaves function

if (dram\_port->getSlaves() == NULL)

cout << "Port not connected !" << endl;</pre>

The list of connected slave ports returned by the function getSlaves() must be non-NULL. If NULL is returned, the port has not been successfully connected.

#### **AHB** master ports

AHB transaction master ports use the dedicated CASIAHBMasterPort class to manage the AMBA protocol. See Appendix B *AMBA AHB TLM Specification for CASI*. the AHB documentation, and the example master and slave ports.

#### **AXI** master ports

AXI transaction master ports use the dedicated CASIAXIMasterPort class to manage the AMBA 3 AXI protocol. See Appendix C *AMBA AXI TLM Specification for CASI*, the AXI package documentation for details of the AXI protocol, and the example master and slave ports.

#### 1.10.2 Using slave ports

Slave ports define access methods to shared resources in a component. Because these shared resources differ from case to case, there are no predefined port classes available for slave ports. Therefore, users must implement their own custom slave classes, derived from either CASISignalSlave or CASITransactionSlave.

\_\_\_\_\_ Note \_\_\_\_\_

AMBA AXI, AHB, and APB transaction slave ports derive from intermediate classes that are themselves derived from CASITransactionIF.

Slave ports correspond to SystemC channels and implement the transaction or signal interfaces.

#### Figure 1-19 Class hierarchy showing user defined slave ports

The shared resources are typically encapsulated in the component class, but the access methods are defined in the port class (see Example 1-6). There are various ways that the port class can be given access to the resources. The most efficient way is to use friend class declarations This enables the port classes to access shared resources in the component without the overhead of function calls and is, therefore, the recommended way of shared resource access.

#### Example 1-6 MyMemSlavePort class

```

class MyMemSlavePort : public CASITransactionSlave

{

MyModel* owner;

public:

MyMemSlavePort(MyModel* _owner) : CASITransactionSlave("MyMemSlavePort")

{ owner = _owner; }

CASIStatus read(uint64_t addr, uint32_t *dataP, uint32_t* ctrl=0);

CASIStatus write(uint64_t addr, uint32_t *dataP, uint32_t* ctrl=0);

};

```

```

class MyModel : public CASIModule

{

friend class MyMemSlavePort;

friend class IRQ_Port;

friend class EXTSTALL_Port;

public:

...

};

```

Slave ports provide functions that can be accessed from master ports. These functions (typically virtual functions) must be overridden so that the appropriate function in the slave is executed when a master initiates a transaction.

#### **Transaction Slave Ports**

For transaction slave ports, the read and write functions must be overridden as shown in Example 1-7:

#### Example 1-7 Overriding read and write

```

CASIStatus MyMemSlavePort::read(uint64_t addr, uint32_t *value, uint32_t* ctrl)

{

value[0] = owner->getMyMem(addr);

return CASI_STATUS_OK;

}

CASIStatus MyMemSlavePort::write(uint64_t addr, uint32_t *value, uint32_t* ctrl)

{

if (addr <= 0x3FF) {/* restricted access */

owner->setMyMem(addr, value[0]);

return CASI_STATUS_OK;

}

else {

/* no access above 1k */

return CASI_STATUS_NOACCESS;

}

}

```

Example 1-7 shows the definition of the transaction slave port read and write behavior. In this example, write access is restricted to the lower 1024 words.

## **Signal Slave Ports**

The handling of signal slave ports is equivalent to the transaction slave ports, except that here the access functions driveSignal() and readSignal() must be implemented as shown in Example 1-8.

#### Example 1-8 Implementing driveSignal and readSignal

```

class IRQ_Port : public CASISignalSlave

{

MyModel* owner;

public:

IRQ_Port(MyModel* _owner) { owner = _owner };

void driveSignal(uint32_t value, uint32_t* extValue);

uint32_t readSignal();

};

IRQ_Port::driveSignal(uint32_t value, uint32_t*) {

owner->interrupt = value;

};

uint32_t IRQ_Port::readSignal() {

return owner->interrupt;

};

```

#### 1.10.3 Defining the behavior of clocked components

Non-clocked components are passive and are only triggered by transactions from the outside.

Clocked components, however, can also have behavior that is independent of their interaction with other components. This behavior is defined in the communicate and update phases as shown in Example 1-9:

#### Example 1-9 Communicate and update phases of component

```

MyModel::communicate(){

if (myModel.readDRAM == true)

dram_port->read(addr, value, ctrl);

}

MyModel::update() {

if (interrupt == true) myCore.injectInterrupt();

myModel.execute();

}

```

Example 1-9 on page 1-33 shows the implementation of communicate and update behavior and assumes that MyModel represents a core model that has a private data member called myCore that implements the behavior for the model.

The communicate behavior shows a read access from the dram port that is used if the readDRAM flag has been set in the model.

The update behavior injects an interrupt if the interrupt flag has been set externally (over the irq port) and then executes one cycle in the model.

## 1.10.4 Registering the clock port

A component that implements a clock slave interface must register this interface as the clk-in port in the constructor to be recognized as a clocked component.

registerPort(dynamic\_cast<CASIClockSlaveIF\*>(this), "clk-in");

If the clock is not registered, it might not be visible in the simulation environment.

## 1.10.5 Connecting a component to the clock

To connect a component to the clock, call the casi\_clocked() function in the component constructor:

casi\_clocked();

Alternatively, the CASI\_CLOCKED macro can be used in the constructor:

CASI\_CLOCKED();

—— Note ———

– Note –

Instead of calling casi\_clocked() in the constructor, you can call registerClockSlave() in the interconnect phase. See *The interconnect() function* on page 1-38.

## 1.10.6 Defining a factory class for the system

This class is not required if you are simulating a standalone system using the standard SystemC and ESL API environment. It might be useful, however, in simulation environments that permit dynamic component creation and connection.

In addition to the component itself, a factory class is available that can be used by the third-party simulation systems to access the model.

The factory class must inherit from CASIFactory. The only functions that must be defined are:

- the constructor, this is named MyModelFactory() for the class in Example 1-10

- the createInstance() function.

Example 1-10 Factory class

```

class MyModelFactory : public CASIFactory

{

public:

MyModelFactory(const std::string &name);

~MyModelFactory();

CASIModuleIF * createInstance(CASIModuleIF * parent, const std::string &id);

};

```

The constructor simply calls the default constructor, passing the name of the component as a parameter. It is important that this name is equivalent to the name that is returned by the getName() function of the corresponding component. ARM recommends declaring the constant that contains the name of the model as a string:

```

#define MODEL_NAME "My_Model";

MyModelFactory::MyModelFactory() : CASIFactory (MODEL_NAME) {}

```

#### 1.10.7 The factory member functions

The constructor implementing the system must call the parent's constructor and pass the name of the system as a parameter:

MyModelFactory() : CASIFactory("MyModel") {}

Use the createInstance() function to create an instance of the component by passing a pointer to the parent component as shown in Example 1-11:

#### Example 1-11 Creating an instance of a component

# 1.11 Checklist for components

The implementation of any component must follow the rules listed in this section.

Use this list as a guideline to develop a new components and verify the correctness of the implementation.

## 1.11.1 The component class

This section contains the check list for the component class.

#### Defining your component class

— Note ——

1. Derive your component class from CASIModule:

class MyModel : public CASIModule

CASIModule has the public virtual function ObtainInterface(). All components deriving from CASIModule implement the CAInterface class. with at least revision 0 for the interface named CAInterface. The CAInterface class enables extending the ESL API interfaces with custom interfaces. The default implementation is sufficient if your component only uses the standard ESL API interfaces.

- Declare all slave ports as friend: friend class MySlavePort;

- Define a constant for the component name. This constant is used in the getName() function and in the component factory:

#define MODEL\_NAME "DLX\_Core"

## The component constructor

- 1. Create all ports in the component constructor:

- a. if you are creating a slave port, register it in the port list: registerPort(new MySlavePort(...), "irq");

- b. if you are creating a master port, keep a pointer to it for fast access: ext\_mem = createPort(CASI\_TRANSACTION\_MASTER, "ext\_mem"); then register it in the port list: registerPort(ext\_mem, "ext\_mem");

- c. register the clock slave port if the component is clocked: registerPort(dynamic\_cast<CASIClockSlaveIF\*>(this), "clk\_in");

If the component class is clocked, call casi\_clocked() function: casi\_clocked();

\_\_\_\_\_ Note \_\_\_\_\_

You can register the clock in the interconnect stage instead of in the constructor. See *The interconnect() function* on page 1-38.

3. Define all parameters in the component constructor.

# The component destructor

1. Delete only what has been created in the constructor. This includes the created ports.

# The getName() function

- 1. Return the model-name defined in the component header file.

- 2. Ensure that this name is equivalent to the name used in the component factory's constructor.

# The getProperty() function

— Note ———

This function must be implemented for all models.

- 1. For CASI\_PROP\_COMPONENT\_TYPE, use the CASIComponentTypes array to return the type of your component.

- 2. For CASI\_PROP\_COMPONENT\_VERSION, return the version number of your component.

- 3. For CASI\_PROP\_DESCRIPTION, return a brief description of your component and its key features.

- 4. If your component has its own loader, use CASI\_PROP\_LOADFILE\_EXTENSION identify the types of files to look for.

# The setParameter() function

- 1. Implement this function if your component is configurable.

- 2. Distinguish initialization time parameters and runtime parameters.

- 3. If possible, do not access resources directly but instead set flags to control resource allocation.

- 4. Do not access resources that are allocated during init().

— Note ——

setParameter() is called before the init() function.

- 5. For initialization time parameters, defer the parameter evaluation to the init stage.

- 6. Call CASIModule::setParameter() to ensure that the parameter changes are registered in the parameter list.

## The configure() function

- 1. Implement this function only if your component has subcomponents.

- 2. Do not define this function with an empty behavior, call CASIModule::configure() instead.

- 3. After calling CASIModule::configure(), set the parameters of all of your subcomponents here if necessary.

## The init() function

- 1. Allocate all resources necessary for simulation here.

- 2. Call CASIModule::init().

- 3. Allow for parameters that might have been set during the configure stage.

## The interconnect() function

– Note –

- 1. If your component has subcomponents, connect your subcomponents here.

- If your component is clocked, register it with the clockMaster. getClockMaster()->registerClockSlave(this);

Use this function if the clocks were not registered by calling casi\_clocked() in the constructor stage. See *The component constructor* on page 1-36.

3. Call CASIModule::interconnect().

# The reset() function

- 1. Implement your reset behavior here.

- 2. Check the reset level to distinguish hard and soft reset if applicable.

- 3. If your model supports loading of object code, retrieve the filename for your model from the file list only during a hard reset.

- 4. Call CASIModule::reset().

## The terminate() function

- 1. You must implement this function if you allocate memory in the init() function.

- 2. Delete all objects created in init().

# The communicate() and update() functions

- 1. If your component is clocked these functions must be defined.

- 2. All communication with other components must be done in the communicate() function.

- 3. Updating of resources must be done in the update() function.

## \_\_\_\_ Note \_\_\_\_\_

It is technically possible to perform updating during the communicate phase, but this is not recommended because it can cause side effects or difficult to diagnose errors.

## 1.11.2 The port classes

- It is typically only necessary to create your own slave port classes. It is recommended to use the master port classes that are provided by the ESL API.

- 2. In the constructor of each slave port, pass a pointer to the component class that the slave port belongs to.

- 3. Access the resources of the component class directly and avoid unnecessary function calls.

# 1.11.3 The factory class

- 1. You must have a factory class for every component you define if your simulation environment dynamically creates and configures components.

- 2. Pass the name of the component to the constructor of CASIFactory.

- 3. Ensure that the name is equivalent to the name used in the component factory constructor by using the name defined in the header file of the component.

# 1.12 CAInterface extensions

The ESL API interfaces support the CAInterface class to enable adding extensions to the APIs without breaking binary compatibility for already compiled models.

CAInterface is the base class for extendable component interfaces and uses the following software model:

- **components** A component is a black-box entity that has a unique identity. A component provides concrete implementations of one or more interfaces. Each of these interfaces may expose different facets of the component's behavior. These interfaces are the only way to interact with the component.

- interfaces An interface is an abstract class (consisting entirely of pure virtual methods), which derives from CAInterface, and which provides a number of methods for interacting with a component.

Because there is no way for a client to enumerate the set of interfaces that a component implements, the client must ask for specific interfaces by name. If the component does not implement the requested interface, it returns a NULL pointer.

(The implementation of a component's interfaces can be provided by one or several interacting C++ objects. The implementation is transparent to the client).

Interfaces are identified by a string name (of type if\_name\_t), and an integer revision (of type if\_rev\_t). A higher revision number indicates a newer revision of the same interface.

The CAInterface::0btainInterface() method enables a client to obtain a reference to any of the interfaces that the component implements.

The client specifies the id and revision of the interface that it wants to request. The component returns NULL if it does not implement that interface or only implements a lower revision.

Each interface derives from CAInterface and a client can call ObtainInterface() on any interface pointer to obtain a pointer to any other interface implemented by the same component.

The following rules govern the use of components and interfaces:

• Each component is distinct. No two components can return the same pointer for a given interface. An ObtainInterface() call on one component must not return an interface on a different component.

- Each interface consists of a name, a revision number, and a C++ abstract class definition. The return value of ObtainInterface() is either NULL, or is a pointer that can be cast to the class type.

- Where two interfaces have the same if\_name\_t, the newer revision of the interface must be backwards-compatible with the old revision. (This includes the binary layout of any data-structures that it uses, and the semantics of any methods).

- During the lifetime of a component, any calls to ObtainInterface() for a given interface name and revision must always return the same pointer value. It must not matter which of the component's interfaces is used to invoke ObtainInterface().

- All components must implement revision 0 of eslapi::CAInterface. This interface implements eslapi::CAInterface class.

# Chapter 2 The Cycle Accurate Simulation Interface

This chapter describes the classes and member functions of the *Cycle Accurate Simulation Interface* (CASI) that are used in the creation and simulation of components. This chapter has the following sections:

- Class overview on page 2-2

- *The CASIModule class* on page 2-10

- The CASIPortIF class on page 2-38

- The clock interface classes on page 2-41

- The transaction interface classes on page 2-52

- The signal interface classes on page 2-91

- The component factory class CASIFactory on page 2-100

- The save/restore interface CASISaveRestore on page 2-102

- Integrating CASI models into OSCI SystemC on page 2-110.

# 2.1 Class overview

The *Cycle Accurate Simulation Interface* (CASI) defines how components are called by the scheduler and how they communicate with each other. Essentially CASI provides a communication library for SystemC that provides clock, transaction, and signal classes to enable transaction-level communication and cycle-based simulation modeling.

CASI provides the following types of class:

#### **Component classes**

The CASIModule class is the base class for any component. It provides the functionality for instantiating and configuring the model and sub-components. It also provides the API required for connecting other components. Unlike the interface classes, CASIModule is derived from CASIModuleIF.

#### Interface classes

The interface classes manage communication between components.

#### **Clock classes**

The clock classes manage connection to the simulation clocks.

#### Port classes

These classes inherit from other basic classes and simplify creating commonly used objects.

## Support classes

These classes provide functionality for creating, saving, and restoring components. These classes are typically used by the simulator to enable additional functionality during simulation. The CASIMMI class, for example, enables describing and configuring the memory maps for a bus master.

## —— Note ———

See the CASITypes.h file for definitions of enumerations and data structures that are used with the CASI interface.

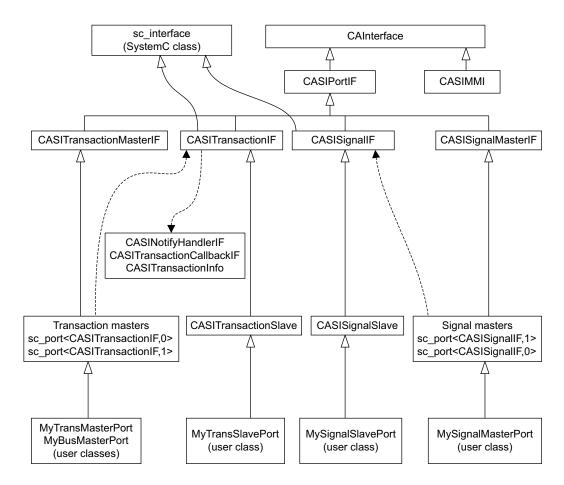

# 2.1.1 Interface classes

The interface classes listed in Table 2-1 have a common base class, CASIPortIF that defines common functionality.

#### Table 2-1 Interface classes

| Class Name              | Class Description                                                                                                                                                                                                                                       |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CASIPortIF              | This class is the base class for all interface classes. Both master and slave ports (including master and slave clock ports) derive from this class. It defines the basic port functionality.                                                           |

| CASITransactionIF       | This class defines the interface for transaction slave ports (for example, memories). This can be used by any component that can be accessed like a memory (for example, DMA, Cache, and Bus). See <i>The CASITransactionIF interface</i> on page 2-56. |

| CASISignalIF            | This class defines the interface for signal slave ports. This can be used for any model that has input signal pins (IRQ or Stall for example). See <i>The CASISignalIF Interface</i> on page 2-92.                                                      |

| CASITransactionMasterIF | This class defines the interface for transaction master ports. See <i>The CASITransactionMasterIF class</i> on page 2-72.                                                                                                                               |

| CASISignalMasterIF      | This class defines the interface for signal master ports. See <i>The CASISignalMasterIF class</i> on page 2-96.                                                                                                                                         |

Figure 2-1 Class hierarchy of the interface classes

# 2.1.2 Port classes

The classes in Table 2-2 are convenience classes that are used to create the ports for a component.

| Class Name                                             | Class Description                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CASISignalSlave                                        | This is the base class for signal slave ports. It is<br>derived from the CASISignalIF class. This type of port<br>is used for any component that has input signal pins<br>(IRQ or Stall for example).<br>See <i>The CASISignalSlave class</i> on page 2-94.                                                                                                                                                                                                       |

| CASITransactionSlave                                   | This is the base class for transaction slave ports. It is<br>derived from the CASITransactionIF class. This type<br>of port is used for any component that can be<br>accessed like memory (for example, DMA, Cache,<br>and Bus).<br>See <i>The CASITransactionSlave class</i> on page 2-66.                                                                                                                                                                       |

| sc_port <casisignalif, 1=""></casisignalif,>           | This is the base class for signal master ports. The basic sc_port class is templated. Using CASISignalIF creates a signal master. Multiple signal slaves can be connected to a signal master.<br>See <i>The signal interface classes</i> on page 2-91.                                                                                                                                                                                                            |

| sc_port <casitransactionif, 0=""></casitransactionif,> | This is the base class for bus master ports. The basic sc_port class is templated. Using CASITransactionIF creates a transaction master. The use of 0 as the second parameter in the template indicates that the master can access multiple transaction slaves. That is, the class contains the address decoder logic that are required if using multiple transaction slaves. See <i>The predefined sc_port &lt; CASITransactionIF, 0&gt; class</i> on page 2-87. |

| sc_port <casitransactionif, 1=""></casitransactionif,> | This is the base class for transaction master ports.<br>The basic sc_port class is templated. Using<br>CASITransactionIF creates a transaction master. The<br>use of 1 as the second parameter in the template<br>indicates that the master can only access a single<br>transaction slave.<br>See <i>The predefined sc_port<casitransactionif, 1=""></casitransactionif,></i><br><i>class</i> on page 2-83.                                                       |

#### Table 2-2 Predefined classes

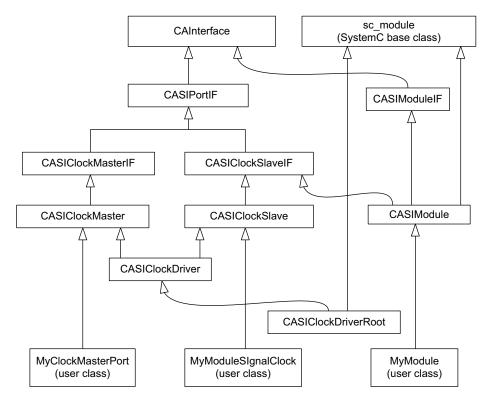

# 2.1.3 Component and clock classes

The classes in Figure 2-2 on page 2-8 provide the clocking functionality for the ESL API and the system components.

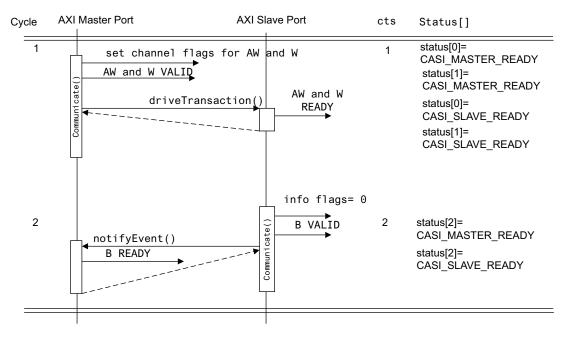

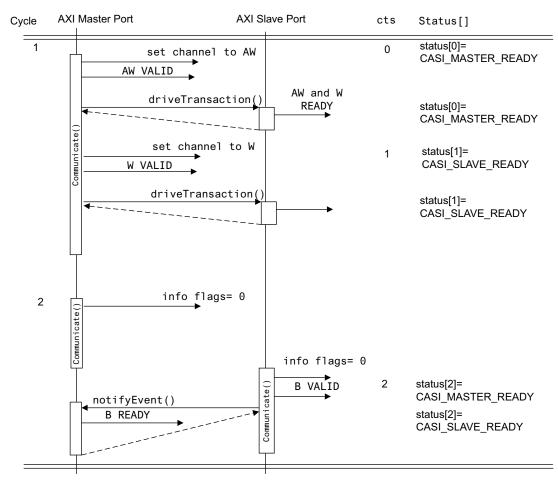

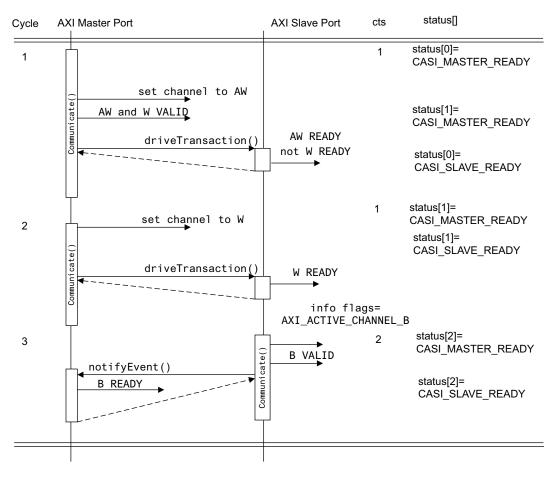

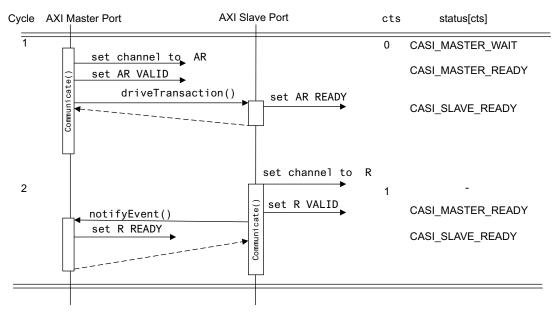

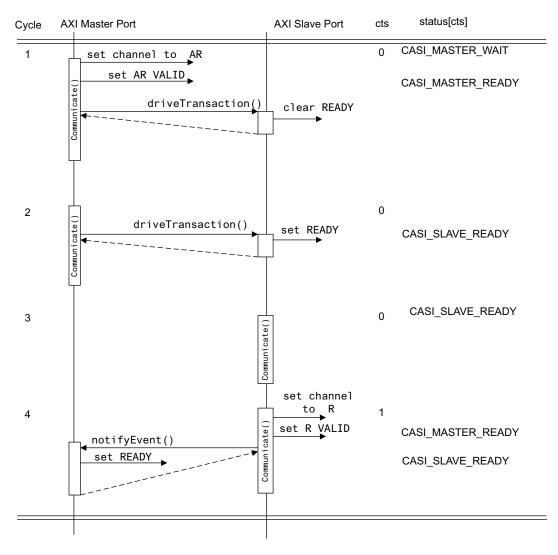

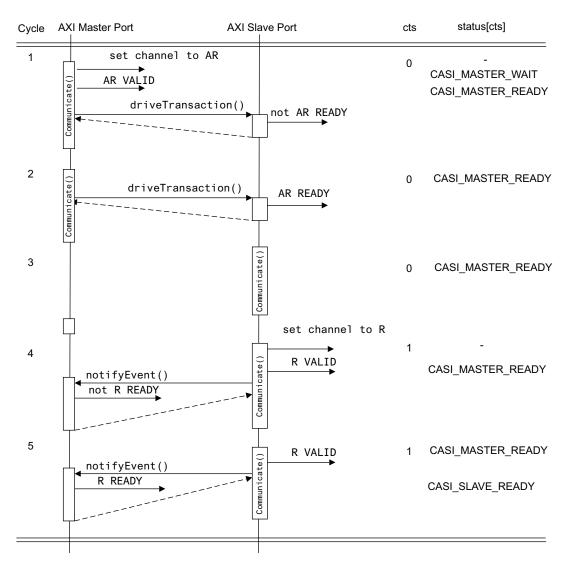

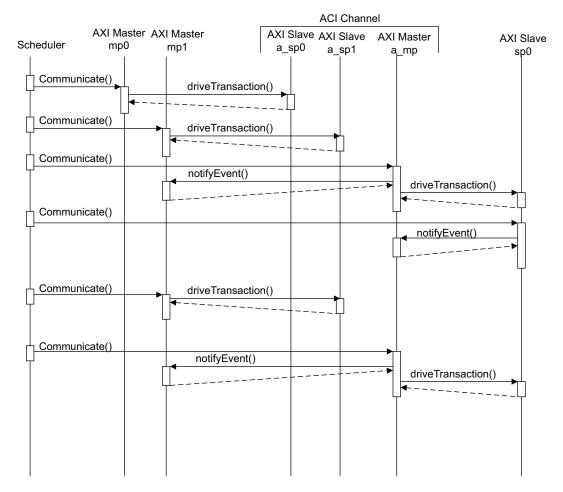

#### Table 2-3 Interface classes