# RealView ICE and RealView Trace

Version 3.1

**User Guide**

# RealView ICE and RealView Trace User Guide

Copyright © 2002, 2004-2007 ARM Limited. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

#### Change history

| Date          | Issue | Confidentiality  | Change                        |

|---------------|-------|------------------|-------------------------------|

| December 2002 | A     | Non-confidential | First release                 |

| January 2004  | В     | Non-confidential | Updated for RealView ICE v1.1 |

| August 2004   | С     | Non-confidential | Updated for RealView ICE v1.2 |

| May 2005      | D     | Non-confidential | Updated for RealView ICE v1.4 |

| November 2005 | Е     | Non-confidential | Updated for RealView ICE v1.5 |

| June 2006     | F     | Non-confidential | Updated for RealView ICE v3.0 |

| May 2007      | G     | Non-confidential | Updated for RealView ICE v3.1 |

#### **Proprietary Notice**

Words and logos marked with ® or ™ are registered trademarks or trademarks owned by ARM Limited. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### **Web Address**

http://www.arm.com

### Contents

## RealView ICE and RealView Trace User Guide

|           | Pretace         |                                                           |      |  |

|-----------|-----------------|-----------------------------------------------------------|------|--|

|           | Ab              | out this document                                         | xv   |  |

|           |                 | edback                                                    |      |  |

| Chapter 1 | Introduc        | tion                                                      |      |  |

| •         | 1.1 Ab          | oout RealView ICE and RealView Trace                      | 1-2  |  |

|           |                 | ailability and compatibility                              |      |  |

|           |                 | roduction to EmbeddedICE logic and debug extensions       |      |  |

|           |                 | roduction to the RealView ICE components                  |      |  |

|           |                 | roduction to GDB debugging with RealView ICE              |      |  |

| Chapter 2 | Getting Started |                                                           |      |  |

| •         | 2.1 Sv          | stem requirements                                         | 2-2  |  |

|           |                 | onnecting the RealView ICE hardware                       |      |  |

|           | 2.3 Us          | sing RealView ICE and RealView Trace                      | 2-11 |  |

| Chapter 3 | Configur        | ing RealView ICE Networking                               |      |  |

| •         |                 | etermining the correct network settings                   | 3-2  |  |

|           |                 | arting and exiting the RealView ICE Config IP application |      |  |

|           |                 | onfiguring the network settings                           |      |  |

|           |                 | estarting your RealView ICE run control unit              |      |  |

|           |                 |                                                           |      |  |

| Chapter 4  | Confi | iguring a RealView ICE Connection                           |      |

|------------|-------|-------------------------------------------------------------|------|

|            | 4.1   | Changes to RealView Debugger                                | 4-2  |

|            | 4.2   | Using the RVConfig dialog                                   | 4-3  |

|            | 4.3   | Connecting RealView Debugger to a target using RealView ICE | 4-30 |

|            | 4.4   | Using the Debug tab of the RealView Debugger Register pane  | 4-31 |

| Chapter 5  | Debu  | igging with RealView ICE                                    |      |

|            | 5.1   | Post-mortem debugging                                       | 5-2  |

|            | 5.2   | Semihosting                                                 | 5-4  |

|            | 5.3   | Breakpoints                                                 | 5-8  |

|            | 5.4   | Cached data                                                 | 5-14 |

|            | 5.5   | Debugging applications in ROM                               | 5-15 |

| Chapter 6  | Using | g RealView Trace                                            |      |

| -          | 6.1   | About RealView Trace                                        | 6-2  |

|            | 6.2   | System requirements                                         | 6-5  |

|            | 6.3   | Installing RealView Trace                                   |      |

|            | 6.4   | Connecting the RealView Trace hardware                      |      |

|            | 6.5   | Configuring RealView Debugger for trace capture             |      |

| Chapter 7  | Mana  | aging the RealView ICE Software                             |      |

| -          | 7.1   | Starting the RVI Update application                         | 7-2  |

|            | 7.2   | Connecting to a RealView ICE unit                           |      |

|            | 7.3   | Viewing software version numbers                            |      |

|            | 7.4   | Installing an update or patch                               |      |

|            | 7.5   | Restarting the RealView ICE run control unit                |      |

| Chapter 8  | Confi | iguring RealView ICE for GDB                                |      |

| -          | 8.1   | About using RealView ICE for debugging with GDB             | 8-2  |

|            | 8.2   | Methods of connecting from remote GDB sessions              |      |

|            | 8.3   | Preparing RealView ICE for remote GDB connections           |      |

|            | 8.4   | Loading and booting a complete system                       |      |

|            | 8.5   | Multiprocessor debugging with GDB and RealView ICE          |      |

|            | 8.6   | The Eclipse Plug-in                                         |      |

| Chapter 9  | Syste | em Design Guidelines                                        |      |

|            | 9.1   | About the system design guidelines                          | 9-2  |

|            | 9.2   | System design                                               | 9-3  |

|            | 9.3   | ASIC guidelines                                             | 9-10 |

|            | 9.4   | PCB guidelines                                              | 9-12 |

|            | 9.5   | JTAG signal integrity and maximum cable lengths             |      |

|            | 9.6   | Compatibility with EmbeddedICE interface target connectors  |      |

| Appendix A | JTAG  | Interface Connections                                       |      |

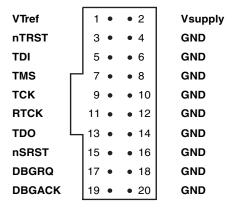

|            | A.1   | JTAG interface pinouts                                      | A-2  |

|            |       |                                                             |      |

|            | A.2   | JTAG interface signals                | A-3  |

|------------|-------|---------------------------------------|------|

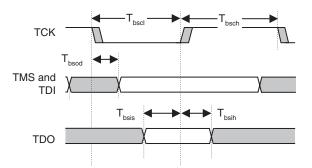

|            | A.3   | JTAG port timing characteristics      | A-6  |

| Appendix B | User  | I/O Connections                       |      |

|            | B.1   | The RealView ICE User I/O connector   | B-2  |

| Appendix C | Real  | View Trace Interface Connections      |      |

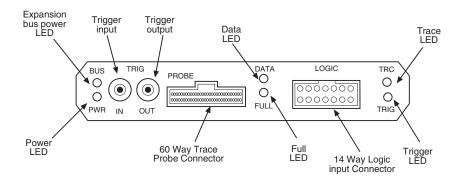

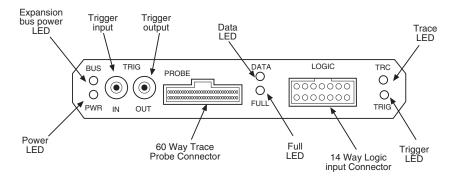

| • •        | C.1   | RealView Trace front panel components | C-2  |

|            | C.2   | Trace signals                         |      |

| Appendix D | Desig | gning the Target Board for Tracing    |      |

| • •        | D.1   | Overview of high-speed design         | D-2  |

|            | D.2   | Termination                           |      |

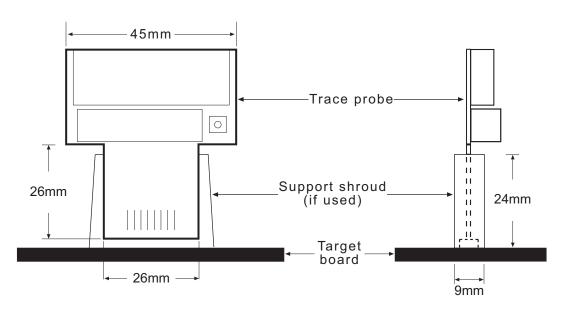

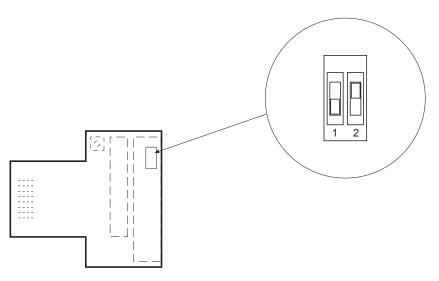

|            | D.3   | Probe dimensions and keep out areas   |      |

|            | D.4   | Signal requirements                   | D-10 |

|            | D.5   | Probe modeling                        |      |

| Appendix E | Hard  | ware Variants                         |      |

| ••         | E.1   | RealView ICE hardware                 | E-2  |

| Appendix F | Seria | al Wire Debug                         |      |

|            | F.1   | Serial Wire Debug                     | F-2  |

|            | Glos  | sarv                                  |      |

|            | J.100 | -u. j                                 |      |

Contents

# List of Tables RealView ICE and RealView Trace User Guide

|           | Change history                          |      |

|-----------|-----------------------------------------|------|

| Table 8-1 | RealView ICE TCP/IP ports               | 8-3  |

| Table A-1 | JTAG signals                            | A-3  |

| Table A-2 | RealView ICE JTAG A timing requirements | A-7  |

| Table A-3 | RealView ICE JTAG B timing requirements | A-7  |

| Table B-1 | User I/O pin connections                |      |

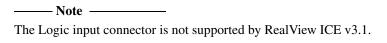

| Table C-1 | Connector signals                       | C-4  |

| Table C-2 | TRACECLK frequencies                    | C-8  |

| Table C-3 | Data setup and hold                     | C-9  |

| Table D-1 | Probe switch settings                   | D-8  |

| Table D-2 | Signals seen at the Mictor connector    | D-10 |

| Table E-1 | Diagnostic table                        | E-5  |

| Table F-1 | SWD interface pinout                    | F-2  |

| Table F-2 | SWD timing requirements                 |      |

List of Tables

# List of Figures

## RealView ICE and RealView Trace User Guide

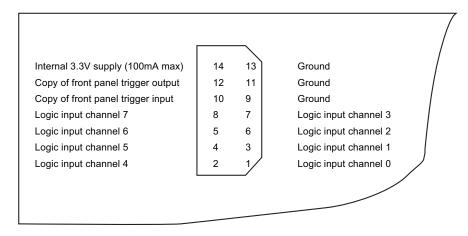

|             | Key to timing diagram conventions                | xix   |

|-------------|--------------------------------------------------|-------|

| Figure 1-1  | Ports for connecting to the host computer        | . 1-8 |

| Figure 1-2  | Ports for connecting to the target hardware      | . 1-9 |

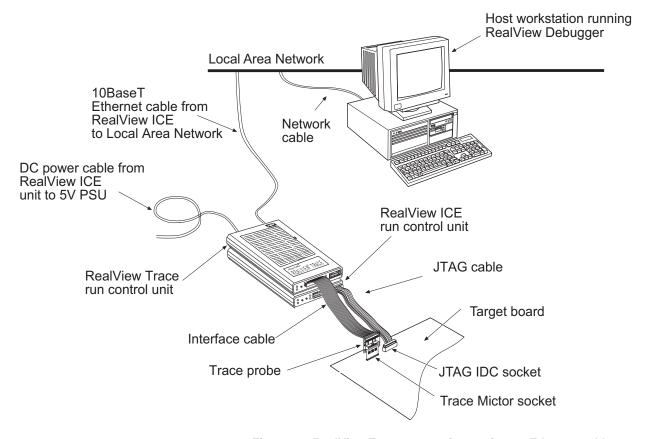

| Figure 2-1  | Connecting the RealView ICE hardware             | . 2-6 |

| Figure 3-1  | The RealView ICE Config IP application           | . 3-3 |

| Figure 3-2  | Error message when another program is browsing   | . 3-5 |

| Figure 3-3  | Error message when no USB devices present        | . 3-6 |

| Figure 3-4  | Error when other connections are active          | . 3-6 |

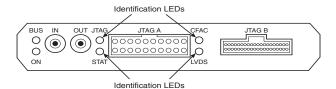

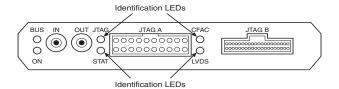

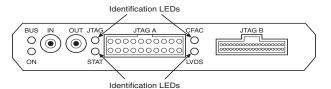

| Figure 3-5  | The identification LEDs                          |       |

| Figure 3-6  | The Configure RealView ICE device dialog box     | . 3-8 |

| Figure 3-7  | The Configure new RealView ICE device dialog box | . 3-9 |

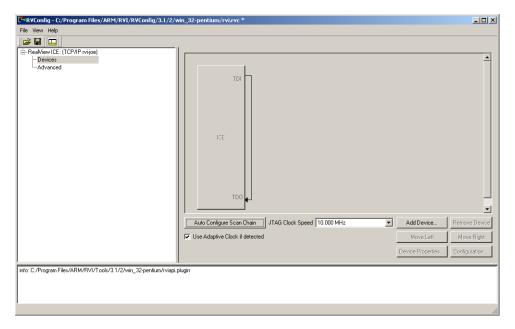

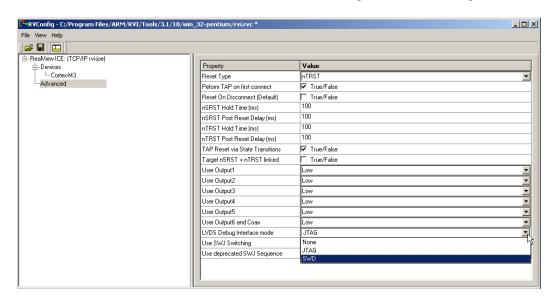

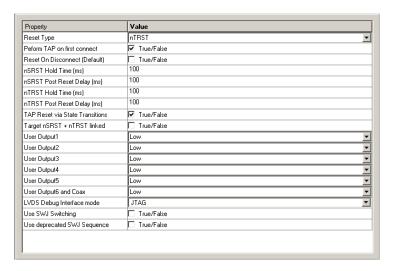

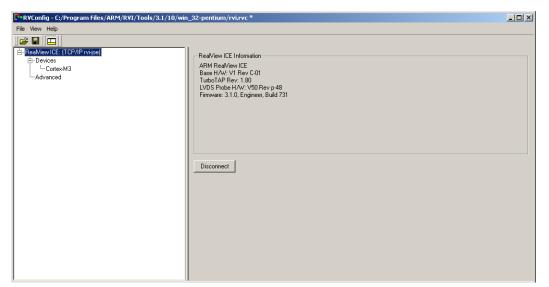

| Figure 4-1  | RVConfig dialog box                              | . 4-4 |

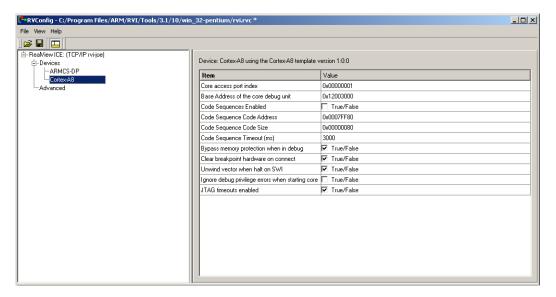

| Figure 4-2  | RVConfig application                             | . 4-5 |

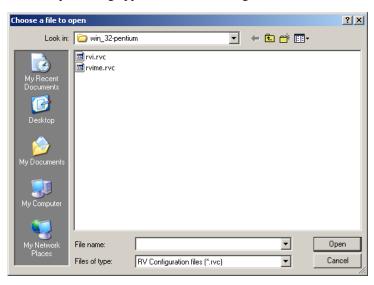

| Figure 4-3  | Choose a file to open dialog                     | . 4-5 |

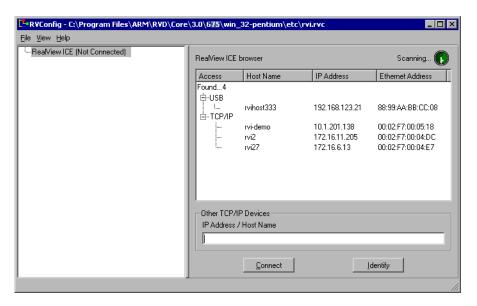

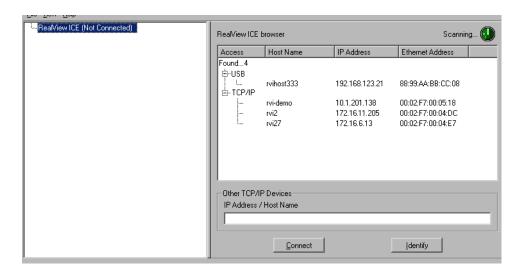

| Figure 4-4  | RVConfig dialog box                              | . 4-6 |

| Figure 4-5  | The RVConfig dialog box showing available units  | . 4-7 |

| Figure 4-6  | The Identification LEDs                          |       |

| Figure 4-7  | Error message when another program is browsing   |       |

| Figure 4-8  | Error message when no USB devices present        | . 4-9 |

| Figure 4-9  | Displaying the scan chain controls               | 4-10  |

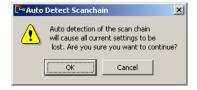

| Figure 4-10 | Auto Detect Scanchain                            | 4-11  |

| Figure 4-11 | Error shown when unpowered devices are detected  | 4-12  |

| Figure 4-12 | Error shown when no devices are detected         |       |

| Figure 4-13 | Error shown when there is no communication with RealView ICE                 | 4-13 |

|-------------|------------------------------------------------------------------------------|------|

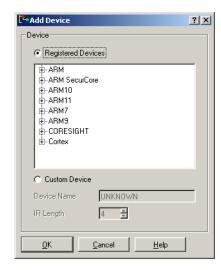

| Figure 4-14 | The Add Device dialog box                                                    | 4-14 |

| Figure 4-15 | The Device Properties dialog box                                             | 4-16 |

| Figure 4-16 | The scan chain JTAG Clock Speed controls                                     | 4-18 |

| Figure 4-17 | Displaying the device controls                                               | 4-20 |

| Figure 4-18 | Displaying the advanced controls                                             |      |

| Figure 4-19 | Recommended settings for an ARM Emulator board                               | 4-27 |

| Figure 4-20 | Displaying the connection controls                                           | 4-28 |

| Figure 4-21 | Warning when disconnecting with unsaved configuration changes                | 4-29 |

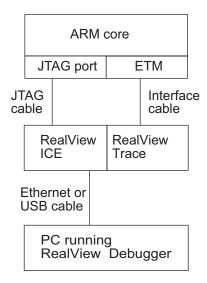

| Figure 6-1  | Trace system                                                                 | 6-2  |

| Figure 6-2  | The RealView Trace data capture unit                                         | 6-3  |

| Figure 6-3  | RealView Trace panel layout                                                  | 6-3  |

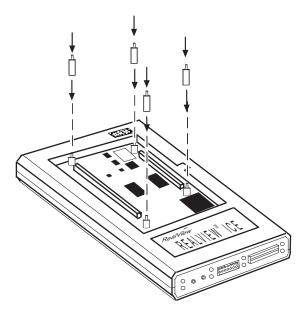

| Figure 6-4  | Positioning of 16mm plastic spacers                                          | 6-8  |

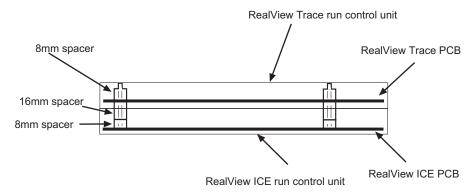

| Figure 6-5  | Profile view of connected units                                              | 6-8  |

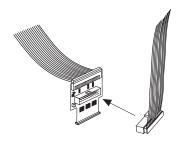

| Figure 6-6  | RealView ICE connector on probe                                              |      |

| Figure 6-7  | RealView Trace connections using an Ethernet cable                           | 6-10 |

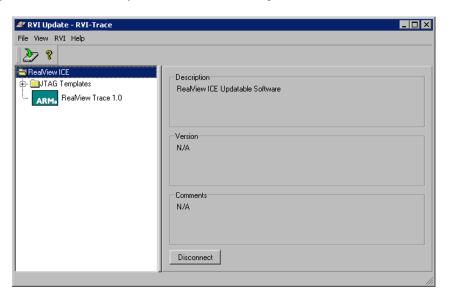

| Figure 7-1  | RVI Update application                                                       | 7-2  |

| Figure 7-2  | RVI Update application showing available units                               | 7-3  |

| Figure 7-3  | The identification LEDs                                                      | 7-4  |

| Figure 7-4  | RVI Update application showing installed components                          | 7-5  |

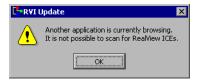

| Figure 7-5  | Error message when another program is browsing                               | 7-6  |

| Figure 7-6  | Error message when no USB devices present                                    | 7-6  |

| Figure 7-7  | Error when other connections are active                                      | 7-7  |

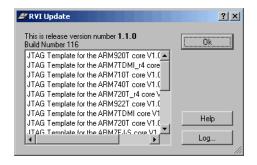

| Figure 7-8  | Version information                                                          |      |

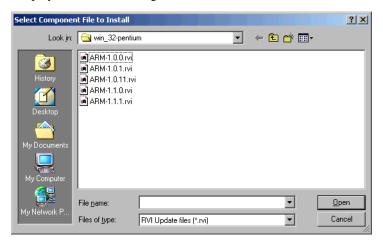

| Figure 7-9  | Selecting the component file to install                                      |      |

| Figure 7-10 | Confirming that you want to install the component file                       |      |

| Figure 7-11 | Error message                                                                |      |

| Figure 7-12 | Error when using an incompatible version of hardware                         |      |

| Figure 7-13 | Progress during an installation                                              |      |

| Figure 7-14 | Progress when rebooting during an installation                               |      |

| Figure 7-15 | Message showing a successful installation                                    |      |

| Figure 7-16 | Progress during probe update                                                 |      |

| Figure 7-17 | Error when installing a patch to uninstalled software                        |      |

| Figure 7-18 | Message when installing a patch that has no new components                   |      |

| Figure 7-19 | Error before data has been written to compact flash                          |      |

| Figure 7-20 | Error during writing to compact flash                                        |      |

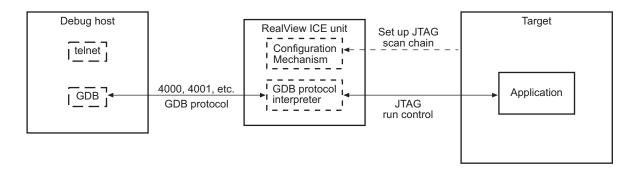

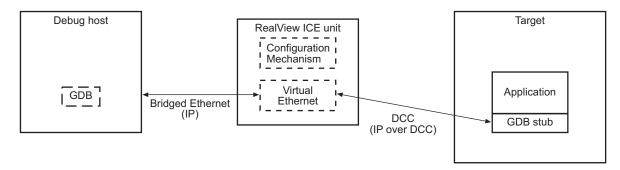

| Figure 8-1  | RVI-GDB connections                                                          |      |

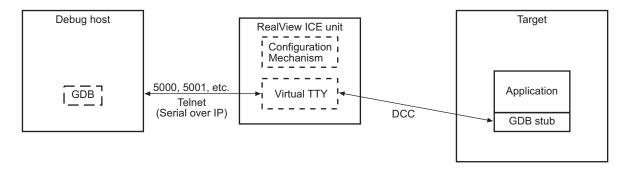

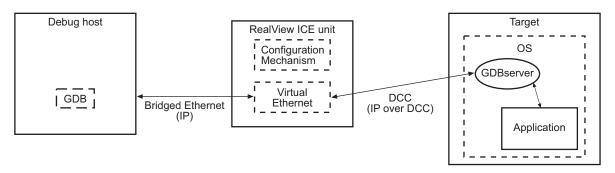

| Figure 8-2  | Target-GDB connections                                                       |      |

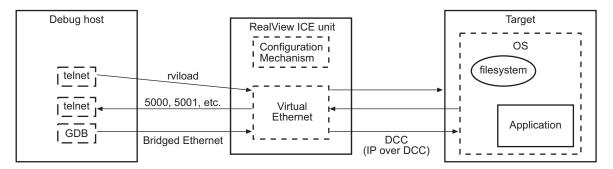

| Figure 8-3  | Target-GDB-Virtual Ethernet connections                                      |      |

| Figure 8-4  | GDBserver connections                                                        |      |

| Figure 8-5  | GDB-NFS connections                                                          |      |

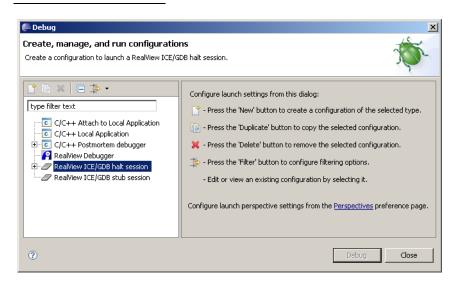

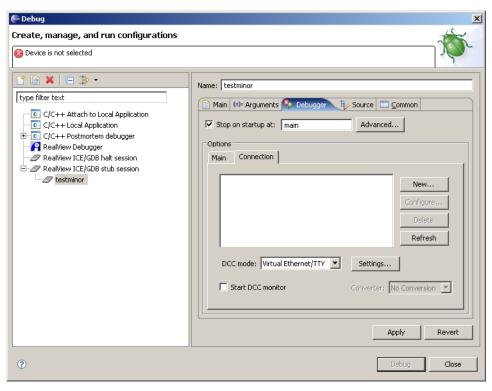

| Figure 8-6  | Debug dialog                                                                 |      |

| Figure 8-7  | Connection option field                                                      |      |

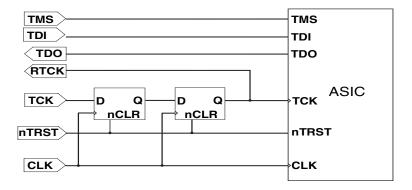

| Figure 9-1  | Basic JTAG port synchronizer                                                 |      |

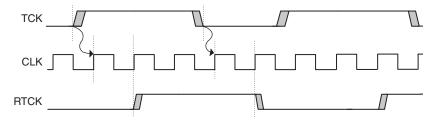

| Figure 9-2  | Timing diagram for the Basic JTAG synchronizer in Figure 9-1                 |      |

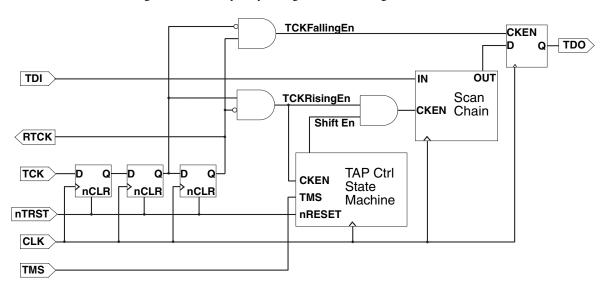

| Figure 9-3  | JTAG port synchronizer for single rising-edge D-type ASIC design rules       |      |

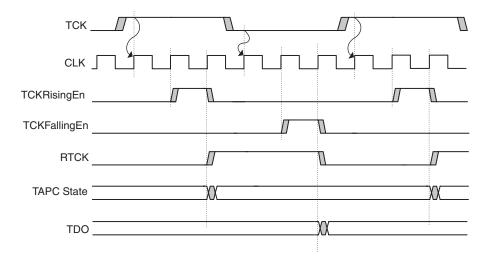

| Figure 9-4  | Timing diagram for the D-type JTAG synchronizer in Figure 9-3 on page 9-5 $$ | 9-6  |

| Figure 9-5 | Example reset circuit logic                            | 9-8  |

|------------|--------------------------------------------------------|------|

| Figure 9-6 | Example reset circuit using power supply monitor ICs   | 9-9  |

| Figure 9-7 | TAP Controllers serially chained within an ASIC        | 9-11 |

| Figure 9-8 | Typical PCB connections                                | 9-12 |

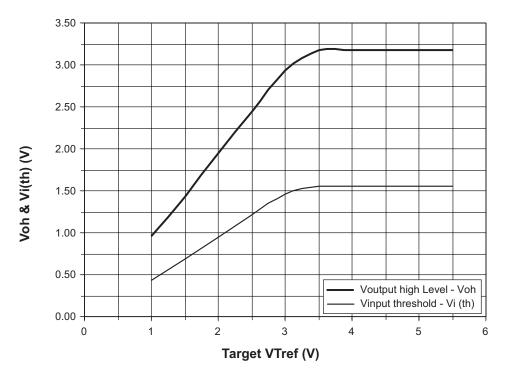

| Figure 9-9 | Target interface logic levels                          |      |

| Figure A-1 | JTAG interface pinout                                  | A-2  |

| Figure A-2 | JTAG port timing diagram                               | A-6  |

| Figure B-1 | User I/O pin connections                               |      |

| Figure C-1 | RealView Trace panel layout                            | C-2  |

| Figure C-2 | Pin surface mount receptacles on trace probe connector | C-4  |

| Figure C-3 | Pin surface mount receptacles on logic input connector | C-7  |

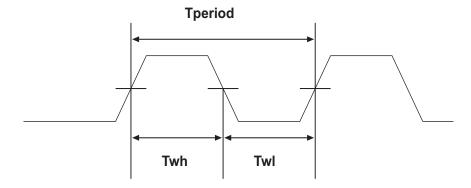

| Figure C-4 | Clock waveforms                                        | C-8  |

| Figure C-5 | Data waveforms                                         |      |

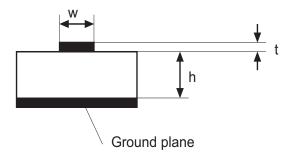

| Figure D-1 | Track impedance                                        | D-6  |

| Figure D-2 | Probe dimensions                                       | D-7  |

| Figure D-3 | Delayed clock probe showing location of switches       | D-8  |

| Figure D-4 | Setup and hold                                         | D-10 |

| Figure E-1 | RVI v3.1 host computer ports end panel                 | E-2  |

| Figure E-2 | Pre-v3.0 host computer ports end panel                 | E-3  |

| Figure E-3 | RVI v3.1 target hardware ports end panel               | E-3  |

| Figure E-4 | Replaced target hardware ports end panel               | E-4  |

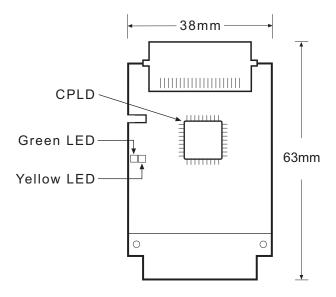

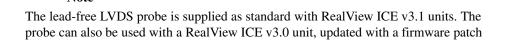

| Figure E-5 | Lead-free LVDS probe LEDs and dimensions               |      |

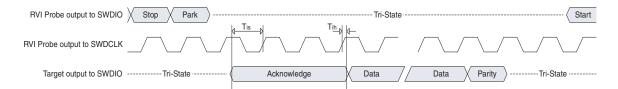

| Figure F-1 | SWD timing diagrams                                    | F-3  |

|            |                                                        |      |

List of Figures

### **Preface**

This preface introduces the *RealView ICE and RealView Trace User Guide*. It explains the structure of the user guide and lists other sources of information that relate to:

- RealView® ICE v3.1 firmware and host software

- RealView Trace v1.0

- RealView Debugger.

This preface contains the following sections:

- About this document on page xvi

- Feedback on page xxi.

#### About this document

This document describes the ARM® RealView ICE (RVI) run control unit, the RealView Trace data capture unit, and the software that enables you to use them.

#### Intended audience

This document is written for those who are using RealView ICE and RealView Trace with *RealView Development Suite* (RVDS) or RealView Debugger with the ARM Developer Suite™ (ADS). It is assumed that you are a software engineer with some experience of the ARM architecture, or a hardware engineer designing a product that is compatible with RealView ICE.

Parts of this document assume that you have some knowledge of *Joint Test Action Group* (JTAG) technology. If you require more information on JTAG, see *IEEE Standard 1149.1-2001*, available from the *Institute of Electrical and Electronic Engineers* (IEEE). For more information, see the IEEE website at http://www.ieee.org.

#### Organization

This document is organized into the following chapters and appendices:

#### Chapter 1 Introduction

Read this chapter for a description of:

- what is provided in the RealView ICE and RealView Trace products

- the purpose of the EmbeddedICE logic within the CPU.

#### Chapter 2 Getting Started

This chapter provides information on how to start working with RealView ICE. It includes the hardware and software system requirements, and how to connect up the hardware.

#### Chapter 3 Configuring RealView ICE Networking

This chapter describes how to configure the network settings for your RealView ICE run control unit. If you are using a TCP/IP connection, you must configure the network settings before you can use the unit for debugging. If you are using a USB connection, you do not have to configure the network settings.

#### Chapter 4 Configuring a RealView ICE Connection

This chapter describes how to configure a connection that is made using a RealView ICE run control unit.

Read this chapter in conjunction with the RealView Debugger user documentation.

#### Chapter 5 Debugging with RealView ICE

This chapter describes how to:

- change the behavior of RealView ICE using internal variables

- implement breakpoints

- access the EmbeddedICE logic directly.

You must read this chapter in conjunction with the RealView Debugger documentation suite.

#### Chapter 6 Using RealView Trace

This chapter describes RealView Trace and tells you how to connect the parts of RealView Trace and RealView ICE together. It also tells you where to find information on using RealView Trace with RealView Debugger.

#### Chapter 7 Managing the RealView ICE Software

This chapter describes how to manage and update the software that is installed on the RealView ICE run control unit.

#### Chapter 8 Configuring RealView ICE for GDB

This chapter provides information on the basic steps required to configure the RealView ICE unit to a state where you can begin debugging your image using the *GNU Debugger* (GDB). This chapter also introduces the Eclipse Plug-in, which allows software developers to use the Eclipse IDE as a project manager to create, build, debug, and manage C, C++ and assembly language projects for ARM targets.

#### Chapter 9 System Design Guidelines

This chapter provides information about designing ARM architecture-based ASICs and PCBs that can be debugged using RealView ICE.

#### It includes:

- suggested clocking and reset circuit diagrams

- information on how to chain *Test Access Port* (TAP) controllers

- suggested physical connector types and pinouts

- a description of logic voltage level adaptation

- information on how power consumption varies with supply voltage.

#### Appendix A JTAG Interface Connections

This appendix describes and illustrates the JTAG pin connections.

#### Appendix B User I/O Connections

This appendix describes and illustrates the additional input and output connections provided in RealView ICE.

#### Appendix C RealView Trace Interface Connections

This appendix describes and illustrates the RealView Trace pin connections.

#### Appendix D Designing the Target Board for Tracing

This appendix describes the properties of a target board that can be connected to RealView Trace.

#### Appendix E Hardware Variants

This appendix describes the RealView® ICE v3.0 hardware unit.

#### Appendix F Serial Wire Debug

This appendix describes the serial wire debug (SWD) connection to the Debug Access Port (DAP).

#### Typographical conventions

The following typographical conventions are used in this document:

bold Highlights ARM processor signal names within text, and interface

elements such as menu names. Can also be used for emphasis in

descriptive lists where appropriate.

*italic* Highlights special terminology, cross-references, and citations.

monospace Denotes text that can be entered at the keyboard, such as commands, file

names and program names, and source code.

<u>mono</u>space Denotes a permitted abbreviation for a command or option. The

underlined text can be entered instead of the full command or option

name.

monospace italic

Denotes arguments to commands or functions where the argument is to

be replaced by a specific value.

#### monospace bold

Denotes language keywords when used outside example code.

#### **Timing diagram conventions**

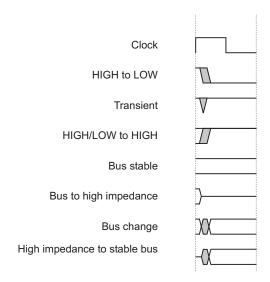

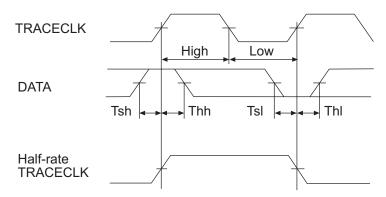

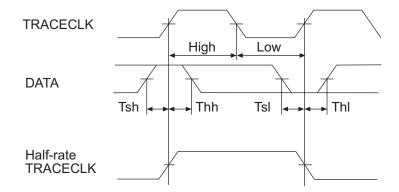

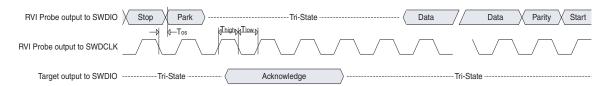

The following diagram shows the components used in the timing diagrams contained in this manual. Any variations are clearly labeled when they occur.

#### Key to timing diagram conventions

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

#### **Further reading**

This section lists publications by ARM® Limited, and by third parties, that are related to this product.

ARM Limited periodically provides updates and corrections to its documentation. See http://www.arm.com for current errata sheets, addenda, and the ARM Frequently Asked Questions list.

#### **ARM** publications

This document contains information that is specific to RealView ICE. The following documents also relate specifically to RealView ICE:

- ARM RealView ICE Installation Guide (ARM DSI 0017)

- The RealView ICE readme.html file, supplied on the RealView ICE distribution CD, and installed beneath the Product subdirectory of the host software.

Also see the following books in the RealView Debugger documentation suite:

- RealView Debugger Essentials Guide (ARM DUI 0181)

- RealView Debugger User Guide (ARM DUI 0153)

- RealView Debugger Target Configuration Guide (ARM DUI 0182)

- RealView Debugger Command Line Reference Guide (ARM DUI 0175)

- RealView Debugger Trace User Guide (ARM DUI 0322).

- RealView Debugger RTOS Guide (ARM DUI 0323).

The following documentation provides general information on the ARM architecture, processors, associated devices, and software interfaces:

• *ARM Reference Peripheral Specification* (ARM DDI 0062).

See the relevant datasheet or Technical Reference Manual for information relating to your hardware.

See the following book for a description of the *Debug Communications Channel* (DCC):

• RealView Compilation Tools Developer Guide (ARM DUI 0203).

#### Other publications

The following publications might also be useful to you:

- IEEE Standard Test Access Port and Boundary Scan Architecture

(IEEE Std. 1149.1-2001) describes the JTAG ports with which RealView ICE

communicates

- Steve Furber, *ARM system-on-chip architecture* (2nd edition, 2000). Addison Wesley, ISBN 0-201-67519-6.

For more information about CEVA-Oak, CEVA-TeakLite, and CEVA-Teak DSP processors from CEVA, Inc. see http://www.ceva-dsp.com.

#### **Feedback**

ARM Limited welcomes feedback on RealView ICE and RealView Trace, and on the documentation.

#### Feedback on RealView ICE and RealView Trace

If you have any problems with RealView ICE and RealView Trace, contact your supplier. To help us provide a rapid and useful response, give:

- the versions of RealView ICE software and firmware that you are using

- details of the platforms you are using, including both the host and target hardware types and operating system

- where appropriate, a small standalone sample of code that reproduces the problem

- a clear explanation of what you expected to happen, and what actually happened

- the commands you used, including any command-line options

- if possible, sample output illustrating the problem.

#### Feedback on this document

If you have any comments on this document, send email to errata@arm.com giving:

- the document title

- the document number

- the page number(s) to which your comments refer

- a concise explanation of your comments.

General suggestions for additions and improvements are also welcome.

Preface

# Chapter 1 Introduction

This chapter introduces RealView® ICE v3.1, RealView Trace v1.0 and GDB debugging, and describes the software components. It contains the following sections:

- About RealView ICE and RealView Trace on page 1-2

- Availability and compatibility on page 1-4

- Introduction to EmbeddedICE logic and debug extensions on page 1-5

- *Introduction to the RealView ICE components* on page 1-8.

- Introduction to GDB debugging with RealView ICE on page 1-11

#### 1.1 About RealView ICE and RealView Trace

RealView ICE v3.1 is an EmbeddedICE® logic debug solution from ARM® Limited. It enables you to debug software running on:

- ARM processor cores that include the EmbeddedICE logic.

- the following *Digital Signal Processor* (DSP) cores:

- CEVA-Oak, CEVA-TeakLite (revisions B and C), and CEVA-Teak (revisions A and B) from CEVA, Inc. (previously known as DSP Group).

RealView ICE provides the software and hardware interface between a debugger running on a Windows or Red Hat Linux host computer, and a *Joint Test Action Group* (JTAG) *IEEE Standard 1149.1-2001* port on the target hardware.

The RealView Trace unit works in conjunction with ARM RealView ICE to provide real-time trace functionality for software running on *System-on-Chip* (SoC) devices with deeply embedded processor cores that contain the *Embedded Trace Macrocell*<sup> $^{\text{IM}}$ </sup> (ETM $^{\text{IM}}$ ) logic.

| Note -        |                | -             |         |            |

|---------------|----------------|---------------|---------|------------|

| RealView Trac | e v1.0 is only | available for | Windows | platforms. |

You can use RealView ICE and RealView Trace with systems that contain one or more ARM processor cores. RealView ICE also supports the *Embedded Trace Buffer*<sup>IM</sup> (ETB $^{\text{IM}}$ ) for capturing small amounts of trace information at high core clock speeds. See Chapter 6 *Using RealView Trace* for more information.

#### 1.1.1 RealView ICE product contents

The RealView ICE product comprises:

- A run control unit that connects to your target board over a JTAG interface and to your PC using either USB or Ethernet.

- Mains cables and a power supply that powers the run control unit.

- An Ethernet cable.

- A USB cable.

- Two alternative cables that connect the RealView ICE run control unit to the target JTAG connector:

- a short 20-way ribbon cable

- a long 40-way ribbon cable and a *Low Voltage Differential Signaling* (LVDS) 40-way to 20-way probe.

- A 20-way to 14-way adaptor, for targets that use a 14-way *Insulation Displacement Connector* (IDC) box header.

| ——— Caution ———                                                  |         |

|------------------------------------------------------------------|---------|

| Before using this adaptor, see Using nonstandard connectors on p | age 2-9 |

- Software on CD-ROM that enables a debugger to communicate with the run control unit, and to configure and manage the run control unit.

- Documentation, including:

- a software Installation Guide, supplied as a CD insert

- a printed copy of this User Guide

- online versions of this User Guide in Dynatext (Windows only) and PDF formats

- online help

- a packing list

- a registration card.

#### 1.1.2 RealView Trace product contents

The RealView Trace product (purchased separately) additionally comprises:

- the RealView Trace capture unit

- a cable to connect the RealView Trace capture unit to a trace port

- a logic grabber cable

- spacers for attachment to the RealView ICE unit.

#### 1.2 Availability and compatibility

RealView ICE and RealView Trace are available from ARM Limited and its resellers.

Contact ARM Limited directly regarding OEM licenses.

RealView ICE v3.1 and RealView Trace v1.0 are compatible with RVDS v3.1.

The RealView ICE software for the host computer is compatible with the following operating systems:

- Windows XP Professional (service pack 2, or later)

- Red Hat Enterprise Linux 4.

| Note                        | <del>-</del>                |

|-----------------------------|-----------------------------|

| RealView Trace is only avai | lable for Windows platforms |

RealView ICE provides:

- The ability to access the target.

- Tools to configure RealView Debugger so that it can connect to the target through RealView ICE. RealView Debugger provides the user interface items, such as register windows and disassemblers, that make it possible to debug your application.

For more information on compatibility with target hardware, see the documentation supplied with your hardware.

#### 1.3 Introduction to EmbeddedICE logic and debug extensions

The EmbeddedICE logic and the ARM processor debug extensions enable RealView ICE to debug software running on an ARM processor. This section describes the basic principles of this operation:

- Debug extensions to the ARM core

- The EmbeddedICE logic on page 1-6

- How the EmbeddedICE debug architecture differs from a debug monitor on page 1-6.

To determine whether a specific ARM processor has support for JTAG debugging, see its datasheet or technical reference manual.

For information on RealView Trace, see Chapter 6 Using RealView Trace.

#### 1.3.1 Debug extensions to the ARM core

The debug extensions consist of several scan chains around the processor core, and some additional signals that are used to control the behavior of the core for debug purposes. The most significant of these additional signals are:

**BREAKPT** This core signal enables external hardware to halt processor execution for debug purposes. When HIGH during an instruction fetch, the instruction is tagged as breakpointed, and the core stops if this instruction reaches the execute stage of the pipeline.

**DBGRQ** This core signal is a level-sensitive input that causes the CPU core to enter debug state when the current instruction has completed.

**DBGACK** This core signal is an output from the CPU core that goes HIGH when the core is in debug state so that external devices can determine the current state of the core.

RealView ICE uses these, and other signals, through the debug interface of the processor core, for example by writing to the control register of the EmbeddedICE logic. For more details, see the section that describes the debug interface support of the ARM datasheet or technical reference manual for your core (for example, the *ARM7TDMI (Rev 4) Technical Reference Manual*).

#### 1.3.2 The EmbeddedICE logic

The EmbeddedICE logic is the integrated on-chip logic that provides JTAG debug support for ARM cores. EmbeddedICE-RT is a superset of EmbeddedICE that includes extensions supporting real-time debug, including setting breakpoints on a running target.

The EmbeddedICE logic is accessed through the TAP controller on the ARM core using the JTAG interface. See Chapter 9 *System Design Guidelines* for details of designing this into your own target.

The EmbeddedICE logic consists of:

- two or more breakpoint units

- a control register

- a status register

- a set of registers implementing the DCC link.

You can program one or both of the breakpoint units to halt the execution of instructions by the ARM CPU core. Execution is halted when a match occurs between the values in the breakpoint registers and the values currently appearing on the address bus, data bus, and selected control signals.

You can mask any bit to prevent it from affecting the comparison. Both breakpoint units can be configured to be a data breakpoint (monitoring data accesses) or an instruction breakpoint (monitoring instruction fetches).

For more information, see the relevant section of the appropriate ARM datasheet or technical reference manual.

#### 1.3.3 How the EmbeddedICE debug architecture differs from a debug monitor

A debug monitor is an application that runs on your target hardware in conjunction with your application, and requires target resources (for example, memory, access to exception vectors, and timers) to be available.

The EmbeddedICE debug architecture requires almost no resources. Rather than being an application on the board, it works by using:

- additional debug hardware within the core, to enable the host to communicate with the target

- an external run control unit that buffers and translates the core signals into something that is usable by a host computer.

The EmbeddedICE debug architecture enables debugging to be as non-intrusive as possible:

- the target being debugged requires very little special hardware to support debugging

- in most cases you do not have to set aside memory for debugging in the system being debugged and you do not have to incorporate special software into the application

- execution of the system being debugged is only halted when a breakpoint unit is triggered, or you request that execution is halted.

#### 1.4 Introduction to the RealView ICE components

This section introduces the components of the RealView ICE product, and describes how they fit together. It contains the following sections:

- The RealView ICE run control unit

- The RealView ICE firmware on page 1-9

- The RealView ICE host software on page 1-10.

See Chapter 6 *Using RealView Trace* for information on the RealView Trace components.

#### 1.4.1 The RealView ICE run control unit

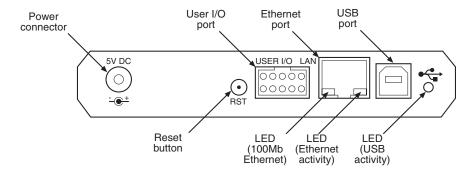

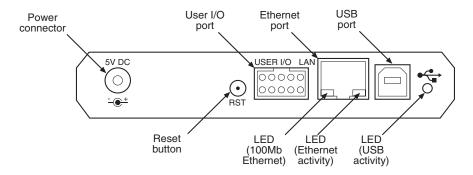

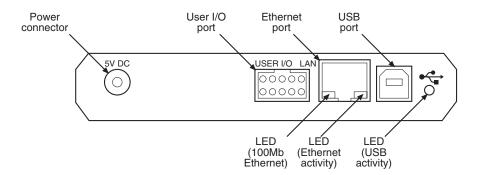

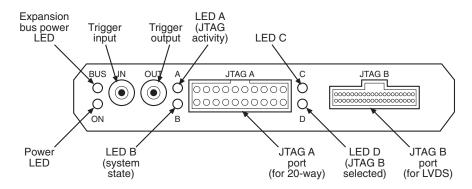

The RealView ICE run control unit provides the hardware to enable a computer to control multiple JTAG capable devices. The unit has ports at one end for connecting to the host computer and to a power source. These ports are shown in Figure 1-1.

Figure 1-1 Ports for connecting to the host computer

The RST button is used to reset the RealView ICE unit when required, and returns RealView ICE to its power-up state. Using the RST button in this way does not reset the target. This button must not be confused with the Reset button mentioned in *Carrying out a real reset* on page 5-16, which is located on the target board itself.

The LEDs at the bottom of the Ethernet port display information about Ethernet speed and activity:

- The green LED shows the Ethernet speed. When Off, it indicates a speed of 10Mb/s, and when On indicates a speed of 100Mb/s.

- The yellow LED indicates that activity is taking place.

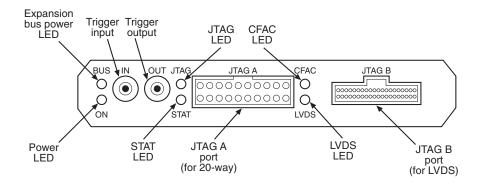

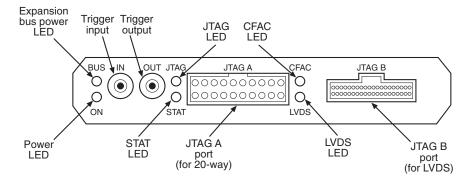

The ports at the other end of the unit connect to the target hardware. These ports are shown in Figure 1-2 on page 1-9.

Figure 1-2 Ports for connecting to the target hardware

Cables are supplied to connect the run control unit to the host computer, and to the target hardware.

| Note                | <del></del>         |                   |                |            |

|---------------------|---------------------|-------------------|----------------|------------|

| RealView ICE v3.1 d | oes not support the | Trigger input and | Trigger output | t signals. |

If the RealView ICE unit detects an internal hardware or software failure from which it cannot recover, the four LEDs JTAG, STAT, CFAC and LVDS (shown in Figure 1-2) flash continuously. You must reboot RealView ICE before you can continue using it. To do this, press the RST button.

During installation of an update or a patch, the CFAC LED lights up, which denotes that Compact Flash Activity (CFAC) is taking place. While this is happening, you must not disconnect power from the run control unit, and must wait until this LED has extinguished. For more information on installing updates and patches, see *Procedure for installing an update or patch* on page 7-10. The CFAC LED also lights up when a debugger connects, and during *Dynamic Host Configuration Protocol* (DHCP) lease renewal.

The RealView ICE run control unit contains an internal cooling fan that operates to control the internal temperature when necessary. The ventilation panels on the top and bottom of the RealView ICE run control unit and RealView Trace data capture unit must not be obscured.

#### 1.4.2 The RealView ICE firmware

The RealView ICE firmware is located in the RealView ICE run control unit. It receives commands from the RealView ICE host software and translates them into JTAG accesses. The RealView ICE firmware contains specific sections of code for each ARM processor. These are called templates.

You can update the RealView ICE firmware using the RealView ICE Update application in the following ways:

- for firmware fixes, you can obtain firmware patches from the ARM website

- for firmware updates that add new functionality, such as additional templates, you must obtain a new CD that also contains updates to the host software.

See Chapter 7 *Managing the RealView ICE Software* for information on using the RealView ICE Update application.

#### 1.4.3 The RealView ICE host software

The RealView ICE host software fits between RealView Debugger and the RealView ICE hardware that controls the JTAG devices. It translates debugger commands, such as start, stop, and download, into JTAG control sequences for a particular processor. The RealView ICE software provides support for debugging on a wide range of ARM cores. To see a list of supported cores, open the RealView ICE Update application and expand the **JTAG Templates** and **ARM** trees. A list of templates for all supported cores is displayed. See Chapter 7 *Managing the RealView ICE Software* for more information on using the RealView ICE Update application.

The RealView ICE software can address each JTAG device individually, without affecting other devices on the board. It uses this ability to create virtual connections for each of the JTAG devices on the board. RealView Debugger can attach to one of these virtual connections, and perform debugging operations with no knowledge of the other devices on the board.

The RealView ICE software enables multiple concurrent connections. You can debug multiprocessor systems, as described in the *RealView Debugger User Guide*. The software can also perform a synchronized start or stop of processors, for debugging multiprocessor systems where the processors interact with each other.

The RealView ICE software also supports connections across a network, so that you can run the debugging software on several different computers.

#### 1.5 Introduction to GDB debugging with RealView ICE

RealView ICE enables you to debug applications running on ARM architecture-based cores using *GNU Debugger* (GDB). In addition to the basic debugging operations, such as setting breakpoints and stepping, RealView ICE provides extended debugging features—for example, you can connect to multiple cores.

RealView ICE enables you to debug applications using the following debugging modes:

- Halt-mode debugging, where the target stops while you examine it.

- Monitor-mode debugging, where the target continually runs and you monitor the target using DCC communications.

To connect to a target from GDB, you must configure RealView ICE to recognize your target devices. You do this by initiating an application to configure the scan chain, which in turn connects to RVI and connects to a core in a single operation. The procedure for configuring RealView ICE is described in Chapter 8 *Configuring RealView ICE for GDB*.

In addition to configuring RealView ICE, there are other requirements that you must consider when connecting to your target application:

- Your host workstation might require specific services to be running depending on the requirements of your target application, for example, DHCP.

- Your application might be running as a standalone application without an operating system, or as part of an operating system.

The methods you can use to connect to a target application, and the requirements for each method, are described in Chapter 8 *Configuring RealView ICE for GDB*.

#### 1.5.1 GDB availability and compatibility

To find the latest information on GNU Debugger (GDB) compatibility with RealView ICE v3.1, see the ARM RealView ICE v3.1 Release Notes. Also see *The GNU toolchain for ARM architectures* on page 1-12.

For more information on compatibility with target hardware, see the documentation supplied with your hardware.

#### 1.5.2 Supported debug host platforms

RealView ICE supports remote GDB sessions running on the following operating systems:

• Windows XP Professional (service pack 2, or later)

• Red Hat Enterprise Linux 4.

#### 1.5.3 Recommended applications for debugging with GDB

The recommended applications for debugging with GDB are described in the following sections:

- The GNU toolchain for ARM architectures

- Cygwin on Windows on page 1-13

- *Using an IDE with a GNU toolchain for ARM architectures* on page 1-13.

| —— Note – |  |

|-----------|--|

|-----------|--|

ARM Limited does not provide support for these applications. If you require support for these applications, see the related web site.

All examples in this chapter assume that you are using GDB from a Unix shell. Also, this chapter assumes that you are familiar with using:

- a GNU toolchain for ARM architectures (see *The GNU toolchain for ARM architectures*)

- Cygwin (see *Cygwin on Windows* on page 1-13)

It also assumes that you already have these applications installed. See the related web sites for details on how to obtain, install, and use them.

#### The GNU toolchain for ARM architectures

You must use a GNU toolchain built for ARM architecture support. You can obtain prebuilt versions of the toolchain from either:

• CodeSourcery GNU Toolchain for ARM processors, available from:

http://www.codesourcery.com

The CodeSourcery GNU Toolchain for ARM processors commands are prefixed with arm-none-eabi-, for example arm-none-eabi-gcc.

This toolchain is compliant with the Application Binary Interface (ABI) for the ARM Architecture (base standard) [BSABI].

• GNU ARM toolchain, available from:

http://www.gnuarm.com

The GNU ARM toolchain commands are prefixed with arm-elf- for Windows and arm-linux- for Red Hat Linux. For example, arm-elf-gcc and arm-linux-gcc.

This toolchain is not compliant with the ABI for the ARM Architecture.

#### **Cygwin on Windows**

On Windows you can have Cygwin, obtainable from http://www.cygwin.com. Instructions for setting up Cygwin for use with RealView ICE are given in the document *Setting Up Cygwin on Windows*, in the file CygwinSetup.pdf that accompanies this document.

#### Using an IDE with a GNU toolchain for ARM architectures

Although GDB is a command-line debugger, there are *Integrated Development Environments* (IDEs) that use GDB as their backend. For more information on using IDEs in this way, see the Application Note that accompanies this release.

Introduction

# Chapter 2 **Getting Started**

This chapter describes the system requirements for RealView® ICE, and how to connect the RealView ICE hardware to your host computer and target system. It also describes how to use some common parts of the RealView ICE software. It contains the following sections:

- System requirements on page 2-2

- *Connecting the RealView ICE hardware* on page 2-5

- Using RealView ICE and RealView Trace on page 2-11.

# 2.1 System requirements

This section describes the hardware and software requirements of RealView ICE:

- *Host software requirements*

- *Host hardware requirements* on page 2-3

- *Target hardware requirements* on page 2-3.

See Chapter 6 *Using RealView Trace* for information on the requirements for RealView Trace.

# 2.1.1 Host software requirements

The RealView ICE software for the host computer runs under the following operating systems:

- Windows XP Professional (service pack 2, or later)

- Red Hat Enterprise Linux 4.

| Note              |                    |                   |

|-------------------|--------------------|-------------------|

| RealView Trace is | only available for | Windows platforms |

RealView ICE v3.1 is compatible with RVDS v3.1.

## **Automatic dialup**

Automatic dialup might be triggered when you use RealView ICE, because RealView ICE uses network facilities. You might want to prevent unnecessary dialups by disabling automatic dialup in the operating system for your host computer.

### 2.1.2 Host hardware requirements

This section defines the minimum recommended hardware requirements for installing and running the RealView ICE software on a host computer.

## Disk space

If you carry out a full installation of the software, up to 100MB of hard disk space is required.

## Using the RealView ICE software on Windows

To use the RealView ICE software on Windows, you require the following:

- Pentium IBM-compatible machine

- CD-ROM drive (this can be a networked CD-ROM drive)

- an unused USB port, if direct connection to the run control unit is required

- a TCP/IP connection, if remote connection to the run control unit is required.

## Using the RealView ICE software on Red Hat Linux

To use the RealView ICE software on Red Hat Linux, you require the following:

- Pentium IBM-compatible machine

- CD-ROM drive (this can be a networked CD-ROM drive)

- a TCP/IP connection.

| Note                         |                              |

|------------------------------|------------------------------|

| RealView Trace is only avail | lable for Windows platforms. |

# 2.1.3 Target hardware requirements

RealView ICE has the following target hardware requirements:

- A device interface conforming to the IEEE Std. 1149.1-2001 (JTAG) specification.

- Electronic signals available to the interface, and within the limits of current and voltage specified in Chapter 9 *System Design Guidelines*.

- One of the following IDC box headers on the target hardware:

- a 20-way header that conforms to the current ARM JTAG connection standard (as described in Appendix A JTAG Interface Connections)

— a 14-way header that conforms to the previous ARM JTAG connection standard (as used by the ARM EmbeddedICE® run control unit).

To use any other connectors, you must construct an appropriate adaptor or cable yourself.

- A maximum cable length between the target hardware and the RealView ICE run control unit of:

- 30cm if you are using a 20-way ribbon cable

- 3m if you are using a 40-way ribbon cable with the supplied LVDS probe.

Otherwise, one or more of the modifications described in Chapter 9 *System Design Guidelines* must be used.

• One or more ARM architecture CPUs that has supporting debug logic linked into a JTAG scan chain. This includes most ARM7<sup>™</sup>, ARM9<sup>™</sup>, ARM10<sup>™</sup>, and ARM11<sup>™</sup> cores. It does not include the StrongARM<sup>®</sup> and XScale processors.

You can use the RealView Update application to find out which processors are supported by the version of RealView ICE that you are using. To do this, start the RealView ICE Update application (see Chapter 7 *Managing the RealView ICE Software*) and select **Version Info...** from the **RVI** menu.

# 2.2 Connecting the RealView ICE hardware

This section explains how to set up the hardware for RealView ICE:

- What you require

- *Connection instructions* on page 2-6

- Using nonstandard connectors on page 2-9

- *Hot plugging and unplugging the JTAG cable* on page 2-9.

See Chapter 6 *Using RealView Trace* for information on setting up the RealView Trace hardware.

## 2.2.1 What you require

To set up the hardware you require the following items from the RealView ICE product kit:

- the RealView ICE run control unit

- the power adaptor for the run control unit

- the mains cable for the power adaptor that is appropriate for your region

- one of the following cables, to connect the run control unit to the PC or the network:

- the USB cable, to connect the run control unit directly to the PC using the USB port

- the RJ-45 Ethernet cable, to connect the run control unit to the network

- the Ethernet cross-over cable, to connect the run control unit directly to the PC using the Ethernet port.

- one of the following cables, to connect the run control unit to the target hardware:

- the *JTAG cable* (a short 20-way ribbon cable)

- the *LVDS cable and probe* (a long 40-way ribbon cable, and a small PCB with a 40-way and a 20-way IDC connector mounted on it)

You must also provide the following items:

- a host computer that conforms to the requirements given in *Host software* requirements on page 2-2, and in *Host hardware requirements* on page 2-3

- some target hardware containing a JTAG-capable device supported by RealView ICE (see *Target hardware requirements* on page 2-3).

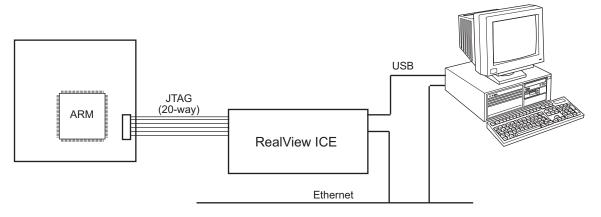

Figure 2-1 shows connections using both the USB and Ethernet cables, and the JTAG 20-way ribbon cable.

Figure 2-1 Connecting the RealView ICE hardware

#### 2.2.2 Connection instructions

To connect the RealView ICE run control unit to your host computer and to the target hardware:

- 1. Ensure the RealView ICE software is installed on the host computer. See the *RealView ICE Installation Guide* for information on how to do this.

- 2. Connect the host computer to the RealView ICE run control unit, using either the USB port or a TCP/IP network connection, as required (see Figure 2-1):

- If you are connecting using the USB port, connect one end of the supplied USB cable to a USB port on the host computer, and the other end of the cable to the USB port on the run control unit.

——Note ———

The USB drivers are installed with the RealView ICE host software.

- If you are connecting across an Ethernet network, connect the Ethernet port of the run control unit to a socket for the Ethernet network using the supplied RJ-45 Ethernet cable.

- If you are using the cross-over cable, connect one end of the cross-over cable to the Ethernet port of the host computer, and the other end to the Ethernet port of the run control unit.

- 3. Connect the RealView ICE run control unit to the target hardware, using the appropriate cable:

- If you want to use the highest JTAG clock speeds, or if you cannot position the run control unit close to the target hardware, use the LVDS cable and probe:

- plug the supplied LVDS probe into the 20-way JTAG header on the target hardware

\_\_\_\_\_ Note \_\_\_\_\_

If there is insufficient clearance to plug the probe directly into the header, you can use the supplied 20-way JTAG cable to connect the probe to the header.

- connect one end of the supplied LVDS cable to the 40-way connector on the probe

- connect the other end of the LVDS cable to the 40-way JTAG B socket on the RealView ICE run control unit.

—— Note ———

Cable selection is performed when the RealView ICE run control unit boots. If you change the cable, you must reboot the unit.

- Otherwise, use the JTAG cable:

- connect one end of the supplied JTAG cable to the 20-way JTAG header on the target hardware

- connect the other end of the cable to the 20-way JTAG A socket on the Real View ICE run control unit.

The IDC connectors used for these cables are keyed using a small protrusion that must be matched up with a slot in the header or socket.

—— Caution ———

If the target hardware does not have a 20-way IDC connector that conforms to the current ARM JTAG connection standard (as described in Appendix A *JTAG Interface Connections*), see *Using nonstandard connectors* on page 2-9.

- 4. If you are using RealView Trace, you have to connect the RealView Trace unit to the RealView ICE unit and to the target board. See *Connecting the RealView Trace hardware* on page 6-7 for information on how to do this.

- 5. Power up the target hardware.

- 6. Connect the external power supply to the RealView ICE run control unit, and to the mains electricity.

- Switch on the power supply. The power LED and the expansion bus power LED both switch on.

- 8. The RealView ICE run control unit firmware is based on an embedded Linux kernel. Therefore, the unit takes a short time to boot up and establish either a network or USB connection. When the unit is booting:

- The CFAC LED lights up, and the STAT LED flashes.

As the RealView ICE run control unit boots, the STAT LED flash rate increases.

- The unit detects which JTAG socket has a cable attached:

- If RealView ICE detects that the LVDS cable and probe are connected to JTAG B socket, it uses them. It also switches on the LVDS LED.

- If RealView ICE detects that a JTAG cable is connected to the JTAG A socket, the LVDS LED remains unlit.

- When the STAT LED is permanently On, the RealView ICE run control unit has finished booting, and is ready to use.

- 9. If your RealView ICE unit is connected to a network, you must now run the Config IP application to configure the network settings, as described in Chapter 3 *Configuring RealView ICE Networking*.

| Yo   | u have only to do the network configuration once.                                |

|------|----------------------------------------------------------------------------------|

| If t | he RealView ICE unit is powered up with only a USB connection, it uses an IF     |

|      | dress of 127.0.0.0. However, if a network cable is also attached, the IP address |

| ass  | ociated with the USB connection is the IP address that you have assigned to      |

| the  | RealView ICE unit, or that it obtains from a DHCP server.                        |

Do not obstruct the ventilation grills on the top and bottom of the RealView ICE unit,

because doing so causes the unit to overheat.

### 2.2.3 Using nonstandard connectors

RealView ICE is supplied with cables that each terminate in a 20-way IDC connector, wired to the current ARM JTAG connection standard (see Appendix A *JTAG Interface Connections*). Box headers suitable for this connector are fitted on all current ARM target hardware, and on several third-party targets.

Some target hardware is fitted instead with a 14-way IDC box header:

- Older ARM target hardware uses the previous ARM JTAG connection standard (as used by EmbeddedICE). This is signal-compatible with the current ARM standard. Use the supplied adaptor card to connect to these targets.

- Some other targets instead use the *Texas Instruments* (TI) JTAG connection standard. This has a different signal assignment to the ARM standards. An adaptor to enable RealView ICE to connect to these targets is available from ARM on request. Quote part number HBI 0068B.

| ——— Caution ———— |  |

|------------------|--|

|------------------|--|

If you use the wrong 20-way to 14-way adaptor, you might damage the target hardware.

If you are not certain of the connection standard that your target hardware uses, you *must* check the reference manual for the target *before* you connect it to the RealView ICE run control unit. This is especially important if you are using a target that has a 14-way IDC box header, or that is not manufactured by ARM Limited.

If the target that you are using does not use an ARM style connector, or if you are designing target hardware, contact ARM Limited for more information.

# 2.2.4 Hot plugging and unplugging the JTAG cable

You can plug and unplug the JTAG cable without affecting the target. This is because the RealView ICE run control unit includes power conditioning and switching circuitry.

You might want to do this if you have a target that is operating without a RealView ICE run control unit connected and you want to examine the target to find out why it is behaving in a particular way. To do this, you must power up the RealView ICE run control unit and configure the connection without disturbing the state of the target. This requires that the RealView ICE run control unit is powered before it is connected to the target.

When unplugging the JTAG connector, you must be aware of the following:

- If you are using an RTCK system, make sure that no communication is taking place between the system and the RealView ICE run control unit. Otherwise, if the RealView ICE unit is waiting for a return clock, it might lock up. In this case, you must power down the RealView ICE unit, and power it back up again.

- If you are not using an RTCK system, the RealView ICE software can handle this situation. However, you must arrange to do a TAP reset using the debugger when you next plug the RealView ICE unit into a target. See *Advanced configuration* on page 4-25 for details.

# 2.3 Using RealView ICE and RealView Trace

When you have connected RealView ICE to your host computer (see *Connecting the RealView ICE hardware* on page 2-5), you are ready to begin using RealView ICE (and RealView Trace if present) with RealView Debugger. See the *RealView Debugger* documentation suite for information on using RealView Debugger.

When you install the RealView ICE software, it adds capabilities to RealView Debugger to enable you to configure a RealView ICE connection using the RVConfig dialog box. This is described in full in Chapter 4 *Configuring a RealView ICE Connection*.

If you have to update the RealView ICE firmware at a later date, to extend the capabilities of the RealView ICE unit for example, you must use the RVI Update utility. This is described in Chapter 7 *Managing the RealView ICE Software*.

Getting Started

# Chapter 3 Configuring RealView ICE Networking

This chapter describes how to configure the network settings for your RealView® ICE run control unit. If you have connected your run control unit to an Ethernet network or directly to the host computer using an Ethernet cross-over cable, you must configure the network settings before you can use the unit for debugging. You have only to configure the network settings once.

If you have connected your run control unit directly to the host computer using a USB cable, and you do not intend to connect it to a network, you do not have to configure the network settings. See *Connection instructions* on page 2-6 for information on connecting up the components.

To configure your RealView ICE run control unit to use the correct network settings for your network:

- 1. Determining the correct network settings on page 3-2

- 2. Starting the RealView ICE Config IP application on page 3-3

- 3. Configuring the network settings on page 3-4

- 4. Restarting your RealView ICE run control unit on page 3-12

- 5. Exiting the RealView ICE Config IP application on page 3-3.

# 3.1 Determining the correct network settings

Before you can configure the network settings, you must first determine the correct network settings for your RealView ICE run control unit. To do this, you must consult with the system administrator for your network.

The information that you require depends on whether or not your network uses DHCP:

- if your network does not use DHCP, see *Not using DHCP*

- if your network uses DHCP, see *Using DHCP*.

## 3.1.1 Not using DHCP

If your network does not use DHCP, you must know:

- the hostname that you want to use for your run control unit (if any)

- the IP address that you want to use for your run control unit

- the default gateway for your network (if it has one)

- the subnet mask for your network.

# 3.1.2 Using DHCP

| If your network uses DHCP, you must know the hostname that you want to use for your run control unit (if any).                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note                                                                                                                                                                                              |

| You do not have to know the IP address for your run control unit, or the default gateway and subnet mask for your network, because these settings are fetched from a DHCP server on your network. |

# 3.2 Starting and exiting the RealView ICE Config IP application

This section describes how to start and exit the RealView ICE Config IP application:

- Starting the RealView ICE Config IP application

- Exiting the RealView ICE Config IP application.

## 3.2.1 Starting the RealView ICE Config IP application

To start the RealView ICE Config IP application:

• On Windows, select Start  $\rightarrow$  Programs  $\rightarrow$  ARM  $\rightarrow$  RealView ICE v3.1  $\rightarrow$  RealView ICE Config IP.

— Note —

If you are using the default Windows XP settings, select **All Programs**.

• On Red Hat Linux, choose the appropriate shortcut. This depends on the version of Red Hat Linux and the desktop environment that you are using. If no desktop shortcut is available, enter the command rviconfigip at the command line.

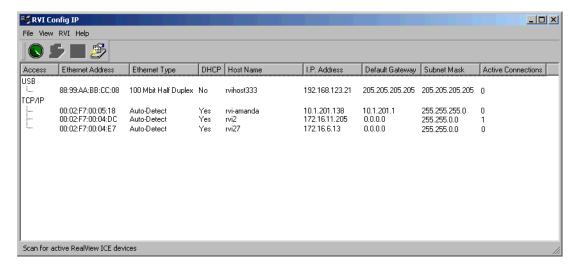

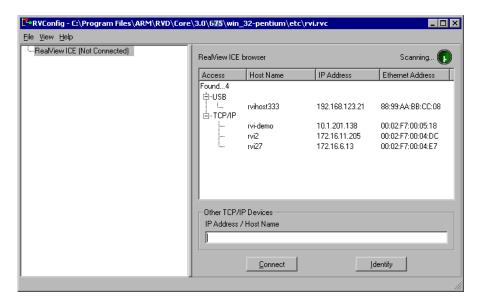

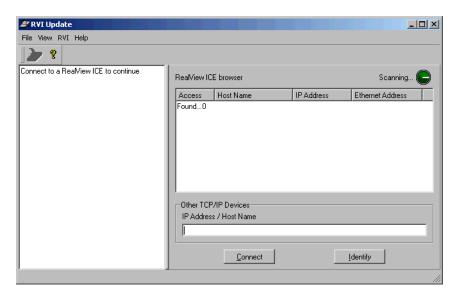

The RealView ICE Config IP application opens, as shown in Figure 3-1.

Figure 3-1 The RealView ICE Config IP application

# 3.2.2 Exiting the RealView ICE Config IP application

To exit the RealView ICE Config IP application, select **Exit** from the **File** menu.

# 3.3 Configuring the network settings

The configuration process depends on the way in which the RealView ICE unit is connected to the host computer, and whether or not you know its Ethernet address:

- If your RealView ICE unit is connected to your local network, but you do not know its Ethernet address, you can select it from the list of available units. See *Configuring by scanning all run control units*

- If you know the Ethernet address of your RealView ICE unit, you can go straight to the Configuration dialog box and enter the address. See *Configuring using an Ethernet address* on page 3-9

- If you have connected your run control unit directly to the host computer using a cross-over cable, you must assign static IP addresses to the host computer and the run control unit. See *Configuring for connection with an Ethernet cross-over cable* on page 3-10.

| Note                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------|

| f you have connected your run control unit directly to the host computer using a US able, you do not have to configure the network settings. |

| Note                                                                                                                                         |

| The toolbar buttons mentioned in the following sections also have equivalent options are <b>RVI</b> menu.                                    |

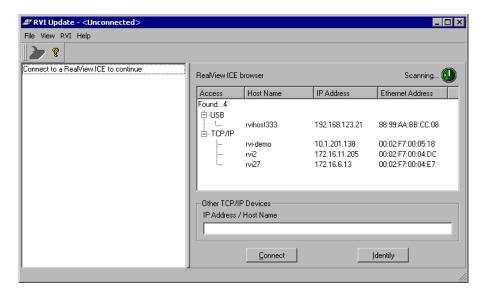

# 3.3.1 Configuring by scanning all run control units

This section describes how to configure the network settings for your RealView ICE run control unit by scanning for all available run control units. You can also configure your run control unit by specifying its Ethernet address, as described in *Configuring using an Ethernet address* on page 3-9.

The configuration process consists of the following steps:

- 1. Scanning for your RealView ICE run control unit

- 2. Identifying and selecting your RealView ICE run control unit on page 3-7

- 3. Configuring your RealView ICE run control unit on page 3-7.

# Scanning for your RealView ICE run control unit

Click **Scan** to scan for run control units that are connected to your local network. The Scan button becomes animated to indicate that a scan is in process. When RealView ICE finds a unit, it adds it to the list of available units, as shown in Figure 3-1 on page 3-3.

If you want to stop scanning, click **Scan**. You can click **Scan** again at any time to force a rescan of available RealView ICE units and update the list.

If you are using DHCP, RealView ICE scans for a DHCP server during the first minute after rebooting. During this period, the Scan tool cannot locate the unit. If the unit is unable to obtain its IP address from a DHCP server, it appears in the RealView ICE Config IP dialog box with the address 127.0.0.2.

If you want the RealView ICE run control unit to try again to obtain its IP settings from a DHCP server, you must first reboot the unit.

The number of active connections shown in the RVI Config IP dialog box might be more than the number of active users, because each user might have multiple active connections. For example, the RealView ICE connection and the RealView Trace connection are both displayed as active connections, or a device might be listed under both USB and TCP/IP if it is accessible by both methods.

## Troubleshooting

This section describes problems you might encounter when attempting to connect to a RealView ICE unit, and what you can do to solve them:

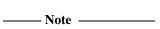

## Multiple programs attempting to scan

Only one program can scan the TCP/IP network or USB ports for available RealView ICE units. If another program is scanning, for example the RVConfig dialog box in RealView Debugger (see *Using the RVConfig dialog* on page 4-3), the RVI Config IP application displays the error message shown in Figure 3-2.

Figure 3-2 Error message when another program is browsing

You must stop one of the programs from scanning. To do this, click **Scan**, or select **Stop Scan** from the **RVI** menu in the application that you want to stop scanning.

#### USB server not accessible

If the USB server is not accessible, the error message shown in Figure 3-3 appears:

Figure 3-3 Error message when no USB devices present

This indicates a problem with your RealView ICE installation. Click **OK**. If you do not want to connect to any devices over a USB connection, you can continue using RealView ICE over only TCP/IP connections. If you want to connect to a device using USB, you must reinstall RealView ICE. If the error persists, there might be a problem with your operating system.

#### Connection times out

The default timeout for establishing a TCP/IP connection is 5 seconds. If you repeatedly get timeouts when attempting to connect to a RealView ICE run control unit, you can change this setting. To do this:

- 1. If the environment variable RVI\_COMMS\_CONNECT\_TIMEOUT does not already exist, then create it.

- 2. Set the value of this variable to the timeout that you want, in seconds. This must be an integer in the range 0-120.

For details of how to create and set an environment variable, see the documentation for the operating system that is supplied with your host computer.

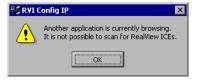

#### Other active connections

If you connect to a RealView ICE run control unit that has other active connections, the RVI Config IP application displays the error message shown in Figure 3-4.

Figure 3-4 Error when other connections are active

If you continue, the changes that you make might interfere with the correct operation of these applications. Do one of the following:

- ensure that the other applications are disconnected, and then click **Yes** to continue using the RealView ICE Config IP application

- click **No** to stop using the RealView ICE Config IP application, and try again later.

## Identifying and selecting your RealView ICE run control unit

To identify and select your RealView ICE run control unit from the list of units found, do one of the following:

• Determine the Ethernet address of your run control unit by reading the label on the side of the unit. Find the entry in the list that has the same Ethernet address, and select it.

- Select an entry in the list and click the **Identify** tool:

- If the four LEDs JTAG, STAT, CFAC and LVDS on your interface (shown in Figure 3-5) flash for 5 seconds, you have selected its entry.

Figure 3-5 The identification LEDs

Otherwise, select another entry and try again.

# Configuring your RealView ICE run control unit

When you have selected your RealView ICE run control unit, you must configure it to use the network settings that you previously determined (see *Determining the correct network settings* on page 3-2):

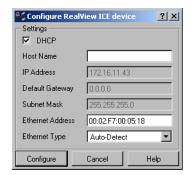

1. Click the **Configure** tool. The Configure RealView ICE device dialog box appears. See Figure 3-6 on page 3-8.

Figure 3-6 The Configure RealView ICE device dialog box

- 2. If you are using DHCP, select **DHCP**. Otherwise, deselect **DHCP**.

- 3. Enter the hostname in the Host Name field. This must contain only the alphanumeric characters (A-Z, a-z, and θ-9) and the character, and must be no more than 255 characters long.

- 4. If you are not using DHCP, enter the required details in the following fields:

- IP Address

- Default Gateway

- Subnet Mask.

\_\_\_\_\_Note \_\_\_\_\_

If you are using DHCP, you do not have to type these settings, because they are allocated from a DHCP server on your network.

- 5. Set the required Ethernet Type:

- if you know the type of network that you are using, select that type

- otherwise, select Auto-Detect.

- 6. Click **Configure**.

The RealView ICE run control unit restarts. While it is restarting, it is not present in the list of units. When it has restarted, it re-appears in the list of units, with its new network settings.

\_\_\_\_\_Note \_\_\_\_\_

If the RealView ICE run control unit is using DHCP, the list of units might display its **IP Address** as 127.0.0.2. This is a dummy address, which the run control unit uses when it fails to obtain an IP address from the DHCP server.

The list of units shows the correct address if the DHCP server has assigned it.

## 3.3.2 Configuring using an Ethernet address

If you have a RealView ICE run control unit that does not have a valid IP address or is on a different subnet, you must manually enter the Ethernet address during configuration.

To configure your RealView ICE run control unit by entering an Ethernet address:

1. Open the required configuration dialog box, which depends on whether or not your run control unit has a USB connection:

If the device has a USB connection, select the device in the USB list and click the Configure tool. The Configure RealView ICE device dialog box appears, as shown in Figure 3-6 on page 3-8.

Alternatively, double-click on the device in the USB list.

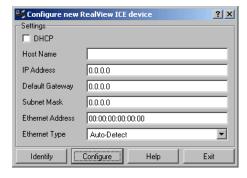

• If the device does not have a USB connection, click the **Config New** tool. The Configure new RealView ICE device dialog box appears, as shown in Figure 3-7.

Figure 3-7 The Configure new RealView ICE device dialog box

2. Determine the Ethernet address of your run control unit by reading the label on the side of the unit, and enter it into the Ethernet Address field.

If you are using the Configure new RealView ICE device dialog box and you want to be certain that you are configuring the correct run control unit, click the **Identify** tool. Verify that the identification LEDs flash (see Figure 3-5 on page 3-7).

- 3. If you are using DHCP, select **DHCP**. Otherwise, deselect **DHCP**.

- 4. Enter the hostname in the Host Name field. This must contain only the alphanumeric characters (A-Z, a-z, and 0-9) and the character, and must be no more than 255 characters long.

| 5. | If you are not usi          | ng DHCP, enter | the required | details in th | e following     | fields |

|----|-----------------------------|----------------|--------------|---------------|-----------------|--------|

|    | 11 ) 0 0 01 01 0 110 0 0101 | .,             | roquirou     |               | • 10110 ;; 111g | 110100 |

- IP Address

- Default Gateway

- Subnet Mask.

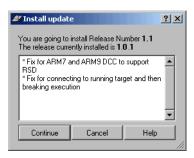

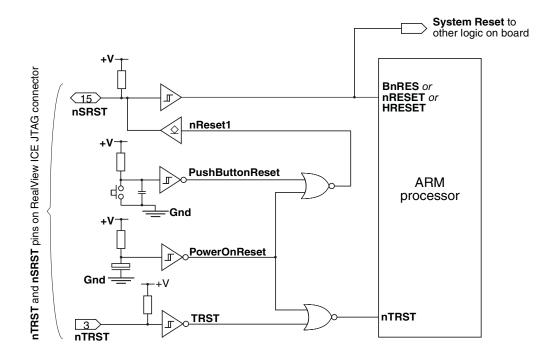

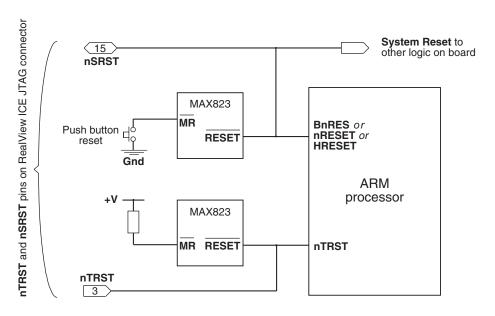

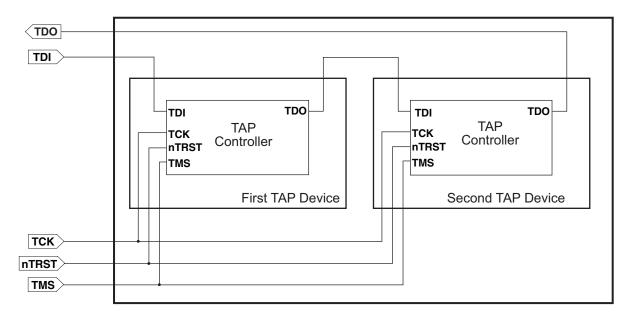

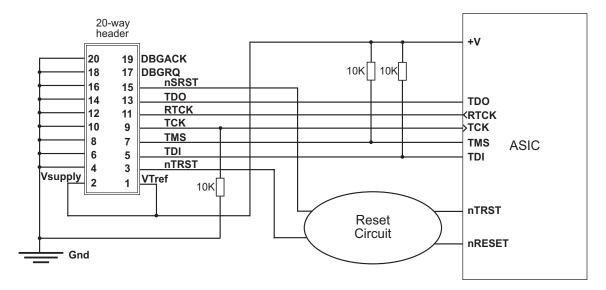

| ——Note |  |