# ARM<sup>®</sup> Firmware Suite

Version 1.4

**Reference Guide**

Copyright © 1999-2002 ARM Limited. All rights reserved. ARM DUI 0102G

### ARM Firmware Suite Reference Guide

Copyright © 1999-2002 ARM Limited. All rights reserved.

#### **Release Information**

**Change History**

| Date           | Issue | Change                                |

|----------------|-------|---------------------------------------|

| September 1999 | А     | New document (internal release)       |

| September 1999 | В     | First release                         |

| February 2000  | С     | Second release                        |

| October 2000   | D     | Third release                         |

| March 2001     | E     | Fourth release                        |

| March 2002     | F     | Fifth release                         |

| September 2002 | G     | Interim release for Excalibur support |

#### **Proprietary Notice**

Words and logos marked with  $^{\otimes}$  or  $^{\bowtie}$  are registered trademarks or trademarks owned by ARM Limited. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

## Contents ARM Firmware Suite Reference Guide

| Prefa  | ce                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | About this document                                                                                                | viii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|        | Further reading                                                                                                    | xi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|        | Feedback                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Introc | luction to the ARM Firmware Suite                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.1    | About the ARM Firmware Suite                                                                                       | 1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.2    | AFS directories and files                                                                                          | 1-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| μHAL   | Application Programming Interfaces                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.1    | About the µHAL APIs                                                                                                | 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.2    | Simple API memory functions                                                                                        | 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.3    | Simple API interrupt functions                                                                                     | 2-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.4    | Simple API MMU and cache functions                                                                                 | 2-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.5    | Simple API timer functions                                                                                         | 2-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.6    |                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.7    |                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.8    | Serial input/output functions, definitions, and macros                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.9    | Extended API initialization functions                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.10   | Extended API interrupt handling functions                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.11   | Extended API software interrupt (SWI) function                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.12   | Extended API MMU and cache functions                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|        | Introd<br>1.1<br>1.2<br><b>µHAL</b><br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11 | Further reading         Feedback         Introduction to the ARM Firmware Suite         1.1       About the ARM Firmware Suite         1.2       AFS directories and files         #HAL Application Programming Interfaces         2.1       About the µHAL APIs         2.2       Simple API memory functions         2.3       Simple API interrupt functions         2.4       Simple API MMU and cache functions         2.5       Simple API support functions         2.6       Simple API support functions         2.7       Simple API LED control functions         2.8       Serial input/output functions, definitions, and macros         2.9       Extended API interrupt handling functions         2.10       Extended API software interrupt (SWI) function |

|           | 2.13  | Extended API processor execution mode functions | 2-43 |

|-----------|-------|-------------------------------------------------|------|

|           | 2.14  | Extended API timer functions                    | 2-46 |

|           | 2.15  | Extended API coprocessor access functions       | 2-49 |

|           | 2.16  | Library support functions                       |      |

| Chapter 3 | ۵RM   | Boot Monitor                                    |      |

| enapter e | 3.1   | About the boot monitor                          | 3-2  |

|           | 3.2   | Common commands for the boot monitor            |      |

|           | 3.3   | Rebuilding the boot monitor                     |      |

| Chapter 4 | Oper  | rating Systems and µHAL                         |      |

| onuptor 4 | 4.1   | About porting operating systems                 | 1-2  |

|           | 4.2   | Simple operating systems                        |      |

|           | 4.3   | Complex operating system                        |      |

| Chapter 5 | Anac  |                                                 |      |

| Chapter 5 | Ange  |                                                 | 5.0  |

|           | 5.1   | About Angel                                     |      |

|           | 5.2   | µHAL-based Angel                                |      |

|           | 5.3   | Building a µHAL-based Angel                     |      |

|           | 5.4   | Source file descriptions                        |      |

|           | 5.5   | Device drivers                                  |      |

|           | 5.6   | Developing applications with Angel              |      |

|           | 5.7   | Angel in operation                              |      |

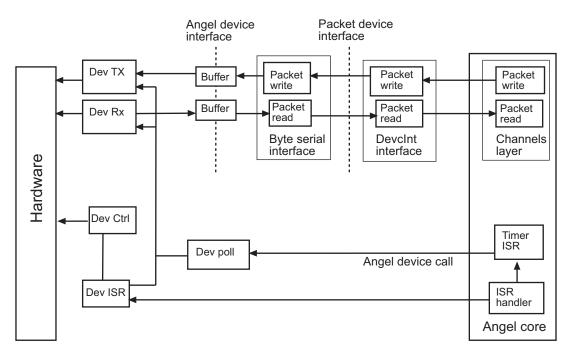

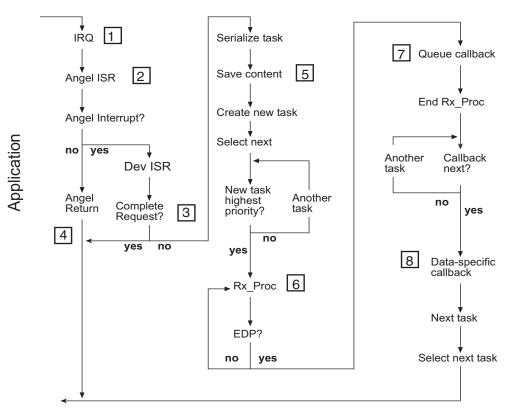

|           | 5.8   | Angel communications architecture               | 5-46 |

| Chapter 6 | Flasl | h Library Specification                         |      |

|           | 6.1   | About the flash library                         | 6-2  |

|           | 6.2   | About flash management                          | 6-4  |

|           | 6.3   | ARM flash library specifications                | 6-5  |

|           | 6.4   | Functions listed by type                        | 6-14 |

|           | 6.5   | Flash library functions                         | 6-19 |

|           | 6.6   | File processing functions                       | 6-35 |

|           | 6.7   | SIB functions                                   | 6-40 |

|           | 6.8   | Using the library                               | 6-47 |

| Chapter 7 | Usin  | g the ARM Flash Utilities                       |      |

| •         | 7.1   | About the AFU                                   |      |

|           | 7.2   | Starting the AFU                                |      |

|           | 7.3   | AFU commands                                    |      |

|           | 7.4   | The Boot Flash Utility                          |      |

|           | 7.5   | BootFU commands                                 |      |

| Chapter 8 | PCI   | Management Library                              |      |

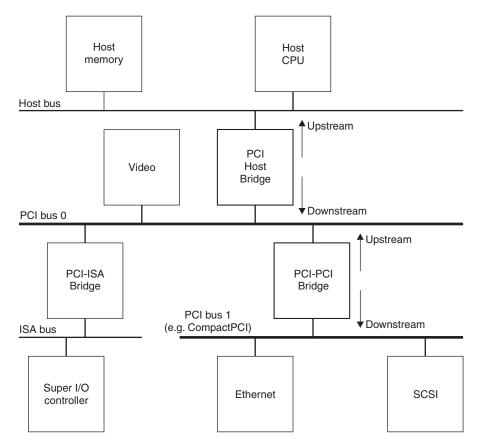

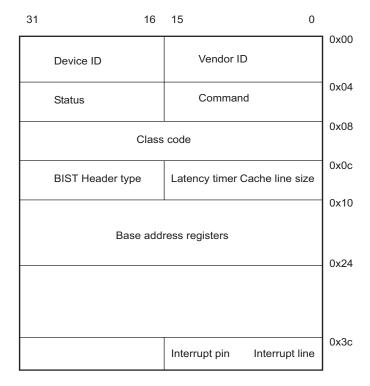

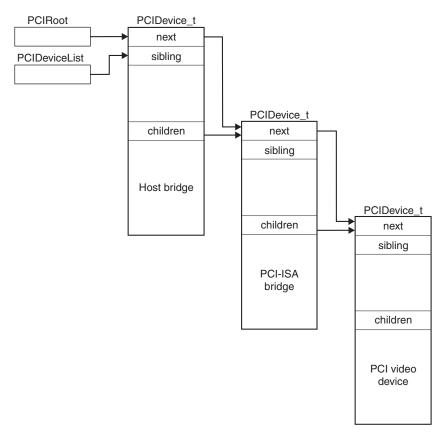

|           | 8.1   | About PCI                                       | 8-2  |

|           | 8.2   | PCI configuration                               |      |

|           | 8.3   | The PCI library                                 |      |

|           | 0.0   |                                                 |      |

Copyright © 1999-2002 ARM Limited. All rights reserved.

|            | 8.4   | PCI library functions and definitions                 | 8-14 |

|------------|-------|-------------------------------------------------------|------|

|            | 8.5   | About µHAL PCI extensions                             | 8-16 |

|            | 8.6   | µHAL PCI function descriptions                        | 8-17 |

|            | 8.7   | Example PCI device driver                             | 8-23 |

| Chapter 9  | Usin  | g the DHCP Utility                                    |      |

| •          | 9.1   | DHCP overview                                         | 9-2  |

|            | 9.2   | Using DHCP                                            | 9-3  |

|            | 9.3   | Configuration files                                   | 9-4  |

| Chapter 10 | Chai  | ning Library                                          |      |

| •          | 10.1  | About exception chaining                              | 10-2 |

|            | 10.2  | The SWI interface                                     |      |

|            | 10.3  | Chain structure                                       | 10-8 |

|            | 10.4  | Owners and users                                      | 10-9 |

|            | 10.5  | Rebuilding the chaining library                       |      |

| Chapter 11 | Libra | aries and Support Code                                |      |

|            | 11.1  | Library naming                                        | 11-2 |

|            | 11.2  | Rebuilding libraries                                  |      |

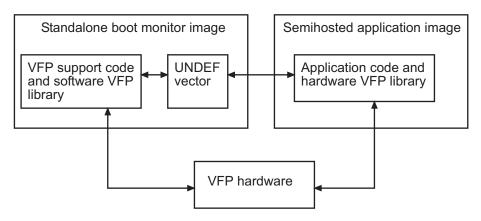

|            | 11.2  | Support for VFP                                       |      |

|            | 11.4  | Support for the ADS C library                         |      |

| Appendix A |       | Eirmwara Suita an Integrator                          |      |

| Appendix A |       | Firmware Suite on Integrator                          |      |

|            | A.1   | About Integrator                                      |      |

|            | A.2   | Integrator-specific commands for boot monitor         |      |

|            | A.3   | Using the boot monitor on Integrator                  |      |

|            | A.4   | Angel on Integrator                                   |      |

|            | A.5   | PCI initialization on Integrator (Integrator/AP only) | A-26 |

| Appendix B |       | Firmware Suite on Prospector                          |      |

|            | B.1   | About Prospector                                      |      |

|            | B.2   | Prospector-specific commands for boot monitor         |      |

|            | B.3   | Using boot monitor on Prospector                      |      |

|            | B.4   | Angel on Prospector                                   | B-10 |

| Appendix C | ARM   | Firmware Suite on the Intel IQ80310 and IQ80321       |      |

|            | C.1   | About the IQ80310 development kit                     | C-2  |

|            | C.2   | About the IQ80321 development kit                     |      |

|            | C.3   | IQ-specific commands for boot monitor                 | C-4  |

|            | C.4   | Using boot monitor on the Intel IQ systems            | C-7  |

|            | C.5   | Angel on the Intel IQ systems                         |      |

|            | C.6   | Flash recovery                                        | C-11 |

|            |       |                                                       |      |

| Appendix D | ARM   | Firmware Suite on the ARM Evaluator-7T                      |   |

|------------|-------|-------------------------------------------------------------|---|

|            | D.1   | About Evaluator-7T D-2                                      | 2 |

|            | D.2   | Evaluator-7T-specific commands for boot monitor D-3         | 3 |

|            | D.3   | Using boot monitor on the Evaluator-7T D-6                  | 6 |

|            | D.4   | Angel on the Evaluator-7T D-6                               |   |

|            | D.5   | Manufacturing image D-s                                     |   |

| Appendix E | ARM   | Firmware Suite on the Agilent AAED-2000                     |   |

| ••         | E.1   | About AAED-2000 E-2                                         | 2 |

|            | E.2   | AAED-2000-specific commands for boot monitor E-3            | 3 |

|            | E.3   | Using boot monitor on AAED-2000 E-6                         |   |

|            | E.4   | Angel on the AAED-2000 E-S                                  |   |

| Appendix F | Integ | rator CM/922T-XA10                                          |   |

| ••         | F.1   | About the Integrator/CM922T-XA10 F-2                        | 2 |

|            | F.2   | Excalibur922T system-specific commands for boot monitor F-3 |   |

|            | F.3   | Using the boot monitor on Excalibur922T F-                  |   |

| Appendix G | API ( | Quick Reference                                             |   |

|            | G.1   | μHAL                                                        | 2 |

|            | G.2   | Flash APIsG-8                                               |   |

|            | G.3   | PCI APIsG-13                                                |   |

|            | Glos  | sary                                                        |   |

## Preface

This preface introduces the ARM Firmware Suite and its reference documentation. It contains the following sections:

- About this document on page viii

- *Further reading* on page xi

- *Feedback* on page xiii.

### About this document

This book provides a guide on how to setup and use the ARM Firmware Suite. It describes its major components and features, and how to use them to develop applications for ARM-based hardware platforms.

#### Intended audience

This book is written for hardware and software developers to aid the development of ARM-based products and applications. It assumes that you are familiar with ARM architectures and have an understanding of computer hardware.

A simplified guide to running the demonstration applications is provided in the *ARM Firmware Suite User Guide*. See *ARM publications* on page xi for additional guides that describe other ARM products in detail.

#### Using this book

This document is organized into the following chapters:

#### Chapter 1 Introduction to the ARM Firmware Suite

Read this chapter for a brief introduction to the *ARM Firmware Suite* (AFS). A more detailed introduction is provided in the *ARM Firmware Suite User Guide*.

#### Chapter 2 µHAL Application Programming Interfaces

Read this chapter for information about the µHAL applications programming interface including parameter types and functions.

#### Chapter 3 ARM Boot Monitor

Read this chapter for a description of the boot monitor and its command-line interface.

#### Chapter 4 Operating Systems and µHAL

Read this chapter for a description how operating systems are ported to a platform which has  $\mu$ HAL ported to it.

#### Chapter 5 Angel

Read this chapter for a description of the Angel debug monitor and AFS.

#### Chapter 6 Flash Library Specification

Read this chapter for reference information about the flash library, flash management, and the firmware flash library functions.

#### Chapter 7 Using the ARM Flash Utilities

Read this chapter for information about using the *ARM Flash Utility* (AFU) and *Boot Flash Utility* (BootFU).

#### Chapter 8 PCI Management Library

Read this chapter for information about PCI management. This chapter describes how PCI resources are initialized and managed, and describes the PCI management functions.

#### Chapter 9 Using the DHCP Utility

Read this chapter for information on using the remote-booting system.

#### **Chapter 10** Chaining Library

Read this chapter for a description of the chaining library.

#### Chapter 11 Libraries and Support Code

Read this chapter for a description of support code used in AFS.

#### Appendix A ARM Firmware Suite on Integrator

Read this appendix for a description of the Integrator boards and the board-specific features of AFS

#### Appendix B ARM Firmware Suite on Prospector

Read this appendix for a description of the Prospector boards and the board-specific features of AFS.

#### Appendix C ARM Firmware Suite on the Intel IQ80310 and IQ80321

Read this appendix for a description of the Intel XScale board and the board-specific features of AFS.

#### Appendix D ARM Firmware Suite on the ARM Evaluator-7T

Read this appendix for a description of the ARM Evaluator-7T Board and the board-specific features of AFS.

#### Appendix E ARM Firmware Suite on the Agilent AAED-2000

Read this appendix for a description of the Agilent AAED-2000 board and the board-specific features of AFS.

#### Appendix G API Quick Reference

Read this appendix for an overview of all of the APIs used in AFS.

### **Typographical conventions**

The following typographical conventions are used in this book:

| typewriter         | Denotes text that can be entered at the keyboard, such as commands, file<br>and program names, and source code.                                 |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>type</u> writer | Denotes a permitted abbreviation for a command or option. The<br>underlined text can be entered instead of the whole command or option<br>name. |

| typewriter         | italic                                                                                                                                          |

|                    | Denotes arguments to commands and functions where the argument is to<br>be replaced by a specific value                                         |

| italic             | Highlights important notes, introduces special terminology, denotes cross-references, and citations.                                            |

| bold               | Highlights interface elements, such as menu names. Also used for emphasis in descriptive lists and for ARM processor signal names.              |

| typewriter k       | bloc                                                                                                                                            |

Denotes language keywords when used outside example code.

## **Further reading**

This section lists publications from ARM and third parties that provide additional information about developing on ARM processors.

#### **ARM publications**

The following publication provides a simplified guide to running the demonstration applications:

• ARM Firmware Suite User Guide (ARM DUI 0136).

The following publications provide information about ARM Integrator products:

- ARM Integrator/CM920T User Guide (ARM DDI 0097)

- ARM Integrator/CM940T User Guide (ARM DDI 0125)

- ARM Integrator/CM720T User Guide (ARM DDI 0126)

- ARM Integrator/CM740T User Guide (ARM DDI 0124)

- ARM Integrator/CM7TDMI User Guide (ARM DDI 0126)

- ARM Integrator/SP User Guide (ARM DUI 0099)

- ARM Integrator/AP User Guide (ARM DUI 0098).

The following publication provides information about ARM Prospector products:

• ARM Prospector/P1100 User Guide (ARM DUI 122).

The following publications provide information about ARM hardware and software debugging tools:

- ARM RMHost User Guide (ARM DUI 0137)

- ARM RMTarget Integration Guide (ARM DUI 0142)

- *Multi-ICE User Guide* (ARM DUI 0048).

The following publication provides reference information about ARM architecture:

• AMBA Specification (ARM IHI 0011).

The following publications provide information about the ARM Developer Suite:

- ADS Getting Started (ARM DUI 0064)

- ADS Tools Guide (ARM DUI 0067)

- ADS Debuggers Guide (ARM DUI 0066)

- ADS Debug Target Guide (ARM DUI 0058)

- ADS Developer Guide (ARM DUI 0056)

- ADS CodeWarrior IDE Guide (ARM DUI 0065).

Further information can be obtained from the ARM web site at:

http://www.arm.com

#### Other publications

The following publication provides reference information about ARM architecture:

- ARM Architecture Reference, David Seal, Addison Wesley, ISBN 0-201-73719-1

- *ARM System-On-Chip Architecture*, Steve Furber, Addison Wesley, ISBN 0-201-67519-6.

The following publications provide information and guidelines for developing products for Microsoft Windows CE:

- HARP Enclosure Requirements for Microsoft<sup>®</sup> Windows<sup>®</sup> CE 1998 Microsoft Corporation

- Standard Development Board for Microsoft<sup>®</sup> Windows<sup>®</sup> CE 1998 Microsoft Corporation.

Further information on Microsoft Windows CE is available from the Microsoft web site:

http://www.microsoft.com

The following publication provides information about  $\mu$ C/OS-II:

• *MicroC/OS-II, The Real-Time Kernel*, Jean Labrosse, R&D Technical Books, ISBN 0-87930-543-6.

## Feedback

Feedback on both AFS and the documentation is welcome.

#### Feedback on this book

If you have any comments on this book, please send email to errata@arm.com giving:

- the document title

- the document number

- the page number(s) to which your comments apply

- a concise explanation of your comments.

General suggestions for additions and improvements are also welcome.

#### Feedback on the ARM Firmware Suite

If you have any problems with the ARM Firmware Suite, please contact your supplier. To help them provide a rapid and useful response, please give:

- details of the release you are using

- details of the platform you are running on, such as the hardware platform, operating system type and version

- a small standalone sample of code that reproduces the problem

- a clear explanation of what you expected to happen, and what actually happened

- the commands you used, including any command-line options

- sample output illustrating the problem

- the version string of the tool used, including the version number and date.

Preface

## Chapter 1 Introduction to the ARM Firmware Suite

This chapter introduces the AFS components and utilities used to develop applications and operating systems on ARM-based systems. It contains the following sections:

- About the ARM Firmware Suite on page 1-2

- *AFS directories and files* on page 1-3.

Refer to the ARM Firmware Suite User Guide for a more detailed introduction to AFS.

## 1.1 About the ARM Firmware Suite

AFS provides:

#### µHAL libraries

$\mu$ HAL (pronounced *Micro-HAL*) is the ARM Hardware Abstraction Layer that is the basis of the AFS.  $\mu$ HAL is a set of low-level functions that simplify the porting of operating systems and applications.

#### **Flash library**

The flash library provides an API for programming and reading flash memory. The API provides access to individual blocks or words in flash, and access to images and user data.

#### **Development environment**

AFS is an easy-to-use environment for evaluating ARM-based platforms. The library APIs enable rapid development of applications and device drivers. Reusable code is provided to help develop applications and product architectures on a wide range of ARM and third-party development platforms.

AFS is compatible with the ARM Development Suite (ADS 1.0 or higher). It supports the Angel debug monitor, Multi-ICE (if the target board supports it), and third-party debug monitors.

#### **Additional components**

Additional components provided with AFS include a boot monitor, generic applications, and board-specific applications. Use these components to verify that your development board is working correctly. You can use the source code for the applications as a starting point for your own applications.

#### Additional libraries

AFS supplies libraries for specialized hardware. For example, the supplied PCI library supports the PCI bus on the Integrator board.

- **Angel** A version of Angel that has been implemented using µHAL is included with AFS.

- $\mu$ C/OS-II AFS includes a port of  $\mu$ C/OS-II for the ARM architecture using the  $\mu$ HAL interfaces.

## 1.2 AFS directories and files

This section describes the directories created by the AFS installer. Throughout this book there are examples of source code provided as part of AFS. The path names used assume that you installed AFS in the default directory AFSv1\_4.

#### 1.2.1 AFS installation layout

The ARM Firmware Suite installs a range of directories below the AFSv1\_4 install directory:

| Boards     | Subdirectories of this directory contain utilities and documentation relevant to the hardware on supported platforms.                                          |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Components | This directory contains additional online documentation for AFS.                                                                                               |

| Demos      | Subdirectories of this directory contain pre-built executable example images which can be loaded and run on the appropriate platform.                          |

| docs       | This directory contains the online documentation for AFS.                                                                                                      |

| Examples   | This directory contains simple example source code and project files.                                                                                          |

| Images     | Subdirectories of this directory contain pre-built executable images of the utilities provided with each platform.                                             |

| Include    | This directory contains the header files for AFS on supported platforms.                                                                                       |

| lib        | Subdirectories of this directory contain pre-built libraries for the AFS components that build as libraries.                                                   |

| Source     | This directory contains the source code for AFS on supported platforms. Not all modules are provided in source form. See <i>AFS source code organization</i> . |

#### 1.2.2 AFS source code organization

In order to understand the ARM Firmware Suite, it is useful to know how the source code is organized in the AFSv1\_4\Source directory. Each library or module is organized into generic, processor, and board-specific code. In addition, there are build directories for each individual board. For example, it is possible to build versions of  $\mu$ HAL for

Integrator using a range of processors such as an ARM7TDMI or ARM920T. In these cases, only the processor-specific code differs. The following subdirectories are contained in most module directories:

- Boards Subdirectories of this directory contain the board-specific code. For example, the Integrator-specific code for the µHAL library is found in AFSv1\_4\Source\uHAL\Boards\INTEGRATOR. The board-specific code might be a combination of board definitions (such as the memory layout and the location of the interrupt controller) and code (such as code to turn the LEDs on and off).

- Build Subdirectories of this directory contain the build files and built images for each supported board. For example, the ARM720T variant of µHAL for the Integrator is built within the AFSv1\_4\Source\uHAL\Build\Integrator720T.b subdirectory.

- h This directory contains available routine definitions and board-independent and processor-independent definitions.

- Sources This directory contains the board-independent module code. The directory itself contains no board-specific or processor-specific software, although parts of it may be conditionally compiled for either standalone or semihosted usage.

Source directories for some of the more complex modules,  $\mu$ HAL for example, contain additional subdirectories:

- docs This directory contains additional documentation for the module.

- Processors This directory contains processor-specific code. Most processor-specific code is involved with memory management unit and cache support.

- tools This directory contains build tools such as, for example, a Perl script that translates assembler-definition files into C-definition files.

## Chapter 2 µHAL Application Programming Interfaces

This chapter describes the simple and extended APIs to  $\mu$ HAL. It contains the following sections:

- *About the µHAL APIs* on page 2-2

- Simple API memory functions on page 2-4

- Simple API interrupt functions on page 2-8

- Simple API MMU and cache functions on page 2-11

- Simple API timer functions on page 2-13

- Simple API support functions on page 2-19

- Simple API LED control functions on page 2-21

- Serial input/output functions, definitions, and macros on page 2-25

- Extended API initialization functions on page 2-31

- Extended API interrupt handling functions on page 2-33

- Extended API software interrupt (SWI) function on page 2-38

- Extended API MMU and cache functions on page 2-39

- Extended API processor execution mode functions on page 2-43

- Extended API timer functions on page 2-46

- Extended API coprocessor access functions on page 2-49

- *Library support functions* on page 2-51.

## 2.1 About the µHAL APIs

This section provides an overview of the general APIs provided by  $\mu$ HAL. See  $\mu$ HAL *PCI function descriptions* on page 8-17 for a description of PCI functions contained in  $\mu$ HAL.

#### 2.1.1 µHAL-specific function types

$\mu$ HAL uses three function types that are abstracted to make interface routines easier to use. These are described in Table 2-1.

#### Table 2-1 Parameter types

| Description                                                                                    | Syntax                                   |

|------------------------------------------------------------------------------------------------|------------------------------------------|

| A pointer to a function with no argument. The function does not return a value.                | <pre>typedef void (*PrVoid)(void);</pre> |

| A pointer to a function with one integer argument. The function does not return a value.       | typedef void (*PrHandler)(unsigned int); |

| A pointer to a function with no argument. The function returns a PrVoid pointer to a function. | typedef PrVoid (*PrPrVoid)(void);        |

For example, with the uHALr\_RequestTimer() declaration:

an interrupt handler can be declared as:

void TickTimer(unsigned int interrupt)

and registered with µHAL using:

uHALr\_RequestSystemTimer(TickTimer, "test");

#### 2.1.2 Simple and extended API functions

Using the  $\mu$ HAL simple API does not require an understanding of how  $\mu$ HAL works, or of the ARM architecture. Using the  $\mu$ HAL extended API requires an understanding of how  $\mu$ HAL functions. All functions and type definitions are contained in AFSv1\_4\Source\uHAL\h\uhal.h and AFSv1\_4\Source\uHAL\h\cdefs.h.

\_\_\_\_\_ Note \_\_\_\_\_

You can find several demonstration programs that use this interface in the uHALDemos subdirectory of the AFS installation. The code examples used in this section are taken from these demonstration programs.

2.1.3 Rebuilding the µHAL library

Use the project files or makefiles to rebuild the Library.

#### PC project files

You can build the library using ADS 1.0 (or higher) CodeWarrior project files (.mcp).

#### Unix makefile

The CD has a makefile for use in a Unix environment.

There is a makefile for rebuilding the library for a single development board and processor combination. For example, if you installed to \AFSv1\_4 use \AFSv1\_4\Source\uHAL\Build\Integrator940T.b\makefile to rebuild the library for the Integrator board with an ARM940T processor.

You must maintain the hierarchy of the CD directories created by the installer. The makefile defines R00T as the root of the build tree and is required by the make program. The directory T00LS contains build tools of various kinds.

## 2.2 Simple API memory functions

This section describes the set of functions that are used to find free memory in the system, and to allocate and free heap storage. Free memory is memory that is not used by  $\mu$ HAL itself or a debug agent. Prototypes for all of these functions are available in AFSv1\_4\Source\uHAL\h\uhal.h.

The memory functions are:

- uHALr\_StartOfRam()

- *uHALr\_EndOfFreeRam()*

- *uHALr\_EndOfRam()* on page 2-5

- *uHALr\_HeapAvailable()* on page 2-5

- *uHALr\_InitHeap()* on page 2-5

- *uHALr\_malloc()* on page 2-5

- *uHALr\_free()* on page 2-6.

There is an example of a program that allocates and de-allocates heap storage in *Example of heap allocation and de-allocation* on page 2-7.

#### 2.2.1 uHALr\_StartOfRam()

This function returns the address of the first free uninitialized RAM location.

#### Syntax

void \*uHALr\_StartOfRam(void)

#### **Return value**

Returns the address of the first available RAM location.

#### 2.2.2 uHALr\_EndOfFreeRam()

This function returns the address of the last available RAM location.

#### Syntax

void \*uHALr\_EndOfFreeRam(void)

#### **Return value**

Returns the address of the last available RAM location.

#### 2.2.3 uHALr\_EndOfRam()

This function returns the address of the last RAM location.

#### Syntax

void \*uHALr\_EndOfRam(void)

#### **Return value**

Returns the address of last RAM location.

#### 2.2.4 uHALr\_HeapAvailable()

This function returns a flag to indicate whether this port of the  $\mu$ HAL library includes support for heap management.

#### Syntax

int uHALr\_HeapAvailable(void)

#### **Return value**

Returns one of the following:

| 1 If the heap management functions are included in t | he library. |

|------------------------------------------------------|-------------|

|------------------------------------------------------|-------------|

**0** If heap management functions are not included.

#### 2.2.5 uHALr\_InitHeap()

This function initializes the heap. It must be called before any memory allocation or de-allocation is attempted.

#### Syntax

void uHALr\_InitHeap(void)

#### 2.2.6 uHALr\_malloc()

This function allocates contiguous storage from the heap.

#### Syntax

void \*uHALr\_malloc(unsigned int size)

| where: |                                            |

|--------|--------------------------------------------|

| size   | is the number of bytes of memory required. |

#### **Return value**

| Returns |                                                               |

|---------|---------------------------------------------------------------|

| 0       | If size is 0.                                                 |

| -1      | If the memory cannot be allocated.                            |

| pointer | If successful, a pointer to the allocated memory is returned. |

#### 2.2.7 uHALr\_free()

This routine frees previously allocated memory pointed at by memPtr.

#### Syntax

void uHALr\_free(void \*memPtr)

where:

*memPtr* Is a pointer to the heap memory to be freed. This value must not be -1. If the value is 0, the function returns without taking any action.

#### 2.2.8 Example of heap allocation and de-allocation

Example 2-1 shows an example of a program that allocates and de-allocates heap storage. You can find a similar program in uHALDemos\Sources\heap.c.

#### Example 2-1 Allocating and de-allocating heap storage

```

#include "uhal.h"

int main (int argc, int *argv[])

{

int i ;

void *memP ;

uHALr_printf("*** HEAP Allocation/Deallocation ***\n");

uHALr_InitHeap() ;

// init

for (i = 0 ; i < 16 ; i++) { // allocate and free some memory

uHALr_printf("malloc'ing 0x%X bytes...", i * 16) ;

memP = uHALr_malloc(i * 16) ;

uHALr_printf("@ 0x%X\n", memP) ;

uHALr_free(memP) ;

}

return (OK);

}

```

## 2.3 Simple API interrupt functions

µHAL assumes that interrupts occur using IRQs. These routines allow you to:

- install a generic interrupt handler

- request control of a particular interrupt

- enable and disable that interrupt.

Your application can install different interrupt handlers for different interrupts, or install a single handler for many interrupts.

When an interrupt occurs,  $\mu$ HAL traps it and calls the appropriate handler routine, passing it the number of the interrupt that occurred.

\_\_\_\_ Note \_\_\_\_\_

$\mu$ HAL does not provide any support to the application for finding the source of interrupts. It is the responsibility of the board-specific code to map the programmable interrupt controller format to and from a 32-bit quantity.

The interrupt functions are:

- *uHALr\_InitInterrupts()*

- *uHALr\_RequestInterrupt()* on page 2-9

- *uHALr\_FreeInterrupt()* on page 2-9

- *uHALr\_EnableInterrupt()* on page 2-10

- *uHALr\_DisableInterrupt()* on page 2-10.

#### 2.3.1 uHALr\_InitInterrupts()

This function is called once on startup by the application. It initializes the  $\mu$ HAL internal interrupt structures. This must be called before installing a new IRQ handler.

#### Syntax

void uHALr\_InitInterrupts(void)

#### 2.3.2 uHALr\_RequestInterrupt()

This function assigns a high-level handler routine to the specified interrupt. It sets up the internal structures, but does not activate the interrupt.

#### Syntax

where:

| intNum  | Is the number of the interrupt to be processed.                     |

|---------|---------------------------------------------------------------------|

| handler | Is a pointer to the routine that processes the interrupt.           |

| devname | Is a pointer to a string identifying the function of the interrupt. |

#### **Return value**

| Returns one of the following: |                                                  |  |

|-------------------------------|--------------------------------------------------|--|

| 0                             | If successful.                                   |  |

| -1                            | If <i>intNum</i> is unknown or already assigned. |  |

#### 2.3.3 uHALr\_FreeInterrupt()

This function removes the high-level handler from the specified interrupt.

\_\_\_\_\_Note \_\_\_\_\_

An application must always call uHALr\_DisableInterrupt() before calling this routine. Call uHALr\_FreeInterrupt() before changing the routine associated with an interrupt.

#### Syntax

int uHALr\_FreeInterrupt(unsigned int intNum)

where:

*intNum* Is the number of the interrupt to be freed.

#### **Return value**

Returns one of the following:

| 0 | If successful. |

|---|----------------|

|   |                |

-1 If *intNum* is unknown, reserved, or not allocated.

#### 2.3.4 uHALr\_EnableInterrupt()

This function enables the specified interrupt. On many ARM-based systems, this is a two-step process. It enables an on-board interrupt controller, and then it enables the interrupt mask on the processor.

#### Syntax

void uHALr\_EnableInterrupt(unsigned int intNum)

where:

*intNum* Is the number of the interrupt to be enabled.

#### 2.3.5 uHALr\_DisableInterrupt()

This function disables the specified interrupt. On many ARM-based systems, interrupts are enabled and disabled at two stages:

- an on-board controller

- the interrupt mask on the processor.

The uHALr\_DisableInterrupt() function disables the interrupt on the interrupt controller and does not affect masking by the processor.

#### Syntax

void uHALr\_DisableInterrupt(unsigned int intNum)

where:

*intNum* Is the number of the interrupt to be disabled. The routine has no effect if the number is not in the range of valid interrupts.

## 2.4 Simple API MMU and cache functions

On processors that support it, µHAL allows an application to:

- Turn virtual memory on and off using the *Memory Management Unit* (MMU). (On systems that use the MMU to remap read-only memory at address 0, the MMU cannot be disabled.)

- Enable and disable the caches.

These functions are:

- *uHALr\_ResetMMU()*

- uHALr\_InitMMU()

- *uHALr\_EnableCache()* on page 2-12

- *uHALr\_DisableCache()* on page 2-12.

*Memory management and cache code example* on page 2-12 includes an example of a basic cache manipulation program.

#### 2.4.1 uHALr\_ResetMMU()

This function safely resets the MMU (and caches) to a fully disabled state (all OFF), irrespective of the state they were originally in. If the MMU cannot be disabled, this function has no effect.

#### Syntax

void uHALr\_ResetMMU(void)

#### 2.4.2 uHALr\_InitMMU()

This function initializes the MMU to a default one-to-one mapping. This mapping also defines the types of access allowed to each area according to execution mode. For example, flash can be written in Supervisor mode, but not User mode.

#### Syntax

void uHALr\_InitMMU(int mode)

where:

*mode* Is any combination of the MMU mode flags and cache bit flags, EnableMMU, IC\_ON, DC\_ON, and WB\_ON. See also *uHALir\_WriteCacheMode()* on page 2-42.

#### 2.4.3 uHALr\_EnableCache()

This function provides a way to enable all caches that are supported by the processor.

#### Syntax

void uHALr\_EnableCache(void)

#### 2.4.4 uHALr\_DisableCache()

This function disables all caches that are supported by the processor.

#### Syntax

void uHALr\_DisableCache(void)

#### 2.4.5 Memory management and cache code example

Example 2-2 is an example of a simple cache manipulation program. A similar program is in uHALDemos\Sources\simple-caches.c.

#### Example 2-2 MMU and cache

```

#include "uhal.h"

#include "mmu_h.h"

int main (int argc, int *argv[]) {

uHALr_printf("Simple Cache Usage [v1.0]\n") ;// who are we?

uHALr_printf("Resetting caches...") ; // Reset the caches to a known state

uHALr_ResetMMU() ;

uHALr_printf("done\n") ;

uHALr_printf("Enabling the MMU and all caches...") ;// Init MMU to all on

uHALr_InitMMU(IC_ON | DC_ON | WB_ON | EnableMMU) ;

uHALr_printf("done\n") ;

uHALr_printf("Disabling all caches...") ; // Disable the caches

uHALr_DisableCache() ;

uHALr_printf("done\n") ;

// Finally, enable all of the caches

uHALr_printf("Enabling all caches...") ;

uHALr_EnableCache() ;

uHALr_printf("done\n") ;

return (OK);// go home

}

```

## 2.5 Simple API timer functions

$\mu$ HAL provides a set of routines that allow an application to use a timer as a system or operating system timer. This is the simplest way to use timers in  $\mu$ HAL.

$\mu$ HAL also provides generic timer access routines that give more direct access, although with a little more complexity, to the timers in the system.

The timer functions are:

- *uHALr\_CountTimers()*

- uHALr\_InitTimers()

- *uHALr\_RequestSystemTimer()* on page 2-14

- *uHALr\_InstallSystemTimer()* on page 2-14

- *uHALr\_RequestTimer()* on page 2-15

- *uHALr\_InstallTimer()* on page 2-16

- *uHALr\_FreeTimer()* on page 2-16

- *uHALr\_GetTimerInterval()* on page 2-16

- *uHALr\_SetTimerInterval()* on page 2-17

- *uHALr\_GetTimerState()* on page 2-17

- *uHALr\_SetTimerState()* on page 2-18

- *uHALr\_EnableTimer()* on page 2-18

- *uHALir\_GetSystemTimer()* on page 2-48.

System timer programming example on page 2-15 shows how to use a system timer.

#### 2.5.1 uHALr\_CountTimers()

This function returns the number of timers that are supported by the target.

#### Syntax

unsigned int uHALr\_CountTimers(void)

#### **Return value**

Returns the number of timers supported by the target.

#### 2.5.2 uHALr\_InitTimers()

This function must be called before any other timer function. This function:

• Initializes the µHAL internal interrupt structures.

• Resets all timers to a known state. (It sets the internal delays to a predefined value and sets all timers off.)

If this function is compiled for use with a debug agent, such as Angel, the timer associated with the debug agent is not reset and is locked to prevent access from within  $\mu$ HAL.

\_\_\_\_\_ Note \_\_\_\_\_

For the timer interrupt handler to be correctly installed, the application must ensure that uHALr\_InitInterrupts() has been called before this function call.

#### Syntax

void uHALr\_InitTimers(void)

#### 2.5.3 uHALr\_RequestSystemTimer()

This function installs a handler for the system timer, sets up the internal structures, and stops (and does not restart) the timer. By default, the system timer is set to tick once every millisecond.

#### Syntax

int uHALr\_RequestSystemTimer(PrHandler handler, const unsigned char \*devname)

where:

| handler | Is a pointer to the routine that will process the interrupt.        |

|---------|---------------------------------------------------------------------|

| devname | Is a pointer to a string identifying the function of the interrupt. |

#### **Return value**

Returns one of the following:

- 0 If successful.

- -1 If the IRQ is already assigned.

#### 2.5.4 uHALr\_InstallSystemTimer()

This function starts the timer and enables the interrupt associated with it.

#### Syntax

void uHALr\_InstallSystemTimer(void)

#### 2.5.5 System timer programming example

The program in Example 2-3 demonstrates how a system timer is used.

#### Example 2-3 System timer example

```

#include "uhal.h"

// High-level routine called by IRQ Trap Handler when the timer interrupts

static int OSTick = 0 ;

void TickTimer(unsigned int irq){

OSTick++ ;

}

int main (int argc, int *argv[]) {

int i, j ;

uHALr_printf("System Timer\n") ; // who are we?

uHALr_InitInterrupts() ; // Install new trap handlers and soft vectors

// initialize the timers

uHALr_InitTimers() ;

OSTick = 0;

// initialize the tick count

uHALr_printf("Timer init\n") ;

if (uHALr_RequestSystemTimer(TickTimer,(const unsigned char*)"test")<= 0)</pre>

uHALr_printf("Timer/IRQ busy\n") ;

// Start system timer & enable the interrupt

uHALr_InstallSystemTimer() ;

// loop flashing a led and giving out the tick count

for (j = 0; ; j++) {

if (j & 1)

uHALr_SetLED(1) ;

else

uHALr_ResetLED(1) ;

uHALr_printf("Tick is %x\n", OSTick);

for (i = 0; i < 1000000; i++);

}

return (OK);

}

```

#### 2.5.6 uHALr\_RequestTimer()

This function gets the next available timer and installs a handler. On return, the timer is initialized but not running.

#### Syntax

int uHALr\_RequestTimer(PrHandler handler, const unsigned char \*devname)

| where:  |                                                                     |

|---------|---------------------------------------------------------------------|

| handler | Is a pointer to the routine that will process the interrupt.        |

| devname | Is a pointer to a string identifying the function of the interrupt. |

#### **Return value**

| Returns one of the following: |                                              |  |

|-------------------------------|----------------------------------------------|--|

| timer                         | If successful, the timer number is returned. |  |

| -1                            | If the timer is unknown or already assigned. |  |

#### 2.5.7 uHALr\_InstallTimer()

This function starts the specified timer by enabling the timer and the associated interrupt.

void uHALr\_InstallTimer(unsigned int timer)

where:

*timer* Is the timer to be started.

#### 2.5.8 uHALr\_FreeTimer()

This function disables the specified timer, frees the interrupt, and updates the internal structure.

#### Syntax

int uHALr\_FreeTimer(unsigned int timer)

where:

*timer* Is the number of the timer to be freed.

#### **Return value**

Returns one of the following:

0 If successful.

-1 If the timer is unknown.

#### 2.5.9 uHALr\_GetTimerInterval()

This function gets the interval, in microseconds, for the specified timer.

#### Syntax

int uHALr\_GetTimerInterval(unsigned int timer)

where:

*timer* Is the number of the timer for which the interval is requested.

#### **Return value**

Returns one of the following:intervalIf successful (return value in microseconds).-1If the timer is not found.

#### 2.5.10 uHALr\_SetTimerInterval()

This function sets the interval, in microseconds, for the specified timer.

#### Syntax

int uHALr\_SetTimerInterval(unsigned int timer, unsigned int interval)

where:

| timer    | Is the timer number for which the interval is to be set. |

|----------|----------------------------------------------------------|

| interval | Is the number of microseconds between events.            |

#### **Return value**

Returns one of the following:0If the timer is found.-1If the timer is not found.

#### 2.5.11 uHALr\_GetTimerState()

This function gets the current state of the specified timer.

#### Syntax

int uHALr\_GetTimerState(unsigned int timer)

where:

*timer* Is the timer number for which the state is requested.

#### **Return value**

Returns one of the following:

| state | If the timer is found      | If the timer is found, the current state is one of: |  |

|-------|----------------------------|-----------------------------------------------------|--|

|       | T_FREE                     | Available.                                          |  |

|       | T_ONESHOT                  | Single-shot timer (in use).                         |  |

|       | T_INTERVAL                 | Repeating timer (in use).                           |  |

|       | T_LOCKED                   | Not available for use by µHAL.                      |  |

| -1    | If the timer is not found. |                                                     |  |

#### 2.5.12 uHALr\_SetTimerState()

This function sets the timer state.

#### Syntax

int uHALr\_SetTimerState(unsigned int timer, enum uHALe\_TimerState state)

| where: |                                                       |                             |

|--------|-------------------------------------------------------|-----------------------------|

| timer  | Is the timer number for which the state is being set. |                             |

| state  | Is a valid timer state which is one of:               |                             |

|        | T_ONESHOT                                             | Single-shot timer (in use). |

|        | T_INTERVAL                                            | Repeating timer (in use).   |

#### **Return value**

Returns one of the following:

- **0** If the timer is found.

- -1 If the timer is not found.

#### 2.5.13 uHALr\_EnableTimer()

This function reloads the interval and enables the specified timer.

#### Syntax

void uHALr\_EnableTimer(unsigned int timer)

where:

*timer* Is the timer to be enabled.

# 2.6 Simple API support functions

In addition to the general routines,  $\mu$ HAL provides implementations of a number of standard C library routines. The support functions include:

- uHALr\_memset()

- *uHALr\_memcmp()*

- *uHALr\_memcpy()* on page 2-20

- *uHALr\_strlen()* on page 2-20.

### 2.6.1 uHALr\_memset()

This function places character c into the first n characters of s, and returns s.

### Syntax

void \*uHALr\_memset(char \*s, int c, int n)

where:

| 5 | Is the start address of memory to be set.    |

|---|----------------------------------------------|

| с | Is the character to be copied into memory.   |

| n | Is the number of memory locations to be used |

### **Return value**

Returns s.

#### 2.6.2 uHALr\_memcmp()

This function compares the first *n* characters of *cs* with *ct*.

#### Syntax

int uHALr\_memcmp(char \*cs, char \*ct, int n)

where:

- *cs* Is the start of memory locations to be compared.

- *ct* Is the start of memory locations to be compared *against*.

- *n* Is the number of memory locations to be compared.

#### **Return value**

Returns one of the following:

| 1  | If cs>ct.                 |

|----|---------------------------|

| 0  | If cs=ct.                 |

| -1 | If cs <ct.< th=""></ct.<> |

# 2.6.3 uHALr\_memcpy()

This function copies *n* characters from *ct* to *s*.

## Syntax

void \* uHALr\_memcpy(char \*s, char \*ct, int n)

where:

| 5  | Is a pointer to the destination memory locations. |

|----|---------------------------------------------------|

| ct | Is a pointer to the source memory locations.      |

| n  | Is the number of memory locations to be copied.   |

### **Return value**

Returns the address of the first location copied to.

## 2.6.4 uHALr\_strlen()

This function returns the length of *s*.

### Syntax

int uHALr\_strlen(const char \*s)

where:

*s* Is a pointer to a zero-terminated string.

### **Return value**

This function returns the size, in bytes, of *s*.

# 2.7 Simple API LED control functions

$\mu HAL$  provides a set of simple routines for accessing any LEDs in the system. The LED control functions are:

- *uHALr\_CountLEDs()* on page 2-22

- *uHALr\_InitLEDs()* on page 2-22

- *uHALr\_ResetLED()* on page 2-22

- *uHALr\_SetLED()* on page 2-23

- *uHALr\_ReadLED()* on page 2-23

- *uHALr\_WriteLED()* on page 2-23.

An example of a simple LED flashing program is provided in *LED control code example* on page 2-24.

# 2.7.1 LED states and addresses

The  $\mu$ HAL LED code is generic and manages any LEDs that can be accessed at different addresses on different boards. Logic 1 can indicate either ON or OFF.

The LED code in the module AFSv1\_4\Source\uHAL\Sources\led.c keeps the LED addresses (or homes) in the uHALiv\_LedHomes array.

The set of pointers to LEDs is initialized to be the contents of uHAL\_LED\_OFFSETS. The addresses, pointers, and the number of LEDs (uHAL\_NUM\_OF\_LEDS), are defined in the board-specific definition files platform.s and platform.h. The platform definitions for the generic Integrator platform, for example, are in AFSv1\_4\Source\uHAL\Boards\INTEGRATOR.

For some systems, the platform files contain different addresses for different LEDs. The LED code also keeps a set of masks, one per LED, in the uHALiv\_LedMasks array. This is set to the contents of UHAL\_LED\_MASKS.

When reading the state of the LEDs, the LED code does the following:

- 1. Reads the LED register using its home address.

- 2. ANDs the value read with the mask for this LED.

- 3. Compares the result with the board-specific literal uHAL\_LED\_ON. Some LEDs report 0 as on.

A board-specific LED write function,  $uHALr_WriteLED()$  in board.c, is used to write to the LEDs.

# 2.7.2 uHALr\_CountLEDs()

This function returns the number of LEDs available to the µHAL application.

### Syntax

unsigned int uHALr\_CountLEDs(void)

## **Return value**

| Returns the number of LEDs: |                       |  |

|-----------------------------|-----------------------|--|

| 0                           | If there are no LEDs. |  |

| count                       | If there are LEDs.    |  |

## 2.7.3 uHALr\_InitLEDs()

This function initializes the LEDs in the system to 0FF.

### Syntax

unsigned int uHALr\_InitLEDs(void)

## **Return value**

Returns the number of LEDs.

# 2.7.4 uHALr\_ResetLED()

This function turns the specified LED off.

### Syntax

void uHALr\_ResetLED(unsigned int led)

where:

*led* Is the specified LED number.

## 2.7.5 uHALr\_SetLED()

This function turns the specified LED on.

## Syntax

void uHALr\_SetLED(unsigned int 1ed)

where:

*led* Is the specified LED number.

## 2.7.6 uHALr\_ReadLED()

This function returns the state of the specified LED.

# Syntax

int uHALr\_ReadLED(unsigned int 1ed)

where:

*led* Is the specified LED number.

# **Return value**

Returns one of the following:

**TRUE** If the LED state is on.

- FALSE If the LED state is off.

- -1 If the LED number specified is invalid.

TRUE is defined as 1 and FALSE is defined as 0.

# 2.7.7 uHALr\_WriteLED()

This function writes a value to the specified LED.

# Syntax

int uHALr\_WriteLED(unsigned int led, unsigned int state)

| where: |                           |                          |

|--------|---------------------------|--------------------------|

| 1ed    | Is the specified          | d LED number.            |

| state  | Is the desired LED state: |                          |

|        | TRUE                      | to turn the led on (1).  |

|        | FALSE                     | to turn the led off (0). |

#### **Return value**

Returns one of the following:

| 0  | If successful.                          |

|----|-----------------------------------------|

| -1 | If the LED number specified is invalid. |

### 2.7.8 LED control code example

Example 2-4 is a fragment of the simple LED flashing program. A similar program is in uHALDemos\Sources\led.c).

#### Example 2-4 LED flashing program

```

#include "uhal.h"

int main (int argc, int *argv[])

{

unsigned int count, max, on ;

unsigned int wait, i, j ;

count = uHALr_InitLEDs() ;

max = (1 \ll count);

while(1) {

for (i = 0; i < max; i++) {

/* which LEDs are on? */

on = (max - 1) \& i;

for (j = 0; j < \text{count} ; j++)

if (on & (i << j )

uHALr_SetLED( j + 1 );

else

uHALResetLED (j + 1);

/* wait a while */

for (wait = 0 ; wait < 1000000 ; wait++) ;</pre>

}

}

return (OK);

}

```

# 2.8 Serial input/output functions, definitions, and macros

If there is a serial port,  $\mu$ HAL provides access for the application by using a series of polled calls. In the case of a semihosted application,  $\mu$ HAL makes SWI calls to the underlying debug agent to process the requests.

The simple serial I/O functions are:

- *uHALr\_ResetPort()*

- *uHALr\_getchar()*

- *uHALr\_putchar()* on page 2-26

- *uHALr\_printf()* on page 2-26.

A basic character I/O program example is provided in:

• *Serial input/output code example* on page 2-26.

The one extended serial function is:

• *uHALir\_InitSerial()* on page 2-26.

#### 2.8.1 uHALr\_ResetPort()

This function resets the port defined for stdin/stdout to the board default state.

### Syntax

void uHALr\_ResetPort(void)

#### 2.8.2 uHALr\_getchar()

This function waits for a character from the default port. When compiled as a semihosted application, this function uses the SWI handler provided by the debug agent to get the character from the host console.

### Syntax

unsigned int uHALr\_getchar(void)

### **Return value**

Returns the unsigned int containing the character read from the serial port.

### 2.8.3 uHALr\_putchar()

This function sends the given character to the default port. When compiled as a semihosted application, this function uses the SWI handler provided by the debug agent to send the character to the host console.

## Syntax

void uHALr\_putchar(unsigned char c)

where:

*c* Is the character to be sent to the serial port.

# 2.8.4 uHALr\_printf()

This function converts, formats, and writes the arguments to the standard output.

#### Syntax

void uHALr\_printf(char \*format, ...)

where: