# ARM<sup>®</sup> CoreLink<sup>®</sup> SIE-200 System IP for Embedded

Revision: r3p1

**Technical Reference Manual**

#### ARM CoreLink SIE-200 System IP for Embedded Technical Reference Manual

Copyright © 2016-2017 ARM Limited or its affiliates. All rights reserved.

#### **Release Information**

The following changes have been made to this document:

Change history

| Date              | Issue | Confidentiality    | Change                     |

|-------------------|-------|--------------------|----------------------------|

| 4 March 2016      | А     | Confidential draft | First release of r0p0      |

| 24 June 2016      | В     | Confidential       | Beta release of r0p0       |

| 29 July 2016      | С     | Confidential       | Beta update of r0p0        |

| 28 September 2016 | D     | Confidential       | First release of r1p0 LAC  |

| 16 December 2016  | Е     | Non-Confidential   | First release of r2p0 EAC  |

| 31 March 2017     | F     | Non-Confidential   | First release of r3p0 EAC2 |

| 7 June 2017       | G     | Non-Confidential   | First release of r3p1 REL  |

#### **Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of ARM. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, ARM makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to ARM's customers is not intended to create or refer to any partnership relationship with any other company. ARM may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any signed written agreement covering this document with ARM, then the signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

Words and logos marked with <sup>®</sup> or <sup>™</sup> are registered trademarks or trademarks of ARM Limited or its affiliates in the EU and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow ARM's trademark usage guidelines at http://www.arm.com/about/trademarks/guidelines/index.php.

Copyright © 2016-2017 ARM Limited or its affiliates. All rights reserved.

ARM Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

## Contents ARM CoreLink SIE-200 System IP for Embedded Technical Reference Manual

|           | Prefa | ace                                                       |      |

|-----------|-------|-----------------------------------------------------------|------|

|           |       | About this book                                           | vii  |

|           |       | Feedback                                                  | x    |

| Chapter 1 | Intro | duction                                                   |      |

| •         | 1.1   | About the CoreLink SIE-200 System IP for Embedded         | 1-2  |

|           | 1.2   | Product revisions                                         |      |

| Chapter 2 | Fund  | ctional Description                                       |      |

|           | 2.1   | AHB5 bus matrix                                           | 2-3  |

|           | 2.2   | AHB5 default slave                                        | 2-8  |

|           | 2.3   | AHB5 example slave                                        | 2-10 |

|           | 2.4   | AHB5 exclusive access monitor                             | 2-12 |

|           | 2.5   | AHB5 GPIO                                                 | 2-17 |

|           | 2.6   | AHB5 master multiplexer                                   | 2-20 |

|           | 2.7   | AHB5 slave multiplexer                                    | 2-24 |

|           | 2.8   | AHB5 timeout monitor                                      | 2-28 |

|           | 2.9   | AHB5 to external SRAM interface                           | 2-32 |

|           | 2.10  | AHB5 to ROM interface                                     | 2-37 |

|           | 2.11  | AHB5 to internal SRAM interface module                    | 2-40 |

|           | 2.12  | Cortex-M3/Cortex-M4 AHB5 adapter                          | 2-44 |

|           | 2.13  | Comparison between bridges and their low-latency versions | 2-49 |

|           | 2.14  | AHB5 access control gate                                  |      |

|           | 2.15  | AHB5 downsizer                                            | 2-55 |

|           | 2.16  | AHB5 to AHB5 and APB4 asynchronous bridge                 | 2-59 |

|           | 2.17  | AHB5 to AHB5 sync-down bridge                             |      |

|           | 2.18  | AHB5 to AHB5 low-latency sync-down bridge                 |      |

|            | 2.19  | AHB5 to AHB5 synchronous bridge                 |       |

|------------|-------|-------------------------------------------------|-------|

|            | 2.20  | AHB5 to AHB5 sync-up bridge                     |       |

|            | 2.21  | AHB5 to AHB5 low-latency sync-up bridge         |       |

|            | 2.22  | AHB5 to APB4 asynchronous bridge                |       |

|            | 2.23  | AHB5 to APB4 sync-down bridge                   |       |

|            | 2.24  | AHB5 to APB4 low-latency sync-down bridge       |       |

|            | 2.25  | AHB5 upsizer                                    |       |

|            | 2.26  | AHB5 TrustZone master security controller       |       |

|            | 2.27  | AHB5 TrustZone memory protection controller     |       |

|            | 2.28  | AHB5 TrustZone peripheral protection controller |       |

|            | 2.29  | APB4 TrustZone peripheral protection controller |       |

|            | 2.30  | AHB5 FRBM                                       |       |

|            | 2.31  | Behavioral SRAM model with an AHB5 interface    |       |

|            | 2.32  | External asynchronous 8-bit SRAM model          |       |

|            | 2.33  | External asynchronous 16-bit SRAM model         |       |

|            | 2.34  | FPGA SRAM synthesizable model                   |       |

|            | 2.35  | RAM wrapper model                               |       |

|            | 2.36  | ROM behavioral model                            |       |

|            | 2.37  | ROM wrapper model                               | 2-139 |

| Chapter 3  | Prog  | rammers Model                                   |       |

| -          | 3.1   | AHB5 example slave                              |       |

|            | 3.2   | ABH5 GPIO                                       |       |

|            | 3.3   | AHB5 TrustZone memory protection controller     |       |

| Appendix A | Revis | sions                                           |       |

### Preface

This preface introduces the *ARM*<sup>®</sup> *CoreLink* <sup>™</sup> *SIE-200 System IP for Embedded Technical Reference Manual*. It contains the following sections:

- *About this book* on page vii.

- *Feedback* on page x.

#### About this book

This is the *Technical Reference Manual* (TRM) for the CoreLink SIE-200 System IP for Embedded product.

| Product revision status |                              |                                                                                                                                                                                                                |

|-------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | rn Ident                     | indicates the revision status of the product described in this book, where:<br>if is the major revision of the product.<br>if is the minor revision or modification status of the product.                     |

| Intended audience       |                              |                                                                                                                                                                                                                |

|                         |                              | n for system designers to design products with the ARM Cortex <sup>®</sup> -M form to the ARMv8-M processor architecture.                                                                                      |

| Using this book         |                              |                                                                                                                                                                                                                |

|                         | This book is organi          | zed into the following chapters:                                                                                                                                                                               |

|                         | Chapter 1 Introdu            | ction                                                                                                                                                                                                          |

|                         | Read                         | this for an introduction to the system IP.                                                                                                                                                                     |

|                         | Chapter 2 Function           | onal Description                                                                                                                                                                                               |

|                         |                              | this for an overview of the major functional components and the operation e system IP.                                                                                                                         |

|                         | Chapter 3 Program            | nmers Model                                                                                                                                                                                                    |

|                         |                              | this for an the registers and memory map for components that have a ramming interface.                                                                                                                         |

|                         | Appendix A Revis             | ions                                                                                                                                                                                                           |

|                         | Read<br>book                 | this for a description of the technical changes between released issues of this                                                                                                                                |

| Glossary                |                              |                                                                                                                                                                                                                |

|                         | those terms. The A           | <i>y</i> is a list of terms used in ARM documentation, together with definitions for <i>RM Glossary</i> does not contain terms that are industry standard unless the fors from the generally accepted meaning. |

|                         | See ARM <sup>®</sup> Glossar | <pre>y http://infocenter.arm.com/help/topic/com.arm.doc.aeg0014-/index.html</pre>                                                                                                                              |

#### **Typographical Conventions**

This book uses the conventions that are described in:

- Typographical conventions on page viii.

- *Timing diagrams* on page viii.

- *Signals* on page viii.

#### **Typographical conventions**

The following table describes the typographical conventions:

| Style                   | Purpose                                                                                                                                                                                                          |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| italic                  | Introduces special terminology, denotes cross-references, and citations.                                                                                                                                         |  |  |

| bold                    | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.                                                                            |  |  |

| monospace               | Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.                                                                                                      |  |  |

| <u>mono</u> space       | Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.                                                                          |  |  |

| monospace <i>italic</i> | Denotes arguments to monospace text where the argument is to be replaced by a specific value.                                                                                                                    |  |  |

| monospace bold          | Denotes language keywords when used outside example code.                                                                                                                                                        |  |  |

| <and></and>             | Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example: MRC p15, 0 <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd>                                  |  |  |

| SMALL CAPITALS          | Used in body text for a few terms that have specific technical meanings, that are defined in the <i>ARM glossary</i> . For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE. |  |  |

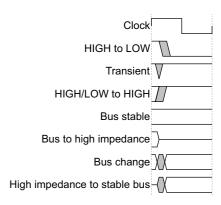

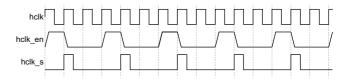

#### **Timing diagrams**

The figure named *Key to timing diagram conventions* explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

#### Key to timing diagram conventions

#### Signals

The signal conventions are:

**Signal-level** The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals.

- LOW for active-LOW signals.

**Lower-case n** At the start or end of a signal name denotes an active-LOW signal.

#### Additional reading

This section lists publications by ARM and by third parties.

See Infocenter http://infocenter.arm.com, for access to ARM documentation.

#### **ARM** publications

This book contains information that is specific to this product. See the following documents for other relevant information:

• Cortex<sup>®</sup>-M3 Technical Reference Manual (ARM DDI 0337).

The following confidential books are only available to licensees:

- ARM<sup>®</sup> CoreLink<sup>m</sup> SIE-200 System IP for Embedded Configuration and Integration Manual (ARM DIT 0067).

- ARM<sup>®</sup> AMBA<sup>®</sup> 5 AHB Protocol Specification (ARM IHI 0033).

- ARM<sup>®</sup> AMBA<sup>®</sup> APB Protocol Specification (ARM IHI 0024).

- ARM<sup>®</sup> Low Power Interface Specification (ARM IHI 0068).

- ARMv8-M Architecture Reference Manual (ARM DDI 0553).

#### Other publications

This section lists relevant documents published by third parties:

- JEDEC website www.jedec.org.

- Accellera website www.accellera.org.

#### Feedback

ARM welcomes feedback on this product and its documentation.

#### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

#### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- The title.

- The number, ARM DDI 0571G.

- The page numbers to which your comments apply.

- A concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

#### \_\_\_\_\_Note \_\_\_\_\_

ARM tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader.

### Chapter 1 Introduction

This chapter introduces the CoreLink SIE-200 System IP for Embedded. It contains the following sections:

- About the CoreLink SIE-200 System IP for Embedded on page 1-2

- *Product revisions* on page 1-4.

### 1.1 About the CoreLink SIE-200 System IP for Embedded

The CoreLink SIE-200 System IP for Embedded product is a collection of interconnect, peripheral, and TrustZone<sup>®</sup> controller components for use with a processor that complies with the ARMv8-M processor architecture.

#### 1.1.1 Bus architecture

CoreLink SIE-200 System IP for Embedded supports the following bus protocols:

- AMBA 5 AHB5 Protocol.

- AMBA 3 AHB-Lite Protocol.

- AMBA 4 APB4 Protocol.

- AMBA 3 APB3 Protocol.

#### Bus naming convention

It is important to always view each AMBA point-to-point connection as a master to slave connection. To distinguish between external AMBA masters or slaves and the conceptual masters or slaves on the component, masters and slaves on the interconnect are referred to as master ports or slave ports. External masters and slaves are referred to as masters and slaves.

#### 1.1.2 Design and verification components

CoreLink SIE-200 System IP for Embedded consists of the following components and models:

- AHB5 system components.

- *AHB5 bridge components.*

- *TrustZone Protection controllers* on page 1-3.

- *Verification components* on page 1-3.

#### AHB5 system components

The AHB5 system components are:

- AHB5 bus matrix.

- AHB5 default slave.

- AHB5 example slave.

- AHB5 exclusive access monitor.

- AHB5 GPIO.

- AHB5 master multiplexer.

- AHB5 slave multiplexer.

- AHB5 timeout monitor.

- AHB5 to external SRAM interface.

- AHB5 to ROM interface.

- AHB5 to internal SRAM interface module.

- Cortex-M3/Cortex-M4 AHB5 adapter.

#### AHB5 bridge components

The AHB5 bridge components are:

- AHB5 access control gate.

- AHB5 downsizer.

- AHB5 to AHB5 and APB4 asynchronous bridge.

- AHB5 to AHB5 sync-down bridge.

- AHB5 to ABH5 low-latency sync-down bridge.

- AHB5 to AHB5 synchronous bridge.

- AHB5 to AHB5 sync-up bridge.

- AHB5 to AHB5 low-latency sync-up bridge.

- AHB5 to APB4 asynchronous bridge.

- AHB5 to APB4 sync-down bridge.

- AHB5 to APB4 low-latency sync-down bridge.

- AHB5 upsizer.

#### **TrustZone Protection controllers**

The TrustZone components are:

- AHB5 TrustZone master security controller.

- AHB5 TrustZone memory protection controller.

- AHB5 TrustZone peripheral protection controller.

- APB4 TrustZone peripheral protection controller.

#### Verification components

- AHB5 FRBM.

- Behavioral SRAM model with an AHB5 interface.

- External asynchronous 8-bit SRAM model.

- External asynchronous 16-bit SRAM model.

- FPGA SRAM synthesizable model.

- RAM wrapper model.

- ROM behavioral model.

- ROM wrapper model.

#### 1.2 Product revisions

This section describes the differences in functionality between product revisions of the CoreLink SIE-200 System IP for Embedded:

- r0p0 First release.

- r1p0 Second release. Functional improvement to AMBA® AHB5 downsizer.

- r2p0 Third release. Added the following:

- AHB5 example slave.

- AHB5 GPIO.

- AHB5 timeout monitor.

- AHB5 to external SRAM interface.

- AHB5 to ROM interface.

- Cortex-M3/Cortex-M4 AHB5 adapter.

- Behavioral SRAM model with an AHB5 interface.

- External asynchronous 8-bit SRAM model.

- External asynchronous 16-bit SRAM model.

- FPGA SRAM synthesizable model.

- RAM wrapper model.

- ROM behavioral model.

- ROM wrapper model.

**r3p0** Fourth release. Added the following:

- ABHB5 to AHB5 low-latency sync-down bridge.

- AHB5 to AHB5 low-latency sync-up bridge.

- ABH5 to APB4 low-latency sync-down bridge.

—— Note ——

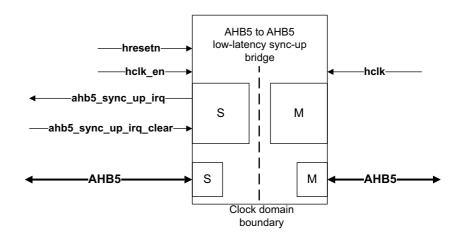

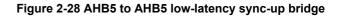

The low-latency bridges in release r3p0 are similar in function to their non-low-latency equivalents. They are options for designs that do not require Q-channel support for power management.

This option enables optimization for reduced latency in these three bridges.

**r3p1** REL quality release. No feature increment.

### Chapter 2 Functional Description

This chapter describes the components supplied with the CoreLink SIE-200 System IP for Embedded product.

The following sections describe the system components provided in the CoreLink SIE-200 System IP for Embedded:

- *AHB5 bus matrix* on page 2-3.

- *AHB5 default slave* on page 2-8.

- *AHB5 example slave* on page 2-10.

- *AHB5 exclusive access monitor* on page 2-12.

- *AHB5 GPIO* on page 2-17.

- *AHB5 master multiplexer* on page 2-20.

- *AHB5 slave multiplexer* on page 2-24.

- *AHB5 timeout monitor* on page 2-28.

- *AHB5 to external SRAM interface* on page 2-32.

- *AHB5 to ROM interface* on page 2-37.

- *AHB5 to internal SRAM interface module* on page 2-40.

- Cortex-M3/Cortex-M4 AHB5 adapter on page 2-44.

The following sections describe the SIE-200 AHB5 bridge components:

- Comparison between bridges and their low-latency versions on page 2-49.

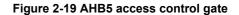

- *AHB5 access control gate* on page 2-50.

- *AHB5 downsizer* on page 2-55.

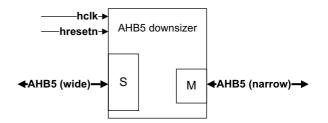

- AHB5 to AHB5 and APB4 asynchronous bridge on page 2-59.

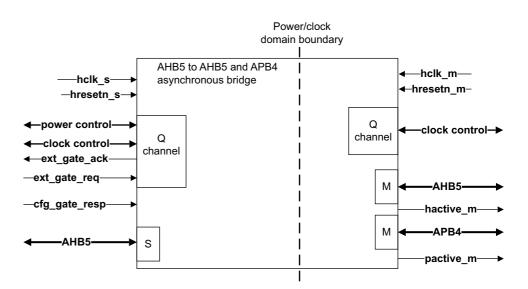

- *AHB5 to AHB5 sync-down bridge* on page 2-65.

- *AHB5 to AHB5 low-latency sync-down bridge* on page 2-70.

- *AHB5 to AHB5 synchronous bridge* on page 2-75.

- *AHB5 to AHB5 sync-up bridge* on page 2-79.

- *AHB5 to AHB5 low-latency sync-up bridge* on page 2-84.

- *AHB5 to APB4 asynchronous bridge* on page 2-89.

- *AHB5 to APB4 sync-down bridge* on page 2-93.

- *AHB5 to APB4 low-latency sync-down bridge* on page 2-97.

- *AHB5 upsizer* on page 2-100.

The following sections describe the SIE-200 TrustZone Protection components:

- *AHB5 TrustZone master security controller* on page 2-104.

- *AHB5 TrustZone memory protection controller* on page 2-112.

- AHB5 TrustZone peripheral protection controller on page 2-117.

- *APB4 TrustZone peripheral protection controller* on page 2-123.

The following sections describe the SIE-200 verification components:

- *AHB5 FRBM* on page 2-128.

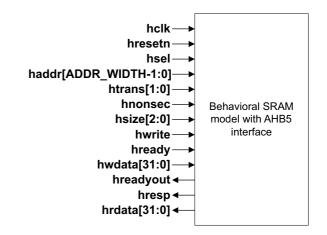

- Behavioral SRAM model with an AHB5 interface on page 2-131.

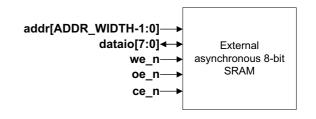

- External asynchronous 8-bit SRAM model on page 2-133.

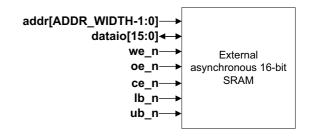

- *External asynchronous 16-bit SRAM model* on page 2-134.

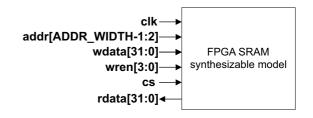

- *FPGA SRAM synthesizable model* on page 2-135.

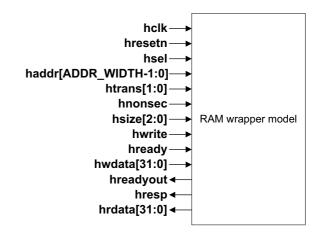

- *RAM wrapper model* on page 2-136.

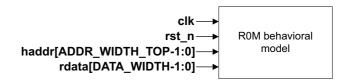

- *ROM behavioral model* on page 2-138.

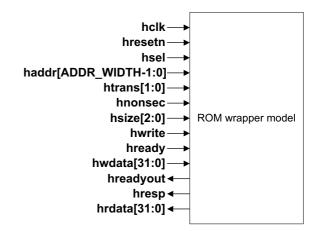

- *ROM wrapper model* on page 2-139.

#### 2.1 AHB5 bus matrix

This section describes the AHB5 bus matrix.

The section contains the following subsections:

- Functional description.

- *Port list* on page 2-5.

- AHB5 bus properties on page 2-7.

#### 2.1.1 Functional description

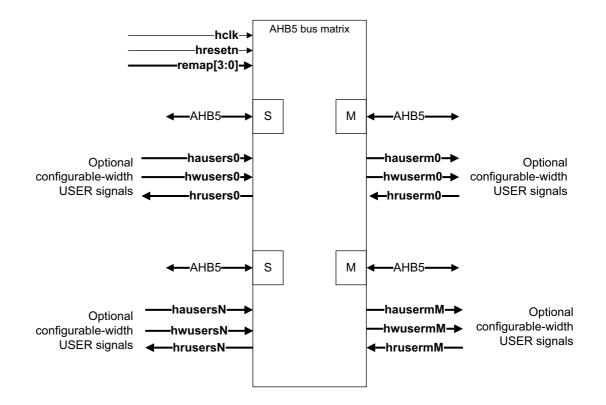

The AHB5 bus matrix connects other AHB5 components through its slave and master ports.

The bus matrix has the following configurable features:

- Number of slave ports, from 1-16.

- Number of master ports, from 1-16.

- Data width, either 32 bits or 64 bits.

- Address width, from 32-64 bits.

- Arbiter types: round, fixed, burst, round\_nolat, burst\_nolat, and fixed\_nolat.

- Optional **xUSER** signals, from 0-32 bits.

- Sparse connectivity:

- The sparse connectivity feature removes any unnecessary connections, and reduces area and multiplexer delays.

- Separate instances of the output stage and output arbiter are generated for each master port.

- For input-output stages with only one sparse connection, the choice of arbiter is overridden with single arbiter and output stage modules. These single modules also permit 1xn interconnects.

- Design entry by XML configuration file that enables you to specify an address map, including REMAP support.

- User-specified module names or automatically derived top-level name.

- User-specified port suffixes.

- User-specified source and target directories.

- Optional `timescale Verilog directives.

The following figure shows the bus matrix module.

#### Figure 2-1 AHB 5 bus matrix

#### Arbitration

The arbitration in the bus matrix module determines the input port that has access to the shared slave, and each shared slave has its own arbitration. Different arbitration schemes provide different system characteristics in terms of access latency and overall system performance.

The slave switch supports the following arbitration schemes:

#### **Fixed** arbitration

This is the simplest scheme, which only provides simple selection. It provides access for the next input port when the current port has finished. The lowest order input port has priority.

#### Fixed (burst) arbitration

This is similar to fixed arbitration, but it does not break defined length burst transfers.

#### **Round-robin arbitration**

This is similar to burst arbitration, but it adds round robin priority handling.

— Note –

The arbitration schemes have two options, with or without latency. The schemes with latency insert an extra cycle each time the downstream port selects a new upstream port to service, but the others do not insert the extra cycle.

The default arbitration is round-robin with latency.

#### 2.1.2 Port list

The following table shows the port list of the AHB5 bus matrix.

| Table 2-1 | AHB5 | bus | matrix | port | list |

|-----------|------|-----|--------|------|------|

| Block                 | SIGNAL                                           | CONDITION           | DIRECTION | DESCRIPTION                                                      |

|-----------------------|--------------------------------------------------|---------------------|-----------|------------------------------------------------------------------|

| System                | hclk                                             |                     | Input     | Clock                                                            |

|                       | hresetn                                          |                     | Input     | Reset                                                            |

| AHB5 Slave            | hsel_ <si></si>                                  | target              | Input     | Slave select                                                     |

| [for each<br>slave    | haddr_ <si>[ADDR_WIDTH-1]<sup>a</sup></si>       |                     | Input     | Address                                                          |

| interface<br>defined] | htrans_ <si>[1:0]<sup>a</sup></si>               |                     | Input     | Transfer type                                                    |

|                       | hwrite_ <si>a</si>                               |                     | Input     | Transfer direction indicator                                     |

|                       | hsize_ <si>[2:0]<sup>a</sup></si>                |                     | Input     | Size of the transfer                                             |

|                       | hburst_ <si>[2:0]<sup>a</sup></si>               |                     | Input     | Burst type                                                       |

|                       | hprot_ <si>[6:0]<sup>a</sup></si>                |                     | Input     | Protection control                                               |

|                       | hmaster_ <si>[MASTER_WIDTH-1:0]<sup>a</sup></si> |                     | Input     | Master identifier.                                               |

|                       | hwdata_ <si>[DATA_WIDTH-1:0]<sup>a</sup></si>    |                     | Input     | Write data                                                       |

|                       | hmastlock_ <si>a</si>                            |                     | Input     | Locked sequence indicator                                        |

|                       | hready_ <si>a</si>                               | target              | Input     | Transfer completior<br>indicator from<br>interconnect            |

|                       | hnonsec_ <si>a</si>                              |                     | Input     | Non-secure transfer indicator                                    |

|                       | hexcl_ <si>a</si>                                |                     | Input     | Exclusive Transfer indicator                                     |

|                       | hauser_ <si>[USER_WIDTH-1:0]<sup>a</sup></si>    | USER_WIDTH >0       | Input     | Address channel user signals                                     |

|                       | hwuser_ <si>[USER_WIDTH-1:0]<sup>a</sup></si>    | USER_WIDTH >0       | Input     | Write channel user signals                                       |

|                       | hrdata_ <si>[DATA_WIDTH-1:0]<sup>a</sup></si>    |                     | Output    | Read data                                                        |

|                       | hreadyout_ <si> or hready_<si>a</si></si>        | target or initiator | Output    | Transfer completion<br>indicator to<br>interconnect or<br>master |

|                       | hresp_ <si>a</si>                                |                     | Output    | Transfer response                                                |

|                       | hexokay_ <si>a</si>                              |                     | Output    | Exclusive okay                                                   |

|                       | hruser_ <si>a</si>                               | USER_WIDTH >0       | Output    | Read channel user signals                                        |

#### Table 2-1 AHB5 bus matrix port list (continued)

| Block                 | SIGNAL                                           | CONDITION      | DIRECTION | DESCRIPTION                              |

|-----------------------|--------------------------------------------------|----------------|-----------|------------------------------------------|

| AHB5                  | hrdata_ <mi>[DATA_WIDTH-1:0]</mi>                |                | Input     | Read data                                |

| Master<br>(slave      | hreadyout_ <mi>b</mi>                            |                | Input     | HREADY feedbac                           |

| initiator)            | hresp_ <mi><sup>b</sup></mi>                     |                | Input     | Transfer response                        |

| [for each master      | hexokay_ <mi>b</mi>                              |                | Input     | Exclusive okay                           |

| interface<br>defined] | hruser_ <mi>[USER_WIDTH-1:0]<sup>b</sup></mi>    | USER_WIDTH >0  | Input     | Read channel user signals                |

|                       | hsel_ <mi><sup>b</sup></mi>                      |                | Output    | Slave select                             |

|                       | haddr_ <mi>[ADDR_WIDTH-1]<sup>b</sup></mi>       |                | Output    | Address                                  |

|                       | htrans_ <mi>[1:0]<sup>b</sup></mi>               |                | Output    | Transfer type                            |

|                       | hwrite_ <mi>b</mi>                               |                | Output    | Transfer direction indicator             |

|                       | hsize_ <mi>[2:0]<sup>b</sup></mi>                |                | Output    | Size of the transfer                     |

|                       | hburst_ <mi>[2:0]<sup>b</sup></mi>               |                | Output    | Burst type                               |

|                       | hprot_ <mi>[6:0]<sup>b</sup></mi>                |                | Output    | Protection control                       |

|                       | hmaster_ <mi>[MASTER_WIDTH-1:0]<sup>b</sup></mi> |                | Output    | Master identifier.                       |

|                       | hwdata_ <mi>[DATA_WIDTH-1:0]<sup>b</sup></mi>    |                | Output    | Write data                               |

|                       | hmastlock_ <mi>b</mi>                            |                | Output    | Locked sequence indicator                |

|                       | hreadymux_ <mi>b</mi>                            |                | Output    | Transfer done                            |

|                       | hnonsec_ <mi>b</mi>                              |                | Output    | Non-secure transferindicator             |

|                       | hexcl_ <mi><sup>b</sup></mi>                     |                | Output    | Exclusive Transfer indicator             |

|                       | hauser_ <mi>[USER_WIDTH-1:0]<sup>b</sup></mi>    | USER_WIDTH > 0 | Output    | Address channel user signals             |

|                       | hwuser_ <mi>[USER_WIDTH-1:0]<sup>b</sup></mi>    | USER_WIDTH>0   | Output    | Write channel user signals               |

| Remap                 | remap[REMAP_WIDTH-1:0]                           | REMAP_WIDTH >0 | Input     | Remap bus for<br>memory map<br>switching |

a. si: slave interface port suffix.

b. mi: master interface port suffix.

#### 2.1.3 AHB5 bus properties

The following table shows the AHB5 properties of the AHB5 bus matrix.

| PROPERTY              | VALUE | COMMENT                                                                    |

|-----------------------|-------|----------------------------------------------------------------------------|

| Extended_Memory_Types | TRUE  | Pass-through                                                               |

| Secure_Transfers      | TRUE  | Pass-through                                                               |

| Endian                | N/A   | Pass-through. The bus matrix provides no built-in endian adaptation.       |

| Stable_Between_Clock  | FALSE | Not supported for SIE-200                                                  |

| Exclusive_Transfers   | TRUE  | Pass-through. The bus matrix<br>provides no built-in endian<br>adaptation. |

| Multi_Copy_Atomicity  | TRUE  | No caches or buffering that make a transfer visible to only some agents    |

| User signaling        | TRUE  | Pass-through                                                               |

#### Table 2-2 AHB5 properties

#### 2.2 AHB5 default slave

This section describes the AHB5 default slave.

The section contains the following subsections:

- Functional description.

- Port list.

.

AHB5 bus properties on page 2-9.

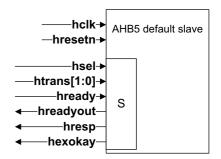

#### 2.2.1 Functional description

The default slave conforms to the AHB5 specification which describes the default slave behavior. It returns a standard two-cycle ERROR response whenever the module is selected.

The AHB5 default slave responds to transfers when the bus master accesses an illegal address range:

- An OKAY response is generated for IDLE or BUSY transfers.

- An ERROR response is generated for NONSEQUENTIAL or SEQUENTIAL transfers.

Figure 2-2 shows the AHB5 default slave.

Figure 2-2 AHB5 default slave

#### 2.2.2 Port list

The following table shows the port list of the AHB5 default slave.

| Table 2-3 | AHB5 | default | slave | port | list |

|-----------|------|---------|-------|------|------|

|-----------|------|---------|-------|------|------|

| Block  | Signal  | Direction | Description |

|--------|---------|-----------|-------------|

| System | hclk    | Input     | Clock       |

|        | hresetn | Input     | Reset       |

Table 2-4 AHB5 properties

#### Table 2-3 AHB5 default slave port list (continued)

| Block      | Signal      | Direction | Description                                          |

|------------|-------------|-----------|------------------------------------------------------|

| AHB5 Slave | hsel        | Input     | Slave select                                         |

|            | htrans[1:0] | Input     | Transfer type                                        |

|            | hready      | Input     | Transfer completion indicator                        |

|            | hreadyout   | Output    | Transfer completion indicator output                 |

|            | hresp       | Output    | Transfer response                                    |

|            | hexokay     | Output    | Exclusive transfer response.<br>This is tied to 0x0. |

#### AHB5 bus properties 2.2.3

The following table shows the AHB5 properties of the AHB5 default slave.

|                       |       | ·····                     |

|-----------------------|-------|---------------------------|

| PROPERTY              | VALUE | COMMENT                   |

| Extended_Memory_Types | FALSE | N/A                       |

| Secure_Transfers      | FALSE | N/A                       |

| Endian                | N/A   |                           |

| Stable_Between_Clock  | FALSE | Not supported for SIE-200 |

| Exclusive_Transfers   | FALSE | Not supported             |

| Multi_Copy_Atomicity  | FALSE | N/A                       |

| User signaling        | FALSE | Not supported             |

#### 2.3 AHB5 example slave

This section describes the AHB5 example slave.

The section contains the following subsections:

- Functional description.

- Port list.

- AHB5 bus properties on page 2-11.

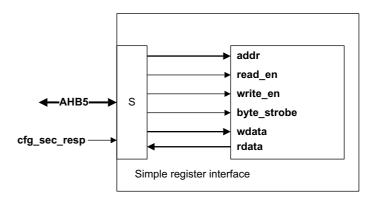

#### 2.3.1 Functional description

The AHB5 example slave provides  $3 \times 16$  bytes ( $3 \times 4$  words) of hardware read/write registers. It demonstrates how to implement a simple security aware AHB5 slave.

Figure 2-3 shows the AHB5 example slave.

#### Figure 2-3 AHB5 example slave

The register sets are accessible by:

- One set (four words) with secure transfers only.

- One set (four words) with non-secure transfers only.

- One set (four words) with both secure and non-secure transfers.

The registers can be accessed by using byte, half word and word transfers.

The example slave is partitioned into two parts, the interface part converts the AHB5 protocol to a simple non-pipelined bus protocol and can be reused for porting simple peripherals from 8-bit/16-bit products to ARM easily. The security checking is done by register bank part.

#### 2.3.2 Port list

The following table shows the port list of the AHB5 example slave.

| Table | 2-5 | AHB5 | examp | le sla | ave p | ort | list |  |

|-------|-----|------|-------|--------|-------|-----|------|--|

|       |     |      |       |        |       |     |      |  |

- - - - - - -

| Block                | Signal  | Direction | Description           |

|----------------------|---------|-----------|-----------------------|

| System               | hclk    | Input     | Clock AHB5 side       |

|                      | hresetn | Input     | Reset for HCLK domain |

| AHB5 slave interface | hsel    | Input     | Slave select          |

| Block | Signal       | Direction | Description                     |

|-------|--------------|-----------|---------------------------------|

|       | hnonsec      | Input     | Non-secure transfer indicator   |

|       | haddr[11:0]  | Input     | Address, configurable width     |

|       | htrans[1:0]  | Input     | Transfer type                   |

|       | hsize[2:0]   | Input     | Size of the transfer            |

|       | hwrite       | Input     | Transfer direction indicator    |

|       | hready       | Input     | HREADY feedback from all slaves |

|       | hwdata[31:0] | Output    | Write data, configurable width  |

|       | hrdata[31:0] | Output    | Read data, configurable width   |

|       | hreadyout    | Output    | Transfer completion indicator   |

|       | hresp[1:0]   | Output    | Transfer response               |

|       | cfg_sec_resp | Input     | Error response (1) /RAZ/WI (0   |

#### 2.3.3 AHB5 bus properties

The following table shows the AHB5 properties of the AHB5 example slave.

#### Table 2-6 AHB5 properties

| Value | Comment                                                                       |

|-------|-------------------------------------------------------------------------------|

| FALSE | N/A                                                                           |

| TRUE  | Supported                                                                     |

| N/A   | Default little endian                                                         |

| FALSE | Not supported for SIE-200                                                     |

| FALSE | Not supported                                                                 |

| TRUE  | No caches or buffering that make<br>a transfer visible to only some<br>agents |

| FALSE | Not used                                                                      |

|       | FALSE<br>TRUE<br>N/A<br>FALSE<br>FALSE<br>TRUE                                |

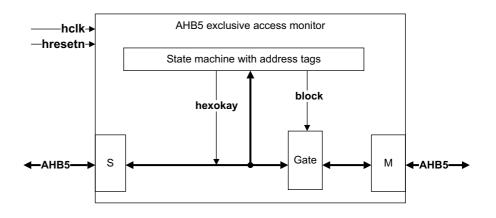

#### 2.4 AHB5 exclusive access monitor

This section describes the AHB5 exclusive access monitor.

The section contains the following subsections:

- Functional description.

- *Port list* on page 2-13.

- AHB5 bus properties on page 2-15.

#### 2.4.1 Functional description

You can add the AHB5 exclusive access monitor to an AHB5 path to monitor access to slaves downstream of it. The component implements the Exclusive Access Monitor feature described in the AHB5 specification.

#### Figure 2-4 AHB5 exclusive access monitor

Due to TrustZone for ARMv8-M, this AHB5 exclusive access monitor has one difference from the AHB5 specification. HNONSEC is treated as an extra address bit in the address tag to prevent non-secure software from clearing a Secure tag.

Under TrustZone for ARMv8-M, the same data cannot be accessed in both secure and non-secure mode, therefore a write is not considered to have overwritten a tagged data if the HNONSEC is different from the state in the exclusive read.

If the exclusive access is set as not supported for a master, that is, the corresponding ID\_PRESENT bit is not set, and an exclusive access arrives from that master, then the response is UNPREDICTABLE. In this implementation, the downstream HEXOKAY must either be tied low or implemented in downstream logic to provide the correct response.

If a master, for which exclusive access is set as not supported, performs a Store exclusive that conflicts with a tag, it is considered to have gone through and the tag cleared, even if another exclusive access capable slave downstream from the AHB5 exclusive access monitor would block it. The AHB5 exclusive access monitor does not check HEXOKAY from the downstream port in this case, as it would add complexity that is very unlikely to be used in practice.

The AHB5 exclusive access monitor blocks an exclusive write by setting the HTRANS signal to idle. It does not deselect the slave by setting HSEL low which means it does not interrupt a stream of transfers from the masters, that is, locked transfers, (HMASTLOCK).

The AHB5 exclusive access monitor treats non-exclusive writes from the same master to an address already tagged by the same master in the same way as writes from a different master, that is, it clears the tag and the matching exclusive write gets an exclusive access fail response.

An exclusive read with an error response will clear the exclusive tag.

#### 2.4.2 Port list

The AHB5 exclusive access monitor has two AHB5 interfaces and associated clock and reset.

It will drive HEXOKAY upstream according to internal logic and will gate an exclusive failed write downstream.

It will still pass through the signals HEXCLS, HMASTER and have a HEXOKAY input on the downstream port. The input signals must be tied to 0, the outputs can be left open.

The following table shows the AHB5 exclusive access monitor interface signals.

#### Table 2-7 AHB5 exclusive access monitor port list

| Block  | SIGNAL  | DIRECTION | DESCRIPTION |

|--------|---------|-----------|-------------|

| System | hclk    | Input     | Clock       |

|        | hresetn | Input     | Reset       |

| Block      | SIGNAL                      | DIRECTION | DESCRIPTION                                      |

|------------|-----------------------------|-----------|--------------------------------------------------|

| AHB5 Slave | hsel_s                      | Input     | Slave select                                     |

|            | hnonsec_s                   | Input     | Non-secure transfer indicator                    |

|            | haddr_s[ADDR_WIDTH-1:0]     | Input     | Address, configurable width                      |

|            | htrans_s[1:0]               | Input     | Transfer type                                    |

|            | hsize_s[2:0]                | Input     | Size of the transfer                             |

|            | hwrite_s                    | Input     | Transfer direction indicator                     |

|            | hready_s                    | Input     | Transfer completion indicator                    |

|            | hprot_s[6:0]                | Input     | Protection control                               |

|            | hburst_s[2:0]               | Input     | Burst type                                       |

|            | hmastlock_s                 | Input     | Locked sequence indicator                        |

|            | hwdata_s[DATA_WIDTH-1:0]    | Input     | Write data, configurable width                   |

|            | hexcl_s                     | Input     | Exclusive Transfer indicator.                    |

|            | hmaster_s[MASTER_WIDTH-1:0] | Input     | Master identifier.                               |

|            | hrdata_s[DATA_WIDTH-1:0]    | Output    | Read data, configurable width                    |

|            | hreadyout_s                 | Output    | Transfer completion indicator                    |

|            | hresp_s                     | Output    | Transfer response                                |

|            | hexokay_s                   | Output    | Exclusive okay                                   |

|            | hruser_s[USER_WIDTH-1:0]    | Output    | Read channel user signals, configurable width    |

|            | hauser_s[USER_WIDTH-1:0]    | Input     | Address channel user signals, configurable width |

|            | hwuser_s[USER_WIDTH-1:0]    | Input     | Write channel user signals, configurable width   |

#### Table 2-7 AHB5 exclusive access monitor port list (continued)

| Block            | SIGNAL                      | DIRECTION | DESCRIPTION                                      |

|------------------|-----------------------------|-----------|--------------------------------------------------|

| AHB5             | hsel_m                      | Output    | Slave select pass-through                        |

| Master<br>(slave | hnonsec_m                   | Output    | Non-secure transfer indicator                    |

| initiator)       | haddr_m[ADDR_WIDTH-1:0]     | Output    | Address, configurable width                      |

|                  | htrans_m[1:0]               | Output    | Transfer type                                    |

|                  | hsize_m[2:0]                | Output    | Size of the transfer                             |

|                  | hwrite_m                    | Output    | Transfer direction indicator                     |

|                  | hready_m                    | Output    | HREADY feedback to all slaves                    |

|                  | hprot_m[6:0]                | Output    | Protection control                               |

|                  | hburst_m[2:0]               | Output    | Burst type                                       |

|                  | hmastlock_m                 | Output    | Locked sequence indicator                        |

|                  | hwdata_m[DATA_WIDTH-1:0]    | Output    | Write data, configurable width                   |

|                  | hexcl_m                     | Output    | Exclusive Transfer indicator.                    |

|                  | hmaster_m[MASTER_WIDTH-1:0] | Output    | Master identifier                                |

|                  | hrdata_m[DATA_WIDTH-1:0]    | Input     | Read data, configurable width                    |

|                  | hreadyout_m                 | Input     | Transfer completion indicator                    |

|                  | hresp_m                     | Input     | Transfer response                                |

|                  | hexokay_m                   | Input     | Exclusive okay                                   |

|                  | hruser_m[USER_WIDTH-1:0]    | Input     | Read channel user signals, configurable width    |

|                  | hauser_m[USER_WIDTH-1:0]    | Output    | Address channel user signals, configurable width |

|                  | hwuser_m[USER_WIDTH-1:0]    | Output    | Write channel user signals, configurable width   |

#### Table 2-7 AHB5 exclusive access monitor port list (continued)

#### 2.4.3 AHB5 bus properties

The following table shows the AHB5 properties of the AHB5 exclusive access monitor.

#### Table 2-8 AHB5 properties

| PROPERTY              | VALUE | COMMENT                                                                                                                           |

|-----------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| Extended_Memory_Types | TRUE  | Pass-through                                                                                                                      |

| Secure_Transfers      | TRUE  | Pass-through. Note that the secure<br>bit interacts with the AHB5<br>exclusive access monitor tagging.                            |

| Endian                | N/A   | Pass-through. The AHB5<br>exclusive access monitor provides<br>no built-in endian adaptation, it<br>functions as a simple bridge. |

#### Table 2-8 AHB5 properties (continued)

| PROPERTY             | VALUE | COMMENT                                                                                                       |

|----------------------|-------|---------------------------------------------------------------------------------------------------------------|

| Stable_Between_Clock | FALSE | Not supported for SIE-200                                                                                     |

| Exclusive_Transfers  | TRUE  | This component is used to add<br>exclusive access handling to a data<br>path that doesn't natively handle it. |

| Multi_Copy_Atomicity | TRUE  | Pass-through, no buffering.                                                                                   |

| User signaling       | TRUE  | Pass-through                                                                                                  |

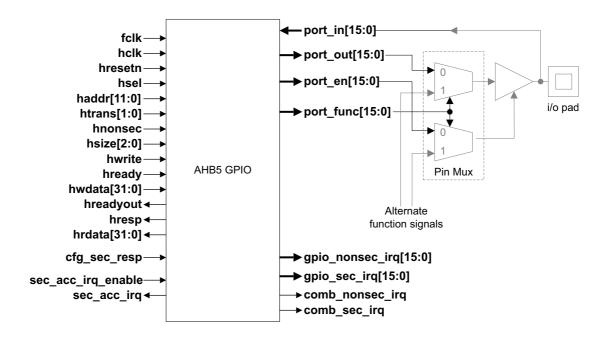

#### 2.5 AHB5 GPIO

This section describes the AHB5 GPIO.

The section contains the following subsections:

- Functional description.

- *Port list* on page 2-18.

- AHB5 bus properties on page 2-19.

#### 2.5.1 Functional description

The AHB5 GPIO is a general-purpose I/O interface unit. This IP component introduces security awareness for GPIO accesses. It separates GPIOs which can be either accessed in secure or non-secure mode only.

Figure 2-5 shows the control circuit and external interface of the AHB5 GPIO.

#### Figure 2-5 AHB5 GPIO control circuit and external interface

The AHB5 GPIO module receives transaction on the AHB5 interface which targets its register bank. The access is checked against the security configuration of the targeted register and then either accepted or responded with error or RAZ/WI depending on the value of the **cfg\_sec\_resp** input.

The Security error interrupt is set when enabled.

GPIO interrupts are only present on the appropriate GPIO\_SEC\_IRQ or GPIO\_NONSEC\_IRQ depending on the configuration parameter. The integrator needs to carefully connect the correct interrupt signals to secure or non-secure handlers in the same way as the configuration parameter is set. Interrupt pins with non-matching security attribute shall be set to 0 and shall never generate interrupt.

A combined interrupt can be used separately in secure and non-secure modes to summarize all relevant GPIO interrupts in one interrupt request.

The module can reach the GPIO ports in little endian, byte-invariant, and word-invariant big endian formats. The selected format can be configured using the endianness parameter.

The byte lane ordering is done according to the endianness parameter in both the read and write datapaths, as the endianness parameter is defined in *ARM*<sup>®</sup> *AMBA 5 AHB Protocol Specification*.

#### 2.5.2 Port list

The following table shows the port list of the AHB5 GPIO.

| Table | 2-9 | AHB5  | GPIO | port list |

|-------|-----|-------|------|-----------|

| Table | 2-3 | ALIDA | GFIU | portinat  |

| Block      | Signal          | Direction | Description                                                                                     |

|------------|-----------------|-----------|-------------------------------------------------------------------------------------------------|

| System     | hclk            | Input     | Clock AHB5 side                                                                                 |

|            | fclk            | Input     | Clock AHB5 side free running. Same phase<br>as <b>hclk</b> but cannot be gated off during sleep |

|            | hresetn         | Input     | Reset for hclk domain                                                                           |

| AHB5 Slave | hsel            | Input     | Slave select                                                                                    |

| Interface  | hnonsec         | Input     | Non-secure transfer indicator                                                                   |

|            | haddr[11:0]     | Input     | Address                                                                                         |

|            | htrans[1:0]     | Input     | Transfer type                                                                                   |

|            | hsize[2:0]      | Input     | Size of the transfer                                                                            |

|            | hwrite          | Input     | Transfer direction indicator                                                                    |

|            | hready          | Input     | HREADY feedback from all slaves                                                                 |

|            | hwdata[31:0]    | Input     | Write data                                                                                      |

|            | hrdata[31:0]    | Output    | Read data                                                                                       |

|            | hreadyout       | Output    | Transfer completion indicator                                                                   |

|            | hresp           | Output    | Transfer response                                                                               |

| GPIO       | port_in[15:0]   | Input     | GPIO input port                                                                                 |

|            | port_out[15:0]  | Output    | GPIO output port                                                                                |

|            | port_en[15:0]   | Output    | GPIO output enable port                                                                         |

|            | port_func[15:0] | Output    | Alternate function selector for each port                                                       |

| Block                           | Signal                | Direction | Description                                                                           |

|---------------------------------|-----------------------|-----------|---------------------------------------------------------------------------------------|

| Interrupts gpio_sec_irq[15:0] O |                       | Output    | Interrupt signal for each secure GPIO                                                 |

|                                 | gpio_nonsec_irq[15:0] | Output    | Interrupt signal for each non-secure GPIO                                             |

|                                 | comb_sec_irq          | Output    | Combined secure interrupt signal                                                      |

|                                 | comb_nonsec_irq       | Output    | Combined non-secure interrupt signal                                                  |

|                                 | sec_acc_irq           | Output    | Security violation interrupt                                                          |

|                                 | sec_acc_irq_enable    | Input     | Security violation interrupt enable. Enables security violation interrupt generation: |

|                                 |                       |           | 0: Security interrupt generation logic turned off                                     |

|                                 |                       |           | 1: Security interrupt generation logic turned on                                      |

| Configuration                   | cfg_sec_resp          | Input     | Response configuration in case of security violation: bus-error (1) or RAZ/WI (0).    |

#### Table 2-9 AHB5 GPIO port list (continued)

#### 2.5.3 AHB5 bus properties

The following table shows the AHB5 properties of the AHB5 GPIO.

#### Table 2-10 AHB5 properties

| Property              | Value | Comment                                                                 |

|-----------------------|-------|-------------------------------------------------------------------------|

| Extended_Memory_Types | FALSE | N/A                                                                     |

| Secure_Transfers      | TRUE  | Supported                                                               |

| Endian                | TRUE  | Configurable during implementation                                      |

| Stable_Between_Clock  | FALSE | Not supported for SIE-200                                               |

| Exclusive_Transfers   | FALSE | Not supported                                                           |

| Multi_Copy_Atomicity  | TRUE  | No caches or buffering that make a transfer visible to only some agents |

| User signaling        | FALSE | Not used                                                                |

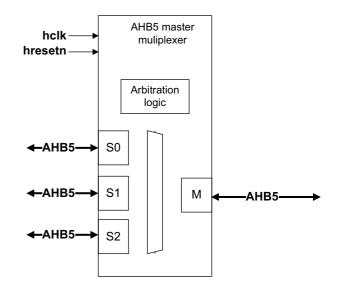

#### 2.6 AHB5 master multiplexer

This section describes the AHB5 master multiplexer.

The section contains the following subsections:

- Functional description.

- *Port list* on page 2-21.

- AHB5 bus properties on page 2-22.

#### 2.6.1 Functional description

The AHB5 master multiplexer has three slave ports to which three masters including interconnects can connect. It uses parameters to define the master port usage to avoid generating unnecessary additional logic.

Figure 2-6 shows the AHB5 master multiplexer.

#### Figure 2-6 AHB5 master multiplexer

The AHB5 master multiplexer selects the transfers going to the master port based on the input requests from the downstream side and its arbitration logic.

When a valid transfer arrives an internal request is generated towards the arbiter.

Every slave port has an input stage which contains a set of flip-flops to hold the address phase of the transfer but can also be bypassed in case the current port is selected.

When holding is required, the **hreadyout\_sx** for the corresponding interface is deasserted until the request is not selected by the arbitration logic.

The AHB5 master multiplexer uses a fixed arbitration scheme as follows:

- Port 0Same priority as port 1, round-robin scheme.Port 1Same priority as port 0, round-robin scheme.

- **Port 2** Higher priority master.

The **hmaster\_m** output signal is driven by the selected port's **hmaster\_s** input.

#### 2.6.2 Port list

The following table shows the port list of the AHB5 master multiplexer.

| Table 2-11 | AHB5 master | <sup>r</sup> multiplexer | port list |

|------------|-------------|--------------------------|-----------|

|------------|-------------|--------------------------|-----------|

| Block      | Signal                                    | Direction | Description                    |

|------------|-------------------------------------------|-----------|--------------------------------|

| System     | hclk                                      | Input     | Clock                          |

|            | hresetn                                   | Input     | Reset                          |

| AHB5 Slave | hsel_sx <sup>a</sup>                      | Input     | Slave select                   |

|            | hnonsec_sx <sup>a</sup>                   | Input     | Non-secure transfer indicator  |

|            | haddr_sx[ADDR_WIDTH-1:0] <sup>a</sup>     | Input     | Address                        |

|            | htrans_sx[1:0] <sup>a</sup>               | Input     | Transfer type                  |

|            | hsize_sx[2:0] <sup>a</sup>                | Input     | Size of the transfer           |

|            | hwrite_sx <sup>a</sup>                    | Input     | Transfer direction indicator   |

|            | hready_sx <sup>a</sup>                    | Input     | Transfer completion indicator  |

|            | hprot_sx[6:0] <sup>a</sup>                | Input     | Protection control             |

|            | hburst_sx[2:0] <sup>a</sup>               | Input     | Burst type                     |

|            | hmastlock_sx <sup>a</sup>                 | Input     | Locked sequence indicator      |

|            | hwdata_sx[DATA_WIDTH-1:0] <sup>a</sup>    | Input     | Write data, configurable width |

|            | hexcl_sx <sup>a</sup>                     | Input     | Exclusive Transfer indicator.  |

|            | hmaster_sx[MASTER_WIDTH-1:0] <sup>a</sup> | Input     | Master identifier.             |

|            | hrdata_sx[DATA_WIDTH-1:0] <sup>a</sup>    | Output    | Read data, configurable width  |

|            | hreadyout_sx <sup>a</sup>                 | Output    | Transfer completion indicator  |

|            | hresp_sx <sup>a</sup>                     | Output    | Transfer response              |

|            | hexokay_sx <sup>a</sup>                   | Output    | Exclusive okay                 |

|            | iicaokay_5a                               | Output    | Enclusive only                 |

| Block       | Signal                      | Direction | Description                                      |

|-------------|-----------------------------|-----------|--------------------------------------------------|

| AHB5 Master | hsel_m                      | Output    | Slave select pass-through                        |

|             | hnonsec_m                   | Output    | Non-secure transfer indicator                    |

|             | haddr_m[ADDR_WIDTH-1:0]     | Output    | Address                                          |

|             | htrans_m[1:0]               | Output    | Transfer type                                    |

|             | hsize_m[2:0]                | Output    | Size of the transfer                             |

|             | hwrite_m                    | Output    | Transfer direction indicator                     |

|             | hready_m                    | Output    | HREADY feedback to all slaves.                   |

|             | hprot_m[6:0]                | Output    | Protection control                               |

|             | hburst_m[2:0]               | Output    | Burst type                                       |

|             | hmastlock_m                 | Output    | Locked sequence indicator                        |

|             | hwdata_m[DATA_WIDTH-1:0]    | Output    | Write data, configurable width                   |

|             | hexcl_m                     | Output    | Exclusive Transfer indicator.                    |

|             | hmaster_m[MASTER_WIDTH-1:0] | Output    | Master identifier                                |

|             | hrdata_m[DATA_WIDTH-1:0]    | Input     | Read data, configurable width                    |

|             | hreadyout_m                 | Input     | Transfer completion indicator                    |

|             | hresp_m                     | Input     | Transfer response                                |

|             | hexokay_m                   | Input     | Exclusive okay                                   |

|             | hruser_m[USER_WIDTH-1:0]    | Input     | Read channel user signals, configurable width    |

|             | hauser_m[USER_WIDTH-1:0]    | Output    | Address channel user signals, configurable width |

|             | hwuser_m[USER_WIDTH-1:0]    | Output    | Write channel user signals, configurable width   |

#### Table 2-11 AHB5 master multiplexer port list (continued)

a. The x in \_sx indicates the number of the master interface (from 0 to 2).

#### 2.6.3 AHB5 bus properties

The following table shows the AHB5 properties of the AHB5 master multiplexer.

#### Table 2-12 AHB5 properties

| PROPERTY              | VALUE | COMMENT                   |

|-----------------------|-------|---------------------------|

| Extended_Memory_Types | TRUE  | Pass-through              |

| Secure_Transfers      | TRUE  | Pass-through              |

| Endian                | N/A   | Pass-through              |

| Stable_Between_Clock  | FALSE | Not supported for SIE-200 |

## Table 2-12 AHB5 properties (continued)

| PROPERTY             | VALUE | COMMENT                                                                 |

|----------------------|-------|-------------------------------------------------------------------------|

| Exclusive_Transfers  | TRUE  | Pass-through                                                            |

| Multi_Copy_Atomicity | TRUE  | No caches or buffering that make a transfer visible to only some agents |

| User signaling       | TRUE  | Pass-through                                                            |

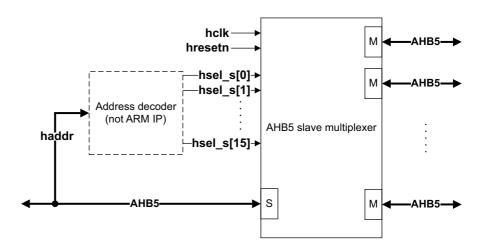

# 2.7 AHB5 slave multiplexer

This section describes the AHB5 slave multiplexer.

The section contains the following subsections:

- Functional description.

- Port list.

- AHB5 bus properties on page 2-27.

### 2.7.1 Functional description

The AHB5 slave multiplexer supports up to 16 AHB5 slaves. It uses parameters to define the slave port usage so that the synthesis process does not generate unnecessary additional logic. Figure 2-7 shows the AHB5 slave multiplexer.

### Figure 2-7 AHB5 slave multiplexer

If you require more AHB5 slave ports, you can either cascade two AHB5 slave multiplexers, or expand the design.

### 2.7.2 Port list

The following table shows the port list of the AHB5 slave multiplexer.

| Table 2-13 | AHB5 | slave | multiplexer | port list |

|------------|------|-------|-------------|-----------|

|------------|------|-------|-------------|-----------|

| Block      | Signal       | Direction | Description                |

|------------|--------------|-----------|----------------------------|

| System     | hclk         | Input     | Clock                      |

|            | hresetn      | Input     | Reset                      |

| AHB5 Slave | hsel_s[15:0] | Input     | Slave select for each port |

| Table 2-13 AHB5 slave multiplexer port list (contin |                             |           |                                                  |  |

|-----------------------------------------------------|-----------------------------|-----------|--------------------------------------------------|--|

| Block                                               | Signal                      | Direction | Description                                      |  |

|                                                     | hnonsec_s                   | Input     | Non-secure transfer indicator                    |  |

|                                                     | haddr_s[ADDR_WIDTH-1:0]     | Input     | Address, configurable width                      |  |

|                                                     | htrans_s[1:0]               | Input     | Transfer type                                    |  |

|                                                     | hsize_s[2:0]                | Input     | Size of the transfer                             |  |

|                                                     | hwrite_s                    | Input     | Transfer direction indicator                     |  |

|                                                     | hready_s                    | Input     | Transfer completion indicator                    |  |

|                                                     | hprot_s[6:0]                | Input     | Protection control                               |  |

|                                                     | hburst_s[2:0]               | Input     | Burst type                                       |  |

|                                                     | hmastlock_s                 | Input     | Locked sequence indicator                        |  |

|                                                     | hwdata_s[DATA_WIDTH-1:0]    | Input     | Write data, configurable width                   |  |

|                                                     | hexcl_s                     | Input     | Exclusive Transfer indicator.                    |  |

|                                                     | hmaster_s[MASTER_WIDTH-1:0] | Input     | Master identifier.                               |  |

|                                                     | hrdata_s[DATA_WIDTH-1:0]    | Output    | Read data, configurable width                    |  |

|                                                     | hreadyout_s                 | Output    | Transfer completion indicator                    |  |

|                                                     | hresp_s                     | Output    | Transfer response                                |  |

|                                                     | hexokay_s                   | Output    | Exclusive okay                                   |  |

|                                                     | hruser_s[USER_WIDTH-1:0]    | Output    | Read channel user signals, configurable width    |  |

|                                                     | hauser_s[USER_WIDTH-1:0]    | Input     | Address channel user signals, configurable width |  |

|                                                     | hwuser_s[USER_WIDTH-1:0]    | Input     | Write channel user signals, configurable width   |  |

| AHB5 Master                                         | hsel_mx <sup>a</sup>        | Output    | Slave select pass-through                        |  |

## Table 2-13 AHB5 slave multiplexer port list (continued)

| Block | Signal                                    | Direction | Description                                      |

|-------|-------------------------------------------|-----------|--------------------------------------------------|

|       | hnonsec_mx <sup>a</sup>                   | Output    | Non-secure transfer indicator                    |

|       | haddr_mx[ADDR_WIDTH-1:0] <sup>a</sup>     | Output    | Address, configurable width                      |

|       | htrans_mx[1:0] <sup>a</sup>               | Output    | Transfer type                                    |

|       | hsize_mx[2:0] <sup>a</sup>                | Output    | Size of the transfer                             |

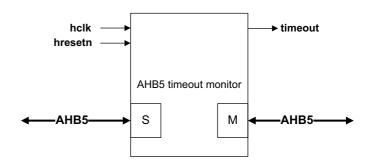

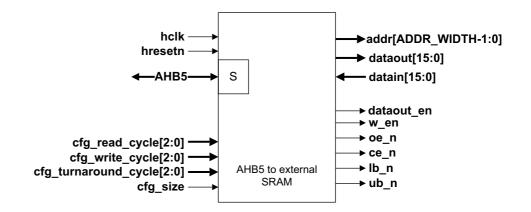

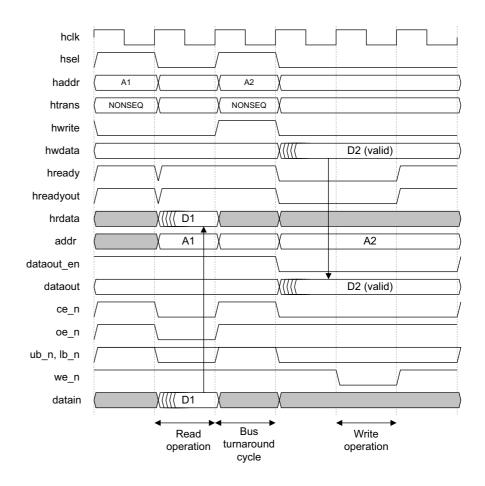

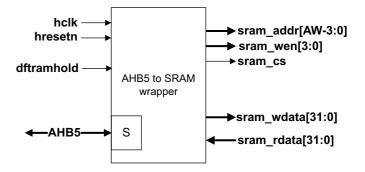

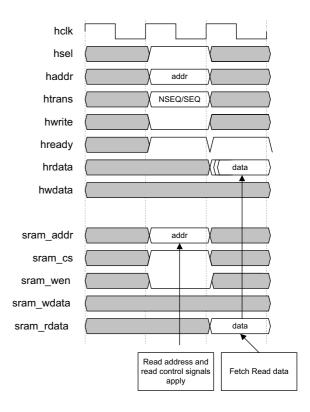

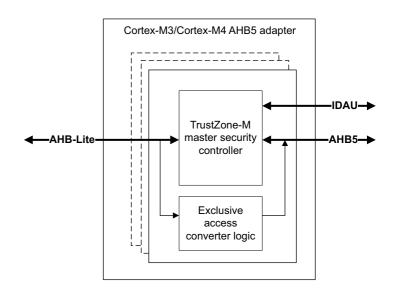

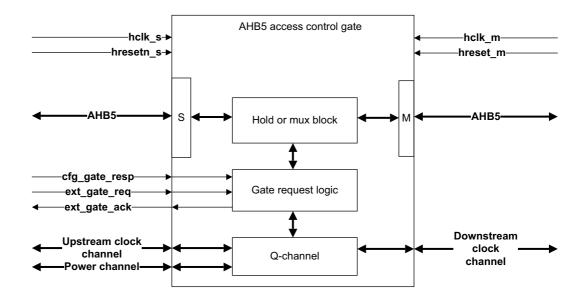

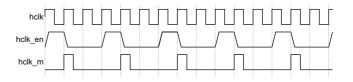

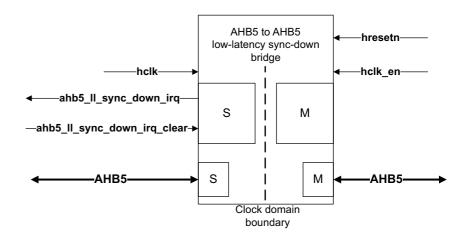

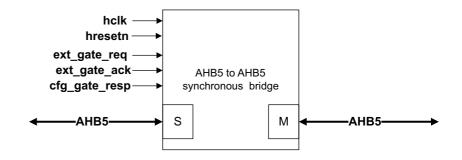

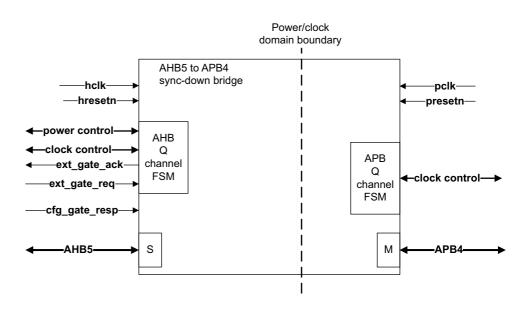

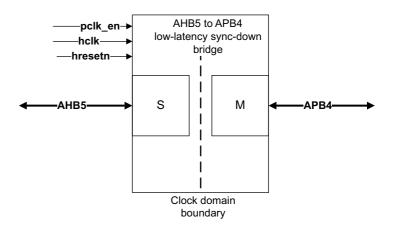

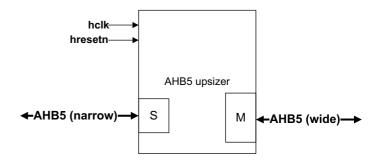

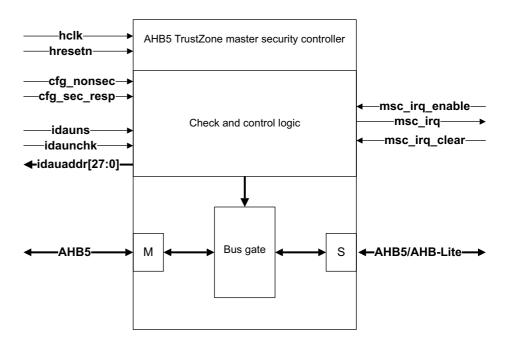

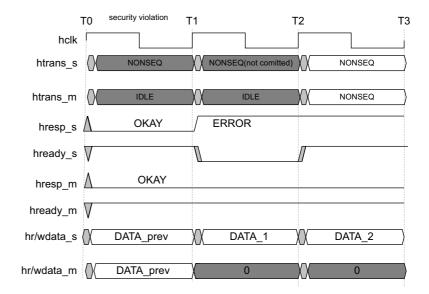

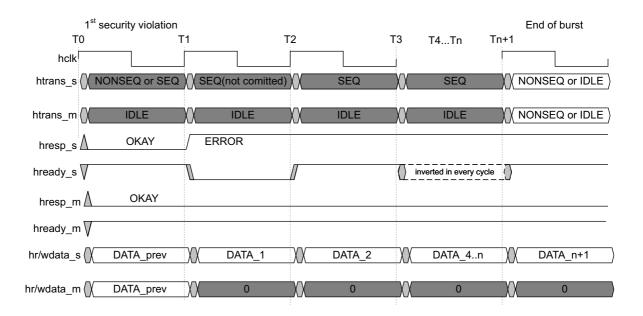

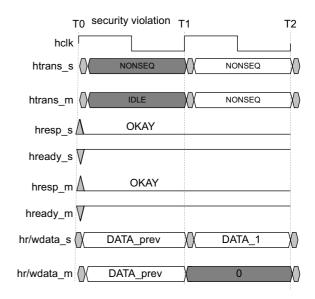

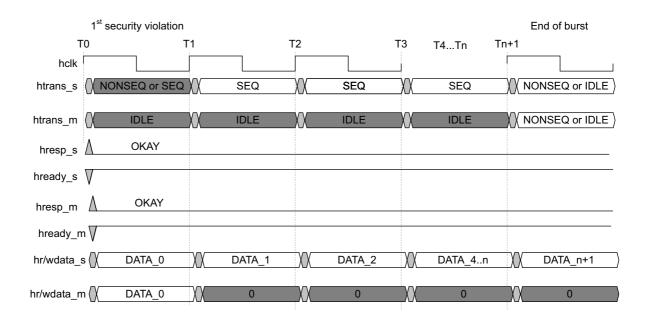

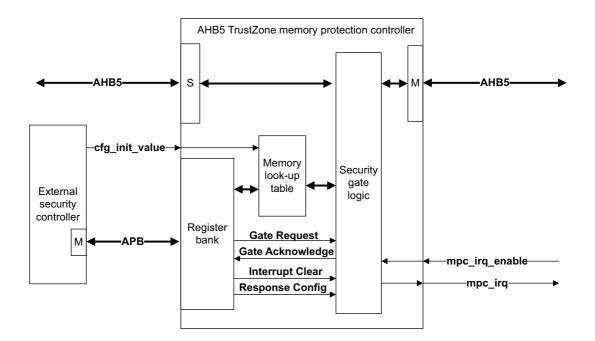

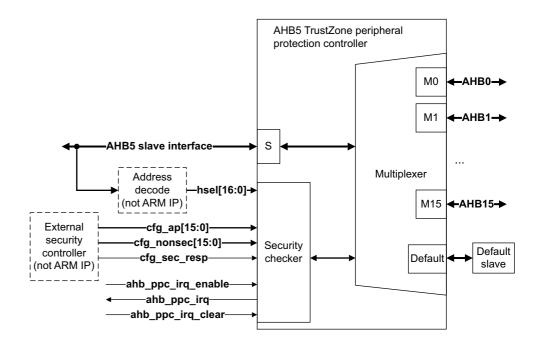

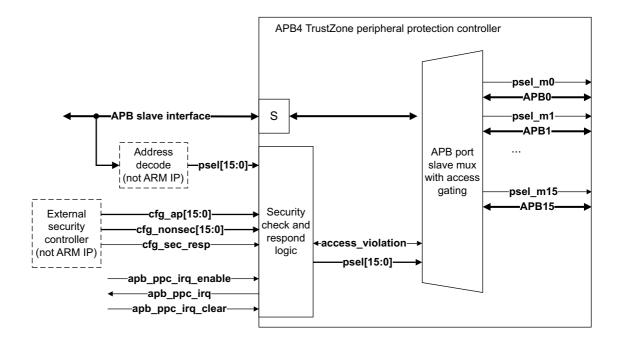

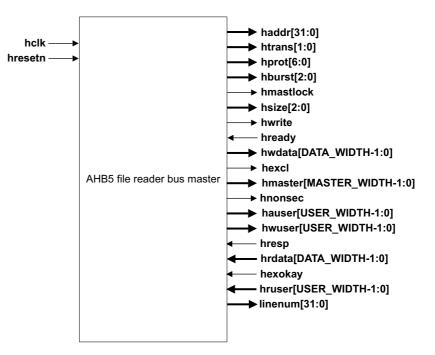

|       | hwrite_mx <sup>a</sup>                    | Output    | Transfer direction indicator                     |