# ARM CoreLink MMU-500 System Memory Management Unit

Revision: r0p0

**Technical Reference Manual**

# ARM CoreLink MMU-500 System Memory Management Unit Technical Reference Manual

Copyright © 2013 ARM. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

#### Change history

| Date           | Issue | Confidentiality  | Change                 |

|----------------|-------|------------------|------------------------|

| 22 August 2013 | A     | Non-Confidential | First release for r0p0 |

#### **Proprietary Notice**

Words and logos marked with ® or ™ are registered trademarks or trademarks of ARM® in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

# Web Address

http://www.arm.com

# Contents

# **ARM CoreLink MMU-500 System Memory Management Unit Technical Reference Manual**

|           | Pref     | face                                  |      |

|-----------|----------|---------------------------------------|------|

|           |          | About this book                       | vi   |

|           |          | Feedback                              | ix   |

| Chapter 1 | Intro    | oduction                              |      |

| •         | 1.1      | About the MMU-500                     | 1-2  |

|           | 1.2      | Compliance                            | 1-6  |

|           | 1.3      | Features                              |      |

|           | 1.4      | Interfaces                            | 1-9  |

|           | 1.5      | Configurable options                  | 1-10 |

|           | 1.6      | Product documentation and design flow |      |

|           | 1.7      | Test features                         | 1-17 |

|           | 1.8      | Product revisions                     | 1-18 |

| Chapter 2 | Fund     | ctional Description                   |      |

| •         | 2.1      | About the functions                   | 2-2  |

|           | 2.2      | Interfaces                            | 2-4  |

|           | 2.3      | Operation                             | 2-10 |

|           | 2.4      | Cache structures of the MMU-500       |      |

|           | 2.5      | Constraints and limitations of use    | 2-17 |

| Chapter 3 | Proc     | grammers Model                        |      |

|           | 3.1      | About this programmers model          |      |

|           | 3.2      | Modes of operation and execution      |      |

|           | 3.3      | Memory model                          |      |

|           | 3.4      | Register summary                      |      |

|           | <b>.</b> |                                       |      |

|            | 3.5  | Global address space 0                            | 3-12 |

|------------|------|---------------------------------------------------|------|

|            | 3.6  | Translation context address space                 | 3-24 |

|            | 3.7  | Integration registers                             | 3-25 |

|            | 3.8  | Peripheral and component identification registers |      |

| Appendix A | Sign | al Descriptions                                   |      |

|            | A.1  | Clock and resets                                  | A-2  |

|            | A.2  | ACE-Lite signals                                  | A-3  |

|            | A.3  | Low-power interface signals                       | A-11 |

|            | A.4  | Miscellaneous signals                             | A-13 |

| Appendix B | Revi | sions                                             |      |

# **Preface**

This preface introduces the  $ARM^{\otimes}$  Corelink<sup>™</sup> MMU-500 System Memory Management Unit (MMU-500) Technical Reference Manual in the following sections:

- About this book on page vi.

- Feedback on page ix.

# About this book

This book is for the MMU-500.

# **Product revision status**

The rnpn identifier indicates the revision status of the product described in this book, where:

**rn** Identifies the major revision of the product.

**pn** Identifies the minor revision or modification status of the product.

#### Intended audience

This book is written for system designers, system integrators, and programmers who are designing or programming a device that uses the MMU-500.

# Using this book

This book is organized into the following chapters:

# Chapter 1 Introduction

Read this for an introduction to the MMU-500 and its features.

# Chapter 2 Functional Description

Read this for an overview of the major functional blocks and the operation of the MMU-500.

# Chapter 3 Programmers Model

Read this for a description of the MMU-500 memory map and registers.

# **Appendix A Signal Descriptions**

Read this for a description of the MMU-500 signals.

# Appendix B Revisions

Read this for a description of the technical changes between released issues of this book.

# **Glossary**

The ARM® Glossary is a list of terms used in ARM documentation, together with definitions for those terms. The ARM® Glossary does not contain terms that are industry standard unless the ARM meaning differs from the generally accepted meaning.

See ARM® Glossary,

http://infocenter.arm.com/help/topic/com.arm.doc.aeg0014-/index.html.

# Conventions

This book uses the conventions that are described in:

- Typographical conventions on page vii.

- Signals on page vii.

# Typographical conventions

The following table describes the typographical conventions:

# Typographical conventions

| Style             | Purpose                                                                                                                                                                                                           |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| italic            | Introduces special terminology, denotes cross-references, and citations.                                                                                                                                          |

| bold              | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.                                                                             |

| monospace         | Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.                                                                                                       |

| <u>mono</u> space | Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.                                                                           |

| monospace italic  | Denotes arguments to monospace text where the argument is to be replaced by a specific value.                                                                                                                     |

| monospace bold    | Denotes language keywords when used outside example code.                                                                                                                                                         |

| <and></and>       | Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example: MRC p15, 0 <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd>                                   |

| SMALL CAPITALS    | Used in body text for a few terms that have specific technical meanings, that are defined in the <i>ARM® Glossary</i> . For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE. |

# **Signals**

The signal conventions are:

Signal level

The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals.

- LOW for active-LOW signals.

Lowercase n

At the start or end of a signal name denotes an active-LOW signal.

# **Additional reading**

This section lists publications by ARM and by third parties.

See Infocenter, http://infocenter.arm.com, for access to ARM documentation.

# **ARM** publications

This book contains information that is specific to this product. See the following documents for other relevant information:

• ARM® System Memory Management Unit Architecture Specification (ARM IHI 0062).

The following confidential books are only available to licensees:

- ARM® CoreLink™ MMU-500 System Memory Management Unit Supplement to AMBA® Designer (ADR-400) User Guide (ARM DSU 0031).

- *ARM® CoreLink™ MMU-500 System Memory Management Unit Technical Reference Manual Supplement* (ARM DSU 0030).

- *ARM® CoreLink™ MMU-500 System Memory Management Unit Implementation Guide* (ARM DII 0289).

- *ARM*<sup>®</sup> *CoreLink*<sup>™</sup> *MMU-500 System Memory Management Unit Integration Manual* (ARM DIT 0051).

- *ARM*<sup>®</sup> *CoreSight*<sup>™</sup> *Architecture Specification* (ARM DSU 0029).

- ARM® Architecture Reference Manual ARMv7-A and ARMv7-R editions (ARM DDI 0406).

- ARM® Architecture Reference Manual, ARMv8, for ARMv8-A architecture profile (ARM DDI 0487).

- $ARM^{\$}$   $AMBA^{\$}$   $AXI^{\texttt{\tiny{M}}}$  and  $ACE^{\texttt{\tiny{M}}}$  Protocol Specification  $AXI3^{\texttt{\tiny{M}}}$ ,  $AXI4^{\texttt{\tiny{M}}}$ , and  $AXI4\text{-}Lite^{\texttt{\tiny{M}}}$   $ACE^{\texttt{\tiny{M}}}$  and  $ACE\text{-}Lite^{\texttt{\tiny{M}}}$  (ARM IHI 0022).

- ARM® Low Power Interface Specification (ARM IHI 0068).

# **Feedback**

ARM welcomes feedback on this product and its documentation.

# Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

#### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

ARM also welcomes general suggestions for additions and improvements.

- The title.

- The number, ARM DDI 0517A.

- The page numbers to which your comments apply.

- A concise explanation of your comments.

ARM tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader.

# Chapter 1 **Introduction**

This chapter provides an overview of the MMU-500 in the following sections:

- About the MMU-500 on page 1-2.

- *Compliance* on page 1-6.

- Features on page 1-7.

- *Interfaces* on page 1-9.

- Configurable options on page 1-10.

- Product documentation and design flow on page 1-16.

- *Test features* on page 1-17.

- *Product revisions* on page 1-18.

# 1.1 About the MMU-500

The MMU-500 is a system-level *Memory Management Unit* (MMU), that translates an input address to an output address, by performing one or more translation table walks.

It supports the translation table formats defined by the ARM architecture, ARMv7 and ARMv8, and can perform:

- Stage 1 translations, that translate an input *Virtual Address* (VA) to an output *Physical Address* (PA) or *Intermediate Physical Address* (IPA).

- Stage 2 translations, that translate an input IPA to an output PA.

- Combined stage 1 and stage 2 translations, that translate an input VA to an output IPA and then translate that IPA to a PA. The MMU-500 performs a translation table walk for each stage of the translation.

A single stage of address translation requires a single translation table walk. This walk often requires multiple translation table lookups, that are called the levels of lookup.

In addition to translating an input address to an output address, a stage of address translation also defines the memory attributes of the output address. With a two-stage translation, the stage 2 translation can modify the attributes defined by the stage 1 translation.

A stage of address translation can be disabled, or bypassed, and the MMU-500 can define memory attributes for a bypassed stage of translation.

The MMU recognizes independent Secure and Non-secure translation contexts. A translation context provides information and resources required by the MMU-500 to process a transaction.

For the stage 1 translations that are typically associated with application and *Operating System* (OS) level operation, the VA range can be split into two subranges, each with associated translation tables and control registers.

These features mean the MMU-500 can perform all of the address translations defined by the ARMv7 and ARMv8 architectures, for memory accesses from either AArch32 state or from AArch64 state.

Stage 1 translations are supported for both Secure and Non-secure translation contexts. Usually, the appropriate OS:

- Defines the translation tables, in memory, for the stage 1 translations for its security state.

- Programs the MMU-500 to configure those stage 1 translations, and then enables the translations.

Stage 2 translations are supported only for Non-secure translation contexts. For Non-secure processor operation, the typical usage model for two stages of address translation is as follows:

The Non-secure OS defines the stage 1 address translations for application level and OS

| level operation. Typically, it does this believing it is defining the mapping from VAs to    |

|----------------------------------------------------------------------------------------------|

| PAs, but it is actually defining the mapping from VAs to IPAs.  Note                         |

| This means all the addresses the OS uses in the translation tables it defines are in the IPA |

| address space, and require a stage 2 translation to map them to the PA address space.        |

• The hypervisor defines the stage 2 address translations, that map the IPAs to PAs. It does this as part of its virtualization of one or more Non-secure guest operating systems.

The MMU-500 can cache the result of a translation table lookup in a *Translation Lookaside Buffer* (TLB). This means the MMU-500 also supports TLB maintenance operations.

For more information about:

- The features of the MMU-500, see the ARM® System Memory Management Architecture Specification.

- Address translation, including the translation table formats and TLB maintenance operations, see either:

- The ARM® Architecture Reference Manual, ARMv7-A and ARMv-7 R edition.

- The ARM® Architecture Reference Manual, ARMv8, for ARMv8-A architecture profile.

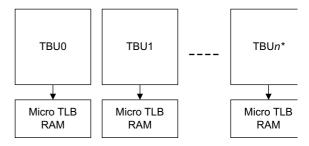

The MMU-500 has the following key components:

# Translation Buffer Unit (TBU)

The TBU contains a *Translation Look-aside Buffer* (TLB) that caches page tables. The MMU-500 implements a TBU for each connected master, and a TBU can be implemented so that it is local to the master rather than local to the MMU-500.

# Translation Control Unit (TCU)

Controls and manages the address translations. The MMU-500 implements a single TCU.

**Interconnect** Connects the multiple TBUs to the TCU.

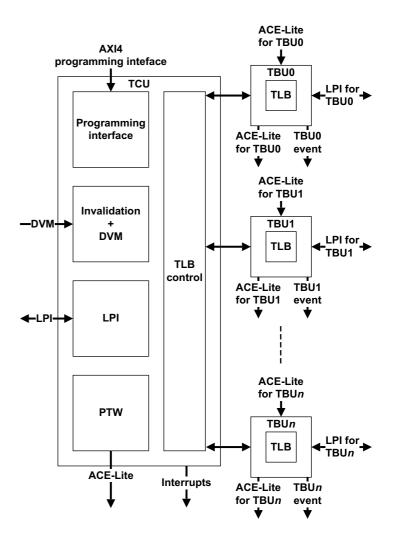

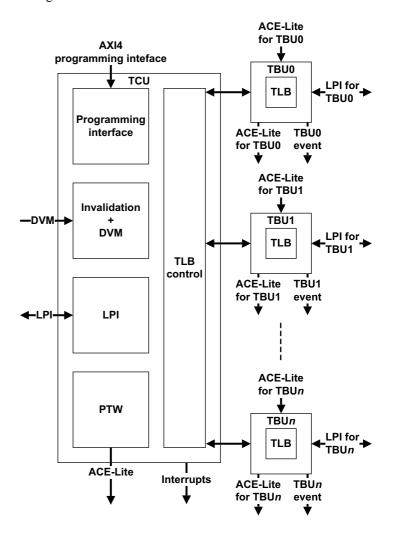

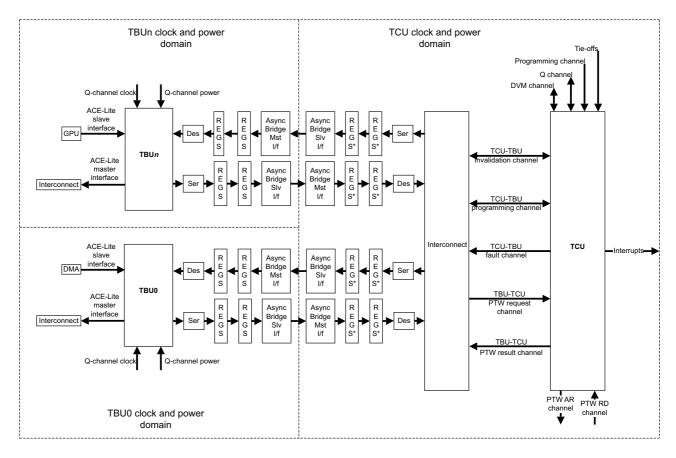

Figure 1-1 on page 1-4 shows the block diagram for MMU-500.

Figure 1-1 MMU-500 block diagram

See Chapter 2 *Functional Description* for more information about logical processing steps, interfaces, and operational features.

The following are example masters for the MMU-500:

- GPUs.

- · Video engines.

- Direct Memory Access (DMA) controllers.

- Color LCD (CLCD) controllers.

- Network controllers.

# 1.1.1 MMU-500 example system

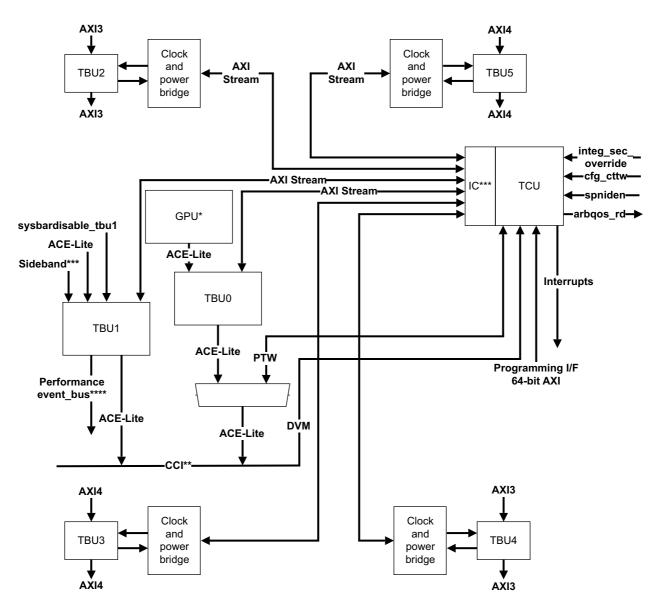

Figure 1-2 on page 1-5 shows the MMU-500 in an example ARM processor and *CoreLink*™ *Cache Coherent Interconnect-400* (CCI-400) system, performing address translation functions for a *Graphics Processor Unit* (GPU).

- \* Graphics Processor Unit (GPU) is an example master for the MMU-500.

- \* Cache Coherent Interconnect (CCI) is not a part of the MMU-500.

- \*\* Interconnect (IC).

Figure 1-2 MMU-500 in system context

<sup>\*\*\* -</sup> sysbardisable, performance event bus, and other sideband signals are present on all TBUs. These are shown on only one TBU for convenience.

# 1.2 Compliance

This TRM complements architecture reference manuals, architecture specifications, protocol specifications, and relevant external standards. It does not duplicate information from these sources.

# **ARM SMMU architecture**

The MMU-500 implements the ARM SMMU architecture v2.

See the ARM® System Memory Management Unit Architecture Specification.

### ARMv7 and v8 architecture

The MMU-500 supports the ARMv7 and ARMv8 address translation schemes. That is, it supports VMSAv7, VMSAv8-32, and VMSAv8-64. This includes support for the long-descriptor and short-descriptor translation table formats.

See the following documents:

- ARM® Architecture Reference Manual, ARMv8, for ARMv8-A architecture profile.

- ARM® Architecture Reference Manual ARMv7-A and ARMv7-R editions.

# Low-Power Interface (LPI) support

The MMU-500 supports the ARM LPI.

See the *ARM*<sup>®</sup> *Low Power Interface Specification*.

# 1.3 Features

The MMU-500 provides the following features:

- Address virtualization to processors and other bus masters in the system.

- Supports stage 1 translations, stage 2 translations, and stage 1 followed by stage 2 translations.

- Programmable Quality of Service (QoS).

- Distributed translation support for up to 32 TBUs.

- Translation support for 32-bit to 49-bit virtual address ranges and 48-bit physical address ranges.

See the following documents:

- ARM® Architecture Reference Manual, ARMv8, for ARMv8-A architecture profile.

- ARM® Architecture Reference Manual ARMv7-A and ARMv7-R editions.

- Multiple transaction contexts can apply to address translations for specific streams of transactions.

- Supports up to 64 configurable contexts and programmable page size. The MMU-500 maps each context by using an input stream ID from the master device that requires address translation.

- Translation support for the following:

- Stage 1 ARMv7 VMSA.

- ARMv8 AArch32.

- AArch64 with 4KB and 64KB granules.

- Stage 1 followed by stage 2 translations.

See the following documents:

- ARM® Architecture Reference Manual, ARMv8, for ARMv8-A architecture profile.

- ARM® Architecture Reference Manual ARMv7-A and ARMv7-R editions.

- Supports 1-bit error detection in the TBU, and 1-bit error detection and correction in the TCU.

- Supports 4KB, 64KB, 1MB, 2MB, 16MB, 512MB, and 1GB page sizes.

See the following documents:

- ARM® Architecture Reference Manual, ARMv8, for ARMv8-A architecture profile.

- ARM® Architecture Reference Manual ARMv7-A and ARMv7-R editions.

- Arbitrates transactions from different TBUs by using the programmed QoS value.

- Provides page table walk cache for storing intermediate page table walk data.

- Caches page table entries in the TLB.

- Supports TLB *Hit-Under-Miss* (HUM).

- Provides configurable 4-32 PTW depth.

- Provides TLB invalidation through the AMBA 4 DVM signalling or register programming.

See the  $ARM^{\otimes}$   $AMBA^{\otimes}$   $AXI^{\bowtie}$  and  $ACE^{\bowtie}$  Protocol Specification  $AXI3^{\bowtie}$ ,  $AXI4^{\bowtie}$ , and  $AXI4\text{-}Lite^{\bowtie}$   $ACE^{\bowtie}$  and  $ACE\text{-}Lite^{\bowtie}$  for more information on the DVM.

- Supports translation and protection checks including support for TrustZone® extensions.

- Fault handling, logging, and signalling that includes demand paging and the support for the stall model.

- Debug and performance-monitoring events.

- One AMBA slave interface that supports ACE-Lite for connecting the bus master device that requires address translations.

- See the ARM® CoreLink™ MMU-500 System Memory Management Unit Implementation Guide for more information on connecting AXI3 or AXI4 devices.

- One AMBA master interface for master device transactions or PTWs that support ACE-Lite and DVM.

- See the *ARM*<sup>®</sup> *CoreLink*<sup>™</sup> *MMU-500 System Memory Management Unit Implementation Guide* for more information on connecting AXI3 or AXI4 devices.

- An AXI4 interface for programming or configuration.

The MMU-500 is based on the ARM® System Memory Management Unit Architecture Specification.

# 1.4 Interfaces

The MMU-500 supports the following interfaces:

- TCU interfaces:

- Programming interface.

- Interrupts.

- TBU interfaces:

- ACE-Lite interface.

- Sideband interfaces. (Stream interface and security state determination interface.)

- Common interfaces:

- LPI and clock gating.

- Performance interface.

- Tie-off signal interface.

See *Interfaces* on page 2-4 for more information.

# 1.5 Configurable options

Table 1-1 shows the options that the MMU-500 implementer can configure. The configurable options of the MMU-500 are classified as follows:

- TBU options.

- TCU options.

**Table 1-1 Configurable options**

| Parameter                                 | Range                                       | Description                                                                                                                                                                                                                                  |  |

|-------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TCU options                               |                                             |                                                                                                                                                                                                                                              |  |

| Number of configurable TBUs               | 1-16                                        | Use this to select the number of unique TBU configurations. Each TBU configuration can be instantiated multiple times, using the TBU mapping.                                                                                                |  |

| Number of TBUs                            | 1-32                                        | Use this to select the total number of TBUs.                                                                                                                                                                                                 |  |

| TBU mapping                               | 1-16                                        | Each TBU can be mapped to a TBU configuration, using the configuration number.                                                                                                                                                               |  |

| StreamID - width of the sideband signal   | 1-10                                        | Use this to select the width of the stream ID sideband signal on each TBU.  The stream ID is specified on the sideband signals, and dedicated sideband signals are used for read and write accesses. See <i>Stream ID</i> on page 2-11.      |  |

| AXI programming interface ID signal width | 1-23                                        | Use this to select the programming interface AXI ID width.                                                                                                                                                                                   |  |

| PTW has a dedicated AXI port              | Enable or disable                           | Use this to select a dedicated AXI interface for PTWs. This ensures that the other TBU0 AXI interface is reserved for device transactions.                                                                                                   |  |

| PTW AXI data bus width                    | 64 or 128                                   | Use this to set the width, in bits, of the TCU AXI data bus that is used for PTWs.  This option is applicable only when the TCU has a dedicated AXI port for PTWs.                                                                           |  |

| Only stage 2 translations                 | Enable or disable                           | Use this to configure the TCU to support stage 2 only or stage 1 followed by stage 2 translation. You can set the value to one of the following:  Enable Only the stage 2 translation is supported.  Disable All translations are supported. |  |

| Number of contexts                        | 1, 2, 4, 8, 16, 32, or 64                   | Use this to specify the number of contexts. Select the value as one, only when the device is configured for Only stage 2 translations.                                                                                                       |  |

| Number of SMRs                            | 2, 4, 8, 16, 24, 32, 40, 48, 56, 64, or 128 | Use this to set the number of <i>Stream Mapping Registers</i> (SMR) groups.                                                                                                                                                                  |  |

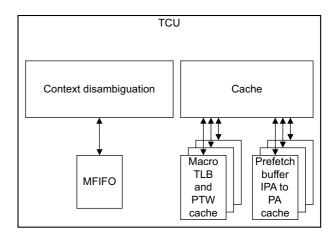

| PTW depth                                 | 4, 8, 16, 24, or 32                         | Use this to set the number of PTWs.                                                                                                                                                                                                          |  |

| Macro-TLB depth                           | 0, 8, 128, 256, 512, 1024, or 2048          | Use this to set the macro-TLB depth.                                                                                                                                                                                                         |  |

| PTW cache depth                           | 4, 32, 64, or 128                           | Use this to set the depth of the PTW cache, the IPA to PA translation cache, and the prefetch buffer.                                                                                                                                        |  |

Table 1-1 Configurable options (continued)

| Parameter                                          | Range                                | Description                                                                                                                                                                                                                        |

|----------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TBU options                                        |                                      |                                                                                                                                                                                                                                    |

| Name                                               | NA                                   | Use this to set the name of the TBU.                                                                                                                                                                                               |

| AXI ID signal width                                | 1-23 bits                            | Use this to select the incoming AXI ID width.                                                                                                                                                                                      |

| AXI data bus width                                 | 64 or 128 bits                       | Use this to set the width, in bits, of the AXI data bus.                                                                                                                                                                           |

| Depth of write buffer                              | 0, 4, 8, or 16                       | Use this to select the depth of the write buffer.  The write buffer can accommodate multiple bursts up to the depth of the buffer.  The MMU-500 does not stall the write data path for                                             |

|                                                    |                                      | transactions that the write buffer can hold.  The MMU-500 stalls transactions that cannot fit in the write buffer.                                                                                                                 |

| TLB depth                                          | 2, 8, 16, 32, 40, 48, 56, 64, or 128 | Use this to specify the TLB depth.                                                                                                                                                                                                 |

| Implement the TLB using the memory                 | Enable or disable                    | When enabled, you can implement the TLB using RAM. Otherwise, the MMU-500 implements the TLB as flip-flops. Implementing the TLB as RAM optimizes area, but the setup and clock-to-Q delay is higher compared to using flip-flops. |

| Width of the AXI slave interface<br>AWUSER signals | 2-128 bits                           | Use this to set the width of the AXI slave interface AWUSER signals.  Note  You must set the input user width to two bits more than the required data width. See the AWUSER signal in the Table A-3 on page A-4.                   |

| Width of the AXI slave interface<br>WUSER signals  | 1-128 bits                           | Use this to set the width of the AXI slave interface <b>WUSER</b> signals.                                                                                                                                                         |

| Width of the AXI slave interface<br>BUSER signals  | 1-128 bits                           | Use this to set the width of the AXI slave interface <b>BUSER</b> signals.                                                                                                                                                         |

| Width of the AXI slave interface<br>ARUSER signals | 2-128 bits                           | Use this to set the width of the AXI slave interface ARUSER signals.  Note  You must set the input user width to two bits more than the required data width. See the ARUSER signal in the Table A-9 on page A-7.                   |

| Width of the AXI slave interface<br>RUSER signals  | 1-128 bits                           | Use this to set the width of the AXI slave interface <b>RUSER</b> signals.                                                                                                                                                         |

| TBU in separate clock and power<br>domains         | Enable or disable                    | Enable this to configure a clock and power domain cross bridge between the TBU-TCU and TCU-TBU paths.  When disabled, the TBU and TCU are in the same clock and power domain.                                                      |

**Table 1-1 Configurable options (continued)**

| Parameter                                                             | Range          | Descripti                                                                                                                                         | ion                                                                                                                                                                                                     |

|-----------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Depth of the asynchronous first-in first-out buffer on the TCU to the | 0, 2, 4, or 10 | Use this to cross bridg                                                                                                                           | configure a buffer in the clock and power domain ge.                                                                                                                                                    |

| TBU channel                                                           |                |                                                                                                                                                   | n is applicable only when the TBU is in a separate power domain.                                                                                                                                        |

| TBU-TCU channel width                                                 | 0, 1, or 2     | Use this to configure the width of the data path bet TCU and the TBU, and the width of the serial data can set the width to one of the following: |                                                                                                                                                                                                         |

|                                                                       |                | 0                                                                                                                                                 | Full width, 14 bytes. By selecting this option, you can send all TBU-TCU messages as one packet. The data width between TBU-TCU is HIGH, but the message delay can be LOW.                              |

|                                                                       |                | 1                                                                                                                                                 | Half width, 7 bytes. By selecting this option, you can send all TBU-TCU messages as two packets. The data width is half of the full width option, and a trade-off between message delay and data width. |

|                                                                       |                | 2                                                                                                                                                 | 1 byte. By selecting this option, TBU-TCU messages can use maximum 14 clocks. The data width is only one byte, and used to connect lower priority TBUs.                                                 |

| Security options                                                      |                |                                                                                                                                                   |                                                                                                                                                                                                         |

| SSD index signal width                                                | 0-10 bits      | Non-secure                                                                                                                                        | specify the SSD index signal width as 0, the e state is directly assigned to the incoming sideband ong with the transaction.                                                                            |

|                                                                       |                | Writes                                                                                                                                            | Non-secure state = wsb_ns, where wsb_ns is the write sideband signal for security.                                                                                                                      |

|                                                                       |                |                                                                                                                                                   | The Security State Determination (SSD) index is zero for a Secure access and it is one for a Non-secure master.                                                                                         |

|                                                                       |                | Reads                                                                                                                                             | Non-secure state = <b>rsb_ns</b> , where <b>rsb_ns</b> is the read sideband signal for security.                                                                                                        |

|                                                                       |                |                                                                                                                                                   | The SSD index is zero for a Secure access and it is one for a Non-secure access.                                                                                                                        |

|                                                                       |                |                                                                                                                                                   | driven on the sideband signal SSD index signal is pointer into the SSD index table.                                                                                                                     |

|                                                                       |                |                                                                                                                                                   | configure at least one programmable or fixed e entry in the SSD index table.                                                                                                                            |

**Table 1-1 Configurable options (continued)**

| Parameter                                                                                              | Range                                                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Specify use of SSDIndex0-7 Specify SSDIndex0-7                                                         | Disable Secure Programmable-Secure Programmable-Non-secure | Use this to specify Secure entries in the SSD index table.  These options are applicable only when the width of the SSD index signal is greater than zero.  When the SSD index is determined, the SSD index table comprises bits from 0-2SSD index signal width-1. You must determine the status of all the bits as follows:  List of non-programmable indices:  For these indices, the security state of the master is defined and does not change.  You must specify the indices of the masters whose security states are always Secure.  List of programmable indices:  You can program the security state of these indices.  You must determine the default state of each master whose security state is programmable.  An SSD index is programmable or non-programmable, and is in the Secure or Non-secure state. By default, an SSD index is in the non-programmable Non-secure state.  For example, if the SSD index signal width is 6-bit, there are 64 indices in the range 0-63, whose security states must be determined. |

| TBU timing options                                                                                     |                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| AWUSER slave interface registering options  WUSER slave interface registering options                  | Forward Reverse Full Bypass                                | Each AXI channel has a configurable register slice in the MMU-500 slave interface.  An I/O delay of 70 percent of the clock is assumed for interfaces that are driven to, or driven by, a register.  An I/O delay of 40 percent of the clock is assumed for bypassed interfaces.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BUSER slave interface registering options  ARUSER slave interface registering options                  | -                                                          | bypassed interfaces.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RUSER slave interface registering options                                                              | _                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TBU-TCU channel prebridge register slice 1 options  TBU-TCU channel prebridge register slice 2 options | Forward Reverse Full Bypass                                | <ul> <li>Each TBU-TCU channel has 0-4 configurable register slices:</li> <li>0-2 register slices between the TBU and the clock and power domain cross bridge.</li> <li>0-2 register slices between the clock and power domain cross bridge and the TCU.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TBU-TCU channel postbridge register slice 1 options                                                    | _                                                          | cross bridge and the TCU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TBU-TCU channel postbridge register slice 2 options                                                    |                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

**Table 1-1 Configurable options (continued)**

| Parameter                                           | Range              | Description                                                                                                                              |

|-----------------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| TCU-TBU channel prebridge register slice 1 options  | Forward<br>Reverse | Each TCU-TBU channel has 0-4 configurable register slices:  • 0-2 register slices between the TCU and the clock and                      |

| TCU-TBU channel prebridge register slice 2 options  | Full<br>Bypass     | <ul> <li>power domain cross bridge.</li> <li>0-2 register slices between the clock and power domain cross bridge and the TBU.</li> </ul> |

| TCU-TBU channel postbridge register slice 1 options | _                  | orose orage and the TBe.                                                                                                                 |

| TCU-TBU channel postbridge register slice 2 options | _                  |                                                                                                                                          |

# 1.5.1 Output ID width

The following equation defines the output ID width of all TBUs, other than TBU0 in multiplexed configurations:

• TBU output width = Incoming AXI ID width + 1.

\_\_\_\_\_Note \_\_\_\_\_

The extra bit is required for barrier transactions generated by TBU to identify the transactions that are generated by the TBU.

If the AXI interface between TBU0 and TCU is multiplexed, then the output ID width is based on:

- The number of parallel PTW supported in the TCU.

- The input AXI ID width in TBU0.

If the TCU has a separate AXI interfaces, then:

• TCU Output ID width = TCUIDW + 1.

Where,

- TCUIDW = log base 2<sup>Nummax\_of\_parallel\_PTW</sup>.

- Nummax\_of\_parallel\_PTW is the number of parallel PTW queues adjusted to the smallest power of two that is greater than this number, if the number is not already a power of 2.

\_\_\_\_\_ Note \_\_\_\_\_

The extra bit is required to identify the synchronous complete transaction.

The output AXI ID width follows the following rules:

- When the TBU ID width is in the range 0-TCUIDW, the output width is TCUIDW + 2.

- For TBUIDW > TCUIDW, the output width is TBUIDW + 1.

The value driven on the AXI ID signal is:

• Passing through the incoming transaction on the TBU, with the following address translation condition:

If TBUIDW is 0

All 0s.

# If TBUIDW is not 0

Incoming ID, appending with all 0s in the MSB.

- All 1s when the TBU generates a synchronous transaction, all 1s.

- 0b10 followed by 0s until TCUIDW when the TCU generates a PTW transaction. The TCU drives the ID in the range (TCUIDW-1) to 0.

- 0b110 followed by 0s when the TCU generates a synchronous complete transaction.

# 1.6 Product documentation and design flow

This section describes the MMU-500 books and how they relate to the design flow.

See *Additional reading* on page vii for more information about the books described in this section. For information on the relevant architectural standards and protocols, see *Compliance* on page 1-6.

# 1.6.1 Documentation

The MMU-500 documentation is as follows:

# **Technical Reference Manual**

The *Technical Reference Manual* (TRM) describes the functionality and the effects of functional options on the behavior of the MMU-500. It is required at all stages of the design flow. The choices made in the design flow can mean that some behavior described in the TRM is not relevant. If you are programming the MMU-500 then contact:

- The implementer to determine:

- The build configuration of the implementation.

- What integration, if any, was performed before implementing the MMU-500.

- The integrator to determine the pin configuration of the device that you are using.

# **Implementation Guide**

The *Implementation Guide* (IG) describes:

- The available build configuration options and related issues in selecting them

- How to configure the *Register Transfer Level* (RTL) with the build configuration options.

- The processes to sign off the configured design.

The ARM product deliverables include reference scripts and information about using them to implement your design.

The IG is a confidential book that is only available to licensees.

# **Integration Manual**

The *Integration Manual* (IM) describes how to integrate the MMU-500 into an SoC. It describes the pins that the integrator must tie off to configure the macrocell for the required integration. Some of the integration is affected by the configuration options used when implementing the MMU-500.

The IM is a confidential book that is only available to licensees.

# **User Guide Supplement**

The User Guide Supplement describes how to use the *AMBA*<sup>®</sup> *Designer* (ADR-400) application to build and configure the MMU-500.

# **Technical Reference Manual Supplement**

The TRM Supplement describes how to intialize the MMU-500, and how the MMU-500 generates final memory attributes.

# 1.7 Test features

The MMU-500 includes the clock gating circuitry that you can use to enable the clock during MMU-500 testing.

The *Design For Test* (DFT) port, **dftclkenable**, allows you to bypasses architectural clock gates during a DFT shift.

# 1.8 Product revisions

This section describes the differences in functionality between product revisions of the MMU-500:

**r0p0** First release.

# Chapter 2 **Functional Description**

This section describes the functional operation of the MMU-500 in the following sections:

- *About the functions* on page 2-2.

- *Interfaces* on page 2-4.

- *Operation* on page 2-10.

- Cache structures of the MMU-500 on page 2-15.

- Constraints and limitations of use on page 2-17.

# 2.1 About the functions

The TBU and TCU are the major functional blocks of the MMU-500. The TBU caches frequently used address ranges and the TCU performs the page table walk.

Figure 2-1 shows the block diagram for MMU-500.

Figure 2-1 MMU-500 block diagram

The MMU-500 applies the following logical processing steps to every transaction that flows in:

- 1. Determines the security state of the device that originates the transaction. The security attribute presented on **AWPROT[1]** and **ARPROT[1]** is different from the security state of the device. Identifying the security state of the device is called security state determination.

- 2. Maps an incoming transaction to one of the contexts using an incoming stream ID.

- 3. Caches frequently used address ranges using the TLB. The best-case hit latency of this caching is two clocks when the TBU address slave register slices are not specified. The best-case latency is three clocks when the TBU address slave register slices are specified.

- 4. Performs the main memory PTW automatically on an address miss.

5. Shares with the processor the page table formats as specified in the *Large Physical Address Extension* (LPAE) for maximum efficiency.

For more information on LPAE addresses, see the following documents:

- ARM® Architecture Reference Manual ARMv7-A and ARMv7-R edition.

- ARM® Architecture Reference Manual, ARMv8, for ARMv8-A architecture profile.

- 6. Applies the required fault handling for every transaction.

- 7. Performs debug and performance monitoring through programmable performance counters, and reports statistics. For example, TLB refills or number of read or write accesses.

# 2.2 Interfaces

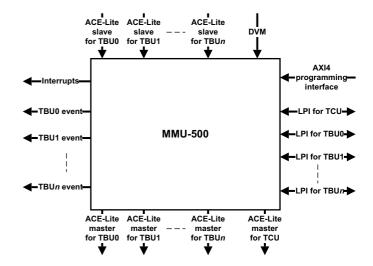

Figure 2-2 shows the MMU-500 interfaces.

Figure 2-2 Interfaces of the MMU-500

\_\_\_\_ Note \_\_\_\_\_

You can connect AXI3 interface, but you must tie-off the inactive ACE-Lite signals.

The MMU-500 contains the following interfaces:

- TCU interfaces.

- TBU interfaces on page 2-5.

- *Common interfaces* on page 2-7.

# 2.2.1 TCU interfaces

The MMU-500 supports the following TCU interfaces:

- Programming interface.

- *Interrupts* on page 2-5.

# **Programming interface**

The MMU-500 requires a programming interface to permit the software to configure the controller and to initialize the memory devices. See *Modes of operation and execution* on page 3-3 for information about using the 64-bit AXI4 programming interface.

The MMU-500 provides 32-bit address buses, **awaddr\_prog[31:0]** and **araddr\_prog[31:0]**, but it only uses bits[23:2]. The MMU-500 ignores:

- Bits[31:24], but their presence facilitates the process of integrating the MMU-500 with adjacent RTL blocks, such as an interconnect.

- Bits[1:0], because the MMU-500 only permits word accesses to its internal registers.

This interface operates at the same frequency as the TCU clock.

# Interrupts

This interface provides global, per-context, and performance interrupts. See *Interrupt signals* on page A-13 for more information.

#### 2.2.2 TBU interfaces

The MMU-500 supports the following TCU interfaces:

• *ACE-Lite interfaces*.

The ACE-Lite interface supports the following interfaces:

- AXI slave interface.

- AXI master interface.

- Snoop channel interface on page 2-6.

- TBU barrier support on page 2-6.

- *Sideband interface* on page 2-6.

The sideband interface supports the following interfaces:

- Stream interface on page 2-7.

- Security State Determination interface on page 2-7.

#### **ACE-Lite interfaces**

The MMU-500 uses the ACE-Lite interfaces to receive transactions, translate transactions, and perform PTWs.

You can connect the AXI3 or AXI4 bus to this interface with certain limitations as described in *AXI3 and AXI4 support* on page 2-17.

In this mode, the MMU-500 generates barrier transactions and updates attributes of input barrier transactions. Barrier transactions guarantee the ordering and observation of transactions in a system.

See the  $ARM^{\otimes}$   $AMBA^{\otimes}$  AXI and ACE Protocol Specification  $AXI3^{\text{\tiny TM}}$ ,  $AXI4^{\text{\tiny TM}}$ , and  $AXI4\text{-}Lite^{\text{\tiny TM}}$  ACE and  $ACE\text{-}Lite^{\text{\tiny TM}}$  for more information on barrier transactions.

The MMU-500 supports DVM signaling for TLB maintenance operations on its PTW port.

### AXI slave interface

The MMU-500 supports only the ACE-Lite slave interface for every TBU. You must tie the extra ACE-Lite signals to their inactive values and the **sysbardisable\_<tbuname>** signal to HIGH to use the AXI3 or AXI4 interfaces.

You must connect pin-to-pin the read address, write address, read data, write data, and buffered write response channels of the ACE-Lite slave interface, with \_s suffix, to an ACE-Lite master interface. In a system, the master interface can be the AXI bus infrastructure output, or the output of a bridge that converts another bus protocol to AXI.

| —— Note ———                |                                                      |

|----------------------------|------------------------------------------------------|

| A PTW read interface might | be present depending on the specified configuration. |

# AXI master interface

The MMU-500 supports only the ACE-Lite master interface for every TBU and PTW read interface of the TCU. You must tie the extra ACE-Lite signals to their inactive values and the **sysbardisable\_<tbundered** signal to HIGH to use AXI3 or AXI4 interfaces.

The ACE-Lite master interface, with \_m suffix, drives the translated address to the downstream slave. You must connect pin-to-pin the read address, write address, read data, write data, and buffered write response channels to the corresponding ACE-Lite slave interface.

If the MMU-500 is configured to support a dedicated interface for PTWs, you must connect the read address and read data channels of the slave interface associated with the PTWs to the MMU-500 PTW channel. In this configuration, the PTW channel contains the \_ptw suffix. For example, araddr ptw and acaddr ptw.

| Note                       | -                                               |          |

|----------------------------|-------------------------------------------------|----------|

| A PTW read interface might | t be present depending on the specified configu | ıration. |

# Snoop channel interface

The AC channel of the ACE-Lite interface of the MMU-500 is connected to the CCI-driven AC channel or to the ACE-compatible slave interface that supports DVM messaging. ARM recommends that you use the DVM channel for TLB maintenance operations. If the system cannot access the DVM channel, the **acvalid** signal must be tied LOW, and the programming interface can be used for TLB maintenance operations.

When you configure the MMU-500 to provide a dedicated AXI channel to perform PTWs, the AC channel must be part of the PTW channel.

This interface supports the following:

#### Snoop data channel

The snoop data channel is not connected to the MMU-500.

Note ———

The snoop data channel is not supported in the MMU-500.

# Snoop address channel

The 44-bit wide snoop address channel is connected to the TCU.

# TBU barrier support

The TBU in the MMU-500 receives, passes on, and generates barriers of its own in response to the **SYNC** signal received from the TCU DVM channel.

The MMU-500 generates the DSBSYS barrier after ensuring that all invalidation-related transactions are initiated on receiving one of the following:

- The programmed SYNC message.

- The DVM **SYNC** message.

See the  $ARM^{\circledast}$   $AMBA^{\circledast}$  AXI and ACE Protocol Specification  $AXI3^{\mathsf{TM}}$ ,  $AXI4^{\mathsf{TM}}$ , and AXI4- $Lite^{\mathsf{TM}}$  ACE and ACE- $Lite^{\mathsf{TM}}$  for more information on  $\mathbf{SYNC}$  and  $\mathbf{DVM}$   $\mathbf{SYNC}$  messages.

#### Sideband interface

This interface provides associated information along with the ACE-Lite interface. See *Sideband signals* on page A-13 for more information.

| Note                                                                                       |              |

|--------------------------------------------------------------------------------------------|--------------|

| he stream and security state determination are associated with the ACE-Lite slave ach TBU. | interface to |

| 120.                                                                                       |              |

#### Stream interface

This interface is a sideband interface for the MMU-500 TBU slave interface. It provides information about the translation mechanism that the MMU-500 applies to an incoming transaction.

The MMU-500 samples signals in the interface along with each valid address transaction.

See Stream ID on page 2-11 for more information.

# Security State Determination interface

This interface is a sideband interface for the MMU-500 TBU slave interface. It provides information about the security state of a transaction.

Similar to the *Stream interface*, the MMU-500 samples signals in this interface along with each valid address transaction.

See Security determination on page 2-11 for more information.

#### 2.2.3 Common interfaces

The MMU-500 supports the following interfaces that are common to TBUs and the TCU:

- Low-power interface for clock gating and power control.

- *Performance interface* on page 2-9.

- *Tie-off signal interface* on page 2-9.

# Low-power interface for clock gating and power control

The MMU-500 contains Low-power interfaces that enable:

- Power gating of the TBU module.

- Clock gating of the TBU module.

- Clock gating of the TCU module.

You can control the power-control interfaces at the system level by a system power-control module. Alternatively, if there is no system control block, you must tie the **qreqn\_\*** inputs HIGH, and can leave the outputs, **qacceptn\_\*** and **qactive\_\***, unconnected.

The MMU-500 never denies a powerdown request, and therefore you must tie LOW the **qdeny** \* input to the system power controller.

You must powerup the TCU module to powerup a TBU module.

The LPI signals are not synchronized. The system must provide the synchronous signals to the MMU-500.

The MMU-500 provides low-power interface and clock gating support in the following manner:

- The TBU and TCU have dedicated Q-channel interfaces for clock gating:

- qreqn\_tbu\_<tbuname>\_cg, qacceptn\_tbu\_<tbuname>\_cg, and qactive tbu <tbuname> cg.

- qreqn tcu, qacceptn tcu, and qactive tcu.

- The TBU and the clock or power bridge each have a dedicated Q-channel interface for entering the power-down state:

- qreqn\_tbu\_<tbuname>\_pd and qacceptn\_tbu\_<tbuname>\_pd.

- qreqn\_pd\_slv\_br\_<tbuname> and qacceptn\_pd\_slv\_br\_<tbuname>.

- qreqn\_pd\_mst\_br\_<tbuname> and qacceptn\_pd\_mst\_br\_<tbuname>.

\_\_\_\_ Note \_\_\_\_\_

If the TBU in separate clock and power domains option is disabled, you must tie the **qreqn\_tbu\_<tbuname>\_pd** and **qreqn\_pd\_br\_<tbuname>** signals HIGH.

- The clock or power bridge contains the following **qactive** signals:

- The qactive\_br\_tbu\_<tbuname> signal for handling the cross-boundary clock wakeup to wakup the TBU clock.

- The qactive\_br\_tcu\_<tbuname> signal for handling the cross-boundary clock wakeup to wakeup the TCU clock.

Figure 2-3 shows the possible clock and power domains of the MMU-500.

<sup>\*</sup> AXI stream register slice

Figure 2-3 Clock and power domains of the MMU-500

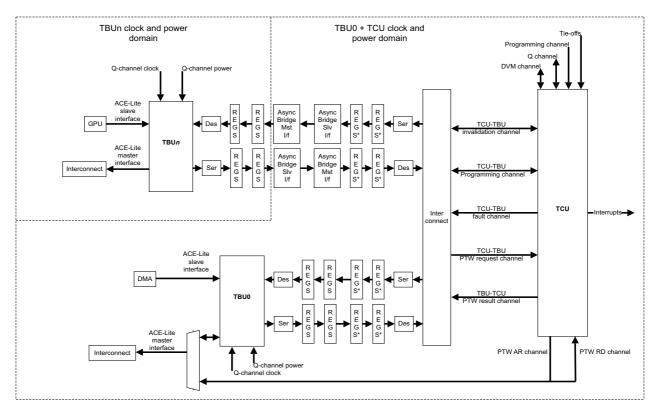

Figure 2-4 on page 2-9 shows a scenario in which the TBU0 and the TCU share a common clock or power domain and a PTW read channel.

<sup>\*</sup> AXI stream register slice

Figure 2-4 Sharing a common clock or power domain and PTW read channel

See the following documents for more information about low-power interface:

- ARM® Low Power Interface Specification.

- ARM® CoreLink MMU-500 System Memory Management Unit Integration Manual.

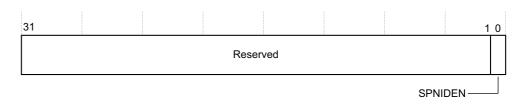

# Performance interface

This interface contains the input signal **spniden**, which indicates whether security events need to be considered in the performance counters.

The performance interface also contains an event output interface that provides updates from each TBU to the performance counters.

See *Performance event signals* on page A-14 and *Authentication interface signal* on page A-14 for more information.

# Tie-off signal interface

This interface provides configuration information about certain functionality. See *Tie-off signals* on page A-14 for more information.

# 2.3 Operation

The MMU-500 routes each translation through the following logical processing steps:

- 1. Security state determination.

- 2. Context determination.

- 3. Page table walk, if the translation is not cached in the TLB.

- 4. Protection checks.

- 5. Attribute generation or merging, depending on the programming.

You can configure the MMU-500 to bypass the transaction process for a transaction or to fault a transaction regardless of the translation state.

The primary function of the MMU-500 is to provide address translations from an input address to an output address, based on address mapping and memory attribute information stored in translation tables

The MMU-500 uses the following steps to achieve this:

- 1. Receives an address transaction, along with security and stream information.

- 2. Uses the security information received along with a transaction to determine the further processing steps for the transaction. The received security information is the security state of the originator of a transaction. The MMU-500 uses a Secure or Non-secure set of registers, for additional processing of a transaction, depending on the security state of the originator is Secure or Non-secure, respectively. See Security determination on page 2-11 for more information.

- 3. Uses the stream information received along with the transaction to determine the translation mechanism to apply to the transaction. The translation mechanism can be a bypass, a stage 1 translation, a stage 2 translation, or a stage 1 followed by stage 2 translation. See the *ARM® System Memory Management Unit Architecture Specification* for more information.

- 4. Adds the fault information to the Global Fault Status Register if a fault is identified in the translation process before a context is mapped. The MMU-500 adds the fault information to the Context Banks Fault Status Register if a fault is identified after the context mapping. A fault results in an interrupt when interrupt reporting is enabled. You can clear interrupts by clearing the Fault Status Register.

- See the ARM® System Memory Management Unit Architecture Specification for more information.

- 5. The MMU-500 supports both little and big endian translation tables. You can program endianness in the SMMU\_CBn\_SCTLR register. See *ARM® Architecture Reference Manual ARMv7-A and ARMv7-R editions* for more information.

See the *ARM® CoreLink™ MMU-500 System Memory Management Unit Technical Reference Manual Supplement* for information about initialization and configuration.

This section describes how the  $ARM^{\$}$  CoreLink<sup>™</sup> MMU-500 System Memory Management Unit operates, and contain the following subsections:

- Stream ID on page 2-11.

- Security determination on page 2-11.

- *Hit-Under-Miss* on page 2-12.

- Fault handling on page 2-13.

- *Implementation defined operational features* on page 2-13.

#### 2.3.1 Stream ID

A stream ID is used to map the incoming transaction to a context by using the stream mapping table. The characteristics of the stream ID are as follows:

- The width of the stream ID is selected during the MMU-500 configuration.

- You must specify the stream ID on a dedicated AXI sideband signal. Select the Stream ID

width of the sideband signal parameter value from the range 1-10 bits, and dedicated sideband signals are used for read and write transactions.

For more information about streamID signals, see *Sideband signals* on page A-13.

The stream ID width in the TCU is a constant 15-bits. The stream ID from each TBU is zero-extended to form a 10-bit field appended to a 5-bit TBU ID field, making it 15-bits wide. This arrangement ensures that the stream ID presented to each TBU must not be unique, and happens at the TCU. If the Stream ID presented to each TBU is already unique, and the TBU ID addition is not required, then you must ensure that the TBU ID field is masked in the SMR.

See the ARM® System Memory Management Unit Architecture Specification for more information on stream ID-to-context mapping.

# 2.3.2 Security determination

The MMU-500 determines the Secure ownership of a transaction in one of the following ways:

- Assigns the Non-secure state to an incoming sideband signal along with a transaction:

- For write accesses, the Non-secure state is the write sideband signal for security.

- For read accesses, the Non-secure state is the read sideband signal for security.

- Determines the security state of a master by using the input signals,

wsb\_ssd\_<tbuname>\_s and rsb\_ssd\_<tbuname>\_s, that index an SSD index into the SSD index table. The entry in the SSD index table determines whether the master that initiated the transaction is Secure or Non-secure. For more information about SSD signals, see Sideband signals on page A-13.

- You can configure the width of the SSD index in the range 0-10 bits. The MMU-500 uses a separate SSD index for each TBU.

- You can configure the number of programmable entries in the SSD table in the range 1-32. The security state determination address space supports 15-bit wide SSD indices. This space is equally divided among 32 TBUs starting with TBU0 from the bottom of the address space. Each TBU contains 1024 entries.

- You can program the security state of the SSD table entries at runtime, or specify the non-programmable and fixed SSD table entries at configuration time.

After the SSD index is determined, the SSD table contains bits from 0 to 2<sup>SSD index signal width</sup>\_1. You must determine the status of the bits as follows:

## List of non-programmable indices

For these indices, the security state of the master is defined, and does not change.

You must specify the indices of the masters whose security states are always Secure.

#### List of programmable indices

You can program the security state of the programmable indices.

You must determine the default state of each master whose security state is programmable.

An SSD index can be programmable or non-programmable, and can be in the Secure or Non-secure state. By default, an SSD index is in the non-programmable Non-secure state.

| Note  |  |

|-------|--|

| 11016 |  |

An entry must not be duplicated in more than one list.

You must specify at least one programmable or fixed Non-secure entry for every configuration.

The number of indices is determined by the configured SSD index signal width. For example, if the SSD index signal width is six bits, there are 64 indices in the range 0-63. You must program the indices to be one of:

- Programmable Secure.

- Programmable Non-secure.

- Non-programmable Secure.

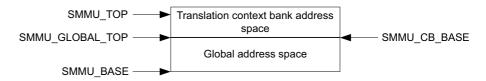

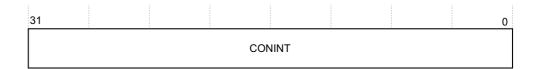

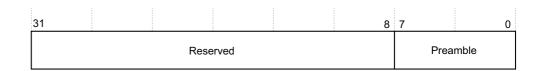

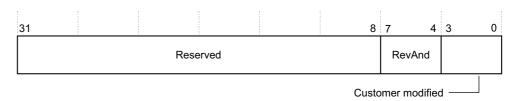

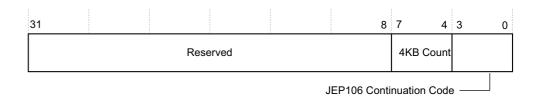

The unprogrammed indices default to non-programmable Non-secure.