# ARM<sup>®</sup> CoreLink<sup>®</sup> GIC-500 Generic Interrupt Controller

Revision: r0p0

**Technical Reference Manual**

Copyright © 2014 ARM. All rights reserved. ARM DDI 0516B (ID060914)

## ARM CoreLink GIC-500 Generic Interrupt Controller Technical Reference Manual

Copyright © 2014 ARM. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

|               |       |                  | Change history          |

|---------------|-------|------------------|-------------------------|

| Date          | Issue | Confidentiality  | Change                  |

| 30 April 2014 | А     | Non-Confidential | First release for r0p0  |

| 21 May 2014   | В     | Non-Confidential | Second release for r0p0 |

#### **Proprietary Notice**

Words and logos marked with \* or \* are registered trademarks or trademarks of ARM\* in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

## Contents ARM CoreLink GIC-500 Generic Interrupt Controller Technical Reference Manual

Preface

|           |       | About this book<br>Feedback         |      |

|-----------|-------|-------------------------------------|------|

| Chapter 1 | Intro | oduction                            |      |

|           | 1.1   | About the GIC-500                   | 1-2  |

|           | 1.2   | Compliance                          | 1-6  |

|           | 1.3   | Features                            | 1-7  |

|           | 1.4   | Interfaces                          | 1-8  |

|           | 1.5   | Configurable options                | 1-9  |

|           | 1.6   | Test features                       | 1-10 |

|           | 1.7   | Product documentation               | 1-11 |

|           | 1.8   | Product revisions                   | 1-12 |

| Chapter 2 | Fund  | ctional Description                 |      |

| -         | 2.1   | About the functions                 | 2-2  |

|           | 2.2   | Interfaces                          | 2-3  |

|           | 2.3   | Operation                           | 2-7  |

|           | 2.4   | Clocking and resets                 | 2-14 |

|           | 2.5   | Constraints and limitations         | 2-15 |

| Chapter 3 | Prog  | grammers Model                      |      |

| -         | 3.1   | About the GIC-500 programmers model |      |

|           | 3.2   | The GIC-500 register map            |      |

|           | 3.3   | Distributor register summary        |      |

|           | 3.4   | Distributor register descriptions   |      |

|            | 3.5                 | Distributor registers for message-based SPIs summary                     | 3-11 |  |

|------------|---------------------|--------------------------------------------------------------------------|------|--|

|            | 3.6                 | Redistributor registers for control and physical LPIs summary            |      |  |

|            | 3.7                 | Redistributor register descriptions                                      |      |  |

|            | 3.8                 | Redistributor registers for SGIs and PPIs summary                        |      |  |

|            | 3.9                 | ITS control register summary                                             |      |  |

|            | 3.10                | ITS control register descriptions                                        |      |  |

|            | 3.11                | ITS translation register summary                                         | 3-21 |  |

|            | 3.12                | Implementation defined test registers in GICD page summary               | 3-22 |  |

|            | 3.13                | Implementation defined test registers in the GICR page for PPIs and SGIs | 3-25 |  |

|            | 3.14                | Implementation defined test registers in the GITS control page summary   | 3-28 |  |

| Appendix A | Signal Descriptions |                                                                          |      |  |

| ••         | A.1                 | Clock and reset signals                                                  | A-2  |  |

|            | A.2                 | Miscellaneous signals                                                    | A-3  |  |

|            | A.3                 | Interrupt signals                                                        | A-4  |  |

|            | A.4                 | Test signals                                                             |      |  |

|            | A.5                 | AXI4 slave interface signals                                             | A-6  |  |

|            | A.6                 | AXI4 master interface signals                                            | A-8  |  |

|            | A.7                 | GIC Stream master interfaces                                             | A-10 |  |

|            | A.8                 | GIC Stream slave interfaces                                              | A-11 |  |

|            | A.9                 | MBIST interface signals                                                  | A-12 |  |

| Appendix B | Revis               | sions                                                                    |      |  |

## Preface

This preface introduces the *ARM*<sup>®</sup> *CoreLink*<sup>™</sup> *GIC-500 Generic Interrupt Controller Technical Reference Manual*. It contains the following sections:

- *About this book* on page vi.

- *Feedback* on page ix.

## About this book

This technical reference manual is for the CoreLink GIC-500 *Generic Interrupt Controller* (GIC).

| Product revision status | S                                                                                                                                                                                                                                                                                                      |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | The <i>rmpn</i> identifier indicates the revision status of the product described in this book, for example, r1p2, where:<br><b>rm</b> Identifies the major revision of the product, for example, r1.                                                                                                  |

|                         | <b>p</b> <i>n</i> Identifies the minor revision or modification status of the product, for example, p2.                                                                                                                                                                                                |

| Intended audience       |                                                                                                                                                                                                                                                                                                        |

|                         | This book is for system designers, system integrators, and programmers who are designing or programming a <i>System-on-Chip</i> (SoC) that uses the GIC-500.                                                                                                                                           |

| Using this book         |                                                                                                                                                                                                                                                                                                        |

|                         | This book contains the following chapters:                                                                                                                                                                                                                                                             |

|                         | Chapter 1 Introduction                                                                                                                                                                                                                                                                                 |

|                         | Read this for an introduction to the GIC-500 and its features.                                                                                                                                                                                                                                         |

|                         | Chapter 2 Functional Description                                                                                                                                                                                                                                                                       |

|                         | Read this for a description of the major interfaces and for the implementation-defined behavior of the GIC-500.                                                                                                                                                                                        |

|                         | Chapter 3 Programmers Model                                                                                                                                                                                                                                                                            |

|                         | Read this for a description of the memory map and registers, and for information about programming the device.                                                                                                                                                                                         |

|                         | Appendix A Signal Descriptions                                                                                                                                                                                                                                                                         |

|                         | Read this for a description of the input and output signals.                                                                                                                                                                                                                                           |

|                         | Appendix B Revisions                                                                                                                                                                                                                                                                                   |

|                         | Read this for a description of the technical changes between released issues of this book.                                                                                                                                                                                                             |

| Glossary                |                                                                                                                                                                                                                                                                                                        |

|                         | The <i>ARM</i> <sup>®</sup> <i>Glossary</i> is a list of terms used in ARM documentation, together with definitions for those terms. The <i>ARM</i> <sup>®</sup> <i>Glossary</i> does not contain terms that are industry standard unless the ARM meaning differs from the generally accepted meaning. |

|                         | See the ARM <sup>®</sup> Glossary<br>http://infocenter.arm.com/help/topic/com.arm.doc.aeg0014-/index.html.                                                                                                                                                                                             |

| Conventions             |                                                                                                                                                                                                                                                                                                        |

|                         | This book uses the conventions that are described in:                                                                                                                                                                                                                                                  |

|                         | • Typographical conventions on page vii.                                                                                                                                                                                                                                                               |

|                         | • Signals on page vii.                                                                                                                                                                                                                                                                                 |

|                         |                                                                                                                                                                                                                                                                                                        |

### **Typographical conventions**

The following table describes the typographical conventions:

### Typographical conventions

| Style             | Purpose                                                                                                                                                                                                                              |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| italic            | Introduces special terminology, denotes cross-references, and citations.                                                                                                                                                             |

| bold              | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.                                                                                                |

| monospace         | Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.                                                                                                                          |

| <u>mono</u> space | Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.                                                                                              |

| monospace italic  | Denotes arguments to monospace text where the argument is to be replaced by a specific value.                                                                                                                                        |

| monospace bold    | Denotes language keywords when used outside example code.                                                                                                                                                                            |

| <and></and>       | Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example: MRC p15, 0 <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd>                                                      |

| SMALL CAPITALS    | Used in body text for a few terms that have specific technical meanings, that are defined in the <i>ARM</i> <sup>®</sup> <i>Glossary</i> . For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE. |

### Signals

The signal conventions are:

| Signal level | The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means: |

|--------------|-------------------------------------------------------------------------------------------------------------|

|              | <ul><li>HIGH for active-HIGH signals.</li><li>LOW for active-LOW signals.</li></ul>                         |

| Lowercase n  | At the start or end of a signal name denotes an active-LOW signal.                                          |

### Additional reading

This section lists publications by ARM and by third parties.

See Infocenter http://infocenter.arm.com, for access to ARM documentation.

### **ARM** publications

This book contains information that is specific to this product. See the following documents for other relevant information:

- ARM<sup>®</sup> AMBA<sup>®</sup> AXI and ACE Protocol Specification (ARM IHI 0022).

- ARM<sup>®</sup> AMBA<sup>®</sup> 4 AXI4-Stream Protocol Specification (ARM IHI 0051).

- ARM<sup>®</sup> Generic Interrupt Controller Stream Protocol Interface Specification (ARM IHI 0066).

- *ARM*<sup>®</sup> Generic Interrupt Controller Architecture Specification version 3.0 and version 4.0 (ARM IHI 0069).

- *ARM*<sup>®</sup> *Architecture Reference Manual, ARMv8, for ARMv8-A architectural profile* (ARM DDI 0487).

The following confidential books are only available to licensees:

- *ARM*<sup>®</sup> CoreLink<sup>™</sup> GIC-500 Generic Interrupt Controller Implementation Guide (ARM DII 0288).

- *ARM*<sup>®</sup> CoreLink<sup>™</sup> GIC-500 Generic Interrupt Controller Integration Manual (ARM DIT 0050).

### Other publications

•

This section lists relevant documents published by third parties:

JEDEC Standard Manufacturer's Identification Code, JEP106 http://www.jedec.org.

## Feedback

ARM welcomes feedback on this product and its documentation.

### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- The title.

- The number, ARM DDI 0516B.

- The page numbers to which your comments apply.

- A concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

### \_\_\_\_\_Note \_\_\_\_\_

ARM tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader.

## Chapter 1 Introduction

This chapter introduces the GIC-500. It contains the following sections:

- *About the GIC-500* on page 1-2.

- *Compliance* on page 1-6.

- *Features* on page 1-7.

- *Interfaces* on page 1-8.

- *Configurable options* on page 1-9.

- *Test features* on page 1-10.

- *Product documentation* on page 1-11.

- *Product revisions* on page 1-12.

## 1.1 About the GIC-500

The GIC-500 is a build-time configurable interrupt controller that supports up to 128 cores. The GIC-500 only supports cores that implement the ARMv8 architecture and the GIC CPU interface with the standard GIC Stream Protocol interface, such as Cortex\*-A57 and Cortex-A53. It implements the *ARM*\* *Generic Interrupt Controller Architecture Specification version 3.0*, to enable support for:

- ARMv8 cores.

- Physical interrupt signals.

- Software Generated Interrupts (SGIs).

- Interrupts generated by writing to the AXI4 slave port, known as message-based interrupts.

- An *Interrupt Translation Service* (ITS) that provides ID translation and core migration for message-based interrupts.

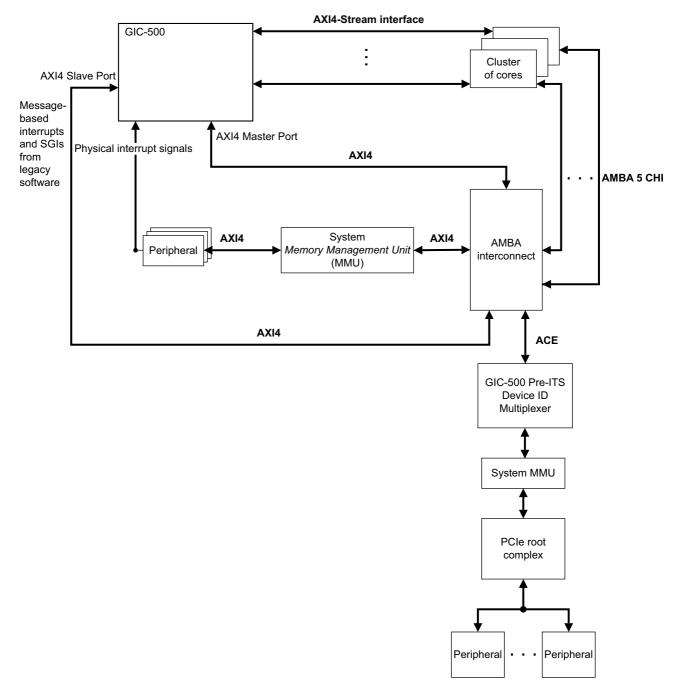

Figure 1-1 on page 1-3 depicts the GIC-500 in an example system.

Figure 1-1 GIC-500 in an example system

The GIC-500 receives interrupts from the AXI4 slave, or from physical inputs, depending on the type of interrupt. The GIC-500:

- Supports a few different types of interrupt with different characteristics. See *Interrupt types* on page 2-7.

- Prioritizes the interrupts and ensures that the highest priority pending interrupt is sent to the CPU interface. The CPU interface is part of the interrupt controller which is not part of the GIC-500, but is instead part of compatible ARMv8 cores. ARM recommends the

CPU interfaces are programmed using System register accesses, although legacy software might program them using memory-mapped accesses, depending on what the core supports.

- Connects to these CPU interfaces using dedicated AXI4-Stream interfaces.

- Is programmed using its AXI4 Slave port.

- Supports virtualization of interrupts for each connected CPU interface that provides this feature.

- ITS provides interrupt ID translation that can allow peripherals to be programmed by a virtual machine directly.

- Provides registers for managing interrupt sources, interrupt behavior, and interrupt routing to one or more cores.

Connected ARM cores have System registers that provide the CPU interface to the GIC.

### 1.1.1 Topologies and terminology

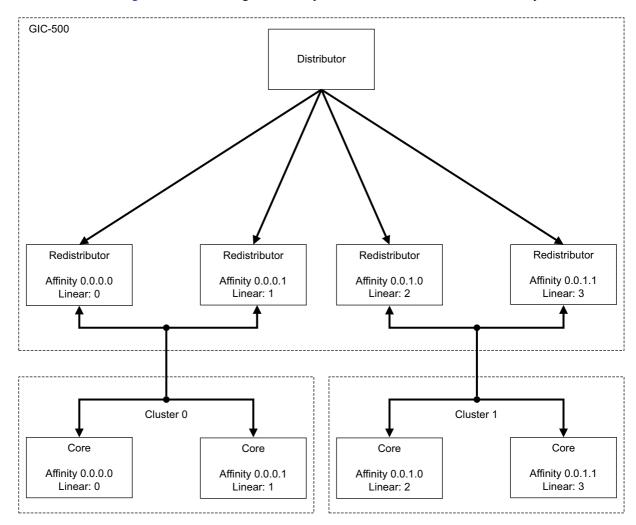

Figure 1-2 shows a diagrammatic representation of the Redistributor hierarchy.

### Figure 1-2 Redistributor hierarchy

— Note —

The linear representation indicates the order of the cores, that is sorted by the affinity values. For example 0.0.1.1 is given the value of 3 because it is the fourth lowest affinity value in the system.

The ARM architecture defines a register in a core that identifies the logical address of the core in the system. This register, known as the *Multiprocessor Affinity Register* (MPIDR), has a hierarchical format. Each level of the hierarchy is known as an affinity level, with the highest affinity levels specified first:

- For an ARMv7 processor, the MPIDR defines three levels of affinity, with an implicit affinity level 3 value of 0.

- For an ARMv8 processor, the MPIDR defines four levels of affinity.

This means the affinity can be specified, using a four-field dot-decimal notation, as <Aff3>.<Aff2>.<Aff1>.<Aff0>, where Affn is a value for affinity level n.

For most processors, for example the Cortex-A57 MPCore processor, the processor is made up from a cluster of cores that have a common affinity level 1. Each core must have a different MPIDR value, so the cores have different affinity level 0 values, beginning from 0. For example, a processor with four cores might have MPIDR values in the range 0.0.0.0-0.0.0.3. If there were two processors then the second processor might have values in the range 0.0.1.0-0.0.1.3. Typically the processor number is affinity level 1 and the core number is affinity level 0.

The GIC-500 only supports topologies where affinity levels 2 and above are the same. That is, all cores must have MPIDR values of the form 0.0.c.d, where c and d are variables. The range for c is assumed to start at 0 and be contiguous. The range for d is also assumed to start at 0 and be contiguous for each c. For example, the first processor must have IDs 0.0.0.0 to 0.0.0.x and the second processor must have IDs 0.0.1.0 to 0.0.1.y.

The GIC-500 supports up to 128 cores in up to 32 processors with a limit of eight cores per processor, and has a pair of AXI4-Stream interfaces for each processor.

When using backwards compatibility mode, GIC-500 supports the first eight cores. That is, it supports the eight cores with the lowest MPIDR values, whether they are in the same processor or not.

GIC-500 provides a Redistributor for each core, each with a corresponding set of registers. Many registers in the GIC-500 use the MPIDR value to specify cores. However, programming the Interrupt Translation Service and integrating the AXI4 slave port require an alternative linear representation. This representation is based on numbering the cores in order of increasing affinity level, starting at 0. For example, in backwards compatibility mode, GIC-500 supports cores 0-7 in linear representation.

## 1.2 Compliance

٠

The GIC-500 is compliant with the following interfaces and specifications:

- The AMBA AXI4 protocol. See the *ARM*<sup>®</sup> *AMBA*<sup>®</sup> *AXI and ACE Protocol Specification*, and *AXI4 slave interface signals* on page A-6.

- The GIC Stream protocol is based on the following specifications:

- ARM<sup>®</sup> AMBA<sup>®</sup> 4 AXI4-Stream Protocol Specification.

- ARM<sup>®</sup> Generic Interrupt Controller Stream Protocol Interface Specification.

- Version 3.0 of the ARM GIC architecture specification. See the *ARM*<sup>®</sup> *Generic Interrupt Controller Architecture Specification version 3.0.*

## 1.3 Features

The GIC-500 provides registers for managing interrupt sources, interrupt behavior, and interrupt routing to one or more cores. It supports:

- Multiprocessor environments with up to 128 cores.

- Up to 32 affinity-level 1 clusters.

- Up to eight cores for each cluster.

- The following interrupt types:

- Locality-specific Peripheral Interrupts (LPIs). These interrupts are generated by a peripheral writing to a memory-mapped register in the GIC-500. See Configurable options for the GIC-500 RTL on page 1-9.

- Shared Peripheral Interrupts (SPIs). See Configurable options on page 1-9.

- 16 Private Peripheral Interrupts (PPIs), that are independent for each core and can be programmed to support either edge-triggered or level-sensitive interrupts.

- 16 SGIs, that are generated either by using software to write to GICD\_SGIR or through the GIC CPU interface of a core.

- *Interrupt Translation Service* (ITS). This provides device isolation and ID translation for message-based interrupts, which allows virtual machines to program devices directly.

- Memory-mapped access to all registers.

- Interrupt masking and prioritization.

- Programmable interrupt routing based on affinity.

- Three different interrupt groups, which allow interrupts to target different exception levels:

- Group 0.

- Non-secure Group 1.

- Secure Group 1.

- A global *Disable Security* (DS) bit. This allows support for systems with and without security.

- 32 priority values, five bits for each interrupt.

## 1.4 Interfaces

The GIC-500 provides the following external interfaces:

- *AXI4 Slave Interface* on page 2-3.

- *AXI4 Master Interface* on page 2-4.

- *RAM Interfaces* on page 2-5.

- *Physical interrupt signals* on page 2-5.

- *GIC-500 Stream Protocol Interface* on page 2-6.

- *Other core signals* on page 2-6.

## 1.5 Configurable options

Table 1-1 shows the configurable options in the GIC-500 RTL.

| Feature                                                                   | Range of options                                                                                                                                                                                                                                                                                                                         |  |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Number of affinity-level 1 clusters.                                      | 1-32                                                                                                                                                                                                                                                                                                                                     |  |

| Number of cores for each cluster. This can be different for each cluster. | 1-8                                                                                                                                                                                                                                                                                                                                      |  |

| Read Address ID width.                                                    | 1-32                                                                                                                                                                                                                                                                                                                                     |  |

| Write Address ID width.                                                   | 1-32                                                                                                                                                                                                                                                                                                                                     |  |

| Number of SPIs.                                                           | 32-960 <sup>a</sup>                                                                                                                                                                                                                                                                                                                      |  |

| GICv2 backwards compatibility support.                                    | <ul> <li>Options include:</li> <li>Both Secure and Non-secure AREs are always set in GICD_CTLR. There is no backwards compatibility.</li> <li>Both Secure and Non-secure AREs are programmable The GIC-500 resets to backward compatible mode.</li> <li>See <i>Backwards compatibility</i> on page 2-10 for more information.</li> </ul> |  |

| Security Support.                                                         | <ul> <li>Options include:</li> <li>Security support programmable. Resets to supporting security.</li> <li>Security support not present.</li> </ul>                                                                                                                                                                                       |  |

| ITS and LPI support.                                                      | <ul> <li>Options include:</li> <li>ITS is present. LPIs are supported.</li> <li>ITS is not present. LPIs are not supported.</li> </ul>                                                                                                                                                                                                   |  |

| ITS Device ID width.                                                      | 3-20<br>See <i>AXI4 Slave Interface</i> on page 2-3 for more information.                                                                                                                                                                                                                                                                |  |

| Number of LPI cache entries.                                              | 16-1024 (powers of two only).                                                                                                                                                                                                                                                                                                            |  |

Table 1-1 Configurable options for the GIC-500 RTL

a. Range from 32-960, with increments of 32.

## 1.6 Test features

The GIC-500 provides *Design For Test* (DFT) signals for test mode. See *Test signals* on page A-5.

## 1.7 Product documentation

This section describes the GIC-500 documentation, how it relates to the design flow, and the relevant architectural standards and protocols.

### **Technical Reference Manual**

The *Technical Reference Manual* (TRM) describes the functionality and the effects of functional options on the behavior of the GIC-500. It is required at all stages of the design flow. Some behavior described in the TRM might not be relevant because of the way that the GIC-500 is implemented and integrated. If you are programming the GIC-500 then contact:

- The implementer to determine the build configuration of the implementation.

- The integrator to determine the signal configuration of the SoC that you are using.

The TRM complements protocol specifications and relevant external standards. It does not duplicate information from these sources.

### **Implementation Guide**

The Implementation Guide (IG) describes:

- The available build configuration options and related issues if you select them.

- How to configure the *Register Transfer Level* (RTL) with the build configuration options.

- The processes to sign off the configured design.

The ARM product deliverables include reference scripts and information about how you use them to implement your design.

The IG is a confidential book that is only available to licensees.

### **Integration Manual**

The *Integration Manual* (IM) describes how to integrate the GIC-500 into a SoC. It includes a description of the signals that the integrator must tie off to configure the macrocell for the required integration. Some of the integration is affected by the configuration options you use when you implement the GIC-500.

The IM is a confidential book that is only available to licensees.

## 1.8 Product revisions

This section describes the differences in functionality between the product revisions:

r0p0 First release.

## Chapter 2 Functional Description

This chapter describes the functionality of the GIC-500. It contains the following sections:

- *About the functions* on page 2-2.

- *Interfaces* on page 2-3.

- *Operation* on page 2-7.

- *Clocking and resets* on page 2-14.

- Constraints and limitations on page 2-15.

### 2.1 About the functions

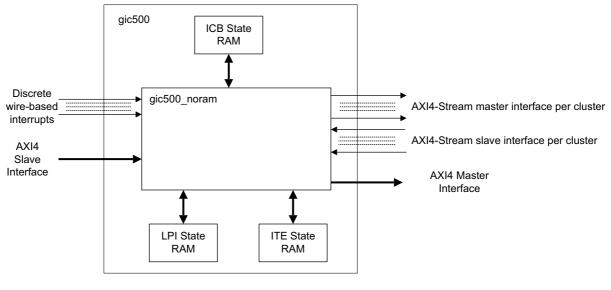

Figure 2-1 shows the top-level functional block diagram with interfaces:

- The interfaces that the GIC-500 provides are described in *Interfaces* on page 2-3.

- The *Interrupt Control Block* (ICB) State RAM holds the settings for SPIs, PPIs, and SGIs. It exists in all configurations of the GIC-500. See *Interrupt types* on page 2-7 for a description of the interrupt types.

- The LPI State RAM and ITE State RAM cache settings for the LPIs and ITS. They only exist in configurations where the ITS exists and LPIs are supported. See *Configurable options* on page 1-9.

- Note

The names of the top-level and noram blocks in a real design contain the names of the chosen configurations. The inputs and outputs are described in *Interfaces* on page 2-3.

### 2.2 Interfaces

The GIC-500 interfaces are:

- AXI4 Slave Interface.

- AXI4 Master Interface on page 2-4.

- *RAM Interfaces* on page 2-5.

- *Physical interrupt signals* on page 2-5.

- GIC-500 Stream Protocol Interface on page 2-6.

- Other core signals on page 2-6.

### 2.2.1 AXI4 Slave Interface

One 32-bit AMBA AXI4 slave interface provides access to the programming interfaces of all parts of the GIC-500:

- Distributor.

- Redistributors.

- ITS.

The slave interface also handles all message-based interrupts, which are interrupts generated by writes to the AXI4 slave interface. Message-based interrupts can generate SPIs or LPIs, depending on the register that you write to. See *Interrupt types* on page 2-7 for information about the different types of interrupts.

The slave interface uses a single contiguous address region for all registers. See Chapter 3 *Programmers Model* for the address map.

Accesses to some registers requires sideband information. When using backwards compatibility mode, some registers are banked to provide a separate copy for each core. The system integrator must drive **awuser\_s[2:0]** and **aruser\_s[2:0]** with the binary number of the core performing the access for writes and reads, respectively.

—— Note ———

This information is only required for the first eight cores, because only this number of cores is supported in backwards compatibility mode. See *Backwards compatibility* on page 2-10 for more information.

To generate an LPI a peripheral must write to the GITS\_TRANSLATER. For the ITS to know which translations to apply to the generated interrupts, it must know which peripheral performed the write. The ID of the peripheral is known as its Device ID. ARM recommends that for a *PCI Express* (PCIe) peripheral, its GIC Device ID is its PCIe Requester ID without any modification. The AXI4 slave only requires the Device ID for writes to the GITS\_TRANSLATER. For writes to that register, the GIC-500 supports two ways of receiving the Device ID:

- If **awuser\_s[3]** is LOW, then for any writes made to the GITS\_TRANSLATER the Device ID bits are taken from **awuser\_s[23:4]**.

- If awuser\_s[3] is HIGH, the slave port uses a mode of operation which reduces the number of AWUSER bits required by the system. In this mode, the GIC-500 assumes all write accesses are to the GITS\_TRANSLATER and the Device ID bits are taken from awaddr\_s[21:2].

Table 2-1 shows the AXI slave attributes and their values.

### Table 2-1 AXI slave interface attributes

| Attribute                      | Value |

|--------------------------------|-------|

| Combined acceptance capability | 6     |

| Read acceptance capability     | 3     |

| Read data reorder depth        | 1     |

| Write acceptance capability    | 3     |

### 2.2.2 AXI4 Master Interface

The GIC-500 uses the AXI4 master interface to access main memory. One 64-bit AMBA AXI4 master port is provided to allow the ITS and Redistributors to access main memory. The main memory holds the following:

- The translation tables for the ITS.

- The ITS command queue, which software writes to, that in turn programs the ITS.

- The LPI configuration table, which holds the priorities and enable bits for LPIs.

- The LPI pending tables, which can hold information on whether each LPI is pending on each core.

— Note ——

The AXI master interface is not present if the ITS and LPI support are removed.

The hypervisor or OS software is responsible for allocating memory to the GIC-500. The GIC architecture also requires you to write software that zeros the allocated memory before use. Software must program registers in the ITS and Redistributors with the physical addresses of the allocated memory. Therefore the AXI4 master makes accesses using physical addresses and therefore does not require address translation such as a System *Memory Management Unit* (MMU).

When software has enabled the relevant functionality in the GIC-500, the software must not access the allocated memory again unless allowed by the GIC architecture. For example, memory programmed in the GITS\_BASER must not be accessed when the ITS is enabled. However, the GIC architecture always permits software to write to the LPI configuration table pointed to by GICR\_PROPBASER, and defines the INV and INVALL ITS commands that make the GIC use the new property values.

The GIC-500 does not support shareability, but does have programmable cacheability settings. Therefore the GIC-500 always treats memory as non-shareable. Software must discover this by attempting to write to the shareability and cacheability fields that are present in registers such as GICR\_PROPBASER and by reading back the written values. The attributes in the MMU translation tables of the core must match those programmed in the GIC.

Consequently, software must issue the appropriate cache maintenance instructions when it wants to ensure that writes made by the core are visible to the GIC and when it wants to ensure that writes made by the GIC are visible to the core.

It is a system integration requirement that accesses that the GIC-500 makes to memory can complete without depending on any other accesses in the system making progress.

The AXI4 master interface only makes certain types of accesses. All transactions are 32 bytes or smaller, consisting of up to four transfers with up to eight bytes in each transfer. Only incrementing bursts are used. Accesses made by the AXI4 master involve the ITS and LPIs, which are always Non-secure. Therefore the AXI4 master always makes Non-secure accesses.

If the AXI4 master receives a bus error, such as SLVERR or DECERR, this is signaled through an external pin, **axim\_err**. When this occurs, the GIC-500 might lose interrupts and cannot recover and you must reset the GIC-500. If it is not reset, the behavior becomes UNPREDICTABLE.

Table 2-2 shows the AXI master attributes and their values.

### Table 2-2 AXI master interface attributes

| Attribute                   | Value |

|-----------------------------|-------|

| Combined issuing capability | 26    |

| Read issuing capability     | 11    |

| Write issuing capability    | 15    |

### 2.2.3 RAM Interfaces

The GIC-500 uses SRAMs to cache state, so that it can save area, power, and latency.

In typical operation, their existence is transparent to software, with a few exceptions:

- After reset, the RAMs are automatically initialized. Accesses made to the GIC-500 during this time could take longer than normal.

- The RAMs are protected from errors using an *Error-Correction Code* (ECC) with single error correction and double error detection (SECDED). If a double error is detected then this is signaled through an external pin, **ecc\_fatal**. When this occurs, the GIC-500 might lose interrupts and cannot recover and must be reset. If it is not reset, behavior becomes UNPREDICTABLE. The GIC-500 returns corrupted data if a double error is detected during a read to any of the following:

- GICD\_IPRIORITYRn.

- GICR\_IPRIORITYRn.

- GICD\_IROUTERn.

- GICD\_ITARGETSRn.

If you want to guarantee that software does not read corrupted data after a double error, software must never read from these registers and instead maintain its own copy of the values written to these registers.

### 2.2.4 Physical interrupt signals

The GIC-500 supports the generation of SPIs and PPIs through physical interrupt signals. These inputs can be programmed as either:

- Level-sensitive, where the interrupt is pending as long as the input is asserted.

- Edge-triggered, where a rising edge causes the interrupt to be set to pending.

There is one independent set of PPIs for each core. SPIs are global and therefore there is only a single set. See *Interrupt types* on page 2-7 for more information.

—— Note ——

- In the GIC-500, level-sensitive PPIs are active-LOW, whereas level-sensitive SPIs are active-HIGH.

- The GIC-500 does not synchronize interrupt inputs. They must be synchronized to the GIC-500 clock externally.

### 2.2.5 GIC-500 Stream Protocol Interface

For each cluster or group of cores, one upstream and one downstream 16-bit AMBA AXI4-Stream interface is provided.

The GIC-500 GIC Stream Protocol Interface consists of a pair of AXI4-Stream interfaces that the GIC-500 uses to send interrupts to the core and receive notifications when the core activates interrupts. There is a pair of physical interfaces, one in each direction, for each cluster.

The GIC Stream interfaces use the prefix **icd** to indicate the master interface, and **icc** to indicate the slave interface. The GIC Stream master interface uses the **icdtdest** signal to direct packets to one core within the cluster. The GIC Stream slave interface uses the **icctid** signal to determine which core within the cluster sent a packet.

### 2.2.6 Other core signals

When a core is powered down, it must first disable the sending of packets over the AXI4-Stream interface using the GICR\_WAKER.ProcessorSleep bit. When this has been done, the presence of an interrupt specifically targeted at that core causes the **wake\_request** signal for that core to be asserted. ARM recommends that you connect this signal to the power controller to cause that core to boot. When the core has booted, software is always expected to re-enable communication over the interface through the use GICR\_WAKER.ProcessorSleep, allowing the interrupt to be processed.

The GIC-500 uses the **cpu\_active** signal to decide which cores are preferred for SPIs that target multiple cores. It does not affect the operation of any other type of interrupt. It also has no effect if GICR\_WAKER.ProcessorSleep is set to one for that core, because those SPIs are never sent to cores with ProcessorSleep set to one. ARM recommends that this signal is deasserted when a core is in certain software-transparent sleep states entered during WFI or WFE instructions, such as retention, so that the core is less likely to handle SPIs that target multiple cores. This can increase the amount of time that cores spend in these sleep states. If you use the **cpu\_active** signal this way, software must not rely on SPIs that target multiple cores causing cores to leave WFI or WFE. Instead, software must use another mechanism to ensure this, such as an SGI, or an SPI targeted at only the core in question.

### 2.3 Operation

The GIC-500 is divided into three main sections:

**ITS** The ITS is responsible for translating message-based interrupts from peripherals into LPIs. You can also use the ITS to manage existing LPIs. The ITS is not used for other types of interrupt.

**Distributor** The Distributor receives interrupts from the:

- Wire interrupts.

- Programming interface.

It is responsible for prioritizing these interrupts and sending them to the CPU interface using the GIC Stream Protocol Interface.

### Redistributor

There is one Redistributor for each core. Each Redistributor holds the state that is individual to a particular core, such as the settings for PPIs, and SGIs. It also stores the LPIs for that core after they have been generated using the ITS.

### 2.3.1 Interrupt types

This section describes the different types of interrupt that the GIC-500 handles.

### SGIs

SGIs are inter-processor interrupts, that is, interrupts generated from one core and sent to other cores. Activating an SGI on one core does not affect the same interrupt ID on another core. Therefore when an SGI is sent to all cores it is handled independently on each core. The settings for each SGI are also independent between cores.

You can generate SGIs using System registers in the generating core, or, in legacy software, by writing to the Software Generated Interrupt Register, GICD\_SGIR. There are 16 independent SGIs, ID0-ID15, that are recorded separately for every target core. In backwards compatibility mode, the number of the generating core is also recorded.

### PPIs

PPIs are typically used for peripherals that are tightly-coupled to a particular core. Interrupts connected to the PPI inputs associated with one core are only sent to that core. Activating a PPI on one core does not affect the same interrupt ID on another core. The settings for each PPI are also independent between cores.

A PPI is an interrupt that is specific to a single core and is generated by a wire input. PPI signals are active-LOW level-sensitive, by default, but can also be programmed to be triggered on a rising edge.

### SPIs

SPIs are typically used for peripherals that are not tightly-coupled to a specific core. You can program each SPI to target either a particular core or any core. Activating an SPI on one core activates the SPI for all cores. That is, the GIC-500 allows at most one core to activate an SPI. The settings for each SPIs are also shared between all cores.

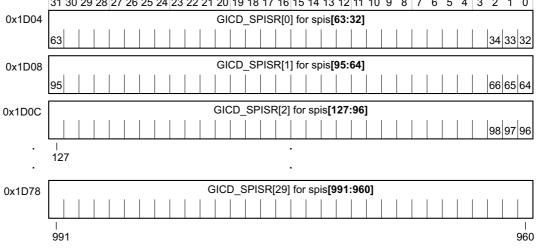

SPIs can be generated either by wire inputs or by writes to the AXI4 slave programming interface. The GIC-500 can support up to 960 SPIs corresponding to the external **spi[991:32]** signal. The number of SPIs available depends on the implemented configuration. The permitted values are 32-960, in steps of 32. The first SPI has an ID number of 32. You can configure whether each SPI is triggered on a rising edge or is active-HIGH level-sensitive.

— Note ———

All signals, including SPIs, must be synchronous to the clock. Therefore, you must synchronize any interrupt signals from an asynchronous source before they are connected to the GIC-500.

### LPIs

LPIs are typically used for peripherals that produce message-based interrupts. An LPI targets only one core at a given time. LPIs are generated when the peripheral writes to the ITS, which also holds the registers to control the generation and maintenance of LPIs. The ITS provides interrupt ID translation, allowing peripherals to be owned directly by a virtual machine if a System MMU is also present for those peripherals.

—— Note ———

The interrupt ID translation in the ITS only allows interrupts from these peripherals to be translated to the ID space of the hypervisor, not sent directly to the virtual machine.

In the GIC-500, you can only generate LPIs by writing to the ITS using the AXI4 slave programming interface. The GIC-500 always supports up to 57344 LPIs, but has a cache that holds the settings for the most frequent interrupts. The settings for the ITS and LPIs are stored in main memory, so a cache miss might result in up to three round trips to memory. The first LPI has an ID number of 8192.

You can debug problems with LPI interrupt generation in the ITS using the LPI tracking registers. These allow you to set a trigger to capture information about the next interrupt that the ITS processes. This allows you to determine what happened to that interrupt and what translation was applied. See *Implementation defined test registers in the GITS control page summary* on page 3-28 for more information.

For the most efficient caching of LPIs, ARM recommends that you allocate input interrupt IDs sequentially. You can measure the performance of the cache the input interrupt ID affects using the GITS\_TRKICR register. See *Debug ITE Cache Statistics* on page 3-32 for more information. The other LPI cache is only affected by the distribution of LPI physical IDs (PIDs). Therefore, if possible, ARM recommends that for best caching, PIDs are also sequentially allocated. The performance of that cache can be monitored using the GITS\_TRKLCR register. See *Debug LPI Cache Statistics* on page 3-33 for more information.

### **Choosing between LPIs and SPIs**

You can use both LPIs and SPIs for message-based interrupts. Your decision about whether to use an LPI or SPI for an interrupt can potentially be made by software, providing there are spare SPIs and the GIC-500 is integrated with ITS support. This can be achieved by either making the peripheral write to a different GIC-500 address, or by changing the address translation for the interrupt write in the System MMU. Changing only the System MMU is possible because the

two registers for Non-secure message-based interrupts, GICD\_SETSPI\_NSR and GITS\_TRANSLATER, are at the same address offset in different pages. The following factors can help you to decide which type of interrupts is most appropriate:

- Only the ITS provides interrupt ID translation and therefore LPIs are preferable for peripherals owned by a virtual machine. This is because the hypervisor can let the virtual machine program the peripheral directly, and let the ITS convert its interrupts from the IDs used by the virtual machine to unique physical IDs.

- LPIs are always Group 1 Non-secure, so message-based interrupts that target Secure software must use SPIs.

- Only SPIs provide the ability to target all cores, which means the GIC-500 attempts to automatically balance the interrupt load to cores that are active but not handling other interrupts.

- The GIC-500 can provide a far larger number of LPIs than SPIs for the same area. The marginal area increase for each additional LPI is much less than for an SPI because the LPI settings are only cached, not stored, in the GIC-500. This means that the lowest area can often be achieved by using LPIs where possible rather than SPIs.

- In a small system where the features of the ITS are not required and there are few message-based interrupts, you might decide not to include the ITS and LPI support.

- SPIs usually have a better worst-case interrupt latency than LPIs. This is because SPIs have all their settings stored internally to the GIC-500, whereas LPIs that are not cached require external memory accesses. The cache hit rate is expected to be higher for the LPIs that occur more frequently. Therefore ARM recommends that SPIs are used for any latency sensitive interrupts that are expected to occur infrequently.

### 2.3.2 Interrupt groups

The GIC-500 implements the following Interrupt Group Registers:

- GICD\_IGROUPRn.

- GICD\_IGRPMODRn.

- GICR\_IGROUPR0.

- GICR\_IGRPMODR0.

These control whether each interrupt is configured as:

- Group 0.

- Group 1 Secure.

- Group 1 Non-secure.

Each interrupt is programmed to belong to an interrupt group. Each interrupt group:

- Determines the target exception level and security state for interrupts in that group.

- Has separate enable bits that control whether interrupts in that group can be forwarded to the core.

- Has an impact on later routing decisions in the CPU interfaces.

When using backwards compatibility mode or with security disabled, the meaning and number of interrupt groups are affected. See the *ARM*<sup>®</sup> *Generic Interrupt Controller Architecture Specification version 3.0* for more information.

### 2.3.3 Interrupt triggering

The GIC-500 supports two types of physical interrupt signal:

### Level-sensitive

The interrupt is pending while the interrupt input is asserted.

### **Edge-triggered**

A rising-edge on the interrupt input causes the interrupt to become pending. The pending bit is later cleared when the interrupt is activated by the CPU interface.

You must program GICD\_ICFGRn and, for PPIs using ARE = 1, GICR\_ICFGR1, to have the correct settings for the system.

### 2.3.4 Backwards compatibility

You can configure the Distributor part of the GIC-500 at build time to support limited backwards compatibility with GICv2. If this support is configured, the Distributor resets to backwards compatibility mode. This mode supports up to eight cores. The eight cores supported by the GIC-500 are the cores with the lowest affinity numbers.

The ARE setting in GICD\_CTLR, which disables backwards compatibility, is programmable when backwards compatibility support is configured. The ARE setting is also banked by security. This allows Secure software to operate in backwards compatibility mode (ARE\_S = 0) while Non-secure software enables ARE. If Secure software is not operating in backwards compatibility mode then Non-secure software cannot operate in backwards compatibility mode.

### — Note —

A major limitation of operating with Non-secure using  $ARE_NS = 1$  and Secure using  $ARE_S = 0$  is that legacy Secure software is not able to control Non-secure interrupts. This means that existing Secure Monitor code that relies on having this control cannot run correctly using this mode of backwards compatibility. See the  $ARM^{\text{(*)}}$  Generic Interrupt Controller Architecture Specification version 3.0 for more information on this limitation.

The GIC-500 can expose software to more race conditions than previous GIC implementations. Legacy code that relies on the stronger guarantees provided in these previous GICs might not work reliably. For example, some GIC implementations ensure that a sequence of accesses to both the CPU interface and Distributor is executed in program order. However, the ordering between the Distributor and CPU interface is not architecturally guaranteed and is not guaranteed in systems with the GIC-500.

In backwards compatibility mode, the GIC-500 ensures that the effects of all interrupt programming are eventually observable, so you only have to update software that relies on the reprogramming being observable by a specific point. Software typically only requires these ordering guarantees during operations such as retargeting SPIs, if it must be ensured that the previous target does not receive the SPI, or saving the state of a Distributor.

If your software relies on these guarantees, you must update your software using the following guidance:

• To ensure that accesses to the CPU interface have completed and any side-effects have been observed by the Distributor, software must execute a DSB instruction. Use this to ensure the status of interrupts reported by the Distributor is up-to-date. Software that is not using backwards compatibility mode must also use the same approach.

To know that updates to the Distributor have completed and have been observed by the CPU interface, you must wait until the GIC-500-specific GICD\_ESTATUSR.SRWP bit reads as zero. Use this to ensure that after reprogramming an interrupt, cores cannot receive interrupts based on the old interrupt programming. Software not using backwards compatibility mode must instead disable interrupts and poll the GICD\_CTLR.RWP bit to ensure that old settings are no longer visible to cores. The advantage of the SRWP bit is that it provides this guarantee even if this sequence is not followed.

The GIC-500 might also implement different IMPLEMENTATION DEFINED choices than previous implementations. For example, the GIC-400 did not set an interrupt pending if the interrupt group for that interrupt was disabled in the GICD\_CTLR. In contrast, the GIC-500 does set interrupts pending in this scenario.

It is expected that legacy power management code is not compatible and has to be updated for operation with the GIC-500. For example, GICR\_WAKER.ProcessorSleep must be set to zero after reset to enable interrupts to be sent to a core. Likewise, the powerdown sequence requires writing to GICR\_WAKER. The GICR\_WAKER register is new in version three of the GIC architecture and therefore you must update legacy code to use it.

### 2.3.5 Disable Security

The *Disable Security* (DS) bit removes the security support of the Distributor. It can be set by Secure software during the boot sequence or be configured to be always set when you configure the design. This configuration option must be used when the system does not have the concept of security to allow access to important registers. If you run software without security awareness on a system that supports security, then the Secure boot code can set DS before switching to a Non-secure exception level to run the software. This enables you to program the GIC-500 from any exception level and use two interrupt groups, Group 0 and Group 1. This means that interrupts can target both the FIQ and IRQ handlers on a core.

You must take care when deciding to write security-unaware software using Group 0, as it might not be portable to systems with a concept of security. This is because Group 0 is always Secure in systems with security. It is most portable for security-unaware software to always use Group 1.

If a system has a concept of security but one or more cores do not, then you must not set DS. Instead each core is only able to enable the interrupt groups corresponding to the security states that it supports.

### 2.3.6 Power management

The GIC-500 supports the power down of cores and can itself be powered down. The GICR\_WAKER registers provide bits to control functions associated with power management. The architecture recommends how these bits can be used. Some bits within the GICR\_WAKER are global, rather than separate, for each Redistributor, as GIC-500 is a monolithic implementation. This means that the components are not distinct, but are instead tightly integrated. The GIC architecture allows such implementations to behave differently. See the *ARM*<sup>®</sup> *Generic Interrupt Controller Architecture Specification version 3.0* for more information.

The GIC architecture defines the programming sequence to safely power down a core that is attached to a Distributor. This involves using the GICR\_WAKER.ProcessorSleep bit. When all cores within a cluster have been powered down using the architectural sequence, you can power gate the AXI4-Stream interface for that cluster.

When powering down the GIC-500, with the exception of the LPI pending bits, software must preserve the state of the GIC-500. The state must be copied after the GIC-500 core power down sequence has completed to ensure that the pending information that is preserved is up to date.

You can preserve the LPI pending bits using the architectural Redistributor powerdown sequence, which ensures the memory pointed to by each GICR\_PENDBASER contains the updated pending information for the LPIs. This involves using the GICR\_WAKER.Sleep bit. When the GIC-500 is powered up again, you can program the GICR\_PENDBASER registers to point to the same memory to reload the LPI pending status. If there is no requirement to reload the pending LPIs, ARM recommends that you zero the pending table and set the GICR\_PENDBASER.PTZ bit to one to speed up the initialization of the GIC-500.

—— Note ———

- GICR\_WAKER.Sleep can only be set to one when:

- All RD0s have GICR\_WAKER.ProcessorSleep == 1.

- All RD0s have GICR\_WAKER.ChildrenAsleep == 1.

- GICR\_WAKER.ProcessorSleep can only be set to zero when:

- $GICR_WAKER.Sleep == 0.$

- GICR\_WAKER.Quiescent == 0.

Before a core is powered down, you must set GICR\_WAKER.ProcessorSleep to one and wait until GICR\_WAKER.ChildrenAsleep is one to ensure there are no outstanding transactions on the AXI4-Stream interface of the core. In the typical powerdown sequence, to ensure that there are no interrupts during the powerdown of the core, you must:

- 1. Mask interrupts on the core.

- 2. Clear the CPU interface enables.

- 3. Set the interrupt bypass disable on the CPU interface.

When a core has been powered down and the GICR\_WAKER.ProcessorSleep bit is set to one, the GIC-500 attempts to wake the core if it receives an interrupt that targets only that core. It does this by asserting the **wake\_request** signal corresponding to that core. This signal connects to the power controller. See *Other core signals* on page 2-6 for more information about the **wake\_request** signals.

You must not set GICR\_WAKER.ProcessorSleep to one unless the core is entering a power state where the GIC-500 must use the power controller to wake the core rather than using the AXI4-Stream interface. For example, with Cortex-A53 and Cortex-A57, if the core is entering a sleep state based on the WFI or WFE instructions, such as retention, you must not set GICR\_WAKER.ProcessorSleep to one. The core can enter these sleep states without software assistance. Given GICR\_WAKER.ProcessorSleep is zero, the GIC-500 sends interrupts using the AXI4-Stream interface as normal. These interrupts can cause the core to leave the WFI or WFE instruction based on the standard rules in the *ARM® Architecture Reference Manual, ARMv8, for ARMv8-A architectural profile*. The system integrator can use the **cpu\_active** signal to ensure that interrupts that can target multiple cores are much less likely to target cores in certain sleep states. In such a system, the software has more control over when cores leave sleep states.

— Note — —

Interrupts that target only one core are unaffected by **cpu\_active** and are always sent to that core. Moreover, if the GICR\_WAKER.ProcessorSleep for that core is set, the **wake\_request** signal is asserted for that core. See *Other core signals* on page 2-6 for more information about the **cpu\_active** signals.

See the *ARM*<sup>®</sup> *Generic Interrupt Controller Architecture Specification version 3.0* for information about power management, and about wakeup signals and their relation to the core outputs.

## 2.4 Clocking and resets

All configurations of the GIC-500 use a single clock input, **clk**, and a single reset input, **resetn**. See *Clock and reset signals* on page A-2.

— Note —

Clock and reset signals apply to all interfaces on the GIC-500 and all interfaces must be synchronous to this clock. Therefore, synchronizer cells might be required for certain inputs.

## 2.5 Constraints and limitations

ARM recommends that when ARE = 1 you avoid generating or disabling SPI interrupts that target multiple cores at times when no core is able to handle them. That is, disable or avoid generating such interrupts while all targeted CPU interfaces are either powered down or do not have the interrupt group enabled. This is because interrupts that are generated in these circumstances might cause higher power consumption inside GIC-500. The GIC architecture specifies that such interrupts do not cause a **wake\_request** to become asserted so, in the absence of other stimulus, this state of higher power consumption persists.

# Chapter 3 Programmers Model

This chapter describes the GIC-500 registers and provides information about programming the device. It contains the following sections:

- *About the GIC-500 programmers model* on page 3-2.

- The GIC-500 register map on page 3-3.

- *Distributor register summary* on page 3-6.

- *Distributor register descriptions* on page 3-9.

- Distributor registers for message-based SPIs summary on page 3-11.

- *Redistributor registers for control and physical LPIs summary* on page 3-12.

- *Redistributor register descriptions* on page 3-14.

- Redistributor registers for SGIs and PPIs summary on page 3-15.

- *ITS control register summary* on page 3-17.

- *ITS control register descriptions* on page 3-19.

- *ITS translation register summary* on page 3-21.

- Implementation defined test registers in GICD page summary on page 3-22.

- Implementation defined test registers in the GICR page for PPIs and SGIs on page 3-25.

- Implementation defined test registers in the GITS control page summary on page 3-28.

# 3.1 About the GIC-500 programmers model

The following sections describe the GIC-500 registers:

- Distributor register summary on page 3-6.

- Distributor registers for message-based SPIs summary on page 3-11.

- *Redistributor registers for control and physical LPIs summary* on page 3-12.

- Redistributor registers for SGIs and PPIs summary on page 3-15.

- *ITS control register summary* on page 3-17.

- *ITS translation register summary* on page 3-21.

- Implementation defined test registers in GICD page summary on page 3-22.

- Implementation defined test registers in the GICR page for PPIs and SGIs on page 3-25.

- Implementation defined test registers in the GITS control page summary on page 3-28.

The following information applies to the GIC-500 registers:

- The GIC-500 implements only memory-mapped registers.

- The GIC-500 has a single base address. This address is not fixed and can be different for each particular system implementation.

The offset of each register from the base address is fixed.

- Accesses to reserved or unused address locations do not result in a bus error. Reads to these locations return zero and writes are ignored.

- Unless otherwise stated in the accompanying text:

- Do not modify reserved register bits.

- Ignore reserved register bits on reads.

- A system reset or a powerup reset resets all register bits to 0.

- The width of the GIC-500 AXI4 slave port is 32 bits. The *ARM*<sup>®</sup> *Generic Interrupt Controller Architecture Specification version 3.0* defines the permitted sizes of access.

When byte access is permitted, halfword access is also permitted. When word access is permitted, doubleword access is also permitted.

Byte or halfword accesses to registers that do not permit those access sizes are not successful and return a SLVERR response.

—— Note ——

The GIC-500 does not guarantee single-copy atomicity for doubleword accesses, although this is guaranteed for each word in the doubleword. However, none of the GIC-500 registers require atomic doubleword accesses for correct operation.

- The GIC-500 only supports data in little-endian format.

- The access types for the GIC-500 are as follows:

- **RO** Read only.

- **RW** Read and write.

- **WO** Write only. Reads return an UNKNOWN value.

# 3.2 The GIC-500 register map

All of the GIC-500 registers have names that provide a short mnemonic for the function of the register. In these names:

- The first letters indicate the logical block that the register belongs to:

- GICD indicates a Distributor register.

- GICR indicates a Redistributor register.

- GITS indicates an Interrupt Translation Service register.

- The remaining letters are a mnemonic for the register, for example the GIC Distributor Control Register is called GICD\_CTLR.

All pages are 64KB in size to allow for best compatibility with ARMv8. The address map within all pages is defined by the architecture specification. See the *ARM*<sup>®</sup> *Generic Interrupt Controller Architecture Specification version 3.0.*

The number of bits of address used by the GIC-500 address map is:

18 + max(1, ceil(log<sub>2</sub> (total\_number\_of\_cpus)))

#### \_\_\_\_ Note \_\_\_\_\_

The write address bus might be larger than the result of this equation in certain cases. In these cases the *most significant bit* (MSB) referred to here might not be the MSB of the write address bus. See *Effect of Device ID multiplexing* on page 3-4 for more information.

The top bit of the address selects between two sets of pages. When the MSB is LOW, the set of pages is as shown in Table 3-1:

| Address[MSB] | Address[MSB-1:16] | Page description                                                                                                                          | Address range   |

|--------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 0            | 0                 | Distributor registers (GICD_*)<br>See <i>Distributor register summary</i> on page 3-6.                                                    | 0x00000-0x0FFFF |

|              | 1                 | Distributor registers for message-based SPIs (GICD_*)<br>See <i>Distributor registers for message-based SPIs summary</i> on<br>page 3-11. | 0x10000-0x1FFFF |

|              | 2                 | Interrupt Translation Service control registers (GITS_*)<br>See <i>ITS control register summary</i> on page 3-17.                         | 0x20000-0x2FFFF |

|              | 3                 | Interrupt Translation Service register (GITS_TRANSLATER)<br>See <i>ITS translation register summary</i> on page 3-21.                     | 0x30000-0x3FFFF |

|              | Otherwise         | Reserved                                                                                                                                  |                 |

#### Table 3-1 Lower half of address map

When the MSB is HIGH as shown in Table 3-2, the set of pages contains the Redistributor pages in sequence. For example, the RDs that correspond to each core in the first cluster precede the RDs that correspond to each core in the second cluster.

| Address[MSB] | Address[MSB-1:17]                                                                                                                     | Address[16] | Page description                                                                                                                                                      |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | Global core number.<br>This is a core number using the contiguous,<br>linear representation as depicted in<br>Figure 1-2 on page 1-4. | 0           | Redistributor registers for control and<br>physical LPIs (GICR_*).<br>See <i>Redistributor registers for control and</i><br><i>physical LPIs summary</i> on page 3-12 |

|              |                                                                                                                                       | 1           | Redistributor registers for SGIs and PPIs (GICR_*).<br>See <i>Redistributor registers for SGIs and PPIs summary</i> on page 3-15.                                     |

|              | Values that do not correspond to a core number.                                                                                       | Х           | Reserved.                                                                                                                                                             |

#### Table 3-2 Upper half of address map

For example, if there are four clusters, each with four cores, then there are 18 + max(1, 4) = 22 address bits, and the RD control registers for cluster 1, core 0 are at an offset 0x280000-0x28FFFF, with those for SGIs and PPIs at an offset of 0x29000-0x29FFFF.

# 3.2.1 Discovery

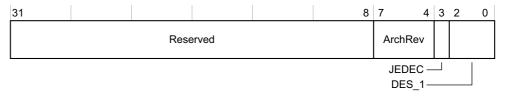

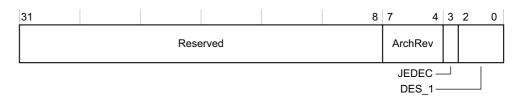

ARM recommends that the system provides the operating system with three pointers to the start of the first Distributor, ITS and Redistributor pages, respectively. These three pages can be checked against the discovery registers that start at offset 0xFFD0 for all of these pages to verify they are pages of GIC registers. These registers allow discovery of whether the architecture version and, for GIC-500, whether the page contains the Distributor, ITS, or Redistributor registers. When this is known, additional information can be obtained from registers specific to each page.

For Redistributors, ARM recommends that GICR TYPER is examined to determine:

- Whether the implementation has two or four pages per Redistributor, based on the features implemented. It can be inferred that GIC-500 has only two pages for each Redistributor because the feature bits in that register indicate that it does not support virtual LPIs.

- Whether it is the last Redistributor in the series of pages.

- Which core it is the Redistributor for, based on affinity values.

This information allows you to iteratively search through all Redistributors, discovering all of them in a generic manner.

The GITS\_TYPER register in the GIC-500 indicates that you must program the ITS with linear processor numbers, rather than physical target addresses. The GICR\_TYPER contains the linear processor number that you must use to reference a Redistributor when programming the ITS.

Legacy code can still discover the identifier that the GIC-500 uses to reference the current core by reading from the GICD\_ITARGETSR0.

## 3.2.2 Effect of Device ID multiplexing

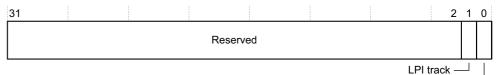

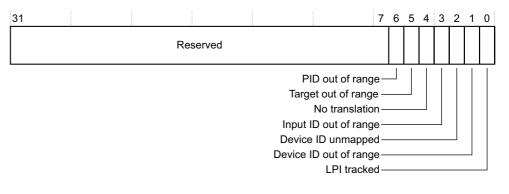

GIC-500 supports transporting the Device ID over **awaddr\_s** for GITS\_TRANSLATER writes, which reduces the size of **awuser\_s** in the system. See *AXI4 Slave Interface* on page 2-3. This is invisible to software and is a system integration decision.