# ARM<sup>®</sup> CoreLink<sup>®</sup> NIC-400 Network Interconnect

Revision: r0p3

**Technical Reference Manual**

## ARM CoreLink NIC-400 Network Interconnect Technical Reference Manual

Copyright © 2012-2014 ARM. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

|                   |       |                  | Change history          |

|-------------------|-------|------------------|-------------------------|

| Date              | Issue | Confidentiality  | Change                  |

| 07 August 2012    | А     | Non-Confidential | First release for r0p0  |

| 13 May 2013       | В     | Non-Confidential | First release for r0p1  |

| 09 December 2013  | С     | Non-Confidential | First release for r0p2  |

| 07 March 2014     | D     | Non-Confidential | First release for r0p3  |

| 30 September 2014 | Е     | Non-Confidential | Second release for r0p3 |

#### **Proprietary Notice**

Words and logos marked with \* or m are registered trademarks or trademarks of ARM\* in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

## Contents ARM CoreLink NIC-400 Network Interconnect Technical Reference Manual

|            | Prefa | ace                                             |     |

|------------|-------|-------------------------------------------------|-----|

|            |       | About this book                                 | vi  |

|            |       | Feedback                                        | ix  |

| Chapter 1  | Intro | oduction                                        |     |

| •          | 1.1   | About the CoreLink NIC-400 Network Interconnect | 1-2 |

|            | 1.2   | Key features                                    | 1-3 |

|            | 1.3   | Relationship between NIC-400 and AMBA Designer  |     |

|            | 1.4   | Product revisions                               |     |

| Chapter 2  | Fund  | ctional Description                             |     |

| •          | 2.1   | About the functions                             | 2-2 |

|            | 2.2   | Interfaces                                      |     |

|            | 2.3   | Operation                                       |     |

|            | 2.4   | Optional features                               |     |

| Chapter 3  | Prog  | grammers Model                                  |     |

| •          | 3.1   | About the programmers model                     | 3-2 |

|            | 3.2   | Configuration programmers model                 |     |

| Appendix A | Sign  | al Descriptions                                 |     |

| ••         | A.1   | Global signals                                  | A-2 |

|            | A.2   | Signal direction                                |     |

|            | A.3   | AXI3 and AXI4 signals                           |     |

|            | A.4   | APB signals                                     |     |

|            | A.5   | AHB-Lite signals                                |     |

|            |       | -                                               |     |

| A.6 | QVN signals A-14 |

|-----|------------------|

|     |                  |

Appendix B Revisions

## Preface

This preface introduces the *ARM*<sup>®</sup> *CoreLink*<sup>™</sup> *NIC-400 Network Interconnect Technical Reference Manual*. It contains the following sections:

- *About this book* on page vi.

- *Feedback* on page ix.

## About this book

This book is for the CoreLink NIC-400 Network Interconnect (NIC-400).

| Product revision status |                                                                                                                                                                                                                                                                                                        |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | The <i>rnpn</i> identifier indicates the revision status of the product described in this book, where: <b>rn</b> Identifies the major revision of the product. <b>pn</b> Identifies the minor revision or modification status of the product.                                                          |

| Intended audience       |                                                                                                                                                                                                                                                                                                        |

|                         | This book is written for system designers, system integrators, and programmers who are designing or programming a <i>System-on-Chip</i> (SoC) that uses the AMBA Network Interconnect.                                                                                                                 |

| Using this book         |                                                                                                                                                                                                                                                                                                        |

|                         | This book is organized into the following chapters:                                                                                                                                                                                                                                                    |

|                         | Chapter 1 Introduction                                                                                                                                                                                                                                                                                 |

|                         | Read this for an introduction to the NIC-400 and a description of its features.                                                                                                                                                                                                                        |

|                         | Chapter 2 Functional Description                                                                                                                                                                                                                                                                       |

|                         | Read this for a description of the functionality of the NIC-400.                                                                                                                                                                                                                                       |

|                         | Chapter 3 Programmers Model                                                                                                                                                                                                                                                                            |

|                         | Read this for a description of the address map and registers of the NIC-400.                                                                                                                                                                                                                           |

|                         | Appendix A Signal Descriptions                                                                                                                                                                                                                                                                         |

|                         | Read this for a description of the signals used by the NIC-400.                                                                                                                                                                                                                                        |

|                         | Appendix B Revisions                                                                                                                                                                                                                                                                                   |

|                         | Read this for a description of the technical changes between released issues of this book.                                                                                                                                                                                                             |

| Glossary                |                                                                                                                                                                                                                                                                                                        |

|                         | The <i>ARM</i> <sup>®</sup> <i>Glossary</i> is a list of terms used in ARM documentation, together with definitions for those terms. The <i>ARM</i> <sup>®</sup> <i>Glossary</i> does not contain terms that are industry standard unless the ARM meaning differs from the generally accepted meaning. |

|                         | See ARM® Glossary, http://infocenter.arm.com/help/topic/com.arm.doc.aeg0014-/index.html.                                                                                                                                                                                                               |

| Conventions             |                                                                                                                                                                                                                                                                                                        |

|                         | Conventions that this book can use are described in:                                                                                                                                                                                                                                                   |

|                         | <ul> <li><i>Typographical conventions</i> on page vii.</li> <li><i>Signals</i> on page vii.</li> </ul>                                                                                                                                                                                                 |

|                         |                                                                                                                                                                                                                                                                                                        |

#### **Typographical conventions**

The following table describes the typographical conventions:

#### Typographical conventions

| Style             | Purpose                                                                                                                                                                                                                              |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| italic            | Introduces special terminology, denotes cross-references, and citations.                                                                                                                                                             |

| bold              | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.                                                                                                |

| monospace         | Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.                                                                                                                          |

| <u>mono</u> space | Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.                                                                                              |

| monospace italic  | Denotes arguments to monospace text where the argument is to be replaced by a specific value.                                                                                                                                        |

| monospace bold    | Denotes language keywords when used outside example code.                                                                                                                                                                            |

| <and></and>       | Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example: MRC p15, 0 <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd>                                                      |

| SMALL CAPITALS    | Used in body text for a few terms that have specific technical meanings, that are defined in the <i>ARM</i> <sup>®</sup> <i>Glossary</i> . For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE. |

#### Signals

The signal conventions are:

| Signal level | The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means: |

|--------------|-------------------------------------------------------------------------------------------------------------|

|              | <ul><li>HIGH for active-HIGH signals.</li><li>LOW for active-LOW signals.</li></ul>                         |

| Lower-case n | At the start or end of a signal name denotes an active-LOW signal.                                          |

#### Additional reading

This section lists publications by ARM and by third parties.

See Infocenter, http://infocenter.arm.com, for access to ARM documentation.

#### **ARM** publications

This book contains information that is specific to this product. See the following documents for other relevant information:

*ARM*<sup>®</sup> CoreLink<sup>™</sup> QoS-400 Network Interconnect Advanced Quality of Service, Supplement to ARM<sup>®</sup> CoreLink<sup>™</sup> NIC-400 Network Interconnect Technical Reference Manual (ARM DSU 0026).

—— Note ——

This product is separately licensed and not included in the NIC-400 base product.

ARM<sup>®</sup> CoreLink<sup>™</sup> QVN-400 Network Interconnect Advanced Quality of Service using Virtual Networks, Supplement to ARM<sup>®</sup> CoreLink<sup>™</sup> NIC-400 Network Interconnect Technical Reference Manual (ARM DSU 0027).

—— Note ———

This product is separately licensed and not included in the NIC-400 base product.

- ARM<sup>®</sup> CoreLink<sup>™</sup> TLX-400 Network Interconnect Thin Links, Supplement to ARM<sup>®</sup> CoreLink<sup>™</sup> NIC-400 Network Interconnect Technical Reference Manual (ARM DSU 028).

- —— Note ———

This product is separately licensed and not included in the NIC-400 base product.

- ARM<sup>®</sup> CoreLink<sup>™</sup> TZC-400 TrustZone<sup>®</sup> Address Space Controller Technical Reference Manual.

- ARM<sup>®</sup> AMBA<sup>®</sup> Designer ADR-400 User Guide (ARM DUI 0333).

- ARM<sup>®</sup> AMBA<sup>®</sup> 4 AXI4, AXI4-Lite, and AXI4-Stream Protocol Assertions User Guide (ARM DUI 0534).

- ARM<sup>®</sup> AMBA<sup>®</sup> Specification (ARM IHI 0011).

- ARM<sup>®</sup> AMBA<sup>®</sup> AXI and ACE Protocol Specification, AXI3, AXI4, AXI4-Lite, ACE and ACE-Lite (ARM IHI 0022).

- ARM<sup>®</sup> AMBA<sup>®</sup> APB Protocol Specification (ARM IHI 0024).

- ARM<sup>®</sup> AMBA<sup>®</sup> 3 AHB-Lite Protocol Specification (ARM IHI 0033).

- ARM<sup>®</sup> AMBA<sup>®</sup> 4 AXI4-Stream Protocol Specification (ARM IHI 0051).

The following confidential books are only available to licensees:

- ARM<sup>®</sup> CoreLink<sup>™</sup> NIC-400 Network Interconnect Integration Manual (ARM DII 0269).

- ARM<sup>®</sup> CoreLink<sup>™</sup> NIC-400 Network Interconnect Implementation Guide (ARM DII 0273).

- ARM<sup>®</sup> CoreLink<sup>™</sup> NIC-400 Network Interconnect Supplement to ARM<sup>®</sup> CoreLink<sup>™</sup> ADR-400 AMBA<sup>®</sup> Designer User Guide (ARM DSU 0018).

- ARM<sup>®</sup> CoreLink<sup>™</sup> QVN Protocol Specification (ARM IHI 0063).

## Feedback

ARM welcomes feedback on this product and its documentation.

#### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

#### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- The title.

- The number, ARM DDI 0475E.

- The page numbers to which your comments apply.

- A concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

#### — Note —

ARM tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader.

## Chapter 1 Introduction

This chapter introduces the CoreLink NIC-400 Network Interconnect. It contains the following sections:

- *About the CoreLink NIC-400 Network Interconnect* on page 1-2.

- *Key features* on page 1-3.

- *Relationship between NIC-400 and AMBA Designer* on page 1-5.

- *Product revisions* on page 1-7.

## 1.1 About the CoreLink NIC-400 Network Interconnect

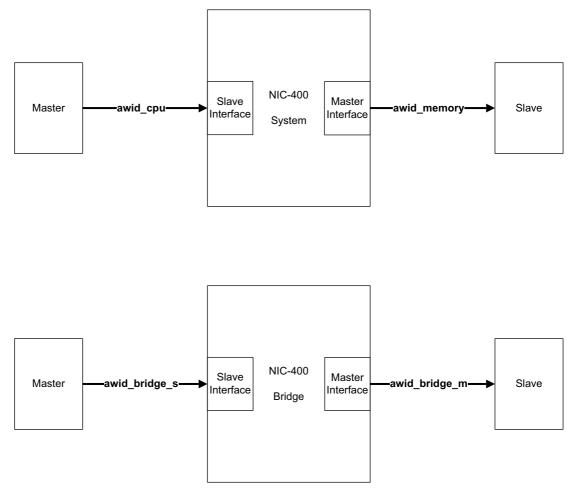

The CoreLink NIC-400 Network Interconnect is highly configurable and enables you to create a complete high performance, optimized, and AMBA-compliant network infrastructure. The possible configurations for the CoreLink NIC-400 Network Interconnect can range from a single bridge component, for example an AHB to AXI protocol conversion bridge, to a complex interconnect that consists of up to 128 masters and 64 slaves of AMBA protocols.

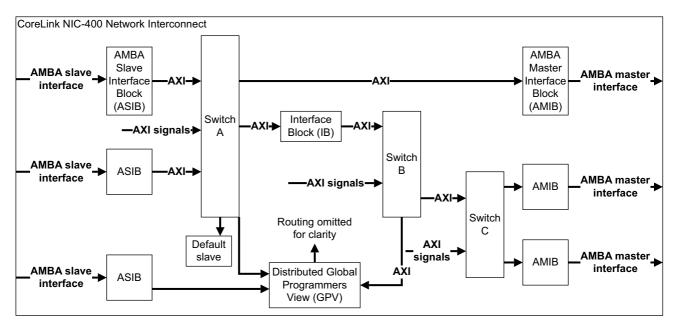

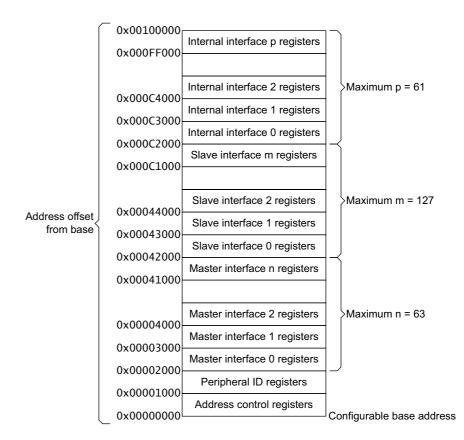

The NIC-400 configuration can consist of multiple switches with many topology options. Figure 1-1 shows a top-level block diagram of the NIC-400 that contains:

- Multiple switches.

- Multiple AMBA Slave Interface Blocks (ASIBs).

- Multiple AMBA Master Interface Blocks (AMIBs).

Figure 1-1 CoreLink NIC-400 Network Interconnect top-level block diagram

## 1.2 Key features

The CoreLink NIC-400 Network Interconnect is a highly configurable interconnect component that supports:

- 1-128 slave interfaces that can be:

- AXI3.

- AXI4.

- AHB-Lite slave interface.

- AHB-Lite mirrored master interface.

- 1-64 master interfaces that can be:

- AXI3.

- AXI4.

- AHB-Lite master interface.

- AHB-Lite mirrored slave interface.

- APB2.

- APB3.

- APB4.

- Hierarchical clock-gating.

- Configuration of:

- An APB AMIB can have up to 16 subports. Each subport can be APB2, APB3, or APB4.

- An AXI port to support four region control bits.

- An AXI port to support *Quality of Service* (QoS) signalling.

- Single-cycle arbitration.

- Full pipelining to prevent master stalls.

- Programmable control for FIFO transaction release.

- Multiple switch networks.

- Complex topologies, including *Network on Chip* (NoC) loop-back connections between switches.

- Up to five cascaded switch networks between any master and slave interface pair.

- AXI or AHB-Lite masters and slaves with:

- An address width of 32-64 bits.

- A data width of 32, 64, 128, or 256 bits.

- Non-contiguous APB slave address map for a single master interface.

- Independent widths of user-defined sideband signals for each channel.

- *Global Programmers View* (GPV) for the entire interconnect that you can configure so that any master, or a discrete configuration slave interface, can access it.

- Highly flexible timing closure options.

- Hierarchical clock-gating to reduce idle or near idle power.

- *Quality of Service* (QoS), using the QoS-400 product. See also *Optional features* on page 2-32.

\_\_\_\_\_ Note \_\_\_\_\_\_ This product is separately licensed and is not included in the NIC-400 base product.

*QoS Virtual Networks* (QVN), using the QVN-400 product. See also *Optional features* on page 2-32.

\_\_\_\_\_ Note \_\_\_\_\_

٠

This product is separately licensed and is not included in the NIC-400 base product.

Thin Links (TLX), using the TLX-400 product. See also *Optional features* on page 2-32.

Note \_\_\_\_\_\_

This product is separately licensed and is not included in the NIC-400 base product.

— Note —

The NIC-400 does not support write data interleaving on any interface.

## 1.3 Relationship between NIC-400 and AMBA Designer

AMBA Designer is a configuration tool that generates a specific implementation of a CoreLink NIC-400 Network Interconnect. AMBA Designer drives the CoreLink NIC-400 Network Interconnect generation engine to provide the following for a set of configuration parameters and implementation scripts:

- Verilog Register Transfer Level (RTL).

- Testbench and stimulus.

- Synthesis scripts.

The documentation suites and implementation scripts for the CoreLink NIC-400 Network Interconnect and AMBA Designer are designed to be used together to describe the principles of the CoreLink NIC-400 Network Interconnect and the configuration options. There is no duplication between the two sets of documentation. The following sections describe the information that each documentation suite provides:

- CoreLink NIC-400 Network Interconnect documentation.

- AMBA Designer documentation.

#### 1.3.1 CoreLink NIC-400 Network Interconnect documentation

The CoreLink NIC-400 Network Interconnect documentation consists of:

#### **Technical Reference Manual**

The *Technical Reference Manual* (TRM) describes how to create the transfer function of a network interconnect component, the features and functions available, and how to dynamically change the transfer function using the programmers model.

#### **Implementation Guide**

The *Implementation Guide* (IG) describes how to set up the network environment and how to use it to run RTL simulations or implementation scripts.

#### **Integration Manual**

The *Integration Manual* (IM) describes how to integrate a configured network into a larger subsystem.

#### 1.3.2 AMBA Designer documentation

The AMBA Designer User Guide describes how to:

- Install AMBA Designer.

- Generate and verify RTL sub-systems of ARM IP.

- Stitch ARM components together. ARM components conform to the IP-XACT standard from the SPIRIT Consortium.

The *ARM*<sup>®</sup> *CoreLink*<sup>™</sup> *Supplement to ARM*<sup>®</sup> *AMBA*<sup>®</sup> *Designer User Guide* describes how to produce a customized Network Interconnect component.

— Note —

The supplement provides configuration guidance.

#### 1.3.3 Documentation for optional CoreLink features

The optional CoreLink NIC-400 Network Interconnect documentation consists of:

#### **QoS Supplement to TRM**

The QoS Supplement to TRM describes programmable QoS facilities for attached AMBA masters that support read and write QoS requests.

#### **QVN Supplement to TRM**

The QVN Supplement to TRM describes a mechanism to avoid head of line blocking and cross path blocking between different data flows.

#### **TLX Supplement to TRM**

The TLX Supplement to TRM describes a mechanism to reduce the number of signals in an AXI point-to-point connection and enable it to be routed over a longer distance.

\_\_\_\_\_Note \_\_\_\_\_

These optional features are obtained through licenses for QoS-400, QVN-400, and TLX-400 products in addition to that required for the NIC-400 base product.

## 1.4 Product revisions

This section describes the differences in functionality between product revisions of the CoreLink NIC-400 Network Interconnect:

r0p0 First release.

**r0p0-r0p1** Configuration improvements for the following:

- Metrics added to the GUI that include:

- *Relative Size Indicator* (RSI).

- *Static Latency* (SL).

- Preallocate can be configured separately for each *Virtual Network* (VN) on external interfaces.

- Peripheral ID2 register value is changed to reflect the product status:

- Offset 0xFE8

- **Bits** [6:4]

- Value 0x1B

For the version number of the product see the *Peripheral ID registers* on page 3-10.

- r0p1-r0p2 Updated Peripheral ID2 register:

- Peripheral ID2 register value is changed to reflect the product status:

- Offset ØxFE8

- **Bits** [6:4]

- Value 0x2B

For the version number of the product, see the *Peripheral ID registers* on page 3-10.

- r0p2-r0p3 Contains the following differences in functionality:

- Additional registering option within Single Slave per ID CDAS logic to assist with timing closure.

- Increased availability of Single Active Slave (SAS) CDAS option within switch slave interfaces to assist with deadlock avoidance in multi NIC-400 systems.

- Updated data-sizing logic to improve dynamic power and output determinism, for example, to assist with the creation of 64-bit ECC values.

- Peripheral ID2 register value is changed to reflect the product status:

- **Offset** 0xFE8

- **Bits** [6:4]

- Value 0x2B

For the version number of the product, see the *Peripheral ID registers* on page 3-10.

## Chapter 2 Functional Description

This chapter describes the functionality of the CoreLink NIC-400 Network Interconnect. It contains the following sections:

- *About the functions* on page 2-2.

- *Interfaces* on page 2-3.

- *Operation* on page 2-16.

- *Optional features* on page 2-32.

## 2.1 About the functions

٠

The CoreLink NIC-400 Network Interconnect is built from functions, each with its own transfer function. A transfer function can be:

- A domain crossing, for example:

- Clock domain crossing.

- Data width crossing.

You can use a transfer function to create timing isolation, for optimizing critical network paths for latency.

Within a domain, a switch, or multiple switches, can exist to enable routing paths between any slave interface and any master interface.

The functions are configured into routing switches or *Interface Blocks* (IBs), and you can use AMBA Designer to create highly complex topologies using these modules.

## 2.2 Interfaces

This section describes the CoreLink NIC-400 Network Interconnect interfaces and contains the following subsections:

- Slave interfaces.

- *Master interfaces* on page 2-8.

- *Low-power interfaces, clock-gating* on page 2-14.

#### 2.2.1 Slave interfaces

The CoreLink NIC-400 Network Interconnect supports the following slave interfaces:

- AXI3 and AXI4 slave interfaces.

- *AHB-Lite slave interfaces* on page 2-4.

#### —— Note ———

Any transaction that does not decode to a legal master interface destination, or to a register that is visible in the programmers model, receives a DECERR response. For an AHB-Lite master, the AXI DECERR is mapped to an AHB-Lite ERROR.

The AXI DECERR error is mapped to an AHB-Lite master ERROR if:

- You do not configure the early write response.

- You configure Early Write Response and INCR Promotion and the transaction is non-cacheable. See *AHB-Lite slave interfaces* on page 2-4.

- The AHB-Lite burst is not broken.

#### AXI3 and AXI4 slave interfaces

An AXI slave interface supports the AXI protocol.

— Note ——

- The NIC-400 base product does not accept, or issue, interleaved write data.

- Data widths of 512 or 1024 bits are not supported.

#### **Configuration options**

You can configure the following options:

- Address width of 32-64 bits.

- Data width of 32, 64, 128, or 256 bits.

- User sideband signal width of 0-256 bits.

- Data width upsizer function. See *Upsizing data width function* on page 2-17.

- Data width downsizer function. See *Downsizing data width function* on page 2-19.

- Frequency domain crossing of the following types:

- ASYNC.

- SYNC 1:1.

- SYNC 1:n.

- SYNC n:1.

SYNC n:m.

Security of the following types:

**Secure** All transactions originating from this slave interface are flagged as Secure transactions and can access both Secure and Non-secure components.

#### Non-secure

All transactions originating from this slave interface are flagged as Non-secure transactions and cannot access Secure components.

#### Per access

The **AxPROT[1]** signal determines the security setting of each transaction, and the slaves that it can access.

Support for the full AXI protocol.

#### — Note —

– Note –

– Note –

- Data widths of 512 or 1024 bits are not supported.

- You can achieve a gate count reduction and a performance increase if the attached master does not create any AXI3 lock transactions.

- Write acceptance capability of 1-32 transactions.

If buffering components exist within the ASIB, then this value can be higher. For example, a full register slice in the slave interface position of the ASIB increases the write acceptance capability by two, and a forward register slice in the same position increases the write acceptance capability by one.

Read acceptance capability of 1-127 transactions.

If buffering components exist within the ASIB, then this value can be higher. For example, a full register slice in the slave interface position of the ASIB increases the read acceptance capability by two, and a forward register slice in the same position increases the read acceptance capability by one.

- Buffering, see *FIFO and clocking function* on page 2-21.

- Timing isolation:

- From the external master.

- From the network.

#### **AHB-Lite slave interfaces**

The CoreLink NIC-400 Network Interconnect can support the full AHB-Lite protocol using either:

#### An AHB-Lite slave interface

This option provides all the AHB-Lite signals that a slave would have, which includes **HSEL**, **HREADY** input, and **HREADY** output signals.

#### An AHB-Lite mirrored master interface

This option has no **HSEL** or **HREADY** input signal; it is designed to be connected directly to an AHB-Lite master.

#### ——Note —

The NIC-400 Network Interconnect requires a word invariant little endian data bus for AHB-Lite interfaces.

The following configuration options can improve AHB-Lite to AXI performance, but cannot always be used robustly:

- Early Write Response and INCR promotion.

- Allow Broken Bursts.

If you configure the interface as an AHB-Lite mirror master interface, you cannot configure **Allow Broken Bursts** because the AHB-Lite protocol does not permit AHB-Lite masters to break bursts.

Table 2-1 shows the four combinations for the configuration of Early Write Response and INCR promotion and Allow Broken Bursts, and contains links to descriptions for each option.

|                                         |                     | <b>5 1 1 1 1 1 1 1 1 1 1</b>     |

|-----------------------------------------|---------------------|----------------------------------|

| Early Write Response and INCR promotion | Allow Broken Bursts | Description of combination       |

| Configured                              | Not configured      | Combination 1                    |

| Not configured                          | Configured          | Combination 2 on page 2-6        |

| Configured                              | Configured          | <i>Combination 3</i> on page 2-6 |

| Not configured                          | Not configured      | Combination 4 on page 2-6        |

### Table 2-1 Combination of configuration parameters

#### **Combination 1**

If you configure **Early Write Response and INCR promotion** and do not configure **Allow Broken Bursts** then the network converts all:

- AHB-Lite read fixed length bursts to AXI fixed length bursts.

- AHB-Lite write fixed length bursts with **HPROT**[3] asserted to AXI fixed length bursts:

- All AHB-Lite write data beats receive an automatic OKAY response from the bridge irrespective of the B-channel AXI response. This means that if the network receives an error response, it does not feed it back to the master.

- The bridge can support up to five outstanding write accesses.

- AHB-Lite write fixed-length bursts with **HPROT[3]** negated to AXI fixed length bursts, and only the last AHB-Lite write data beat receives the AXI buffered response for the complete AHB-Lite transaction.

- AHB-Lite read INCR bursts with **HPROT**[3] asserted to AXI INCR4 bursts.

- AHB-Lite write INCR bursts with **HPROT[3]** asserted to AXI INCR4 bursts, and all AHB-Lite write data beats receive an automatic OKAY response from the bridge, irrespective of the B-channel AXI response. This means that if the network receives an error response, it does not feed it back to the master.

- Read INCR bursts with HPROT[3] negated to a series of AXI singles.

- Write INCR bursts with **HPROT**[3] negated to a series of AXI singles, and each AHB-Lite write beat is acknowledged with the AXI buffered write response.

#### **Combination 2**

If you configure **Allow Broken Bursts** and do not configure **Early Write Response and INCR promotion**, the network converts all:

- Read fixed length bursts with HPROT[3] asserted to AXI fixed length bursts.

- Read fixed length bursts with HPROT[3] negated to AXI singles.

- Write fixed length bursts with **HPROT[3]** asserted to AXI fixed length bursts, but only the last AHB-Lite write data beat receives the AXI buffered response for the whole AHB-Lite transaction. However, if the AHB-Lite burst is broken, then the network does not feed the AXI response back to the master.

- Write fixed length bursts with **HPROT[3]** negated to AXI singles, and each AHB-Lite write beat is acknowledged with the AXI buffered write response.

- Read INCR bursts to a series of AXI singles.

- Write INCR bursts to a series of AXI singles, and each AHB-Lite write beat is acknowledged with the AXI buffered write response.

#### **Combination 3**

If you configure **Early Write Response and INCR promotion** configure **Allow Broken Bursts** then the network converts all:

- Read fixed length bursts with **HPROT**[3] asserted to AXI fixed length bursts.

- Read fixed length bursts with HPROT[3] negated to AXI singles.

- Write fixed length bursts with **HPROT**[3] asserted to AXI fixed length bursts:

- The bridge sends an automatic OKAY response to all the AHB-Lite write data beats, disregarding the B-channel AXI response. Therefore, if the network generates an error response, it does not feed it back to the master.

- The bridge can support up to five outstanding write accesses because the RAW hazard detection function supports up to four transactions. A fifth write is issued, but the AHB-Lite write response is not issued until a slot is freed in the RAW hazard monitor.

- Write fixed length bursts with **HPROT[3]** negated to AXI singles, and each AHB-Lite write beat is acknowledged with the AXI buffered write response.

- Read INCR bursts with **HPROT**[3] asserted speculatively to AXI INCR4 bursts.

- Write INCR bursts with **HPROT[3]** asserted speculatively to AXI INCR4 bursts, and all AHB-Lite write data beats receive an automatic OKAY response from the bridge irrespective of the B-channel AXI response. Therefore, if the network generates an error response, it does not feed it back to the master.

- Read INCR bursts with HPROT[3] negated to a series of AXI singles.

- Write INCR bursts with **HPROT[3]** negated to a series of AXI singles, and each AHB-Lite write beat is acknowledged with the AXI buffered write response.

#### Combination 4

If you do not configure **Early Write Response and INCR promotion** and do not configure **Allow Broken Bursts** then the network converts all:

Read fixed length bursts to AXI fixed length bursts.

- Write fixed length bursts to AXI fixed length bursts, and only the last AHB-Lite write data beat receives the AXI buffered response for the whole AHB-Lite transaction.

- Read INCR bursts to a series of AXI singles.

- Write INCR bursts to a series of AXI singles, and each AHB-Lite write beat is acknowledged with the AXI buffered write response.

— Note ———

If you select either the **Early Write Response and INCR promotion** or **Allow Broken Bursts** configuration options, or both, then the following programmable function override bits also exist:

| d_incr_override | Converts all AHB-Lite read transactions to a series of single beat AXI transactions.                                                                                     |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| r_incr_override | Converts all AHB-Lite write transactions to a series of single beat AXI transactions, and each AHB-Lite write beat is acknowledged with the AXI buffered write response. |

You can configure these bits through a Global Programmers View (GPV) port.

See Chapter 3 Programmers Model for more information.

#### Error response

r

W

If the AHB-Lite master cancels a burst when it receives an ERROR response, the bridge stalls the master until the network receives all the read data beats from the AXI domain. This is only possible with read transfers because AXI writes receive a response at the end of the burst only.

—— Note ———

When communicating with transfer-sensitive slave devices such as FIFOs, the master might not be aware of how many read data beats have been read.

#### Lock transactions

The only supported lock transactions are *SWAP* (SWP) locks. That is, a single locking read followed by a single unlocking write, with an undefined number of IDLE transactions in between.

#### — Note ——

- If the network receives a non-SWP lock sequence, it is possible for a network path to be stalled, particularly if an odd number of lock transactions is issued. The stall is canceled on the next transaction received that unlocks the stalled path.

- When the read part of the SWP operation causes the accessed slave to generate an error, the error is only presented to the AHB-Lite master when the write that terminates the SWP operation has been issued.

If you configure lock support and a GPV, then a lock override function is also configured. You can program this option, named lock\_override, to force no AXI lock transactions to be created. See Chapter 3 *Programmers Model*.

#### **Configuration options**

You can configure the following AHB-Lite options:

- AHB-Lite slave or mirrored master interface types.

- Address width of 32-64 bits.

- Data width of 32, 64, 128, or 256 bits.

- Data width upsizer function that Upsizing data width function on page 2-17 describes.

- Data width downsizer function that *Downsizing data width function* on page 2-19 describes.

- Frequency domain crossing of the following types:

- ASYNC.

- SYNC 1:1.

- SYNC 1:n.

- SYNC n:1.

- SYNC n:m.

- Security of the following types:

**Secure** All transactions originating from this slave interface are flagged as Secure transactions and can access both Secure and Non-secure components.

#### Non-secure

All transactions originating from this slave interface are flagged as Non-secure transactions and cannot access Secure components.

- Early Write Response and INCR promotion.

- Permit broken bursts using the Allow Broken Bursts parameter.

- Support for the full AHB-Lite protocol with only SWP locks.

\_\_\_\_\_Note \_\_\_\_\_

You can reduce the gate count and increase the performance if the attached master does not create any AHB-Lite lock transactions.

- Timing isolation:

- From the external master.

- From the network.

- User signals.

— Note —

**HAUSER** maps onto **AWUSER** or **ARUSER** internally depending on the access type.

**HWUSER** maps onto **WUSER**. **RUSER** maps to **HRUSER**.

#### 2.2.2 Master interfaces

The CoreLink NIC-400 Network Interconnect supports the following master interfaces:

- AXI3 and AXI4 master interfaces on page 2-9.

- *AHB-Lite master interfaces* on page 2-10.

- *APB master interfaces* on page 2-12.

#### AXI3 and AXI4 master interfaces

The network supports the AXI protocol using an AXI master interface.

—— Note ———

Data widths of 512 or 1024 bits are not supported.

#### **Configuration options**

You can configure the following AXI options:

- Address width of 32-64 bits.

- Data width of 32, 64, 128, or 256 bits.

- User sideband signal width of 0-256 bits.

- Data width upsizer function that Upsizing data width function on page 2-17 describes.

- Data width downsizer function that *Downsizing data width function* on page 2-19 describes.

- Frequency domain crossing of type:

- ASYNC.

- SYNC 1:1.

- SYNC 1:n.

- SYNC n:1.

- SYNC n:m.

- Support for the full AXI protocol.

— Note —

- You can reduce the gate count and increase the performance if all attached masters that can access the master interface do not create any AXI lock transactions.

- Data widths of 512 or 1024 bits are not supported.

- Write issuing capability of 1-32 transactions.

#### \_\_\_\_\_Note \_\_\_\_\_

A switch before the AMIB does not issue more than two write address transfers without seeing the associated write data. This reduces the logic requirements in the switch and improves system QoS. It does not have an effect on throughput for the write channel.

Read issuing capability of 1-127 transactions.

\_\_\_\_\_ Note \_\_\_\_\_

You can configure the read issuing capability as 0 when a master interface is not also configured as upsizing or downsizing, and when it is not converting between AXI3 and AXI4. The value of 0 removes any limiting of the read issuing capability by the interface. The read issuing capability is the sum of all upstream nodes that can access the interface.

- Buffering that *FIFO and clocking function* on page 2-21 describes.

- Timing isolation:

٠

— From the external slave.

- From the network.

- AXI masters. You can reduce the number of ID bits exported at the master interface. See *Global ID and ID reduction* on page 2-30.

- AXI region:

- You can determine an AXI region value for a slave by applying an additional finer granularity at the address decode. Alternatively, you can input a region from the master. The AXI region is output to all slaves that have **Multi-region Slave** selected.

— Note —

You can select a 4-bit output region for a slave value, or you can input a region from the master interface.

If an APB slave is addressed, then an input region is overridden by the full address decode.

#### **AHB-Lite master interfaces**

The CoreLink NIC-400 Network Interconnect can support the full AHB-Lite protocol using either:

#### An AHB-Lite mirrored slave interface

This option provides all the AHB-Lite signals that a slave would have, which includes **HSEL**, **HREADY** input, and **HREADY** output signals. This enables the direct connection of an AHB-Lite slave to the NIC-400.

#### An AHB-Lite master interface

This option provides all the AHB-Lite signals that you would expect to see on an AHB-Lite master, so it does not have **HSEL** or **HREADY** output signals.

— Note —

The NIC-400 Network Interconnect requires a word invariant little endian data bus for AHB-lite interfaces.

Table 2-2 shows the mapping of AXI burst types to AHB-Lite burst types.

| AxBURST | Number of transfers in AXI transaction                                                                                                                       | HBURST | Notes                                                                    |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------------------------------|

| FIXED   | -                                                                                                                                                            | SINGLE | This is a series of singles, and the number depends on the AxLEN setting |

| INCR    | 1                                                                                                                                                            | SINGLE | -                                                                        |

| -       | 4                                                                                                                                                            | INCR4  | -                                                                        |

| -       | 8                                                                                                                                                            | INCR8  | -                                                                        |

| -       | 16                                                                                                                                                           | INCR16 | -                                                                        |

| -       | 2, 3, 5, 6, 7, 9, 10, 11, 12, 13, 14, 15<br>AXI4 extends burst length support for the INCR burst type<br>to 2, 3, 5, 6, 7, 9, 10, 11, 12, 13, 14, 15, 17-256 | INCR   | Undefined length                                                         |

| WRAP    | 2                                                                                                                                                            | SINGLE | Two transfers                                                            |

#### Table 2-2 AXI burst type to AHB-Lite burst type mapping

| AxBURST | Number of transfers in AXI transaction | HBURST | Notes |

|---------|----------------------------------------|--------|-------|

| WRAP    | 4                                      | WRAP4  | -     |

| -       | 8                                      | WRAP8  | -     |

| -       | 16                                     | WRAP16 | -     |

#### Table 2-2 AXI burst type to AHB-Lite burst type mapping (continued)

#### — Note ——

Transactions from AHB-Lite slave interfaces that are configured with early write response or broken bursts are output as INCR transactions of an undefined length.

If the AHB-Lite protocol conversion function receives an unaligned address, or a write data beat without all the byte strobes set, the CoreLink NIC-400 Network Interconnect detects it, and a programmable enable bit decerr\_en permits the network to create a DECERR response. See Table 3-3 on page 3-8.

The network still transmits the unaligned address transfer into the AHB-Lite domain, but it aligns the address by forcing the lower address bits of the size of the transaction to zeros.

— Note ——

- Because AHB-Lite does not support write data strobes when accessing AHB-Lite slaves from an AXI master, care must be taken not to generate transactions that have partial strobes. An example of this would be when a AXI master is accessing an AHB-Lite slave. Instead of issuing a single 32-bit transaction with **WSTRB** 00110 you must issue two 8-bit transactions.

- If you set the force\_incr programmable bit, and a beat is received that has no write data strobes set, that write data beat is replaced with an IDLE beat. For more information on the force\_incr programmable bit see Table 3-3 on page 3-8.

- You can configure the inclusion of the programmable enable bit to create a reduced gate count implementation.

The network breaks any transactions that cross a 1KB boundary into multiple AHB-Lite INCR bursts. You can configure a programmable option, named force\_incr. See Table 3-3 on page 3-8. This option maps all transactions that are to be output to the AHB-Lite domain to be an undefined length INCR.

If the AXI burst is part of a locked sequence, the AHB-Lite translation keeps **HMASTLOCK** asserted across the boundary to ensure that the burst atomicity is not compromised. For write transactions, AHB-Lite responses are merged into a single AXI buffered response. The merged response is an AXI SLAVE ERROR if any of the AHB-Lite data beats have an AHB-Lite ERROR.

Any transaction that the network receives without all write data strobes asserted or negated still goes ahead. This means that erroneous data bytes might be written to the slave.

#### **Configuration options**

You can configure the following options for the AHB-Lite interface:

- AHB-Lite master or mirrored slave interface types.

- Address width of 32-64 bits.

- Data width of 32, 64, 128, or 256 bits.

- Data width upsizer function.

AHB-Lite AMIB does not support data packing.

- Data width downsizer function that *Downsizing data width function* on page 2-19 describes.

- Frequency domain crossing of the following types:

- ASYNC.

- SYNC 1:1.

- SYNC 1:n.

- SYNC n:1.

- SYNC n:m.

- Security of the following types:

Secure Only Secure transactions can access components attached to this master interface.

Non-secure

Both Secure and Non-secure transactions can access components attached to this master interface.

#### **Boot Secure**

You can use software to configure whether Secure and Non-secure transactions are permitted to access components attached to this master using the Secure and Non-secure options.

- Support for the full AHB-Lite master protocol.

- Timing isolation:

- From the external slave.

- From the network.

- User signals.

— Note —

HAUSER maps onto AWUSER or ARUSER internally depending on the access type. HWUSER maps onto WUSER.

**RUSER** maps to **HRUSER**.

#### **APB** master interfaces

You can configure each APB interface to be of type APB2, APB3, or APB4. The APB data width is always 32 bits, and it is therefore never necessary for the APB interface to require the upsizer function. The APB interface can ignore AXI writes strobes. If the network receives a write transaction with all of the write strobes negated, then it does not perform the write.

\_\_\_\_\_ Note \_\_\_\_\_

APB SLVERR responses are converted to AXI SLVERR responses.

Any transaction that the network receives without all four write data strobes asserted or negated still proceeds. This means that erroneous data bytes might be written to the APB3 or the ABP2 slaves.

—— Note ———

Because APB4 supports write strobes, the APB4 slave is unaffected by sparse data bytes.

The masters accessing the APB interface must ensure that only word writes access the APB sub-system. The address and data widths are fixed as follows:

- Address width of 32 bits.

- Data width of 32 bits.

#### **Configuration options**

You can configure the following options:

- Data width downsizer function as *Downsizing data width function* on page 2-19 describes.

- Frequency domain crossing for the majority of APB ports of the following types:

- ASYNC.

- SYNC 1:1.

- SYNC 1:n.

- SYNC n:1.

- SYNC n:m.

- Buffering as *FIFO and clocking function* on page 2-21 describes.

- 1-16 supported APB slaves.

- Configurable address region sizes.

- Non-contiguous address regions.

- You can configure each APB slave for:

- APB2, APB3, or APB4.

- Asynchronous interface to the majority of APB ports.

- Security of the following types:

- Secure for each APB port.

- Non-secure for each APB port.

- Boot Secure for all APB ports.

#### \_\_\_\_\_ Note \_\_\_\_\_

- To configure an APB port as Secure or Non-secure, the parent AMIB must have the TrustZone option configured as From Port. All other APB ports on that AMIB must also be configured to be Secure or Non-secure.

- To configure an APB port as Boot Secure, all other APB ports in a group and the parent AMIB must be Boot Secure. The parent AMIB must also have the TrustZone option configured as Boot Secure.

For more information about TrustZone<sup>®</sup> technology and security, see *TrustZone* technology and security on page 2-25.

#### 2.2.3 Low-power interfaces, clock-gating

The AXI low-power interface, C channel, used in the hierarchical clock-gating feature, contains the signals that Table 2-3 shows.

Table 2-3 AXI low-power interface

| Signal  | Direction     | Source, destination      | Description                       |

|---------|---------------|--------------------------|-----------------------------------|

| CACTIVE | Output, input | Interconnect, controller | Interconnect active               |

| CSYSREQ | Output, input | Controller, interconnect | System low-power request          |

| CSYSACK | Output, input | Interconnect, controller | Low-power request acknowledgement |

A low-power interface is present for each clock domain when hierarchical clock-gating is enabled. Hierarchical clock-gating is a global parameter in the NIC-400 configuration. Any slave interface that is configured as an AHB-Lite cannot support hierarchical clock-gating completely because the protocol does not support it.

The AHB-Lite protocol expects a slave to take the address when issued. No mechanism exists for a slave to avoid this, so if the clock for an AHB-Lite interface is off, the address phase of the transfer is lost. Therefore, any AHB-Lite slave interface is required to be in its own unique clock domain.

To turn the AHB-Lite interface clock off, the system designer must ensure that no transactions are inhibited at this interface.

A **CACTIVE** output is provided to show the interface status. This is an additional signal provided specifically to support AHB-Lite. The interface status is whether the interface is busy or not, that is, whether **CACTIVE** is HIGH or LOW.

The ARM<sup>®</sup> AMBA<sup>®</sup> AXI and ACE Protocol Specification contains additional information on the function of these signals.

— Note -

The *ARM*<sup>®</sup> *AMBA*<sup>®</sup> *AXI* and *ACE Protocol Specification* describes the case where **CACTIVE** can remain HIGH when **CSYSACK** falls, and you can interpret this as a denial of the request, with the clock continuing to run. It is not necessary to support this functionality when implementing clock-gating for the NIC-400. When **CSYSACK** falls, it is always safe to gate the clock.

AMIBs with APB connections into another clock domain do not support hierarchical clock\_gating on that boundary. This is because of the large overhead of creating clock control circuitry for effectively one side of an APB asynchronous bridge. The system designer is therefore responsible for ensuring that the clock is already enabled on this interface. The system designer can achieve this in one of two ways:

- By using external logic to ensure that the clock to the APB interface is enabled whenever the APB interface is accessed.

- By ensuring that the APB clock is on the path through the interconnect prior to the APB AMIB.

Either of these solutions enables the NIC to wake up and maintain the clock until the transaction is complete.

## 2.3 Operation

This section describes how the CoreLink NIC-400 Network Interconnect operates, and contains the following subsections:

- AXI3 and AXI4 protocol conversion.

- *Hierarchical clock-gating* on page 2-17.

- *Upsizing data width function* on page 2-17.

- *Downsizing data width function* on page 2-19.

- *FIFO and clocking function* on page 2-21.

- *Arbitration* on page 2-23.

- Cyclic Dependency Avoidance Schemes (CDAS) on page 2-24.

- *Single Active Slave* on page 2-25.

- Lock support on page 2-25.

- *TrustZone technology and security* on page 2-25.

- *Remap* on page 2-27.

- Global ID and ID reduction on page 2-30.

#### 2.3.1 AXI3 and AXI4 protocol conversion

This section describes:

- AXI4 to AXI3.

- AXI3 to AXI4.

#### AXI4 to AXI3

AXI4 long bursts are split into multiple AXI3 bursts, up to a length of 16 beats as required. You can determine the number of output transactions by the formula shown in Figure 2-1:

sum of the number of incoming bytes of an input transaction

number of bytes of an output beat

#### Figure 2-1 Determining the number of output transactions

When more than one transaction is output, then each one is 16 beats apart from the last, which might not be of the same length.

#### AXI3 to AXI4

The maximum possible AXI4 output burst length is 16 beats, unless the downsizing function is also configured.

If there is a requirement to prevent AXI3 transactions creating long bursts, then you can configure a burst limiter function. The burst limiter requires a programmer interface to enable selection of burst limiting or no burst limiting. See registers for the *AXI Slave Interface Block* (ASIB), AXI internal network *Interface Block* (IB), and *AXI Master Interface Block* (AMIB) in Chapter 3 *Programmers Model*.

— Note —

AXI4 does not support locked transactions, therefore you must only use exclusive atomic accesses to access an AXI4 slave from an AXI3 master.

#### 2.3.2 Hierarchical clock-gating

Hierarchical clock-gating is a feature that enables a system to transition to another power state. This can be a low-power state where, in low activity scenarios, the power that the clock tree consumes can be saved. Hierarchical clock-gating enables an external clock controller to individually request clock domains in the interconnect to block new transactions from entering the interconnect when there are no outstanding transactions within the clock domain. The domain then acknowledges that this process is complete and the clock controller is able to remove the clock. Giving control over individual clock domains permits flexible system design and therefore flexible power state design.

The programmers model is distributed throughout the interconnect and therefore generally through multiple clock domains. See Chapter 3 *Programmers Model*. When the hierarchical clock-gating feature is enabled, and more than one clock domain contains a view to a register that is visible in the programmers model or an access point, an additional clock domain is added to the interconnect. This clock domain distributes accesses to the programmers model between the user-specified clock domains. It automatically requests the clock for other domains and makes clock-gating transparent to you when accessing the programmers model. This additional clock domain also has an AXI low-power interface that must be connected to a clock controller in the same way as the other interfaces. All communication between clock domains is carried out asynchronously so the clock frequency of this central ring can be set to what you require, within the limits of bridge limitations stated in the documentation.

#### 2.3.3 Upsizing data width function

The upsizer function can expand the data width by the following ratios:

- 1:2.

- 1:4.

- 1:8.

Upsizing only packs write data for write or read transactions that are cacheable. This section describes the packing rules for different burst types and acceptance capabilities, and the following definitions apply:

- An aligned input burst means that the address is aligned to the output data width word boundary, after the network aligns it to the size of the transfer.

- An unaligned input burst means that the network does not align the address to the output data width word boundary, even after it aligns it to the size of the transfer.

- If a transaction passes through, this means that the upsizer function does not change the input transaction size and type.

—— Note ———

- If the network splits input exclusive transactions into more than one output bus transaction, it removes the exclusive information from the multiple transactions it creates.

- If multiple responses from created transactions are combined into one response, then the order of priority is:

- DECERR is the highest priority.

- SLVERR is the next highest priority.

- OKAY is the lowest priority.

In the examples in this section, the input data width is 64 bits, and the output data width is 128 bits, unless otherwise stated. This section describes:

*INCR bursts* on page 2-18.

- Upsize.

- *WRAP bursts* on page 2-19.

- *Fixed bursts* on page 2-19.

- *Bypass merge* on page 2-19.

- Acceptance capability on page 2-19.

#### **INCR bursts**

The network converts all input INCR bursts that complete within a single output data width into an INCR1 of the minimum SIZE possible, and it packs all INCR bursts into INCR bursts of the optimum size possible. Table 2-4 shows how the network converts INCR bursts when it upsizes them.

| INCR burst type                                    | Converted to               |

|----------------------------------------------------|----------------------------|

| 64-bit INCR1                                       | Passes through unconverted |

| 64-bit aligned INCR2                               | INCR1                      |

| 8-bit aligned INCR8                                | INCR1, 64-bit              |

| 8-bit unaligned, byte address 1, 2, or 3, INCR5    | INCR1, 128-bit             |

| 8-bit unaligned, byte address 4, 5, 6, or 7, INCR5 | INCR2, 64-bit              |

| 64-bit unaligned INCR2                             | Passes through unconverted |

| 64-bit aligned INCR4                               | INCR2                      |

| 64-bit unaligned INCR4                             | Sparse INCR3               |

#### Table 2-4 Conversion of INCR bursts by the upsizer function

— Note —

Bursts are never merged.

#### Upsize

When upsizing and protocol converting to or from AXI3 and AXI4, then the following maximum INCR burst lengths are shown in Table 2-5.

#### Table 2-5 Maximum INCR burst lengths

| Ratio | AXI3 to AXI3         | AXI3 to AXI4         | AXI4 to AXI4          | AXI4 to AXI3         |

|-------|----------------------|----------------------|-----------------------|----------------------|

| 1:2   | Maximum Len16 output | Maximum Len16 output | Maximum Len256 output | Maximum Len16 output |

| 1:4   | Maximum Len16 output | Maximum Len16 output | Maximum Len256 output | Maximum Len16 output |

| 1:8   | Maximum Len16 output | Maximum Len16 output | Maximum Len256 output | Maximum Len16 output |

#### WRAP bursts

All WRAP bursts are either passed through unconverted as WRAP bursts, or converted to one or two INCR bursts of the output bus. Table 2-6 shows how the network converts WRAP bursts when it upsizes them from 64 bits to 128 bits, that is, a ratio of 1:2.

| WRAP burst type            | Converted to                                                                                 |

|----------------------------|----------------------------------------------------------------------------------------------|

| 128-bit aligned WRAP2      | INCR1.                                                                                       |

| 128-bit aligned WRAP4      | WRAP2.                                                                                       |

| 128-bit unaligned<br>WRAP4 | <ul> <li>Depending on the address</li> <li>INCR2 + INCR1.</li> <li>INCR1 + INCR2.</li> </ul> |

— Note —

The network converts input WRAP bursts with a total payload that is less than the output data width to a single INCR.

#### **Fixed bursts**

All FIXED bursts pass through unconverted.

#### Bypass merge

You can configure the upsizer function to have a programmable bit named bypass\_merge. If bypass\_merge is asserted, the network does not alter any transactions that can pass through legally without alteration.

#### Acceptance capability

You can configure the upsizer to support 1-32 read transactions and 1-32 write transactions. The issuing capability is a maximum of twice the acceptance capability.

#### 2.3.4 Downsizing data width function

The downsizer function reduces the data width by the following ratios:

- 2:1.

- 4:1.

- 8:1.

The downsizer does not merge data narrower than the destination bus if the transaction is marked as non-cacheable.

This section describes the following:

- *INCR bursts* on page 2-20.

- *Downsize* on page 2-20.

- WRAP bursts on page 2-20.

- FIXED bursts on page 2-21.

- *Bypass merge* on page 2-21.

- Acceptance capability on page 2-21.

#### **INCR** bursts

The CoreLink NIC-400 Network Interconnect converts INCR bursts that fall within the maximum payload size of the output data bus to a single INCR burst. It converts INCR bursts that are greater than the maximum payload size of the output data bus to multiple INCR bursts. Table 2-7 shows how the network converts INCR bursts when it downsizes them.

| INCR8              |

|--------------------|

| пчено              |

| INCR7 <sup>a</sup> |

| INCR16 + INCR2     |

|                    |

to the destination width, and is not aligned to the source width. For example, if 0x4 is placed on a 64-32 bit downsizer, then 0x1 still requires an INCR8.

INCR bursts with a size that matches the output data width pass through unconverted.

The CoreLink NIC-400 Network Interconnect packs INCR bursts with a SIZE smaller than the output data width to match the output width whenever possible, using the upsizer transfer function. See *Upsizing data width function* on page 2-17.

#### Downsize

When downsizing and protocol converting to or from AXI3 and AXI4, then the following maximum INCR burst lengths are shown in Table 2-8.

| Ratio | AXI3 to AXI3         | AXI3 to AXI4         | AXI4 to AXI4                       | AXI4 to AXI3         |

|-------|----------------------|----------------------|------------------------------------|----------------------|

| 1:2   | Maximum Len16 output | Maximum Len16 output | Maximum Len256 output <sup>a</sup> | Maximum Len16 output |

| 1:4   | Maximum Len16 output | Maximum Len16 output | Maximum Len256 output              | Maximum Len16 output |

| 1:8   | Maximum Len16 output | Maximum Len16 output | Maximum Len256 output              | Maximum Len16 output |

#### Table 2-8 Maximum INCR burst lengths

a. In AXI3 to AXI4 downsizing, you can create long bursts from an AXI3 burst input. If a restriction to short bursts is required, you can control this by a programmable register. For more information, see the registers for the ASIB, IB, and AMIB in Chapter 3 *Programmers Model*.

#### WRAP bursts

The CoreLink NIC-400 Network Interconnect always converts WRAP bursts to WRAP bursts of twice the length, up to the output data width maximum size of WRAP16, in that case, it treats the WRAP burst as two INCR bursts that can each map onto one or more INCR bursts.

— Note —

If a wrap transaction is aligned to the wrap boundary, it is converted into an INCR transaction.

# **FIXED** bursts

The CoreLink NIC-400 Network Interconnect converts FIXED bursts to one or more INCR1 or INCRn bursts depending on the downsize ratio. Table 2-9 shows how the network converts FIXED bursts when it downsizes them.

| FIXED burst type | Converted to    |

|------------------|-----------------|

| FIXED1           | INCR2           |

| FIXED2           | INCR2 + INCR2 + |

#### Table 2-9 Conversion of FIXED bursts by the downsizer function

The CoreLink NIC-400 Network Interconnect optimizes unaligned fixed bursts. If an unaligned input fixed burst maps onto a single output beat, then the output is a fixed burst of the optimal size.

### **Bypass merge**

You can configure the downsizer function to have a programmable bit named bypass\_merge. If bypass\_merge is asserted, the network does not perform any packing of beats to match the optimum SIZE, up to the output data width SIZE.

An aligned input burst means that the address is aligned to the input data width word boundary after the network aligns it to the transfer size. An unaligned input burst means that the address is not aligned to the input data width word boundary, even after the network aligns it to the transfer size.

If a transaction passes through, this means that the downsizer function does not change the input transaction size and type.

— Note —

If an exclusive transaction is split into multiple transactions at the output of the downsizer, the exclusive flag is removed and the master never receives an EXOKAY response. Response priority is the same as for the upsizer function. See *Upsizing data width function* on page 2-17.

# Acceptance capability

You can configure the acceptance capability to 1-32 read transactions and 1-32 write transactions. The maximum issuing capability is (size ratio  $\times$  acceptance capability +1).

# 2.3.5 FIFO and clocking function

If you configure the network as a clock frequency crossing bridge, then a FIFO function is also configured.

— Note ——

You can configure the buffering for multiple outstanding transactions even if you are using a 1:1 clocking ratio.

You can instantiate a FIFO on any channel. You can configure the FIFO to implement both buffering and clock domain crossing functionality. You can define the FIFO to be:

SYNC 1:1.

.

SYNC 1:n.

- SYNC n:1.

- ASYNC.

- SYNC m:n.

```

— Note —

```

You can dynamically change this through the GPV.

The network automatically determines that the width of the FIFO is the width of the widest payload, in or out of the block. You can configure the depth of the FIFO to be 2-32.

All clock boundary crossings are implemented using a FIFO structure with appropriate synchronization for the current mode of operation.

# Changing the synchronization when you select programmable mode

You can change the boundary type by modifying the synchronization that is applied to the two pointers as they pass between domains. This ensures that the data in the FIFO is stable and safe to use.

The following options are available:

#### Asynchronous

Select this if the two clocks bear no relationship to one another.

#### Synchronous (1:1)

Select this if the two clocks are the same.

#### Synchronous (1:n)

Select this if both of the following are true:

- The first clock has a lower frequency than the second clock.

- The positive edge of the first clock always coincides with a positive edge of the second clock.

#### Synchronous (m:1)

Select this if both of the following are true:

- The first clock has a higher frequency than the second clock.

- The positive edge of the second clock always coincides with a positive edge of the first clock.

# Synchronous (m:n)

Select this if both of the following are true:

- Both clocks are derived from a common faster clock.

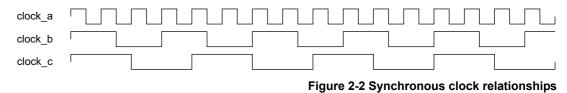

- The positive edge of both "m" and "n" clocks always coincides with a positive edge of the common faster clock. Figure 2-2 shows an example of two clocks, **clock\_b** and **clock\_c** that you can class with this clock relationship.

To change the clocks, the synchronization must remain correct at all times. Table 2-10 shows the actions you must take to convert from one mode to another.

| Original mode | Required mode  | Action                                                                                               |  |  |

|---------------|----------------|------------------------------------------------------------------------------------------------------|--|--|

| ASYNC         | Any other mode | Change the clocks, then change the register.                                                         |  |  |

| Any mode      | ASYNC          | Change the register, then change the clocks. BRESP from the GPV implies that the update is complete. |  |  |

| SYNC m:n      | SYNC 1:1       | Change the clocks, then change the register.                                                         |  |  |

| SYNC 1:1      | SYNC m:n       | Change the register, then change the clocks.                                                         |  |  |

|               |                |                                                                                                      |  |  |

Table 2-10 How to change synchronization modes

#### — Note ——

For some changes, you must use a different setting, that is, you can only change safely from SYNC 1:n to SYNC m:1 by first programming the register to SYNC m:n, before the clock update.

#### Data release mechanism

When you configure a write data FIFO depth of at least four, you can also set an additional write tidemark function, named wr\_tidemark. This is a tidemark level that stalls the release of the transaction until:

- The network receives the WLAST beat.

- The write FIFO becomes full.

- The number of occupied slots in the write data FIFO exceeds the write tidemark. See Chapter 3 *Programmers Model*.

# 2.3.6 Arbitration

You can program the arbitration algorithm for all arbitration nodes within the interconnect.

At the entry point to the infrastructure, all transactions are allocated a local QoS that you can configure to be:

- Static.

- Programmable.

- Received from the attached master, for AXI only.

The arbitration of the transaction as it passes through the interconnect uses this QoS. See Chapter 3 *Programmers Model*.

At any arbitration node, a fixed priority exists for transactions with a different QoS. The highest value has the highest priority. If there are coincident transactions at an arbitration node with the same QoS that require arbitration, then the network uses a *Least Recently Used* (LRU) algorithm.

— Note ——

Alternatively, QoS allocation schemes can be implemented using the QoS-400 add-on.

# 2.3.7 Cyclic Dependency Avoidance Schemes (CDAS)

Because the AXI protocol permits re-ordering of transactions, it might be necessary for the CoreLink NIC-400 Network Interconnect to enforce rules to prevent deadlock when routing multiple transactions concurrently to multiple slaves from a point of ingress to the interconnect, that is, at a slave interface.

Each ASIB can have a different CDAS configured. The same CDAS scheme is configured for both read and write transactions, but they operate independently.

This section describes:

- Single slave.

- Single slave per ID.

# Single slave