# ARM CoreLink MMU-400 System Memory Management Unit

Revision: r0p1

**Technical Reference Manual**

### ARM CoreLink MMU-400 System Memory Management Unit Technical Reference Manual

Copyright © 2011, 2014 ARM. All rights reserved.

#### **Release Information**

The *Change history* table lists the changes made to this book.

#### Change history

| Date            | Issue | Confidentiality  | Change                 |

|-----------------|-------|------------------|------------------------|

| 07 October 2011 | A     | Non-Confidential | First release for r0p0 |

| 20 March 2014   | В     | Non-Confidential | First release for r0p1 |

#### **Proprietary Notice**

Words and logos marked with  $^*$  or  $^{\rm m}$  are registered trademarks or trademarks of ARM $^*$  in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

### Contents

## **ARM CoreLink MMU-400 System Memory Management Unit Technical Reference Manual**

|           | Pret  | ace                                       |      |

|-----------|-------|-------------------------------------------|------|

|           |       | About this book                           | vi   |

|           |       | Feedback                                  | ix   |

| Chapter 1 | Intro | oduction                                  |      |

| •         | 1.1   | About the MMU-400                         | 1-2  |

|           | 1.2   | Features of the MMU-400                   | 1-4  |

|           | 1.3   | Configurable options                      | 1-6  |

|           | 1.4   | Product revisions                         | 1-7  |

| Chapter 2 | Fund  | ctional Description                       |      |

| •         | 2.1   | About the functions                       | 2-2  |

|           | 2.2   | Interfaces                                |      |

|           | 2.3   | Generation of StreamID                    |      |

|           | 2.4   | Generation of the SSD index               | 2-8  |

|           | 2.5   | Determining the security state of masters | 2-9  |

|           | 2.6   | Hit-Under-Miss (HUM)                      | 2-10 |

|           | 2.7   | Fault handling                            | 2-11 |

|           | 2.8   | Dynamic programming                       | 2-12 |

| Chapter 3 | Prog  | grammers Model                            |      |

| -         | 3.1   | About the programmers model               | 3-2  |

|           | 3.2   | The MMU-400 address map                   |      |

|           | 3.3   | Register summary                          |      |

|           | 3.4   | Global Register Space 0                   |      |

|           | 3.5   | Global Register Space 1                   |      |

|           |       |                                           |      |

| Appendix B | Revi | sions                                                  |      |

|------------|------|--------------------------------------------------------|------|

|            | A.3  | Miscellaneous signals                                  | A-19 |

|            | A.2  | AMBA signals                                           |      |

|            | A.1  | Clock and resets                                       |      |

| Appendix A | Sign | al Descriptions                                        |      |

|            | 3.10 | Translation Context Bank registers                     | 3-50 |

|            | 3.9  | Peripheral and Component Identification registers      | 3-46 |

|            | 3.8  | The MMU-400 Security State Determination Address Space | 3-44 |

|            | 3.7  | Performance Monitoring registers                       |      |

|            | 3.6  | Integration registers                                  | 3-33 |

### **Preface**

This preface introduces the  $ARM^{\otimes}CoreLink^{\bowtie}MMU-400$  System Memory Management Unit Technical Reference Manual. It contains the following sections:

- About this book on page vi.

- Feedback on page ix.

#### About this book

This book is for the MMU-400.

#### **Product revision status**

The rnpn identifier indicates the revision status of the product described in this book, where:

**rn** Identifies the major revision of the product.

**pn** Identifies the minor revision or modification status of the product.

#### Intended audience

This book is written for system designers, system integrators, and programmers who are designing or programming a device that uses the MMU-400.

#### Using this book

This book is organized into the following chapters:

#### Chapter 1 Introduction

Read this for an introduction to the MMU-400 and its features.

#### Chapter 2 Functional Description

Read this for an overview of the major functional blocks and the operation of the MMU-400.

#### Chapter 3 Programmers Model

Read this for a description of the MMU-400 memory map and registers.

#### Appendix A Signal Descriptions

Read this for a description of the MMU-400 signals.

#### Appendix B Revisions

Read this for a description of the technical changes between released issues of this book.

#### Glossary

The ARM® Glossary is a list of terms used in ARM documentation, together with definitions for those terms. The ARM® Glossary does not contain terms that are industry standard unless the ARM meaning differs from the generally accepted meaning.

See the ARM® Glossary,

http://infocenter.arm.com/help/topic/com.arm.doc.aeg0014-/index.html.

#### Conventions

Conventions that this book can use are described in:

- Typographical conventions on page vii.

- Signals on page vii.

#### **Typographical conventions**

The following table describes the typographical conventions:

#### Typographical conventions

| Style             | Purpose                                                                                                                                                                                                           |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| italic            | Introduces special terminology, denotes cross-references, and citations.                                                                                                                                          |

| bold              | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.                                                                             |

| monospace         | Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.                                                                                                       |

| <u>mono</u> space | Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.                                                                           |

| monospace italic  | Denotes arguments to monospace text where the argument is to be replaced by a specific value.                                                                                                                     |

| monospace bold    | Denotes language keywords when used outside example code.                                                                                                                                                         |

| <and></and>       | Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example: MRC p15, 0 <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd>                                   |

| SMALL CAPITALS    | Used in body text for a few terms that have specific technical meanings, that are defined in the <i>ARM® Glossary</i> . For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE. |

#### **Signals**

The signal conventions are:

Signal level

The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals

- LOW for active-LOW signals.

Lower-case n

At the start or end of a signal name denotes an active-LOW signal.

#### **Additional reading**

This section lists publications by ARM and by third parties.

See Infocenter, http://infocenter.arm.com, for access to ARM documentation.

#### **ARM** publications

This book contains information that is specific to this product. See the following documents for other relevant information:

- ARM® System Memory Management Unit Architecture Specification (ARM IHI 0062).

- *ARM*<sup>®</sup> *CoreSight*<sup>™</sup> *Architecture Specification* (ARM IHI 0029).

- ARM® Architecture Reference Manual ARMv7-A and ARMv7-R edition (ARM DDI 0406).

- ARM® AMBA® AXI and ACE Protocol Specification AXI3, AXI4, and AXI4-Lite ACE and ACE-Lite (ARM IHI 0022).

The following confidential books are only available to licensees:

- ARM ®CoreLink™ MMU-400 System Memory Management Unit AMBA® Designer (ADR-400) User Guide Supplement (ARM DSU 0017).

- *ARM® CoreLink™ MMU-500 System Memory Management Unit Technical Reference Manual Supplement* (ARM DSU 0030).

- *ARM* <sup>®</sup>CoreLink<sup>™</sup> *MMU-400 System Memory Management Unit Implementation Guide* (ARM DII 0265).

- *ARM* ®*CoreLink*™ *MMU-400 System Memory Management Unit Integration Manual* (ARM DII 0266).

#### **Feedback**

ARM welcomes feedback on this product and its documentation.

#### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

#### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

ARM also welcomes general suggestions for additions and improvements.

- The title.

- The number, ARM DDI 0472B.

- The page numbers to which your comments apply.

- A concise explanation of your comments.

ARM tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader.

### Chapter 1 **Introduction**

This chapter provides an overview of the MMU-400. It contains the following sections:

- About the MMU-400 on page 1-2.

- Features of the MMU-400 on page 1-4.

- Configurable options on page 1-6.

- *Product revisions* on page 1-7.

#### 1.1 About the MMU-400

The *ARM*® *CoreLink*™ *MMU-400* provides ARM v7 virtualization extensions to bus masters in the system other than the processor. The MMU-400 translates addresses in hardware to accelerate hypervisor software virtualization of multiple guest *Operating Systems* (OS)s. You can also configure the MMU-400 to optimize the features, performance, and gate count required for the intended applications.

An address translation from an input address to an output address is described as a stage of address translation.

The MMU-400 supports the translation table formats defined by the ARM architecture, ARMv7, and can perform stage 2 translations that translate an input *intermediate physical address* (IPA) to an output *physical address* (PA). The MMU-400 uses inputs from the requesting master to identify a context. This context communicates to the MMU-400 what resources to use for the translation including which translation tables to use.

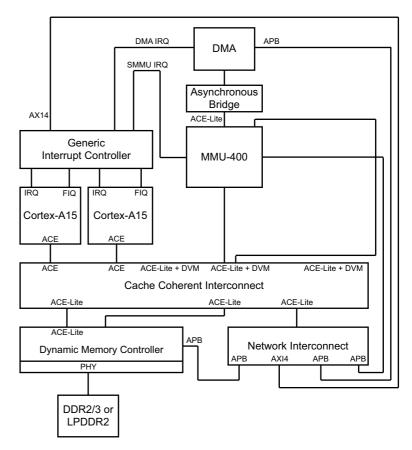

Figure 1-1 shows a single MMU-400 in an example system, performing address translation functions for a *Direct Memory Access* (DMA) controller.

Figure 1-1 MMU-400 in system context

The MMU-400 checks access permissions, translates addresses, and provides the capability to generate or merge access attributes. The *Translation Look-aside Buffer* (TLB) maintenance is performed through:

- Distributed Virtual-memory Messaging (DVM) signaling.

- Programmable control registers.

The following are example masters for the MMU-400:

- Graphics Processor Unit (GPU).

- · Video engines.

- DMA controllers.

- Color LCD (CLCD) controllers.

- Network controllers.

The MMU-400 routes each translation through the following logical processing steps:

- Security state determination.

- Context determination.

- Page table walk, if the translation is not cached in the TLB.

- Protection checks.

- Attribute generation or merging, depending on the programming.

You can configure the MMU-400 to bypass the translation process for a transaction or to fault a transaction regardless of the translation state.

#### 1.2 Features of the MMU-400

The MMU-400 provides the following features:

- Converts from 32-bit to 40-bit Large Physical Address Extension (LPAE) addresses for 32-bit IO devices.

- For more information on LPAE addresses, see the ARM® Architecture Reference Manual ARMv7-A and ARMv7-R edition.

- Multiple transaction contexts to apply to address translations for specific streams of transactions.

- Supports up to eight configurable contexts. The MMU-400 maps each context by using an input StreamID from the master device that requires address translation.

- Stage 2 translations that translate an input IPA to an output PA in the ARM LPAE format.

- For more information on LPAE addresses, see the ARM® Architecture Reference Manual ARMy7-A and ARMy7-R edition.

- Translation support for the ARMv7 4KB, 2MB, and 1GB page sizes:

- For more information on ARM v7 virtualization extensions, LPAE addresses, see the ARM® Architecture Reference Manual ARMv7-A and ARMv7-R edition.

- Page table walk cache for storing intermediate page table walk data.

- Page table entry cache in the TLB.

- Support for TLB *Hit-Under-Miss* (HUM).

- Up to four parallel page table walks.

- TLB invalidation through the AMBA 4 DVM signaling or register programming.

- For more information on the DVM signaling, see the ARM® AMBA® AXI and ACE Protocol Specification AXI3, AXI4, and AXI4-Lite ACE and ACE-Lite.

- Translation and protection check support including TrustZone® extension support.

- Fault handling, logging, and signaling that excludes demand paging support.

- Debug and performance-monitoring events.

- One AMBA slave interface that supports any of the following per *translation buffer unit* (TBU) for connecting the bus master device that requires address translations:

- AXI3 protocol.

- AXI4 protocol.

- ACE-Lite.

- One AMBA master interface for master device transactions or *Page Table Walks* (PTWs) that support any of the following:

- AXI3 protocol.

- AXI4 protocol.

- ACE-Lite with optional DVM extensions that supports the AXI data width, which are 64 or 128 bits with a configurable depth write buffer.

- An APB interface for programming that supports either of the following:

- Separate APB3 interfaces for Secure and Non-secure programming.

- A single APB4 interface for both Secure and Non-secure programming>.

The MMU-400 is based on the ARM® System MMU Architecture Specification.

#### 1.2.1 Performance Targets

The typical TLB hit access latency is 2-3 cycles and the miss latency depends on memory sub-system infrastructure. The following table lists the process technology frequency targets.

Table 1-1 Process technology frequency targets

| Process    | Frequency Targets |        |  |  |

|------------|-------------------|--------|--|--|

| Technology | Min               | Max    |  |  |

| CP32LP     | 400Mhz            | 533Mhz |  |  |

#### 1.3 Configurable options

The following table lists the design-time features and configuration options supported by the MMU-400.

Table 1-2 Design-time features and configuration options

| Feature                                    | Min | Max |

|--------------------------------------------|-----|-----|

| Stage 1 translation (VA→IPA) <sup>a</sup>  | No  | Nob |

| Stage 2 translation (IPA→PA) <sup>a</sup>  | Yes | Yes |

| Stage 1 and Stage 2 (VA→PA) <sup>a</sup>   | No  | Nob |

| Translation contexts                       | 1   | 8   |

| Profiling resource banks                   | 3   | 3   |

| TLB entries                                | 2   | 64  |

| ACE-TLB invalidation through DVMa          | No  | Yes |

| Parallel PTWs                              | 4   | 4   |

| Translation prediction/pre-fetcha          | Yes | Yes |

| Debug TLB visibility <sup>a</sup>          | Yes | Yes |

| Software TLB loading <sup>a</sup>          | Noc | Noc |

| Page table walk (QoS aware) <sup>a</sup>   | Yes | Yes |

| Outstanding transactions                   | 1   | 128 |

| Input/Output port bus width                | 64  | 128 |

| Input ports ACE-Lite + DVM <sup>d</sup>    | 0   | 1   |

| Output ports ACE-Lite                      | 0   | 1   |

| Programming port (APB4 or APB3)            | 1   | 1   |

| Generation of error responses <sup>a</sup> | Yes | Yes |

|                                            |     |     |

a. Where:

Yes Indicates that the MMU-400

supports the feature.

**No** Indicates that the MMU-400 does not support the feature.

- c. The direct TLB control is not recommended for security reasons.

- d. The ACE-Lite + DVM is a subset of AMBA 4

ACE, the AMBA Coherency Extensions. You can

tie-off the unused signals.

b. The MMU-500 supports stage 1 and stage 1 followed by stage 2 translations.

#### 1.4 Product revisions

This section describes the differences in functionality between product revisions of the MMU-400:

**r0p0** First release.

r0p0 - r0p1 No functional changes.

## Chapter 2 **Functional Description**

This section describes the functional operation of the MMU-400. It contains the following sections:

- *About the functions* on page 2-2.

- *Interfaces* on page 2-3.

- *Generation of StreamID* on page 2-7.

- Generation of the SSD index on page 2-8.

- Determining the security state of masters on page 2-9.

- Hit-Under-Miss (HUM) on page 2-10.

- Fault handling on page 2-11.

- *Dynamic programming* on page 2-12.

#### 2.1 About the functions

The TLB and PTW are the major functional blocks of the MMU-400. The TLB caches frequently used address ranges and the PTW performs page table walks.

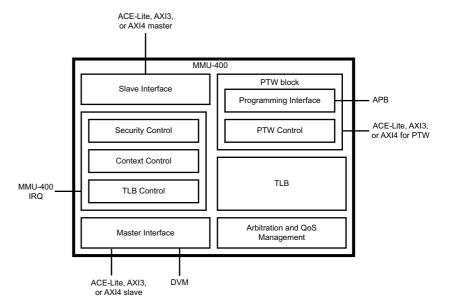

Figure 2-1 shows the block diagram for the MMU-400.

Figure 2-1 MMU-400 block diagram

The MMU-400 applies the following logical processing steps to every transaction:

- 1. Determines the security state of the device that originates the transaction. The security attribute presented on **AWPROT[1]** and **ARPROT[1]** signals is different from the security state of the device. Identifying the security state of the device is called security state determination.

- 2. Maps an incoming transaction to one of the contexts using an incoming StreamID.

- Caches frequently used address ranges using the TLB. The best-case hit latency of this

caching is two clocks when the TBU address slave register slices are not implemented.

The best-case latency is three clocks when the TBU address slave register slices are

specified.

- 4. Performs the main memory PTW automatically on a TLB address miss.

- The MMU-400 shares the page table formats with the processor as specified in the LPAE for maximum efficiency.

- For more information on LPAE addresses, see the *ARM*<sup>®</sup> *Architecture Reference Manual ARMv7-A and ARMv7-R edition*.

- 5. Applies the required fault handling for every transaction.

- 6. Performs debug and performance monitoring through programmable performance counters that report statistics, for example, TLB refills or number of read or write accesses.

#### 2.2 Interfaces

The MMU-400 contains the following interfaces:

- AXI interfaces.

- Programming interface.

- *ACE-Lite interfaces* on page 2-4.

- Low-power interface for clock gating on page 2-5.

#### 2.2.1 AXI interfaces

The MMU-400 supports the following AXI interfaces:

- AXI master interface.

- *AXI slave interface.*

#### **AXI** master interface

The AXI master interface, with \_m suffix, drives the translated address to the downstream slave. You must connect pin-to-pin the read address, write address, read data, write data, and buffered write response channels to the corresponding AXI slave interface.

If the MMU-400 is configured to support a dedicated interface for PTWs, you must connect the read address and read data channels of the slave interface associated with the PTWs to the MMU-400 PTW channel. In this configuration, the PTW channel contains the \_ptw suffix. For example, araddr ptw and acaddr ptw.

#### **AXI** slave interface

The AXI slave interface, with \_s suffix, drives the untranslated address to the TBU. You must connect pin-to-pin the read address, write address, read data, write data, and buffered write response channels of the AXI slave interface to an AXI master interface. In a system, the master interface can be the AXI bus infrastructure output or the output of a bridge that converts another bus protocol to AXI.

There must be AXI type compatibility between the MMU-400 and the master connected to the MMU-400.

#### 2.2.2 Programming interface

The MMU-400 uses the APB interface as a programming interface, to permit the software to program the registers and to perform the debug operation.

The MMU-400 provides one of the following interfaces, which is selected during the MMU-400 configuration:

- The APB4 programming interface. For more information on MMU-400 integration into the AMBA 4 system, see the ARM® AMBA® AXI and ACE Protocol Specification AXI3, AXI4, and AXI4-Lite ACE and ACE-Lite.

- Two APB3 programming interfaces. One of the APB interfaces is configured as Secure, and other interface is configured as Non-secure. You must ensure that only:

- The Secure transactions are sent on the Secure interface.

- The Non-secure transactions are sent on the Non-secure interface.

For more information, see the ARM® AMBA® AXI and ACE Protocol Specification AXI3, AXI4, and AXI4-Lite ACE and ACE-Lite.

#### **APB** slave interface

You must connect the APB slave interface to an AMBA 3 APB or AMBA 4 APB master, depending on the APB configuration type.

If you have configured the AMBA 3 APB interface, there are two ports with \_s suffix for Secure register accesses and an \_ns suffix for Non-secure register accesses.

The MMU-400 provides a 32-bit address bus, **paddr[31:0**], but it only uses bits[15:2]. The MMU-400 ignores:

- Bits[31:16], but their presence facilitates the MMU-400 integration with adjacent RTL blocks, such as an interconnect.

- Bits[1:0], because the smallest accesses allowed to its internal registers are word accesses.

If the APB is not running at the same frequency as that of the **cclk** signal, then you can divide the frequency using the **pclken** signal value.

When operating at this frequency, the APB master must also use the **pclken** signal so that the signal states change only on enabled clock edges. If the APB interface is to run at the same frequency as that of the **cclk** signal, you must ensure that the **pclken** signal is tied HIGH.

#### 2.2.3 ACE-Lite interfaces

You can configure the MMU-400 to use one of the AXI3, AXI4, or ACE-Lite interfaces to receive and forward transactions, and to perform page table walks. The interface information is described in the following sections:

- AXI3 interface.

- *AXI4 interface* on page 2-5.

Write data interleaving

- *ACE-Lite interface* on page 2-5.

- *TLB block barrier support* on page 2-5.

#### **AXI3** interface

The MMU-400 can be configured to support the AXI3 protocol. In this mode, only AXI3 signaling is present on the main data path through the MMU-400.

The MMU-400 supports DVM messages only if a dedicated ACE-Lite master port is configured to perform PTWs.

The following features of AXI3 are not supported in the MMU-400:

| Note                 | <del></del>                                                                                                                                                                                            |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Write data an occur. | d write address ordering must be the same, otherwise data corruption can                                                                                                                               |

| transaction ha       | er. The AxLOCK[1] signal bit cannot be set to 1. However, if any s its AxLOCK[1] set, then it is ignored, and the output transaction has the reset. The other bits of the AxLOCK signal are supported. |

| —— Note              |                                                                                                                                                                                                        |

|                      | 100 receives a locked transaction, the output transaction is passed to the lave as a normal access.                                                                                                    |

#### **AXI4** interface

The MMU-400 can be configured to support the AXI4 protocol. In this mode, only the AXI4 signaling is present on the main data path through the MMU-400.

The MMU-400 supports DVM messages only if a dedicated ACE-Lite master port is configured to perform PTWs.

#### **ACE-Lite interface**

The MMU-400 can be configured to support the ACE-Lite protocol. In this mode, only the ACE-Lite signaling is present on the main data path through the MMU-400.

The MMU-400 supports DVM messages with a combined master port, or when a dedicated ACE-Lite master port is configured to perform PTWs.

When you configure the MMU-400 to support the ACE-Lite interface, you must connect the AC channel to the CCI-driven AC channel or to the ACE-compatible slave interface that supports DVM messaging.

ARM recommends that you use the DVM channel for TLB maintenance operations. If the system cannot access the DVM channel, you must tie the **ACVALID** signal LOW and use the programming interface for TLB maintenance operations.

When you configure the MMU-400 to provide a dedicated AXI channel to perform PTWs, the ACVALID channel must be part of the PTW.

#### TLB block barrier support

A TLB block in the MMU-400 receives, passes on, and generates barriers of its own, in response to the **SYNC** signal received from the DVM channel of the PTW block.

The PTW block sends the **SYNC** signal to the TLB block on receiving one of the following:

- The SYNC message received on the programming interface.

- The DVM **SYNC** message.

For more information on SYNC and DVM SYNC messages, see the ARM® AMBA® AXI and ACE Protocol Specification AXI3, AXI4, and AXI4-Lite ACE and ACE-Lite.

#### 2.2.4 Low-power interface for clock gating

The MMU-400 has two AXI low-power interfaces each of which can be connected pin-to-pin to a dedicated interface of a clock controller. You can use the low-power interfaces to disable the clock of each sub-block of the MMU-400. Alternatively, if there is no clock controller, you must tie the **csysreq\_\*** inputs HIGH, and can leave the outputs, **csysack\_\*** and **cactive\_\*** unconnected.

For more information on the signal functionality, see the ARM® AMBA® AXI and ACE Protocol Specification AXI3, AXI4, and AXI4-Lite ACE and ACE-Lite.

| Note —                  | <del></del>       |                |                    |

|-------------------------|-------------------|----------------|--------------------|

| You must gate the clock | when the csysreq_ | * and csysack_ | * signals are LOW. |

The MMU-400 has two AXI LPIs that allow you to disable the clock for the PTW and TLB blocks independently, as the following sections describe:

- *TLB block* on page 2-6.

- *PTW block* on page 2-6.

#### **TLB block**

An external clock controller can request the TLB block to enter the low-power state by de-asserting the **csysreq tbu** signal.

The TLB block can enter the low-power state under the following conditions:

- No outstanding access is pending.

- No input access is pending.

- No TLB maintenance operation is pending.

When the preceding conditions are satisfied, the **cactive\_tbu** signal is set LOW. The low-power entry request is acknowledged when the **csysreq\_tbu** signal goes LOW. You must disable the clock when the **csysack\_tbu** and **cactive\_tbu** signals are LOW. For more information on the AXI LPI signals, see *AXI low-power interface signals* on page A-17.

#### PTW block

During normal operation, the PTW block is in the idle state. Therefore ARM recommends that you use the AXI low-power interface to disable the clock for this block.

An external clock controller can request the PTW block to enter into the low-power mode by de-asserting the **csysreq\_tcu** signal.

The PTW block pulls the **cactive\_tcu** signal LOW when all the following conditions are satisfied:

- The **PSEL**x signal is LOW.

- The **ACVALID** signal is LOW.

- No outstanding PTW request is pending.

The **PSELx** signal is combinatorially connected to the **cactive\_tcu** signal. Therefore, if the APB interface is synthesized at a value less than that of the **cclk** signal using the **pclken** signal, treat the **cactive\_tcu** signal as asynchronous to prevent metastability problems in the clock controller.

The PTW block acknowledges the low-power entry request by setting the **csysack\_tcu** signal LOW. You can disable the clock when the **csysack\_tcu** and **cactive\_tcu** signals are LOW. For more information on the AXI LPI signals, see *AXI low-power interface signals* on page A-17.

#### 2.3 Generation of StreamID

A StreamID is used to map the incoming transaction to a context by using the stream mapping table. The characteristics of the StreamID are as follows:

- The width of the StreamID is selected during the MMU-400 configuration.

- The width of the StreamID is selected as a function of the incoming AXI ID that is used for read or write transactions and up to 8 sideband signals. Select the StreamID width of the sideband signal parameter value from the range 1-15 bits.

The following signals are selected to generate the StreamID:

**AWID/ARID** Bits[22:0]. If the StreamID width is less than 23 bits, you can set only the

valid bits to one.

R/W Bit[23]. If this bit is set, you can generate the StreamID with this bit set to

one for writes and zero for reads.

**Sideband signals** You can have a maximum of eight sideband signals.

The bit positions of the StreamID stay the same for writes and reads, though different signals are used to arrive at the StreamID.

#### Example 2-1 Generation of StreamID - example 1

If bit[7], bit[4], bit[3], and bit[2] of **AWID/ARID**, the R/W bit, and four of the sideband signals are selected to generate the StreamID, the final generated StreamID has the following formats:

#### Where:

- wsb\_sid and rsb\_sid are the write and read sideband signals for the StreamID respectively.

- awid and arid are the write and read ID signals respectively.

#### Example 2-2 Generation of StreamID - example 2

If bit[2], bit[1], and bit[0] of **AWID/ARID** are selected to generate the StreamID, that is, there is no R/W bit and there are no sideband signals, the final generated StreamID has the following formats:

#### Where:

- wsb\_sid and rsb\_sid are the write and read sideband signals for the StreamID respectively.

- awid and arid are the write and read ID signals respectively.

#### 2.4 Generation of the SSD index

The generation of the SSD index is similar to that of the StreamID.

The SSD index is selected during configuration. It is selected as a function of the incoming AXI ID, and up to eight sideband signals. Select the SSD index signal width parameter value from the range 1-15 bits.

The following signals are selected to generate the SSD index:

**AWID/ARID** Bits[22:0]. If the ID width is less than 23 bits, you can set the valid bits to one

**Sideband signals** You can have a maximum of eight sideband signals.

The bit positions of SSD index stay the same for writes and reads, though different signals are used to arrive at the SSD index.

#### Example 2-3 Generation of StreamID - example 1

If bit[5], bit[3], bit[2], and bits[1:0] of **AWID/ARID** and two sideband signals are selected to generate the SSD Index, the final generated SSD index has the following formats:

#### Where:

- wsb\_ssd and rsb\_ssd are the write and read sideband signals for the SSD index respectively.

- awid and arid are the write and read ID signals respectively.

#### Example 2-4 Generation of StreamID - example 2

If bit[13], bit[10], and bit[5] of **AWID/ARID** are selected to generate the SSD index, that is, there are no sideband signals, the final generated SSD index has the following formats:

#### Where:

- wsb\_ssd and rsb\_ssd are the write and read sideband signals for the SSD index respectively.

- awid and arid are the write and read ID signals respectively.

#### 2.5 Determining the security state of masters

When the SSD index is determined, the SSD table contains bits from 0 to 2<sup>(SSD Index WIDTH)</sup>-1. You must determine the status of the bits as follows:

#### List of non-programmable indices

For these indices, the security state of the master is defined and does not change.

You must specify the indices of the masters whose security states are always Secure.

#### List of programmable indices

You can program the security state of the programmable indices.

You must determine the default state of each master whose security state is programmable.

Indices that are not included in the following states are considered as non-programmable non-secure indices:

- Non-programmable secure.

- Programmable.

#### \_\_\_\_\_ Note \_\_\_\_\_

- An entry must not be duplicated in more than one list.

- You must specify at least one programmable or fixed Non-secure entry for every configuration.

#### Example 2-5 Programmable and non-programmable indices

If the SSD index width is 6 bits, there are 64 indices whose security states must be determined. For example:

Programmable secure default indices 1, 5, 9, 41, 60, 62

Programmable non-secure default indices 3, 7, 22, 42, 61, 63

**Secure indices** 24, 26, 28, 40

The indices between 0 and 63 that are not listed here are fixed as Non-secure indices.

#### 2.6 Hit-Under-Miss (HUM)

HUM allows responses to the master if there is a TLB hit for a subsequent transaction while the MMU-400 is performing a translation for a previous transaction that had a TLB miss.

The HUM functionality is enabled by the write buffer.

HUM enables the hit transactions coming after miss transactions to be translated by the MMU-400. The hit transactions are translated only if the write data from the miss transactions can be accommodated in the write buffer.

The HUM has certain characteristics for read and write transactions:

- If the transactions are read access, HUM is automatically enabled.

- If the transactions are write operations, HUM is enabled or disabled based on the write buffer depth. You can specify the write buffer depth during configuration.

- If the depth of the write buffer is zero, HUM is automatically disabled.

- If the depth of the write buffer is non-zero, a write hit transaction is translated only

if the write data from a missed transaction can be accommodated in the write buffer.

The number of outstanding missed transactions is determined by the depth of the write buffer. For example, if the depth of the buffer is four then it can hold two transactions of length two. Each buffer entry holds only one beat of the transaction, even if it is of a narrow width.

Example 2-6 shows a HUM condition.

Example 2-6 Hit under miss

Consider that the write buffer depth is eight and there are two missed write transactions of lengths four and three. Both missed write transactions are stored in the write buffer during the PTWs for the transactions. If you perform another transaction before the missed write transactions are processed, the new transaction is passed through, if that access results in a TLB hit.

|                                                                      | - |

|----------------------------------------------------------------------|---|

| Note                                                                 |   |

| f the write buffer is full of missed transactions, HUM cannot occur. |   |

|                                                                      |   |

#### 2.7 Fault handling

| Note                                                      |     |

|-----------------------------------------------------------|-----|

| The MMU-400 does not support the stall fault handling mod | le. |

The MMU-400 supports the terminate fault handling mode.

On a fault, the faulted transaction results in an abort based on the fault report setting in the following registers:

- The Secure Configuration Register for global faults.

- The System Control Register of that context for context faults.

When a fault occurs, the transactions that arrive after the faulted transaction can also fault if both of the following conditions are true:

- The second transaction is in the same 4K region and is in the same context as the first transaction.

- The second transaction is received before the response for the first transaction has been sent by MMU-400.

This fault can occur even if a fault clear is received between the first and second transactions.

| ——Note ———                                                                                      |

|-------------------------------------------------------------------------------------------------|

| The MMU-400 does not log an external fault reported to the SMMU system in response to a         |

| transaction issued at a slave interface associated with any context bank. However, it logs a    |

| reported external fault that is synchronous to the SMMU system in response to a fetch issued as |

| part of a translation table walk.                                                               |

For information about the fault handling, see the ARM® System Memory Management Unit Architecture Specification.

#### 2.8 Dynamic programming

ARM recommends that you modify the contents of any control register only when there are no outstanding transactions in the MMU-400. If any of the control registers are modified when there is an existing transaction in the MMU-400, then the following behaviors occur:

- When a control register is written, if a transaction arrives at the MMU-400 after the **PREADY**signal, the MMU-400 ensures that the new register attributes are applied to the transaction.

- When a control register is written, if a transaction is pending within MMU-400, it is unknown whether the old register attributes or new register attributes are applied to that transaction.

## Chapter 3 **Programmers Model**

This chapter describes the MMU-400 registers and provides information about programming the MMU-400. It contains the following sections:

- *About the programmers model* on page 3-2.

- The MMU-400 address map on page 3-3.

- Register summary on page 3-4.

- Global Register Space 0 on page 3-10.

- Global Register Space 1 on page 3-30.

- *Integration registers* on page 3-33.

- Performance Monitoring registers on page 3-36.

- The MMU-400 Security State Determination Address Space on page 3-44.

- Peripheral and Component Identification registers on page 3-46.

- Translation Context Bank registers on page 3-50.

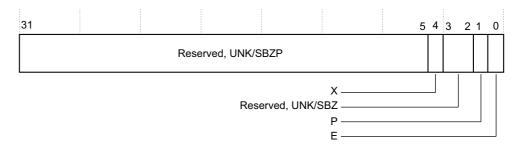

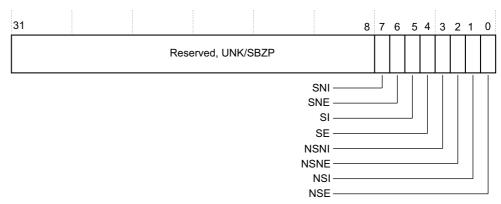

#### 3.1 About the programmers model

The following information applies to the MMU-400 registers:

- Registers are implemented according to the ARM® System Memory Management Unit Architecture Specification with the security extensions implemented in the MMU-400 as follows:

- Global space 0 registers summary on page 3-4.

- Global space 1 register summary on page 3-6.

- Integration registers summary on page 3-7.

- *Performance monitoring registers summary* on page 3-7.

- The MMU-400 security state determination address space summary on page 3-8.

- Peripheral and Component identification summary on page 3-8.

- Translation context bank address map summary on page 3-8.

The following information applies to the MMU-400 registers:

- Unless otherwise stated in the accompanying text:

- Do not modify undefined register bits.

- Ignore undefined register bits on reads.

- All register values are UNKNOWN on reset unless otherwise stated.

- Access types in Table 3-1 on page 3-4 and Table 3-7 on page 3-8 are described as follows:

RW Read and write.

RO Read-only.

WO Write-only.

RAZ Read-As-Zero.

WI Write-ignored.

RAO Read-As-One.

**RAZ/WI** Read-As-Zero, Writes Ignored.

**RAO/SBOP** Read-As-One, Should-Be-One-or-Preserved on writes.

**RAO/WI** Read-As-One, Writes Ignored.

**RAZ/SBZP** Read-As-Zero, Should-Be-Zero-or-Preserved on writes.

**SBO** Should-Be-One.

**SBOP** Should-Be-One-or-Preserved.

SBZ Should-Be-Zero.

**SBZP** Should-Be-Zero-or-Preserved.

When you configure registers using APB4, all transactions must be privileged and data.

In other words, you must set PPROT[0]=1 and PPROT[2]=0, else these transactions are treated as RAZ/WI.

#### 3.2 The MMU-400 address map

The MMU-400 is configured through a memory-mapped register frame. The total size of the MMU-400 address range depends on the number of implemented translation contexts.

The MMU-400 address map consists of the following equally sized portions:

#### The global address space

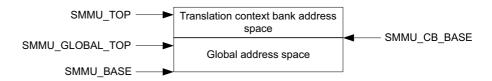

The global address space is located at the bottom of the MMU-400 address space, at SMMU BASE. See Figure 3-1.

#### The translation context bank address space

The translation context bank address space is located above the top of the global address space, at SMMU TOP. See Figure 3-1.

Figure 3-1 The MMU-400 address map, global space, and translation context bank

You can determine the size of the MMU-400 address range by reading the following register fields:

- SMMU IDR1.PAGESIZE.

- SMMU IDR1.NUMPAGENDXB.

For more information, see the ARM® System Memory Management Unit Architecture Specification.

#### 3.3 Register summary

This section describes the registers of the MMU-400 in base offset order. The register map contains the following main blocks:

- Global space 0 registers summary.

- Global space 1 registers summary on page 3-6.

- *Integration register summary* on page 3-7.

- *Performance monitoring registers summary* on page 3-7.

- The MMU-400 security state determination address space summary on page 3-8.

- Peripheral and Component identification registers summary on page 3-8.

- Translation context bank registers summary on page 3-8.

The following tables show the MMU-400 registers and provide a reference to the register description that either this book or the *ARM*<sup>®</sup> *System Memory Management Unit Architecture Specification* includes:

- Global space 0 registers summary.

- Global space 1 registers summary on page 3-6.

- *Integration register summary* on page 3-7.

- *Performance monitoring registers summary* on page 3-7.

- The MMU-400 security state determination address space summary on page 3-8.

- Peripheral and Component identification registers summary on page 3-8.

- *Translation context bank registers summary* on page 3-8.

#### 3.3.1 Global space 0 registers summary

Table 3-1 shows the global space 0 registers in base offset order.

| Note          |            |            |        |           |     |           |

|---------------|------------|------------|--------|-----------|-----|-----------|

| The addresses | that are n | not descri | bed in | Table 3-1 | are | Reserved. |

Table 3-1 Global space 0 registers summary

| Name                  | Туре | S or NS <sup>a</sup> | Offset  | Description                                  | Notes                |

|-----------------------|------|----------------------|---------|----------------------------------------------|----------------------|

| SMMU_SCR0<br>SMMU_CR0 | RW   | S<br>NS              | 0x00000 | Secure Configuration Register 0 on page 3-10 | Banked with security |

| SMMU_SCR1             | RW   | S                    | 0x00004 | Secure Configuration Register 1              | Secure only          |

| SMMU_ACR              | RW   | NS                   | 0x00010 | Auxiliary Configuration Register on          | -                    |

| SMMU_SACR             |      | S                    |         | page 3-16                                    | Banked with security |

Table 3-1 Global space 0 registers summary (continued)

| Name                                  | Type | S or NSa | Offset  | Description                                          | Notes                |

|---------------------------------------|------|----------|---------|------------------------------------------------------|----------------------|

| SMMU_IDR0                             | RO   | S<br>NS  | 0x00020 | Identification registers on page 3-17                | -                    |

| SMMU_IDR1                             | _    | S<br>NS  | 0x00024 |                                                      | -                    |

| SMMU_IDR2                             | _    | S<br>NS  | 0x00028 |                                                      | -                    |

| SMMU_IDR7                             | _    | S<br>NS  | 0x0003C |                                                      | -                    |

| SMMU_SGFAR[31:0]<br>SMMU_GFAR[31:0]   | RW   | S        | 0x00040 | Global Fault Address Register                        | Banked with security |

| SMMU_SGFAR[63:32]<br>SMMU_GFAR[63:32] | _    |          | 0×00044 |                                                      |                      |

| SMMU_GFSR                             | RW   | NS       | 0x00048 | Global Fault Status Register                         | -                    |

| SMMU_SGFSR                            | _    | S        | =       |                                                      | Banked with security |

| SMMU_GFSRRESTORE                      | WO   | NS       | 0x0004C | Global Fault Status Register Restore                 | -                    |

| SMMU_SGFSRRESTORE                     |      | S        | _       |                                                      | Banked with security |

| SMMU_GFSYNR0                          | RW   | NS       | 0x00050 | Global Fault Syndrome Register 0                     | -                    |

| SMMU_SGFSYNR0                         |      | S        |         |                                                      | Banked with security |

| SMMU_GFSYNR1                          | RW   | NS       | 0x00054 | Global Fault Syndrome Register 1                     | -                    |

| SMMU_SGFSYNR1                         |      | S        |         |                                                      | Banked with security |

| SMMU_STLBIALL                         | WO   | S<br>NS  | 0x00060 | Invalidate entire TLB Register                       | Secure only          |

| SMMU_TLBIVMID                         | WO   | NS       | 0x00064 | Invalidate TLB by VMID Register                      | -                    |

| SMMU_TLBIALLNSNH                      | WO   | NS       | 0x00068 | Invalidate Entire Non-secure<br>Non-Hyp TLB Register | -                    |

| SMMU_STLBGSYNC                        | WO   | S        | 0x00070 | Global Synchronize TLB Invalidate                    | _                    |

| SMMU_TLBGSYNC                         |      | NS       |         | Register                                             | -                    |

| SMMU_STLBGSTATUS                      | RO   | S<br>NS  | 0x00074 | Global TLB Status Register                           | Banked with security |

| SMMU_TLBGSTATUS                       |      |          |         |                                                      | -                    |

| SMMU_DBGRPTR                          | RW   | S        | 0×00080 | Debug registers on page 3-23                         |                      |

| SMMU_DBGRDATA                         | RO   | S        | 0x00084 |                                                      | -                    |

|                                       |      |          |         |                                                      |                      |

Table 3-1 Global space 0 registers summary (continued)

| Name                            | Type | S or NSa | Offset            | Description                                                                  | Notes               |

|---------------------------------|------|----------|-------------------|------------------------------------------------------------------------------|---------------------|

| SMMU_NSCR0                      | RW   | S        | 0×00400           | Secure Alias to Non-secure<br>Configuration Register 0 on<br>page 3-27       | Secure only         |

| SMMU_NSACR                      | RW   | S        | 0x00410           | Secure Alias to Non-secure Auxiliary<br>Configuration Register on page 3-27  | Secure only         |

| SMMU_NSGFAR[31:0]b              | RW   | S        | 0x00440           | Secure alias for Non-secure Global<br>Fault Address Register                 | Secure only, 64-bit |

| SMMU_NSGFAR[63:32]b             | RW   | S        | 0x00444           | Secure alias for Non-secure Global<br>Fault Address Register                 | -                   |

| SMMU_NSGFSRb                    | WO   | S        | 0x00448           | Secure alias for Non-secure Global<br>Fault Status Register                  | Secure only         |

| SMMU_NSGFSRRESTORE <sup>b</sup> | WO   | S        | 0x0044C           | Secure alias for Non-secure Global<br>Fault Status Register Restore          | Secure only         |

| SMMU_NSGFSYNR0b                 | RW   | S        | 0x00450           | Secure alias for Non-secure Global<br>Fault Syndrome Register 0              | Secure only         |

| SMMU_NSGFSYNR1b                 | RW   | S        | 0x00454           | Secure alias for Non-secure Global<br>Fault Syndrome Register 1              | Secure only         |

| SMMU_NSTLBGSYNC <sup>b</sup>    | WO   | S        | 0x00470           | Secure alias for Non-secure Global<br>Synchronize TLB Invalidate<br>Register | Secure only         |

| SMMU_NSTLBGSTATUSb              | RO   | S        | 0x00474           | Secure alias for Non-secure Global<br>TLB Status Register                    | Secure only         |

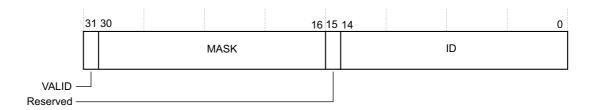

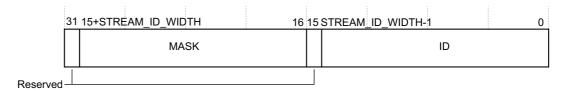

| SMMU_SMRn                       | RW   | S<br>NS  | 0x00800-0x0087C   | Stream Match Registers on page 3-27                                          | -                   |

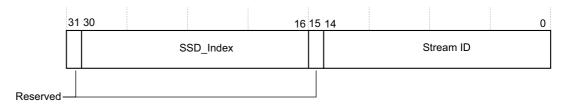

| SMMU_S2CRn                      | RW   | S<br>NS  | 0x00C00 - 0x00C7C | Stream to Context registers on page 3-29                                     | -                   |

a. S stands for Secure and NS stands for Non-secure.

#### 3.3.2 Global space 1 registers summary

Table 3-2 shows the translation context bank address map in base offset order.

Table 3-2 Global space 1 register summary

| Name              | Туре | S or NS | Offset        | Description                                                    |

|-------------------|------|---------|---------------|----------------------------------------------------------------|

| SMMU_CBFRSYNRA0-7 | RW   | NS      | 0x1400-0x141C | Context Bank Fault Restricted Syndrome Register A on page 3-30 |

| SMMU_CBAR0-7      | RW   | NS      | 0x1000-0x101C | Context Bank Attribute Register on page 3-31                   |

b. Using Secure aliases, the Non-secure version of the banked registers are accessed.

#### 3.3.3 Integration register summary

Table 3-3 shows the integration registers in base offset order.

**Table 3-3 Integration registers summary**

| Name | Туре | S or NS | Offset | Description                                   |

|------|------|---------|--------|-----------------------------------------------|

| ITEN | RW   | NS/S    | 0x2000 | Integration Enable Register on page 3-33      |

| ITIP | RO   | NS/S    | 0x2004 | Integration Test Input Register on page 3-34  |

| ITOP | RW   | NS/S    | 0x2008 | Integration Test Output Register on page 3-34 |

#### 3.3.4 Performance monitoring registers summary

Table 3-4 shows the performance monitoring registers in base offset order.

Table 3-4 Performance monitoring registers summary

| Name                | Туре | S or NS | Offset        | Description                                                           |

|---------------------|------|---------|---------------|-----------------------------------------------------------------------|

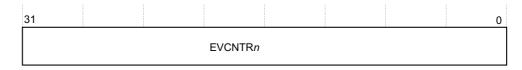

| PMEVCNTR0-2         | RW   | NS      | 0x3000-0x3008 | Performance Monitor Event Count Register on page 3-36                 |

| PMEVTYPE0-2         | RW   | NS      | 0x3400-0x3408 | Performance Monitor Event Type Select Register                        |

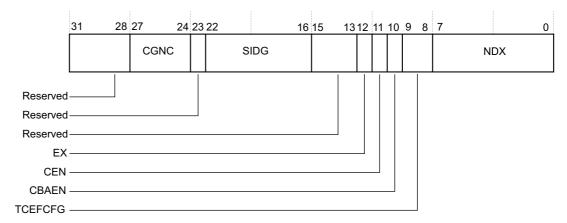

| PMCGCR <i>n</i>     | RW   | NS      | 0x3800        | Performance Monitor Counter Group Configuration Register on page 3-37 |

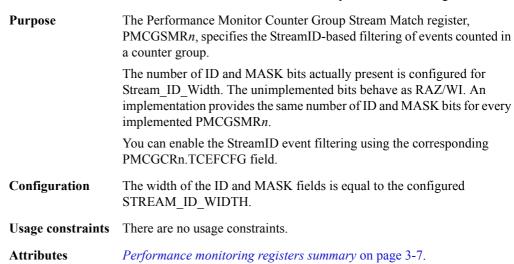

| PMCGSMRn            | RW   | NS      | 0x3A00        | Performance Monitor Counter Group Stream Match Register on page 3-38  |

| PMCNTENSET <i>n</i> | RW   | NS      | 0x3C00        | Performance Monitor Counter Enable Set and Clear registers            |

| PMCNTENCLR <i>n</i> | =    | NS      | 0x3C20        | -                                                                     |

| PMINTENSETn         | RW   | NS      | 0x3C40        | Performance Monitor Interrupt Enable Set and Clear registers          |

| PMINTENCLR <i>n</i> | -    |         | 0x3C60        | -                                                                     |

| PMOVSCLR <i>n</i>   | RW   | NS      | 0x3C80        | Performance Monitor Overflow Status Set and Clear registers           |

| PMOVSSET <i>n</i>   |      |         | 0x3CC0        | -                                                                     |

| PMCFGR              | RO   | NS      | 0x3E00        | Performance Monitor Configuration Register on page 3-39               |

| PMCR                | RW   | NS      | 0x3E04        | Performance Monitor Control Register on page 3-40                     |

| PMCEID0-1           | RO   | NS      | 0x3E20-0x3E24 | Performance Monitor Common Event ID Register                          |

| PMAUTHSTATUS        | RO   | NS      | 0x3FB8        | Performance Monitor Authentication Status register on page 3-41       |

| PMDEVTYPE           | RO   | NS      | 0x3FCC        | Performance Monitor Device Type Register on page 3-43                 |

#### 3.3.5 The MMU-400 security state determination address space summary

Table 3-5 shows the MMU-400 security state address space and its attributes.

Table 3-5 The MMU-400 security state determination address space summary

| Name            | Туре               | S or NS | Offset          | Description                                                         |

|-----------------|--------------------|---------|-----------------|---------------------------------------------------------------------|

| SMMU_SSDR0-1023 | UNK/SBOP/WI/RO/RWa | S       | 0x04000-0x04FFC | The MMU-400 Security State Determination Address Space on page 3-44 |

a. If the SSD table is not implemented, the bits are UNK/SBOP.

If the SSD table is implemented, the non-defined bits are UNK/SBOP/WI and the defined bits are RO/RW as defined.

#### 3.3.6 Peripheral and Component identification registers summary

Table 3-6 shows the Peripheral and Component identification registers in base offset order.

**Table 3-6 Peripheral and Component identification summary**

| Name          | Туре | S or NS | Offset  | Description                                      |

|---------------|------|---------|---------|--------------------------------------------------|

| Periph ID 4   | RO   | NS/S    | 0x0FFD0 | Peripheral Identification registers on page 3-46 |

| Periph ID 5   | RO   | NS/S    | 0x0FFD4 | -                                                |

| Periph ID 6   | RO   | NS/S    | 0x0FFD8 | -                                                |

| Periph ID 7   | RO   | NS/S    | 0x0FFDC | -                                                |

| Periph ID 0   | RO   | NS/S    | 0x0FFE0 | -                                                |

| Periph ID 1   | RO   | NS/S    | 0x0FFE4 | -                                                |

| Periph ID 2   | RO   | NS/S    | 0x0FFE8 | -                                                |

| Periph ID 3   | RO   | NS/S    | 0x0FFEC | -                                                |

| Component ID0 | RO   | NS/S    | 0x0FFF0 | Component Identification registers on page 3-46  |

| Component ID1 | RO   | NS/S    | 0x0FFF4 | -                                                |

| Component ID2 | RO   | NS/S    | 0x0FFF8 | -                                                |

| Component ID3 | RO   | NS/S    | 0x0FFFC | _                                                |

#### 3.3.7 Translation context bank registers summary

Table 3-7 shows the translation context bank address map in base offset order.

Table 3-7 Translation context bank address map summary

| Name                               | Type | Size | Offset          | Description                                                                                   |

|------------------------------------|------|------|-----------------|-----------------------------------------------------------------------------------------------|

| SMMU_CBn_SCTLR                     | RW   | 32   | 0x00000         | System Control Register on page 3-50                                                          |

| SMMU_CBn_TTBR0[63:0]               | RW   | 64   | 0x00020-0x00024 | Translation Table Base Register                                                               |

| SMMU_CBn_TTBCR                     | RW   | 32   | 0x00030         | Translation Table Base Control Register on page 3-53                                          |

| SMMU_CB <i>n</i> _FSR <sup>a</sup> | -    | -    | 0x00058         | Fault Status Register. See the ARM® System Memory Management Unit Architecture Specification. |

Table 3-7 Translation context bank address map summary (continued)

| Name                                      | Туре | Size | Offset          | Description                                                                                           |

|-------------------------------------------|------|------|-----------------|-------------------------------------------------------------------------------------------------------|

| SMMU_CB <i>n</i> _FSRRESTORE <sup>a</sup> | -    | -    | 0x0005C         | Fault Status Restore Register. See the ARM® System Memory Management Unit Architecture Specification. |

| SMMU_CBn_FAR[31:0]a                       | -    | -    | 0x00060         | Fault Address Register. See the ARM® System Memory                                                    |

| SMMU_CBn_FAR[63:32] <sup>a</sup>          | -    | -    | 0x00064         | Management Unit Architecture Specification.                                                           |

| SMMU_CBn_FSYNR0a                          | -    | -    | 0x00068         | Fault Syndrome Registers. See the ARM® System Memory Management Unit Architecture Specification.      |

| SMMU_CBn_PMXEVCNTRm                       | -    | -    | 0x00E00-0x00E08 | See Performance Monitoring registers on page 3-36.                                                    |

| SMMU_CBn_PMXEVTYPERm                      | -    | -    | 0x00E80-0x00E88 | See Performance Monitoring registers on page 3-36.                                                    |

| SMMU_CBn_PMCFGR                           | -    | -    | 0x00F00         | See Performance Monitoring registers on page 3-36.                                                    |

| SMMU_CBn_PMCR                             | -    | -    | 0x00F04         | See Performance Monitoring registers on page 3-36.                                                    |

| SMMU_CBn_PMCEID0-1                        | -    | -    | 0x00F20         | See Performance Monitoring registers on page 3-36.                                                    |

| SMMU_CBn_PMCNTENSET                       | -    | -    | 0x00F40         | See Performance Monitoring registers on page 3-36.                                                    |

| SMMU_CBn_PMCNTENCLR                       | -    | -    | 0x00F44         | See Performance Monitoring registers on page 3-36.                                                    |

| SMMU_CBn_PMINTENSET                       | -    | -    | 0x00F48         | See Performance Monitoring registers on page 3-36.                                                    |

| SMMU_CBn_PMINTENCLR                       | -    | -    | 0x00F4C         | See Performance Monitoring registers on page 3-36.                                                    |

| SMMU_CBn_PMOVSRCLR                        | -    | -    | 0x00F54         | See Performance Monitoring registers on page 3-36.                                                    |

| SMMU_CBn_PMOVSRSET                        | -    | -    | 0x00F50         | See Performance Monitoring registers on page 3-36.                                                    |

| SMMU_CBn_PMAUTHSTATUS                     | -    | -    | 0x00FB8         | See Performance Monitoring registers on page 3-36.                                                    |

a. Follow the same format as *Global Register Space*  $\theta$  on page 3-10 describes.

# 3.4 Global Register Space 0

The MMU-400 Global Register Space 0 provides high-level control of the MMU-400 resources and maps device transactions to translation context banks. It contains the following registers:

- Secure Configuration Register 0.

- Auxiliary Configuration Register on page 3-16.

- *Identification registers* on page 3-17.

- *Debug registers* on page 3-23.

- Secure Alias to Non-secure Configuration Register 0 on page 3-27.

There are no usage constraints.

- Secure Alias to Non-secure Auxiliary Configuration Register on page 3-27.

- Stream Match Registers on page 3-27.

- Stream to Context registers on page 3-29.

#### 3.4.1 Secure Configuration Register 0

The characteristics of the Secure Configuration Register 0 are:

The Secure Configuration Register, 0, SMMU\_SCR0, provides top-level control of the MMU-400 that is only accessible by Secure accesses.

——Note

The Non-secure register, SMMU\_CR0, does not provide full top-level control of the MMU-400 for Secure transactions. In implementations that support security extensions, some SMMU\_CR0 fields only apply to Non-secure transactions.

Configuration

Available in all MMU-400 configurations.

**Usage constraints**

**Attributes** See Table 3-1 on page 3-4.

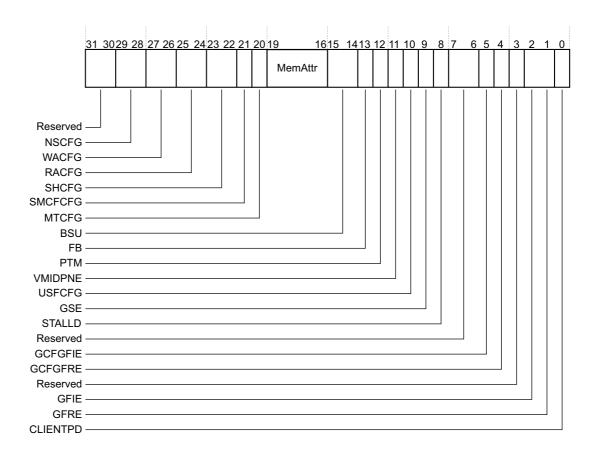

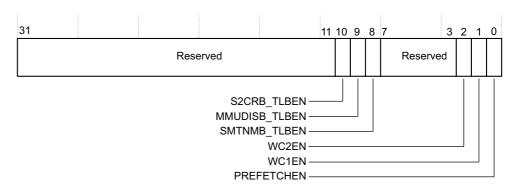

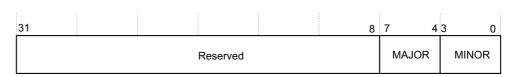

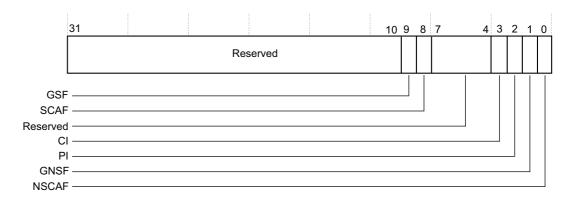

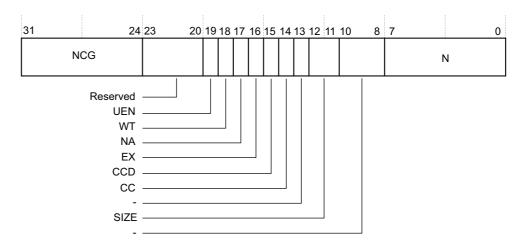

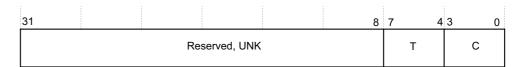

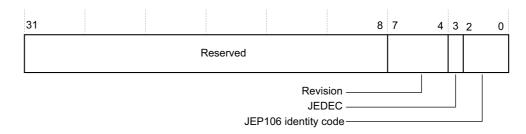

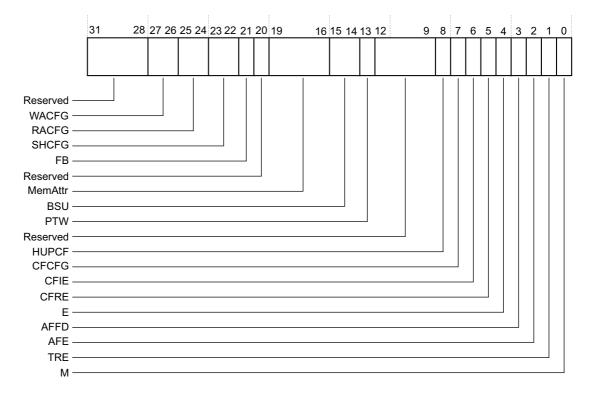

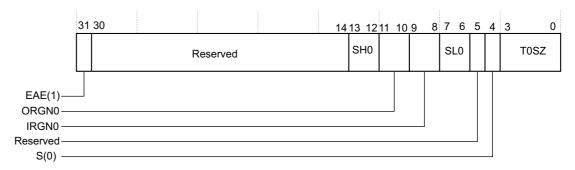

Figure 3-2 on page 3-11 shows the bit assignments.

Figure 3-2 Secure Configuration Register 0 bit assignments

Table 3-8 shows the bit assignments.

Table 3-8 Secure Configuration Register 0 bit assignments

| Bits    | Name     | Reset value | Description                                                                                                                                     |  |  |

|---------|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| [31:30] | Reserved | -           | Reserved.                                                                                                                                       |  |  |

| [29:28] | NSCFG    | -           | Non-secure Configuration.                                                                                                                       |  |  |

|         |          |             | The encodings of this field are:                                                                                                                |  |  |

|         |          |             | 0b00 Use APROTNS as presented with the transaction.                                                                                             |  |  |

|         |          |             | 0b01 Reserved.                                                                                                                                  |  |  |

|         |          |             | 0b10 Secure.                                                                                                                                    |  |  |

|         |          |             | 0b11 Non-secure.                                                                                                                                |  |  |

|         |          |             | Note                                                                                                                                            |  |  |

|         |          |             | • This field is only present in SMMU SCR0. In SMMU CR0, it is reserved.                                                                         |  |  |

|         |          |             | This field applies to the processing of Secure transactions that bypass the MMU-400 stream mapping process. This bypass condition can occur if: |  |  |

|         |          |             | <ul> <li>SMMU_SCR0.CLIENTPD has the value 1.</li> </ul>                                                                                         |  |  |

|         |          |             | <ul> <li>The transaction does not match in the stream mapping table and<br/>SMMU_SCR0.USFCFG has the value 0.</li> </ul>                        |  |  |

| [27:26] | WACFG    | -           | Write Allocate Configuration. Controls the allocation hint for write accesses.                                                                  |  |  |

|         |          |             | The encodings of this field are:                                                                                                                |  |  |

|         |          |             | 0b00 Use allocation attributes as presented with the transaction.                                                                               |  |  |

|         |          |             | 0b01 Reserved.                                                                                                                                  |  |  |

|         |          |             | 0b10 Allocate.                                                                                                                                  |  |  |

|         |          |             | 0b11 No allocate.                                                                                                                               |  |  |

|         |          |             | Note                                                                                                                                            |  |  |

|         |          |             | This field applies to transactions that bypass the MMU-400 stream mapping process. This bypass condition can occur if:                          |  |  |

|         |          |             | • SMMU_CR0.CLIENTPD has the value 1.                                                                                                            |  |  |

|         |          |             | The transaction does not match in the stream mapping table, and SMMU_CR0.USFCFG has the value 0.                                                |  |  |

| [25:24] | RACFG    | -           | Read Allocate Configuration. Controls the allocation hint for read accesses.                                                                    |  |  |

|         |          |             | The encodings of this field are:                                                                                                                |  |  |

|         |          |             | 0b00 Use allocation attributes as presented with the transaction. 0b01 Reserved.                                                                |  |  |

|         |          |             | 0b01 Reserved. 0b10 Allocate.                                                                                                                   |  |  |

|         |          |             | 0b11 No allocate.                                                                                                                               |  |  |

|         |          |             |                                                                                                                                                 |  |  |

|         |          |             | Note                                                                                                                                            |  |  |

|         |          |             | This field applies to transactions that bypass the MMU-400 stream mapping process. This bypass condition can occur if:                          |  |  |

|         |          |             | • SMMU_CR0.CLIENTPD has the value 1.                                                                                                            |  |  |

|         |          |             | • The transaction does not match in the stream mapping table, and SMMU_CR0.USFCFG has the value 0.                                              |  |  |

Table 3-8 Secure Configuration Register 0 bit assignments (continued)

| Bits    | Name    | Reset value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|---------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [23:22] | SHCFG   | -           | Shared Configuration. The encodings of this field are:  0b00                                                                                                                                                                                                                                                                                                                                                                                                                           |

| [21]    | SMCFCFG | -           | Stream Match Conflict Fault Configuration.  Controls the handling of client transactions that are identified as matching multiple entries in the stream mapping table. The possible values of this are:  Permit passes through.  Raise a stream match conflict fault.  Note  The MMU-400 treats this bit as RAO/WI.  The MMU-400 does not guarantee detection of all occurrences of the stream match conflict fault, see the System Memory Management Unit Architecture Specification. |

| [20]    | MTCFG   | 0           | Memory Type Configuration.  Use memory attributes as presented with the transaction.  Use MemAttr field for memory attributes.  Note  This field applies to the processing of Non-secure transactions that bypass the MMU stream mapping process. This bypass condition can occur if:  SMMU_CR0.CLIENTPD has the value 1.  The transaction does not match in the stream mapping table, and SMMU_CR0.USFCFG has the value 0.                                                            |

| [19:16] | MemAttr | -           | Memory Attributes. Memory attributes can be overlaid if SMMU_CR0.MTCFG has the value 1.                                                                                                                                                                                                                                                                                                                                                                                                |

Table 3-8 Secure Configuration Register 0 bit assignments (continued)

| Bits    | Name | Reset value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [15:14] | BSU  | -           | Barrier Shareability Upgrade. Upgrades the required shareability domain of barriers issued by client devices that are not mapped to a translation context, by setting the minimum shareability domain that is applied to any barrier.  The encodings of this field are: 0b00 No effect. 0b01 Inner shareable. 0b10 Outer shareable. 0b11 Full system.  ——Note  The MMU-400 supports the BSU only in ACE-Lite configurations. This field only applies to barriers that are received by the MMU-400. |