# CoreSight ETM -R7

Revision: r0p1

**Technical Reference Manual**

# CoreSight ETM-R7 Technical Reference Manual

Copyright © 2012 ARM. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

#### Change history

| Date              | Issue | Confidentiality  | Change                 |

|-------------------|-------|------------------|------------------------|

| 21 March 2012     | A     | Non-Confidential | First release for r0p0 |

| 28 September 2012 | В     | Non-Confidential | First release for r0p1 |

#### **Proprietary Notice**

Words and logos marked with ® or ™ are registered trademarks or trademarks of ARM in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

# **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

# **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

# Contents

# **CoreSight ETM-R7 Technical Reference Manual**

|            | Preta | ace                                   |      |

|------------|-------|---------------------------------------|------|

|            |       | About this book                       | v    |

|            |       | Feedback                              | ix   |

| Chapter 1  | Intro | oduction                              |      |

| •          | 1.1   | About the ETM-R7                      | 1-2  |

|            | 1.2   | Compliance                            | 1-4  |

|            | 1.3   | Features                              |      |

|            | 1.4   | Interfaces                            | 1-7  |

|            | 1.5   | Configurable options                  | 1-8  |

|            | 1.6   | Test features                         | 1-9  |

|            | 1.7   | Product documentation and design flow | 1-10 |

|            | 1.8   | Product revisions                     | 1-12 |

| Chapter 2  | Fund  | ctional Description                   |      |

| •          | 2.1   | About the functions                   | 2-2  |

|            | 2.2   | Interfaces                            |      |

|            | 2.3   | Clocking and resets                   |      |

|            | 2.4   | Operation                             |      |

| Chapter 3  | Proc  | grammers Model                        |      |

| •          | 3.1   | About the programmers model           | 3-2  |

|            | 3.2   | Modes of operation and execution      |      |

|            | 3.3   | Register summary                      |      |

|            | 3.4   | Register descriptions                 |      |

| Appendix A | Sian  | nal Descriptions                      |      |

| 1-1-2      | A.1   | Signal descriptions                   | A-2  |

|            |       |                                       |      |

| A.2 | Clocks and resets         | . A-4 |

|-----|---------------------------|-------|

|     | Processor trace interface |       |

| A.4 | APB interface             | . A-6 |

| A.5 | ATB interface             | . A-7 |

| A.6 | Miscellaneous signals     | . A-8 |

|     | Test interface            |       |

# Appendix B Revisions

# **Preface**

This preface introduces the *CoreSight ETM-R7 Technical Reference Manual*. It contains the following sections:

- About this book on page vi.

- Feedback on page ix.

# About this book

This book is for the CoreSight *Embedded Trace Macrocell* (ETM) for the Cortex<sup>™</sup>-R7 MPCore<sup>™</sup> processor, the ETM-R7.

#### **Product revision status**

The rnpn identifier indicates the revision status of the product described in this book, where:

**rn** Identifies the major revision of the product.

**pn** Identifies the minor revision or modification status of the product.

#### Intended audience

This book is written for:

- Designers of development tools providing support for ETM functionality. Implementation-specific behavior is described in this document. You can find complementary information in the *Embedded Trace Macrocell Architecture Specification* v4.

- Hardware and software engineers integrating the macrocell into an ASIC that includes a Cortex-R7 MPCore processor. You can find complementary information in the Cortex-R7 MPCore Integration Manual.

# Using this book

This book is organized into the following chapters:

# Chapter 1 Introduction

Read this for an introduction to the functionality of the macrocell.

# **Chapter 2** Functional Description

Read this for a description of the interfaces, operation, clocking and resets of the macrocell.

#### Chapter 3 Programmers Model

Read this for a description of the programmers model for the macrocell.

# Appendix A Signal Descriptions

Read this for a description of the signals used in the macrocell.

#### Appendix B Revisions

Read this for a description of the technical changes between released issues of this book.

#### Glossary

The ARM glossary is a list of terms used in ARM documentation, together with definitions for those terms. The ARM glossary does not contain terms that are industry standard unless the ARM meaning differs from the generally accepted meaning.

See ARM Glossary, http://infocenter.arm.com/help/topic/com.arm.doc.aeg0014-/index.html.

# Conventions

Conventions that this book can use are described in:

- Typographical conventions.

- Timing diagrams.

- Signals on page viii.

# **Typographical conventions**

The following table describes the typographical conventions:

| Style             | Purpose                                                                                                                                                                                                          |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| italic            | Introduces special terminology, denotes cross-references, and citations.                                                                                                                                         |  |

| bold              | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.                                                                            |  |

| monospace         | Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.                                                                                                      |  |

| <u>mono</u> space | Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.                                                                          |  |

| monospace italic  | Denotes arguments to monospace text where the argument is to be replaced by a specific value.                                                                                                                    |  |

| monospace bold    | Denotes language keywords when used outside example code.                                                                                                                                                        |  |

| <and></and>       | Enclose replaceable terms for assembler syntax where they appear in code or code fragments. For example: MRC p15, $\emptyset$ <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd>                         |  |

| SMALL CAPITALS    | Used in body text for a few terms that have specific technical meanings, that are defined in the <i>ARM Glossary</i> . For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE. |  |

# **Timing diagrams**

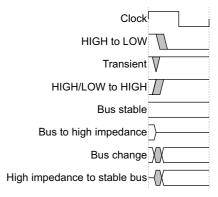

The figure named *Key to timing diagram conventions* explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

Key to timing diagram conventions

# **Signals**

The signal conventions are:

Signal level

The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals.

- LOW for active-LOW signals.

Lower-case n

At the start or end of a signal name denotes an active-LOW signal.

# Additional reading

This section lists publications by ARM and by third parties.

See Infocenter, http://infocenter.arm.com, for access to ARM documentation.

#### **ARM** publications

This book contains information that is specific to this product. See the following documents for other relevant information:

- Embedded Trace Macrocell Architecture Specification ETMv4 (ARM IHI 0064).

- Cortex-R7 MPCore Technical Reference Manual (ARM DDI 0458).

- Cortex-R7 MPCore Configuration and Sign-off Guide (ARM DII 0251).

- Cortex-R7 MPCore Integration Manual (ARM DIT 0030).

- CoreSight SoC Technical Reference Manual (ARM DDI 0480).

- CoreSight SoC User Guide (ARM DUI 0563).

- CoreSight Architecture Specification (ARM IHI 0029).

- CoreSight Technology System Design Guide (ARM DGI 0016).

- *ARM Reference Peripheral Specification* (ARM DDI 0062).

- *AMBA® 3 APB Protocol Specification* (ARM IHI 0024).

- *AMBA 3 ATB Protocol Specification* (ARM IHI 0032).

# **Feedback**

ARM welcomes feedback on this product and its documentation.

# Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

#### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- The title

- The number, ARM DDI 0459B.

- The page numbers to which your comments apply.

- A concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

Note

ARM tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader.

# Chapter 1 **Introduction**

This chapter introduces the CoreSight ETM-R7. It contains the following sections:

- *About the ETM-R7* on page 1-2.

- *Compliance* on page 1-4.

- Features on page 1-5.

- *Interfaces* on page 1-7.

- Configurable options on page 1-8.

- *Test features* on page 1-9.

- Product documentation and design flow on page 1-10.

- *Product revisions* on page 1-12.

# 1.1 About the ETM-R7

The ETM-R7 provides real-time instruction trace and data trace for the Cortex-R7 MPCore processor. The ETM-R7 generates information that trace software tools use to reconstruct the execution of all or part of a program.

For full reconstruction of program execution, the ETM-R7 is able to trace:

- All instructions, including condition code pass/fail.

- Load/store address and data values.

- Values of context-ID.

- Target addresses of taken direct and indirect branch operations.

- Exceptions.

- Changes in processor instruction set state.

- Entry to and return from Debug state when Halting Debug-mode is enabled.

- Cycle counts relating to instruction execution.

The ETM-R7 contains logic, known as resources, that enables you to control tracing by specifying the exact set of triggering and filtering conditions required for a particular application. Resources include address comparators and data value comparators, counters, and a sequencer.

The ETM-R7 is a CoreSight component. For more information about CoreSight, see the *CoreSight Architecture Specification* and *CoreSight Technology System Design Guide*. For more information about the ETM architecture, see the *Embedded Trace Macrocell Architecture Specification*.

# 1.1.1 The CoreSight debug environment

The ETM-R7 is designed for use with CoreSight, an extensible, system-wide debug and trace architecture from ARM. See the *CoreSight SoC User Guide* for more information about how to use the ETM-R7 in a full CoreSight system.

A software debugger provides the user interface to the ETM-R7. You can use this interface to:

- Configure ETM-R7 facilities such as filtering.

- Configure optional trace features such as cycle accurate tracing.

- Configure the other CoreSight components such as the *Trace Port Interface Unit* (TPIU).

- Access the processor debug and performance monitor units.

A CoreSight system can provide memory-mapped access from the processor to its own debug and trace components.

The ETM-R7 outputs its trace stream to the AMBA 3 *Advanced Trace Bus* (ATB) interfaces. The CoreSight infrastructure provides the following options:

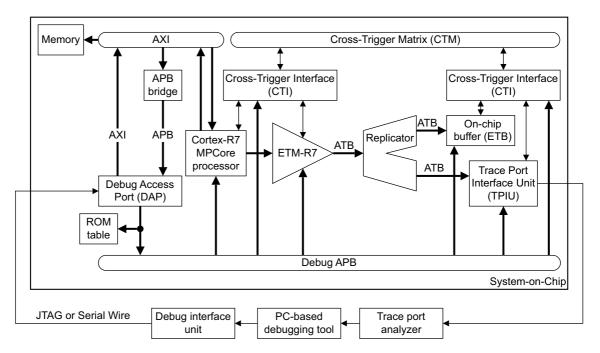

- Export the trace information through a trace port. An external *Trace Port Analyzer* (TPA) captures the trace information as Figure 1-1 on page 1-3 shows.

- Write the trace information directly to an on-chip *Embedded Trace Buffer* (ETB) or to system memory. You can read out the trace at low speed using a JTAG or Serial Wire interface when the trace capture is complete as Figure 1-1 on page 1-3 shows.

The debugger extracts the executed image from memory and the captured trace information from the TPA or ETB and decompresses the image to provide full disassembly, with symbols, of the code that was executed. The trace information generated by the ETM-R7 gives the debugger the capability to link this data back to the original high-level source code, to provide a visualization of how the code was executed on the Cortex-R7 MPCore processor.

Figure 1-1 shows how the ETM-R7 fits into a CoreSight debug environment to provide full trace capabilities in a single processor system. In this example, the external debug software configures the trace and debug components through the *Debug Access Port* (DAP). The ROM table contains a unique identification code for the SoC and the base addresses of the components connected to the debug APB. The trace stream from the ETM-R7 is replicated to provide on-chip storage using the CoreSight ETB or output off-chip using the TPIU. Cross-triggering operates through the *Cross Trigger Interface* (CTI) and *Cross Trigger Matrix* (CTM) components.

Figure 1-1 ETM-R7 system diagram

—— Note ———

In Figure 1-1, the arrows on the thick lines show the transaction direction on busses, from master to slave port. Each bus contains individual signals that go from master to slave and other signals that go from slave to master.

For a Cortex-R7 MPCore processor implementation with two processors, the following options are available:

- One ETM, statically shared between the processors.

- Two ETMs, one dedicated to each processor.

# 1.2 Compliance

The ETM-R7 complies with, or implements, the specifications described in:

- Trace macrocell.

- Advanced Microcontroller Bus Architecture.

This TRM complements architecture reference manuals, architecture specifications, protocol specifications, and relevant external standards. It does not duplicate information from these sources.

#### 1.2.1 Trace macrocell

The ETM-R7 implements the ETM architecture version 4. See the *Embedded Trace Macrocell Architecture Specification ETMv4*.

# 1.2.2 Advanced Microcontroller Bus Architecture

The ETM-R7 complies with the *Advanced Microcontroller Bus Architecture* (AMBA) 3 *Advanced Peripheral Bus* (APB) and *Advanced Trace Bus* (ATB) protocols. See the *AMBA 3 APB Protocol Specification* and *AMBA 3 ATB Protocol Specification*.

# 1.3 Features

ETM-R7 supports tracing of 32-bit ARM instructions, and 16-bit and 32-bit Thumb instructions.

See the Embedded Trace Macrocell Architecture Specification ETMv4 for information about:

- The trace protocol.

- The features of ETMv4.

- Controlling tracing using triggering and filtering resources.

- ETM sharing.

Table 1-1 shows the features of the ETM-R7 that are implementation-defined, in terms of either:

- The number of times the feature is implemented.

- The size of the feature.

Table 1-1 ETM-R7 features with implementation-defined number of instances or size

| Feature ETM-R7 value            |                                                                             | Notes                                                                         |  |

|---------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|

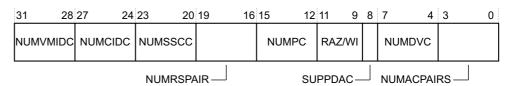

| Address comparators             | omparators 4 pairs See bits[3:0] of the <i>ID Register 4</i> on page        |                                                                               |  |

| Data value comparators          | 2                                                                           | See bits[7:4] of the <i>ID Register 4</i> on page 3-42                        |  |

| Context ID comparators          | 1                                                                           | See bits[27:24] of the ID Register 4 on page 3-42                             |  |

| Single-Shot comparator resource | 2, one for instruction, one for data                                        | See bits[2:0] of the Single-Shot Comparator Status Registers 0-1 on page 3-46 |  |

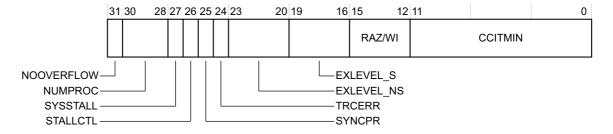

| Counters                        | 2                                                                           | See bits[30:28] of the <i>ID Register 5</i> on page 3-43                      |  |

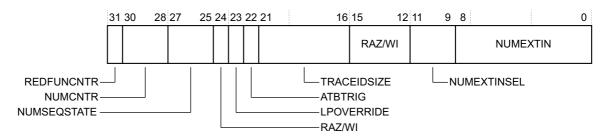

| Cycle count size                | 12                                                                          | See bits[28:25] of the ID Register 2 on page 3-40                             |  |

| Sequencer                       | One four-state sequencer. See bits[27:25] of the <i>III</i> 5 on page 3-43. |                                                                               |  |

| Processor comparator inputs     | Not implemented                                                             | See bits[15:12] of the ID Register 4 on page 3-42                             |  |

| External inputs                 | 64                                                                          | See bits[8:0] of the <i>ID Register 5</i> on page 3-43                        |  |

| External outputs                | 4                                                                           | See bits[3:0] of the Event Control 1 Register on page 3-18                    |  |

| External input selectors        | 4                                                                           | See bits[11:9] of the <i>ID Register 5</i> on page 3-43                       |  |

| Resource selector pairs         | 8                                                                           | See bits[19:16] of the <i>ID Register 4</i> on page 3-42                      |  |

| Instruction trace port size     | 32-bit                                                                      | -                                                                             |  |

| Data trace port size            | 64-bit                                                                      | -                                                                             |  |

| Instruction FIFOa               | 128 byte with 32-bit output                                                 | Uses ATB                                                                      |  |

| Data FIFO                       | 256 byte with 64-bit output                                                 | Uses ATB                                                                      |  |

| Claim tag bits                  | 4                                                                           | See bits[3:0] of the Claim Tag Set Register on page 3-56                      |  |

a. Instruction trace can be configured to take priority over data trace. See bit[10] of the TRCSTALLCTLR.

Table 1-2 shows the optional features of the ETM architecture that the ETM-R7 implements.

Table 1-2 ETM-R7 implementation of optional features

| Feature                                    | Implemented?        | Notes                                                                                           |  |

|--------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------|--|

| Configurable FIFO                          | No                  | -                                                                                               |  |

| Trace Start/Stop block                     | Yes                 | ViewInst Start/Stop Control Register on page 3-25                                               |  |

| Trace all branches option                  | Yes                 | See bit[5] of the <i>ID Register 0</i> on page 3-38                                             |  |

| Trace of conditional instructions          | Yes                 | See bits[13:12] and bit [6] of the <i>ID Register 0</i> on page 3-38, using the full CPSR value |  |

| Cycle counting in instruction trace        | Yes                 | See bit[7] of the <i>ID Register 0</i> on page 3-38                                             |  |

| Data trace supported                       | Yes                 | See bits[4:3] of the <i>ID Register 0</i> on page 3-38                                          |  |

| Data address comparison                    | Yes                 | See bit[8] of the ID Register 4 on page 3-42                                                    |  |

| OS Lock mechanism                          | Yes                 | OS Lock Access Register on page 3-47                                                            |  |

| Secure non-invasive debug                  | No                  | The Cortex-R7 MPCore processor does not implement the Security Extensions                       |  |

| Context ID tracing                         | Yes                 | See bits[9:5] of the <i>ID Register 2</i> on page 3-40                                          |  |

| Trace output                               | Yes                 | ATB                                                                                             |  |

| Timestamp size (48/64)                     | System configurable | See bits[28:24] of the <i>ID Register 0</i> on page 3-38                                        |  |

| Memory mapped access to ETM registers      | Yes                 | -                                                                                               |  |

| System instruction access to ETM registers | No                  | -                                                                                               |  |

| VMID comparator support                    | No                  | See bits[31:28] of the ID Register 4 on page 3-42                                               |  |

| ATB trigger support                        | Yes                 | See bit[22] of the <i>ID Register 5</i> on page 3-43                                            |  |

See Appendix A Signal Descriptions for information about the macrocell signals.

# 1.4 Interfaces

The ETM-R7 has the following main interfaces:

- Processor trace.

- ATB.

- Debug APB.

- Test.

Interfaces on page 2-4 describes the ETM-R7 interfaces in more detail.

# 1.5 Configurable options

The ETM-R7 includes the following configuration inputs:

- NUMPROC.

- SYSSTALL.

- TSSIZE.

See the Embedded Trace Macrocell Architecture Specification ETMv4 for more information.

# 1.6 Test features

The ETM-R7 provides the **DFTSE** input for testing the implemented device. See the *Cortex-R7 MPCore Integration Manual*.

See also *Integration Test Registers* on page 3-65 for information about the integration test registers, provided for testing the ETM-R7 integration in a SoC and performing CoreSight topology detection.

# 1.7 Product documentation and design flow

This section describes the ETM-R7 books, how they relate to the design flow, and the relevant architectural standards and protocols.

See Additional reading on page viii for more information about the books described in this section.

### 1.7.1 Documentation

The ETM-R7 documentation is as follows:

#### **Technical Reference Manual**

The *Technical Reference Manual* (TRM) describes the functionality and the effects of functional options on the behavior of the ETM-R7. It is required at all stages of the design flow. Some behavior described in the TRM might not be relevant because of the way that the ETM-R7 is implemented and integrated.

### Configuration and Sign-off Guide

The Cortex-R7 MPCore Configuration and Sign-off Guide (CSG) describes the processes to test and sign off the implemented design.

The ARM product deliverables include reference scripts and information about using them to implement your design. Reference methodology flows supplied by ARM are example reference implementations. Contact your EDA vendor for EDA tool support.

The CSG is a confidential book that is only available to licensees.

### **Integration Manual**

The *Cortex-R7 MPCore Integration Manual* (IM) describes how to integrate the ETM-R7 into a SoC. It includes a description of the pins that the integrator must tie off, to configure the macrocell for the required integration.

The IM is a confidential book that is only available to licensees.

# 1.7.2 Design flow

The ETM-R7 is delivered as synthesizable RTL. Before it can be used in a product, it must go through the following process:

#### **Implementation**

The implementer configures and synthesizes the RTL to produce a hard macrocell. This might include integrating RAMs into the design.

**Integration** The integrator connects the implemented design into a SoC. This includes connecting it to a memory system and peripherals.

#### **Programming**

This is the last process. The system programmer develops the software required to configure and initialize the ETM-R7, and tests the required application software.

Each stage of the process:

- Can be performed by a different party.

- Can include implementation and integration choices that affect the behavior and features

of the ETM-R7.

The operation of the final device depends on:

# **Build configuration**

The implementer chooses the options that affect how the RTL source files are pre-processed. These options usually include or exclude logic that affects one or more of the area, maximum frequency, and features of the resulting macrocell.

# **Configuration inputs**

The integrator configures some features of the ETM-R7 by tying inputs to specific values. These configurations affect the start-up behavior before any software configuration is made. They can also limit the options available to the software.

# Software configuration

The programmer configures the ETM-R7 by programming particular values into registers. This affects the behavior of the ETM-R7.

See Chapter 3 *Programmers Model* for information on the ETM-R7 registers.

—— Note ———

| This manual refers to implementation-defined features that are applicable to build configuration |

|--------------------------------------------------------------------------------------------------|

| options. Reference to a feature that is included means that the appropriate build and pin        |

| configuration options are selected. Reference to an enabled feature means one that has also been |

| configured by software.                                                                          |

|                                                                                                  |

# 1.8 Product revisions

This section describes the differences in functionality between product revisions:

**r0p0** First release.

**r0p0-r0p1** The following changes have been made in this release:

• ID register values changed to reflect product revision status:

ID Register 1 0x4100F401.

- Number of P0 keys increased from 32 to 64. See Table 3-40 on page 3-36.

- Various engineering errata fixes.

# Chapter 2 **Functional Description**

This chapter describes the interfaces, operation, clocking and resets of the ETM-R7. It contains the following sections:

- *About the functions* on page 2-2.

- *Interfaces* on page 2-4.

- *Clocking and resets* on page 2-6.

- *Operation* on page 2-7.

# 2.1 About the functions

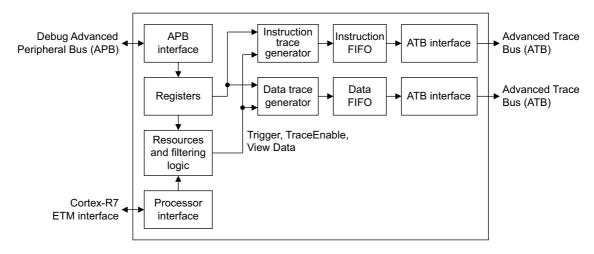

Figure 2-1 shows the main functional blocks of the ETM-R7.

Figure 2-1 ETM-R7 block diagram

#### 2.1.1 Processor interface

This block connects to the ETM-R7 interface. It tracks the execution and speculation information from the processor, decodes the control signals and passes on the information to the internal interfaces.

# 2.1.2 Instruction trace generator

This block generates the trace packets that are a compressed form of the execution information provided by the Cortex-R7 MPCore processor trace generation. The trace packets are then passed to the FIFO.

#### 2.1.3 Data trace generator

This block generates trace packets that are a compressed form of the external data transfer provided by the Cortex-R7 MPCore processor trace generation. The trace packets are then passed to the FIFO.

# 2.1.4 FIFO

This block buffers bursts of trace packets. Separate FIFOs are provided for instruction and data trace streams.

#### 2.1.5 Resources and filtering logic

These blocks contain various comparators and state machines that are programmed by trace software to trigger and filter the trace information. They start and stop trace generation, depending on the conditions that have been set.

#### 2.1.6 ATB interface

This block reads up to four or eight bytes of packet information from the FIFO and sends them over the ATB interface.

# 2.1.7 APB interface

This block implements the interface to the APB, that provides access to the programmable registers. It provides address decoding and pipelining of the address and data to and from the APB.

# 2.1.8 Global timestamping

| The ETM-R7 supports connection to a global timestamp source. This provides a 48 or 64 bit timestamp which can be used for coarse-grained profiling, and correlation of trace sources. ARM recommends that the timestamp counter is no slower than 10% of the processor clock. |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note  Decompression of data trace relies on the presence of a global timestamp count.                                                                                                                                                                                         |

# 2.2 Interfaces

The ETM-R7 has the following interfaces:

**ATB**

Two ATB interfaces, one 32 bits and one 64 bits wide, used for trace output from the macrocell. These interfaces have handshaking signals that indicate when trace data is valid and when the receiving component is ready to accept data. There are also signals to request and acknowledge a flush of the trace information and to indicate when a trigger condition has occurred.

See the AMBA 3 ATB Protocol Specification for more information about these interfaces.

**APB**

An APB interface that provides access to the programmable registers in the ETM-R7 and connects to the system Debug APB. This interface is used to configure the ETM-R7 for a trace session.

See the AMBA 3 APB Protocol Specification for more information about this interface.

#### **Processor trace**

The Cortex-R7 MPCore processor passes its execution information to the ETM-R7 over the processor trace interface. This interface provides both instruction and data execution history and contains address, data, and control information. The information carried on the control bus includes:

- The number of instructions executed in the same cycle.

- Changes in program flow.

- The current processor instruction state.

- The addresses of memory locations accessed by load and store instructions.

- The data values transferred by load and store instructions.

- The type, direction, and size of a transfer.

- Condition code information.

- Exception information.

- Current context ID.

There is also a context ID bus that indicates the current context ID value of the processor.

This interface also includes:

- The **ETMEVENT** bus. See *CPU PMU connectivity* on page 2-5.

- Wait for interrupt state information signals.

- A signal from the ETM to power up the interface.

# Miscellaneous

The ETM-R7 has other interface signals that:

- Configure the ETM. See *Configurable options* on page 1-8.

- Input and output external resource information that controls triggering and filtering of the trace stream.

- Control which core is enabled, as the trace source, on the processor trace interface of the ETM.

- Enable invasive and non-invasive debug.

Test

This interface contains the scan enable signal used in production testing of the ETM-R7.

# 2.2.1 CPU PMU connectivity

Table 2-1 shows the connection of the **ETMEVENT** inputs. These come from the CTI, the processor *Performance Monitoring Unit* (PMU), and ECC monitoring logic, if present..

**Table 2-1 ETMEVENT connections**

| Bits    | Description                          |

|---------|--------------------------------------|

| [63]    | ECC Fatal processor 1, if present    |

| [62]    | ECC Fatal processor 0, if present    |

| [61:60] | Spare                                |

| [59:4]  | Processor performance monitor events |

| [3:0]   | CTITRIGOUT                           |

For details of the mapping of processor performance monitor events, see the *Cortex-R7 MPCore Technical Reference Manual*.

\_\_\_\_\_Note \_\_\_\_\_

When a single ETM is shared between two processors, the PMU event pins are driven from the relevant processor, but the CTI connections for the ETM are always to CTI0, regardless of which processor is being traced.

The ETM output resources, **ETMEXTOUT**, are connected to the CTI and also as inputs to the processor PMU, as Table 2-2 shows.

Table 2-2 ETM EXTOUT connections to CTI and processor PMU

| ETM output   | CTI input    | PMU input   |

|--------------|--------------|-------------|

| ETMEXTOUT[0] | CTITRIGIN[2] | -           |

| ETMEXTOUT[1] | CTITRIGIN[3] | PMUEXTIN[0] |

| ETMEXTOUT[2] | CTITRIGIN[4] | PMUEXTIN[1] |

| ETMEXTOUT[3] | CTITRIGIN[5] | -           |

# 2.3 Clocking and resets

The following sections describe the ETM-R7 clocks and resets:

- ETM-R7 clock.

- ETM-R7 low power control.

- ETM-R7 reset.

- Access permissions and power domains.

#### 2.3.1 ETM-R7 clock

The ETM-R7 has one clock, **CLK**. This clock is synchronous to the **CLK** input of the Cortex-R7 MPCore processor.

# 2.3.2 ETM-R7 low power control

The ETM-R7 has outputs to indicate if the debugger expects power to be maintained, and also an output to indicate when tracing is inactive. The use of these signals is implementation specific.

The ETM can be configured to remain active even if the Cortex-R7 MPCore processor enters a low power state. See bit[23] of the *ID Register 5* on page 3-43.

#### 2.3.3 ETM-R7 reset

| The ETM-R7 has a single reset, <b>nRESET</b> , and must only be reset by a debug reset event. |

|-----------------------------------------------------------------------------------------------|

| Note                                                                                          |

| The programming state must be reconfigured after a reset.                                     |

|                                                                                               |

# 2.3.4 Access permissions and power domains

To determine the access permissions as described in the ETM Architecture v4, the ETM implements a SinglePower domain. The ETM (debug) power domain is typically separate from the processor power domain.

# 2.4 Operation

This section describes the implementation-defined features of the ETM-R7 macrocell. It contains the following sections:

- *Implementation-defined registers*.

- Precise TraceEnable events.

- Parallel instruction execution.

- Context ID tracing on page 2-8.

- *Trace and comparator features* on page 2-8.

- Data address range filtering on page 2-8.

- Interaction with the PMU on page 2-8.

- Packet formats on page 2-9.

- *Resource selection* on page 2-9.

- Trace flush behavior on page 2-10.

- Low power state behavior on page 2-10.

- *Cycle counter* on page 2-10.

- *Micro-architectural exceptions* on page 2-10.

- *Synchronization* on page 2-11.

See the *Embedded Trace Macrocell Architecture Specification ETMv4* for more information about the operation of the ETM-R7.

# 2.4.1 Implementation-defined registers

There are two groups of ETM registers:

- Registers that are completely defined by the *Embedded Trace Macrocell Architecture Specification ETMv4*.

- registers that are at least partly implementation-defined.

See Chapter 3 *Programmers Model* for more information about the ETM registers.

# 2.4.2 Precise TraceEnable events

The *Embedded Trace Macrocell Architecture Specification ETMv4* states that **ViewInst** and **ViewData** are imprecise under certain conditions, with some implementation-defined exceptions. The only condition which ensures that **ViewInst** and **ViewData** are precise is that the enabling event condition is TRUE.

# 2.4.3 Parallel instruction execution

The Cortex-R7 MPCore processor supports parallel instruction execution. This means the macrocell is capable of tracing two instructions per cycle.

Although the **ViewInst** is evaluated for each instruction as required, the macrocell does not trace one instruction without the other. In other words, if one instruction is specified to be traced, the instruction it is paired with is always traced as well. If **ViewData** is active, any data associated with the paired instruction is also traced. If **ViewData** selects only one transfer of a multiple load or store, both transfers which are issued by the core as a 64-bit transfer are traced.

### 2.4.4 Context ID tracing

The ETM-R7 detects updates to the Context ID register and, when the context change sequence is completed with an ISB or exception, traces the appropriate number of bytes as a context ID packet as part of the instruction trace stream. Coprocessor register transfers never generate data trace.

# 2.4.5 Trace and comparator features

In ETM Architecture v4, it is implementation-defined whether an ETM supports a number of trace and comparator features. This section specifies the implementation of these features on the ETM-R7:

- Trace features.

- Comparator features.

#### **Trace features**

The ETM-R7 implements all of the ETMv4 trace features. This means it supports:

- Data value and data address tracing.

- Data suppression.

- Cycle-accurate tracing.

- · Timestamping.

See the *Embedded Trace Macrocell Architecture Specification ETMv4* for descriptions of these features.

### Comparator features

The ETM-R7 implements data address comparison. See the *Embedded Trace Macrocell Architecture Specification ETMv4* for a description of data address comparison.

#### 2.4.6 Data address range filtering

When data address range filtering is used to include both loads and stores, or no data address include ranges are selected, an address range is set to exclude loads or stores, but not both. When a SWP matches for both the include and exclude ranges, both the load and store transfers are traced.

#### 2.4.7 Interaction with the PMU

The Cortex-R7 MPCore processor includes a *Performance Monitoring Unit* (PMU) that enables events, such as cache misses and instructions executed, to be counted over a period of time. The macrocell can still use these events by means of the extended external input facility. Each bit in the **ETMEVENT[63:0]** input is mapped to the corresponding extended external input. See the *Cortex-R7 MPCore Technical Reference Manual* for details of the mapping of PMU events to bits in this bus.

Bits[3:0] of **ETMEVENT** are reserved for cross trigger connections. PMU event signals use bits[50:4], ECC signals use bits[63:62] if implemented, and the remainder are free for system specific use if implemented. Any four of the external inputs can be selected for further use in the resource logic.

PMU event number 8, Executed instruction count, is presented by the core as a 6-bit vector which the ETM is not able to count. These are ORed together for connection to the ETM and the ETM is not able to count instruction execution directly.

The Cortex-R7 PMU can count two of the ETM external outputs as additional events. These events are not provided back to the macrocell as extended external inputs.

These facilities enable additional filtering of the system events using ETM resources, such as instruction address ranges or the start/stop resource, before they are passed back to the PMU for counting. To do this:

- Configure the ETM external input selectors to the system events you want to count.

- Configure the required ETM filtering resource as appropriate.

- Configure the ETM external outputs and the required ETM filtering resource.

- Select the ETM external outputs as the events to be counted in the Cortex-R7 PMU.

#### 2.4.8 Packet formats

See the *Embedded Trace Macrocell Architecture Specification ETMv4* for descriptions of the trace packet formats generated by the ETM-R7.

#### 2.4.9 Resource selection

The ETM-R7 uses event selectors to control the following resources:

- Trace events (triggers and markers in the trace stream).

- Timestamp event.

- ViewInst event.

- ViewData event.

- Counter control.

- Sequencer state transitions.

Each event selector is configured to be sensitive to a resource selector pair, and one resource selector pair can be used to control more than one event selector.

The ETM provides one fixed resource selector pair, with static values of 0 and 1, and seven configurable selector pairs. A resource selector pair provides a bitfield OR selector for resources in two different groups, with each group and a configurable boolean combination provided.

Table 2-3 shows the resources which can be selected.

Table 2-3 Resource selection

| Select | Resource                        |

|--------|---------------------------------|

| 0-3    | External input selector 0-3     |

| 0-1    | Counter at zero 0-1             |

| 4-7    | Sequencer states 0-3            |

| 0-1    | Single-Shot comparator 0-1      |

| 0-7    | Single address comparator 0-7   |

| 0-3    | Address range comparator 0-3    |

| 0      | Context ID comparator 0         |

|        | 0-3<br>0-1<br>4-7<br>0-1<br>0-7 |

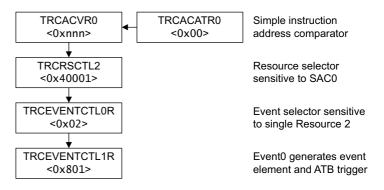

As an example, Figure 2-2 on page 2-10 shows the steps necessary to use a single address comparator to generate a trigger event and an ATB trigger. This example uses the first single resource selector which can be user-configured.

Figure 2-2 Trigger event resource selection

#### 2.4.10 Trace flush behavior

Events which have been observed by the ETM can be confirmed to have reached the trace bus output with the use of the ATB flush protocol. Both ATB ports must be flushed if all trace is required. The ETM internally flushes instruction and data trace together whenever either flush request is seen but does not guarantee that the trace data has drained from the ETM. When the processor enters a low power state, this also causes all trace to be output from the ETM.

If the processor enters a low-power state while an ATB flush request is in progress, the flush is acknowledged only after all instructions presented to the ETM have been traced.

#### 2.4.11 Low power state behavior

When the processor enters a low power state, the ETM resources become inactive after a delay which allows the last instruction executed to trigger a comparator, update the counter or sequencer, and then cause an event packet to be inserted in the trace stream. This event packet is presented on the trace bus before the ETM itself enters a low power state. If an event packet is generated for a different reason, it is not guaranteed to be output before the ETM enters a low power state, but is traced when the processor leaves the low power state, if the ETM logic is not reset before this can occur.

This low power behavior can be disabled, in which case the ETM resources remain active.

#### 2.4.12 Cycle counter

The cycle counter is a 12 bit counter. It does not count when non-invasive debug is disabled, or when the processor is in a low power state.

# 2.4.13 Micro-architectural exceptions

These exception encodings are intended to permit trace decompression rather than to trace the underlying cause of instruction replay.

The ETM indicates exceptions for the following micro-architectural behaviors using the following TYPE encodings:

**b10000** Execution replay resulting from incorrect decode prediction.

**b10001** Execution replay resulting from ECC error detection.

# 2.4.14 Synchronization

All sources of synchronization are combined before being used to generate synchronization in both trace streams, provided that data trace is active.

Periodic synchronization of the data trace stream is aligned with synchronization in the instruction stream. If the ETM is configured to trace only events in the data stream, it is also necessary to configure the instruction trace stream to contain sufficient elements to permit the required data trace stream synchronization.

# Chapter 3 **Programmers Model**

This chapter describes the programmers model. It contains the following sections:

- *About the programmers model* on page 3-2.

- *Modes of operation and execution* on page 3-3.

- *Register summary* on page 3-5.

- Register descriptions on page 3-13.

# 3.1 About the programmers model

This chapter describes the mechanisms for programming the registers used to set up the trace and triggering facilities of the macrocell. The programmers model enables you to use the ETM registers to control the macrocell.

# 3.2 Modes of operation and execution

The following sections describes how to control ETM programming.

# 3.2.1 Controlling ETM programming

When programming the ETM registers, you must enable all the changes at the same time. For example, if the counter is reprogrammed, it might start to count based on incorrect events, before the trigger condition has been correctly set up.

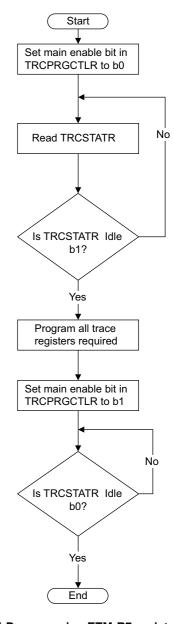

You must use the ETM main enable in the TRCPRGCTLR to disable all trace operations during programming. See *Programming Control Register* on page 3-13. Figure 3-1 shows the procedure to follow.

Figure 3-1 Programming ETM-R7 registers

The Cortex-R7 MPCore processor does not have to be in the debug state while you program the ETM registers.

# 3.2.2 Programming and reading ETM registers

You program and read the ETM registers using the Debug APB interface. This provides a direct method of programming the ETM-R7.

# 3.3 Register summary

This section summarizes the ETM registers. For full descriptions of the ETM registers, see:

- Register descriptions on page 3-13, for the implementation-defined registers.

- the Embedded Trace Macrocell Architecture Specification ETMv4, for the other registers.

Table 3-1 shows the ETM registers in numerical order and describes each register.

The macrocell registers are listed by functional group in *Functional grouping of registers* on page 3-8. The functional group register tables include additional information about each register:

- The register access type. This is read-only, write-only or read and write.

- The base offset address of the register. The base address of a register is always four times its register number.

- Additional information about the implementation of the register, where appropriate.

\_\_\_\_ Note \_\_\_\_\_

- Registers not listed here are not implemented. Reading a non-implemented register address returns 0. Writing to a non-implemented register address has no effect.

- In Table 3-1:

- The Reset value column shows the value of the register immediately after an ETM reset. For read-only registers, every read of the register returns this value.

- Access type is described as follows:

**RW** Read and write.

**RO** Read only.

**WO** Write only.

All ETM registers are 32 bits wide.

Table 3-1 ETM-R7 register summary

| Register<br>number | Base<br>offset | Name          | Туре | Reset<br>value | Description                                    |

|--------------------|----------------|---------------|------|----------------|------------------------------------------------|

| 1                  | 0x004          | TRCPRGCTLR    | RW   | 0x00000000     | Programming Control Register on page 3-13      |

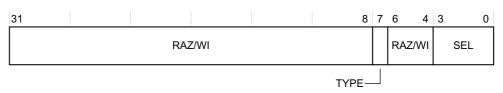

| 2                  | 0x008          | TRCPROCSELR   | RW   | 0x00000000     | Processor Select Control Register on page 3-13 |

| 3                  | 0x00C          | TRCSTATR      | RO   | -              | Status Register on page 3-14                   |

| 4                  | 0x010          | TRCCONFIGR    | RW   | -              | Trace Configuration Register on page 3-15      |

| 6                  | 0x018          | TRCAUXCTLR    | RW   | 0x00000000     | Auxiliary Control Register on page 3-16        |

| 8                  | 0x020          | TRCEVENTCTL0R | RW   | -              | Event Control 0 Register on page 3-17          |

| 9                  | 0x024          | TRCEVENTCTL1R | RW   | -              | Event Control 1 Register on page 3-18          |

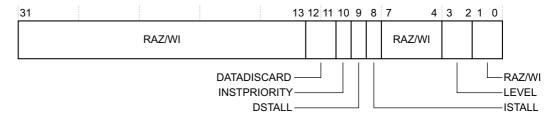

| 11                 | 0x02C          | TRCSTALLCTLR  | RW   | -              | Stall Control Register on page 3-19            |

| 12                 | 0x030          | TRCTSCTLR     | RW   | -              | Global Timestamp Control Register on page 3-20 |

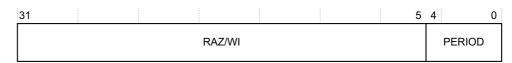

| 13                 | 0x034          | TRCSYNCPR     | RW   | -              | Synchronization Period Register on page 3-21   |

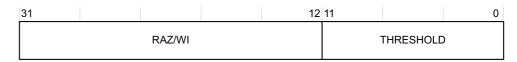

| 14                 | 0x038          | TRCCCCTLR     | RW   | -              | Cycle Count Control Register on page 3-22      |

Table 3-1 ETM-R7 register summary (continued)

| Register<br>number | Base<br>offset | Name         | Туре | Reset<br>value | Description                                                                 |

|--------------------|----------------|--------------|------|----------------|-----------------------------------------------------------------------------|

| 15                 | 0x03C          | TRCBBCTLR    | RW   | -              | Branch Broadcast Control Register on page 3-22                              |

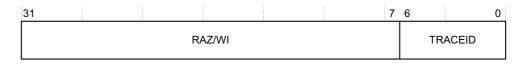

| 16                 | 0x040          | TRCTRACEIDR  | RW   | -              | Trace ID Register on page 3-23                                              |

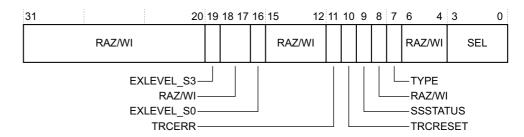

| 32                 | 0x080          | TRCVICTLR    | RW   | -              | ViewInst Main Control Register on page 3-24                                 |

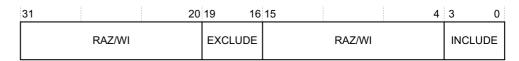

| 33                 | 0x084          | TRCVIIECTLR  | RW   | -              | ViewInst Include/Exclude Control Register on page 3-25                      |

| 34                 | 0x088          | TRCVISSCTLR  | RW   | -              | ViewInst Start/Stop Control Register on page 3-25                           |

| 40                 | 0x0A0          | TRCVDCTLR    | RW   | -              | ViewData Main Control Register on page 3-26                                 |

| 41                 | 0x0A4          | TRCVDSACCTLR | RW   | -              | ViewData Include/Exclude Single Address Comparator<br>Register on page 3-27 |

| 42                 | 0x0A8          | TRCVDARCCTLR | RW   | -              | ViewData Include/Exclude Address Range Comparator<br>Register on page 3-28  |

| 64-66              | 0x100-0x108    | TRCSEQEVRn   | RW   | -              | Sequencer State Transition Control Registers 0-2 on page 3-29               |

| 70                 | 0x118          | TRCSEQRSTEVR | RW   | -              | Sequencer Reset Control Register on page 3-29                               |

| 71                 | 0x11C          | TRCSEQSTR    | RW   | -              | Sequencer State Register on page 3-30                                       |

| 72                 | 0x120          | TRCEXTINSELR | RW   | -              | External Input Select Register on page 3-31                                 |

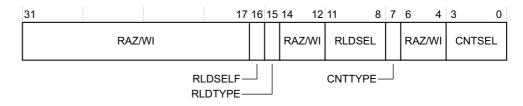

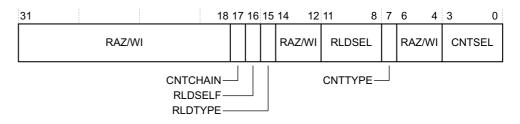

| 80-81              | 0x140-0x144    | TRCCNTRLDVRn | RW   | -              | Counter Reload Value Registers 0-1 on page 3-32                             |

| 84                 | 0x150          | TRCCNTCTLR0  | RW   | -              | Counter Control Register 0 on page 3-32                                     |

| 85                 | 0x154          | TRCCNTCTLR1  | RW   | -              | Counter Control Register 1 on page 3-33                                     |

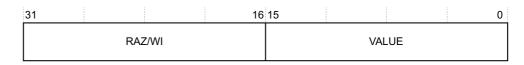

| 88-89              | 0x160-0x164    | TRCCNTVRn    | RW   | -              | Counter Value Registers 0-1 on page 3-34                                    |

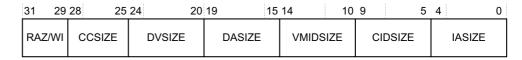

| 96                 | 0x180          | TRCIDR8      | RO   | 0x00000040     | ID Register 8-13 on page 3-35                                               |

| 97                 | 0x184          | TRCIDR9      | RO   | 0x00000040     | -                                                                           |

| 98                 | 0x188          | TRCIDR10     | RO   | 0x00000040     | -                                                                           |

| 99                 | 0x18C          | TRCIDR11     | RO   | 0x00000011     | -                                                                           |

| 100                | 0x190          | TRCIDR12     | RO   | 0x00000020     | -                                                                           |

| 101                | 0x194          | TRCIDR13     | RO   | 0x00000000     | _                                                                           |

| 112                | 0x1C0          | TRCIMSPEC0   | RW   | 0x00000000     | Implementation Specific Register 0 on page 3-37                             |

| 120                | 0x1E0          | TRCIDR0      | RO   | 0xXX001EFF     | ID Register 0 on page 3-38                                                  |

| 121                | 0x1E4          | TRCIDR1      | RO   | 0x4100F401     | ID Register 1 on page 3-39                                                  |

| 122                | 0x1E8          | TRCIDR2      | RO   | 0x00420084     | ID Register 2 on page 3-40                                                  |

| 123                | 0x1EC          | TRCIDR3      | RO   | 0xXX090004     | ID Register 3 on page 3-41                                                  |

| 124                | 0x1F0          | TRCIDR4      | RO   | 0x01270124     | ID Register 4 on page 3-42                                                  |

| 125                | 0x1F4          | TRCIDR5      | RO   | 0x28C70840     | ID Register 5 on page 3-43                                                  |

| 130-140            | 0x208-0x240    | TRCRSCTLRn   | RW   | -              | Resource Selection Registers 2-16 on page 3-44                              |

Table 3-1 ETM-R7 register summary (continued)

| 160-161 | 0x280-0x284 |               |    | value      |                                                           |

|---------|-------------|---------------|----|------------|-----------------------------------------------------------|

|         |             | TRCSSCCRn     | RW | -          | Single-Shot Comparator Control Registers 0-1 on page 3-45 |

| 168-169 | 0x2A0-0x2A4 | TRCSSCSRn     | RW | -          | Single-Shot Comparator Status Registers 0-1 on page 3-46  |

| 192     | 0x300       | TRCOSLAR      | WO | -          | OS Lock Access Register on page 3-47                      |

| 193     | 0x304       | TRCOSLSR      | RO | -          | OS Lock Status Register on page 3-48                      |

| 196     | 0x310       | TRCPDCR       | RW | 0×00000000 | Power Down Control Register on page 3-49                  |

| 197     | 0x314       | TRCPDSR       | RO | 0x00000023 | Power Down Status Register on page 3-49                   |

| 256-271 | 0x400-0x43C | TRCACVRn      | RW | -          | Address Comparator Value Registers 0-7 on page 3-50       |

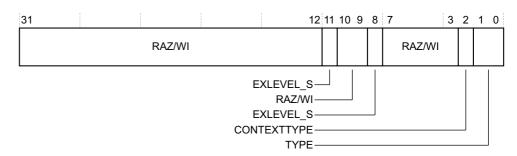

| 288-303 | 0x480-0x4BC | TRCACATRn     | RW | -          | Address Comparator Access Type Registers 0-7 on page 3-51 |

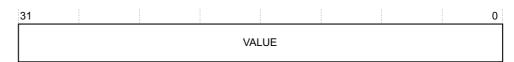

| 320-321 | 0x500-0x504 | TRCDVCVRn     | RW | -          | Data Value Comparator Value Registers 0-1 on page 3-53    |

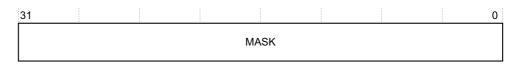

| 352-359 | 0x580-0x59C | TRCDVCMRn     | RW | -          | Data Value Comparator Mask Registers 0-1 on page 3-53     |

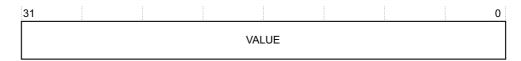

| 384     | 0×600       | TRCCIDCVR0    | RW | -          | Context ID Comparator Value Register 0 on page 3-54       |

| 951     | 0xEDC       | TRCITMISCOUTR | RW | -          | Integration Miscellaneous Outputs Register on page 3-66   |

| 952     | 0xEE0       | TRCITMISCINR  | RO | -          | Integration Miscellaneous Inputs Register on page 3-67    |

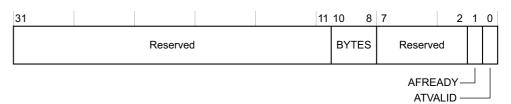

| 953     | 0xEE4       | TRCITATBIDR   | RW | -          | Integration ATB Identification Register on page 3-68      |

| 954     | 0xEE8       | TRCIRDDATAR   | RW | -          | Integration Data ATB Data Register on page 3-69           |

| 955     | 0xEEC       | TRCITIDATAR   | RW | -          | Integration Instruction ATB Data Register on page 3-69    |

| 956     | 0xEF0       | TRCITDATBINR  | RO | -          | Integration Data ATB In Register on page 3-70             |

| 957     | 0xEF4       | TRCITIATBINR  | RO | -          | Integration Instruction ATB In Register on page 3-71      |

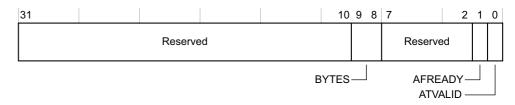

| 958     | 0xEF8       | TRCITDATBOUTR | RW | -          | Integration Data ATB Out Register on page 3-71            |

| 959     | 0xEFC       | TRCITIATBOUTR | RW | -          | Integration Instruction ATB Out Register on page 3-72     |

| 960     | 0xF00       | TRCITCTRL     | RW | 0×00000000 | Integration Mode Control Register on page 3-55            |

| 1000    | 0xFA0       | TRCCLAIMSET   | RW | 0×00000000 | Claim Tag Set Register on page 3-56                       |

| 1001    | 0xFA4       | TRCCLAIMCLR   | RW | 0×00000000 | Claim Tag Clear Register on page 3-56                     |

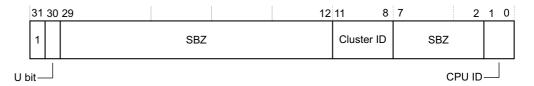

| 1002    | 0xFA8       | TRCDEVAFF0    | RO | -          | Device Affinity Register on page 3-57                     |

| 1004    | 0xFB0       | TRCLAR        | WO | -          | Software Lock Access Register on page 3-58                |

| 1005    | 0xFB4       | TRCLSR        | RO | -          | Software Lock Status Register on page 3-58                |

| 1006    | 0xFB8       | TRCAUTHSTATUS | RO |            | Authentication Status Register on page 3-59               |

| 1007    | 0xFBC       | TRCDEVARCH    | RO | 0x47704A17 | Device Architecture Register on page 3-60                 |

| 1010    | 0xFC8       | TRCDEVID      | RO | 0×00000000 | Device ID Register on page 3-61                           |

Table 3-1 ETM-R7 register summary (continued)

| Register<br>number | Base<br>offset | Name       | Туре | Reset<br>value | Description                                      |

|--------------------|----------------|------------|------|----------------|--------------------------------------------------|

| 1011               | 0xFCC          | TRCDEVTYPE | RO   | 0x00000013     | Device Type Register on page 3-61                |

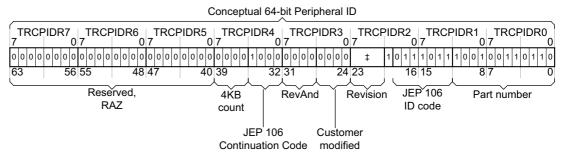

| 1012-1019          | 0xFD0-0xFEC    | TRCPIDRn   | RO   | -              | Peripheral Identification Registers on page 3-62 |

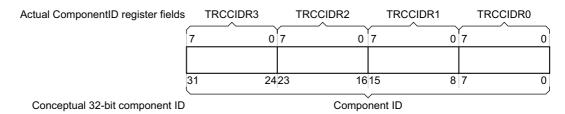

| 1020-1023          | 0xFF0-0xFFC    | TRCCIDRn   | RO   | -              | Component Identification Registers on page 3-64  |

#### 3.3.1 Functional grouping of registers

This section shows the macrocell registers by functional group, as follows:

- General control and ID registers.

- *Trace filtering control registers* on page 3-9.

- *Derived resource registers* on page 3-9.

- *Implementation-specific and identification registers* on page 3-10.

- Resource selection registers on page 3-10.

- Single-Shot comparator registers on page 3-10.

- OS lock and power control registers on page 3-11.

- *Comparator registers* on page 3-11.

- *Integration Test registers* on page 3-11.

- *CoreSight management registers* on page 3-12.

These functional groups include all of the registers.

# General control and ID registers

Table 3-2 shows the general control and ID registers in numerical order.

Table 3-2 General control and ID registers

| Register<br>number | Name          | Base<br>offset | Description                                    |

|--------------------|---------------|----------------|------------------------------------------------|

| 1                  | TRCPRGCTLR    | 0x004          | Programming Control Register on page 3-13      |

| 2                  | TRCPROCSELR   | 0x008          | Processor Select Control Register on page 3-13 |

| 3                  | TRCSTATR      | 0x00C          | Status Register on page 3-14                   |

| 4                  | TRCCONFIGR    | 0x010          | Trace Configuration Register on page 3-15      |

| 6                  | TRCAUXCTLR    | 0x018          | Auxiliary Control Register on page 3-16        |

| 8                  | TRCEVENTCTL0R | 0x020          | Event Control 0 Register on page 3-17          |

| 9                  | TRCEVENTCTL1R | 0x024          | Event Control 1 Register on page 3-18          |

| 11                 | TRCSTALLCTLR  | 0x02C          | Stall Control Register on page 3-19            |

| 12                 | TRCTSCTLR     | 0x030          | Global Timestamp Control Register on page 3-20 |

| 13                 | TRCSYNCPR     | 0x034          | Synchronization Period Register on page 3-21   |

Table 3-2 General control and ID registers (continued)

| Register<br>number | Name        | Base<br>offset | Description                                    |

|--------------------|-------------|----------------|------------------------------------------------|

| 14                 | TRCCCCTLR   | 0x038          | Cycle Count Control Register on page 3-22      |

| 15                 | TRCBBCTLR   | 0x03C          | Branch Broadcast Control Register on page 3-22 |

| 16                 | TRCTRACEIDR | 0x040          | Trace ID Register on page 3-23                 |

# Trace filtering control registers

Table 3-3 shows the trace filtering control registers in numerical order.

Table 3-3 Trace filtering control registers

| Register<br>number | Name         | Base<br>offset | Description                                                              |

|--------------------|--------------|----------------|--------------------------------------------------------------------------|

| 32                 | TRCVICTLR    | 0x080          | ViewInst Main Control Register on page 3-24                              |

| 33                 | TRCVIIECTLR  | 0x084          | ViewInst Include/Exclude Control Register on page 3-25                   |

| 34                 | TRCVISSCTLR  | 0x088          | ViewInst Start/Stop Control Register on page 3-25                        |

| 40                 | TRCVDCTLR    | 0x0A0          | ViewData Main Control Register on page 3-26                              |

| 41                 | TRCVDSACCTLR | 0x0A4          | ViewData Include/Exclude Single Address Comparator Register on page 3-27 |

| 42                 | TRCVDARCCTLR | 0x0A8          | ViewData Include/Exclude Address Range Comparator Register on page 3-28  |

# **Derived resource registers**

Table 3-4 shows the derived resource registers in numerical order. These registers control:

- The two counters, and associated events.

- The sequencer, and associated state change events.

- Trigger events.

- EXTOUT (External Output) events.

- Extended External Input selection.

**Table 3-4 Derived resource registers**

| Register<br>number | Name         | Base offset | Description                                                   |

|--------------------|--------------|-------------|---------------------------------------------------------------|

| 64-66              | TRCSEQVRn    | 0x100-0x108 | Sequencer State Transition Control Registers 0-2 on page 3-29 |

| 70                 | TRCSEQRSTEVR | 0x118       | Sequencer Reset Control Register on page 3-29                 |

| 71                 | TRCSEQSTR    | 0x11C       | Sequencer State Register on page 3-30                         |

| 72                 | TRCEXTINSELR | 0x120       | External Input Select Register on page 3-31                   |

| 80-81              | TRCCNTRLDVRn | 0x140-0x144 | Counter Reload Value Registers 0-1 on page 3-32               |

| 84                 | TRCCNTCTLR0  | 0x150       | Counter Control Register 0 on page 3-32                       |

| 85                 | TRCCNTCTLR1  | 0x154       | Counter Control Register 1 on page 3-33                       |

| 88-89              | TRCCNTVRn    | 0x160-0x164 | Counter Value Registers 0-1 on page 3-34                      |

# Implementation-specific and identification registers

Table 3-5 shows the implementation-specific and identification registers in numerical order.

Table 3-5 Implementation-specific and identification registers

| Register<br>number | Name       | Base<br>offset | Description                                     |

|--------------------|------------|----------------|-------------------------------------------------|

| 96                 | TRCIDR8    | 0x180          | ID Register 8-13 on page 3-35                   |

| 97                 | TRCIDR9    | 0x184          | -                                               |

| 98                 | TRCIDR10   | 0x188          | _                                               |

| 99                 | TRCIDR11   | 0x18C          | _                                               |

| 100                | TRCIDR12   | 0x190          | -                                               |

| 101                | TRCIDR13   | 0x194          | -                                               |

| 112                | TRCIMSPEC0 | 0x1C0          | Implementation Specific Register 0 on page 3-37 |

| 120                | TRCIDR0    | 0x1E0          | ID Register 0 on page 3-38                      |

| 121                | TRCIDR1    | 0x1E4          | ID Register 1 on page 3-39                      |

| 122                | TRCIDR2    | 0x1E8          | ID Register 2 on page 3-40                      |

| 123                | TRCIDR3    | 0x1EC          | ID Register 3 on page 3-41                      |

| 124                | TRCIDR4    | 0x1F0          | ID Register 4 on page 3-42                      |

| 125                | TRCIDR5    | 0x1F4          | ID Register 5 on page 3-43                      |

# **Resource selection registers**

Table 3-6 shows the resource selection registers in numerical order.

Table 3-6 Resource selection registers

| Register<br>number | Name       | Base offset | Description                                    |

|--------------------|------------|-------------|------------------------------------------------|

| 130-140            | TRCRSCTLRn | 0x208-0x240 | Resource Selection Registers 2-16 on page 3-44 |

# Single-Shot comparator registers

Table 3-7 shows the Single-Shot comparator registers in numerical order.

**Table 3-7 Single-Shot Comparator registers**

| Register<br>number | Name      | Base offset | Description                                               |

|--------------------|-----------|-------------|-----------------------------------------------------------|

| 160-161            | TRCSSCCRn | 0x280-0x284 | Single-Shot Comparator Control Registers 0-1 on page 3-45 |

| 168-169            | TRCSSCSRn | 0x2A0-0x2A4 | Single-Shot Comparator Status Registers 0-1 on page 3-46  |

# OS lock and power control registers

Table 3-8 shows the OS lock and power control registers in numerical order.

Table 3-8 OS lock and power control registers

| Register<br>number | Name     | Base<br>offset | Description                              |

|--------------------|----------|----------------|------------------------------------------|

| 192                | TRCOSLAR | 0x300          | OS Lock Access Register on page 3-47     |

| 193                | TRCOSLSR | 0x304          | OS Lock Status Register on page 3-48     |

| 196                | TRCPDCR  | 0x310          | Power Down Control Register on page 3-49 |

| 197                | TRCPDSR  | 0x314          | Power Down Status Register on page 3-49  |

# **Comparator registers**

Table 3-9 shows the comparator registers in numerical order.

**Table 3-9 Comparator registers**

| Register<br>number | Name       | Base offset | Description                                               |

|--------------------|------------|-------------|-----------------------------------------------------------|

| 256-271            | TRCACVRn   | 0x400-0x43C | Address Comparator Value Registers 0-7 on page 3-50       |

| 288-303            | TRCACATRn  | 0x480-0x4BC | Address Comparator Access Type Registers 0-7 on page 3-51 |

| 320-321            | TRCDVCVRn  | 0x500-0x504 | Data Value Comparator Value Registers 0-1 on page 3-53    |

| 352-359            | TRCDVCMRn  | 0x580-0x59C | Data Value Comparator Mask Registers 0-1 on page 3-53     |

| 384                | TRCCIDCVR0 | 0x600       | Context ID Comparator Value Register 0 on page 3-54       |

#### **Integration Test registers**

Table 3-10 shows the Integration Test registers in numerical order.

**Table 3-10 Integration Test registers**

| Register<br>number | Name                                       | Base<br>offset | Description                                             |

|--------------------|--------------------------------------------|----------------|---------------------------------------------------------|

| 951                | Integration Miscellaneous Outputs Register | 0xEDC          | Integration Miscellaneous Outputs Register on page 3-66 |

| 952                | Integration Miscellaneous Inputs Register  | 0xEE0          | Integration Miscellaneous Inputs Register on page 3-67  |

| 953                | Integration ATB Identification Register    | 0xEE4          | Integration ATB Identification Register on page 3-68    |

| 954                | Integration Data ATB Data Register         | 0xEE8          | Integration Data ATB Data Register on page 3-69         |

| 955                | Integration Instruction ATB Data Register  | 0xEEC          | Integration Instruction ATB Data Register on page 3-69  |

| 956                | Integration Data ATB In Register           | 0xEF0          | Integration Data ATB In Register on page 3-70           |

| 957                | Integration Instruction ATB In Register    | 0xEF4          | Integration Instruction ATB In Register on page 3-71    |

| 958                | Integration Data ATB Out Register          | 0xEF8          | Integration Data ATB Out Register on page 3-71          |

| 959                | Integration Instruction ATB Out Register   | 0xEFC          | Integration Instruction ATB Out Register on page 3-72   |

# CoreSight management registers

Table 3-11 shows the CoreSight management registers in numerical order.

Table 3-11 CoreSight management registers

| Register<br>number | Name          | Base offset | Description                                      |

|--------------------|---------------|-------------|--------------------------------------------------|

| 960                | TRCITCTRL     | 0xF00       | Integration Mode Control Register on page 3-55   |

| 1000               | TRCCLAIMSET   | 0xFA0       | Claim Tag Set Register on page 3-56              |

| 1001               | TRCCLAIMCLR   | 0xFA4       | Claim Tag Clear Register on page 3-56            |

| 1002               | TRCDEVAFF0    | 0xFA8       | Device Affinity Register on page 3-57            |

| 1004               | TRCLAR        | 0xFB0       | Software Lock Access Register on page 3-58       |

| 1005               | TRCLSR        | 0xFB4       | Software Lock Status Register on page 3-58       |

| 1006               | TRCAUTHSTATUS | 0xFB8       | Authentication Status Register on page 3-59      |

| 1007               | TRCDEVARCH    | 0xFBC       | Device Architecture Register on page 3-60        |

| 1010               | TRCDEVID      | 0xFC8       | Device ID Register on page 3-61                  |

| 1011               | TRCDEVTYPE    | 0xFCC       | Device Type Register on page 3-61                |

| 1012-1019          | TRCPIDRn      | 0xFD0-0xFEC | Peripheral Identification Registers on page 3-62 |

| 1020-1023          | TRCCIDRn      | 0xFF0-0xFFC | Component Identification Registers on page 3-64  |

# 3.4 Register descriptions

This section describes ETM-R7 registers.

# 3.4.1 Programming Control Register

The TRCPRGCTLR characteristics are:

**Purpose** Enables the ETM-R7.

**Usage constraints** See *Controlling ETM programming* on page 3-3.

**Configurations** Available in all configurations.

**Attributes** See the register summary in Table 3-1 on page 3-5 and Table 3-2 on

page 3-8.

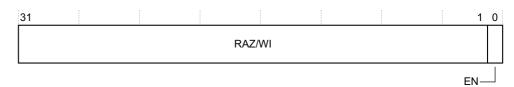

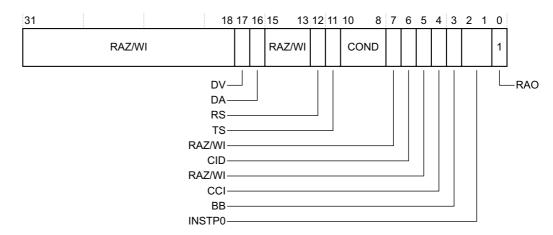

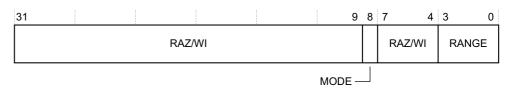

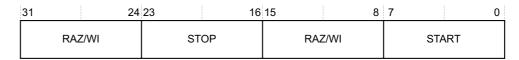

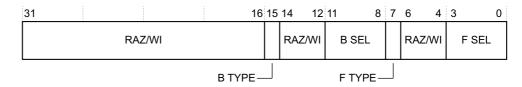

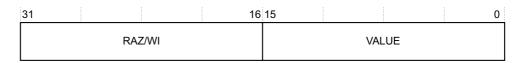

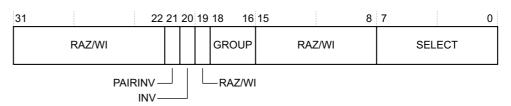

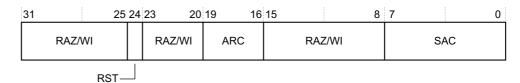

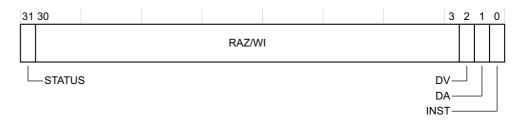

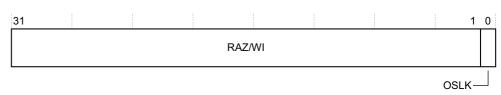

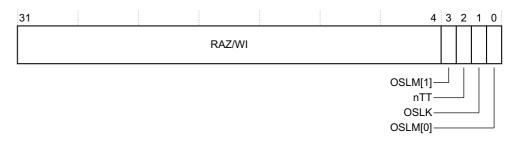

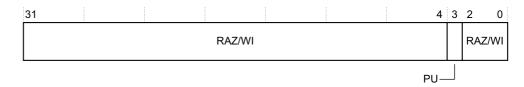

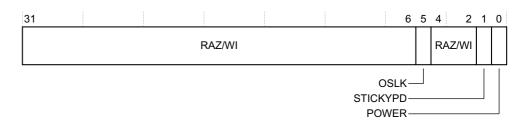

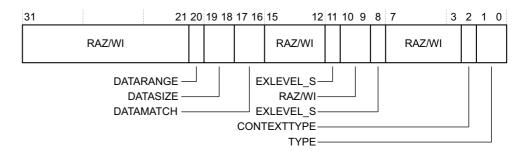

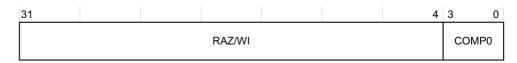

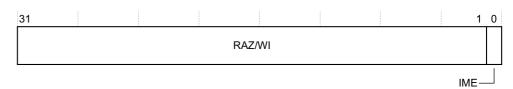

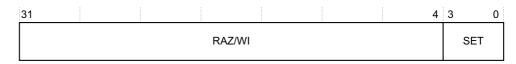

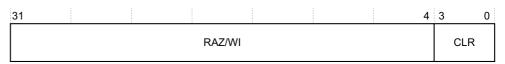

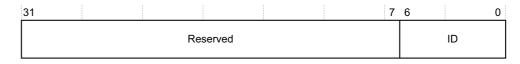

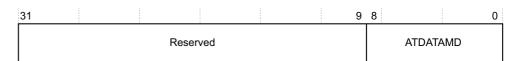

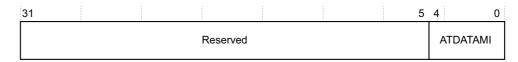

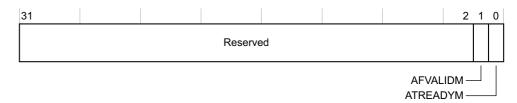

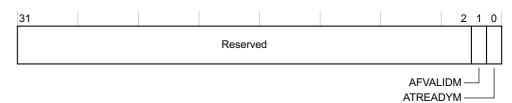

Figure 3-2 shows the TRCPRGCTLR bit assignments.

Figure 3-2 TRCPRGCTLR bit assignments

Table 3-12 shows the TRCPRGCTLR bit assignments.

Table 3-12 TRCPRGCTLR bit assignments

| Bits   | Name | Function |                                                                                                                                                                                                    |

|--------|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:1] | -    | RAZ/WI   |                                                                                                                                                                                                    |

| [0]    | EN   |          | external pin <b>ETMIFEN</b> is LOW, and clocks are only enabled when necessary to process APB esses, or drain any already generated trace. Writes to most registers are ignored. This is the reset |