# ARM PrimeCell<sup>®</sup> General Purpose Input/Output (PL061) Technical Reference Manual

### ARM PrimeCell General Purpose Input/Output (PL061) Technical Reference Manual

Copyright © 2000 ARM Limited. All rights reserved.. All rights reserved.

#### **Release Information**

The following changes have been made to this document.

Change history

| Date           | Issue | Change                                           |

|----------------|-------|--------------------------------------------------|

| August 2000    | А     | First release                                    |

| September 2000 | В     | Only confidentiality and product status changed. |

#### **Proprietary Notice**

ARM, the ARM Powered logo, Thumb, and StrongARM are registered trademarks of ARM Limited.

The ARM logo, AMBA, Angel, ARMulator, EmbeddedICE, ModelGen, Multi-ICE, PrimeCell, ARM7TDMI, ARM7TDMI-S, ARM9TDMI, ARM9E-S, ARM966E-S, ETM7, ETM9, TDMI and STRONG are trademarks of ARM Limited.

All other products or services mentioned herein may be trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

## Contents ARM PrimeCell General Purpose Input/Output (PL061) Technical Reference Manual

|           | Preface                                      |

|-----------|----------------------------------------------|

|           | About this document x                        |

|           | Further reading xii                          |

|           | Feedback xiii                                |

| Chapter 1 | Introduction                                 |

|           | 1.1 About the ARM PrimeCell GPIO (PL061) 1-2 |

| Chapter 2 | Functional Overview                          |

|           | 2.1 PrimeCell GPIO overview                  |

|           | 2.2 PrimeCell GPIO functional description    |

|           | 2.3 PrimeCell GPIO operation                 |

| Chapter 3 | Programmer's Model                           |

| •         | 3.1 About the programmer's model             |

|           | 3.2 Summary of PrimeCell GPIO registers      |

|           | 3.3 Register descriptions                    |

| Chapter 4 | Programmer's Model for Test                  |

| •         | 4.1 PrimeCell GPIO test harness overview     |

|           |                                              |

| Scan testing                         | . 4-3                                                                       |

|--------------------------------------|-----------------------------------------------------------------------------|

| Integration test registers           | . 4-4                                                                       |

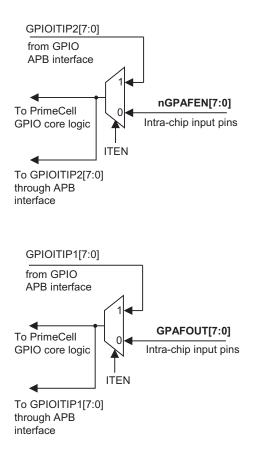

| Integration testing of block inputs  | . 4-8                                                                       |

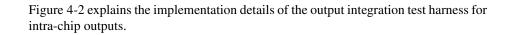

| Integration testing of block outputs | 4-11                                                                        |

| Integration test summary             | 4-14                                                                        |

|                                      | Integration testing of block inputs<br>Integration testing of block outputs |

### Chapter 5 Signal Descriptions

| 5.1 | AMBA APB signals | 5-2 |

|-----|------------------|-----|

| 5.2 | On-chip signals  | 5-3 |

| 5.3 | Signals to pads  | 5-4 |

## List of Tables ARM PrimeCell General Purpose Input/Output (PL061) Technical Reference Manual

| Change history                     | ii                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Triggering an interrupt from pin 2 | 2-12                                                                                                                                                                                                                                                                                                                                                                                                        |

| Pad configuration                  |                                                                                                                                                                                                                                                                                                                                                                                                             |

| PrimeCell GPIO register summary    | 3-3                                                                                                                                                                                                                                                                                                                                                                                                         |

| GPIODATA register                  | 3-6                                                                                                                                                                                                                                                                                                                                                                                                         |

| GPIODIR register                   | 3-6                                                                                                                                                                                                                                                                                                                                                                                                         |

| GPIOIS register                    | 3-6                                                                                                                                                                                                                                                                                                                                                                                                         |

| GPIOIBE register                   | 3-7                                                                                                                                                                                                                                                                                                                                                                                                         |

| GPIOIEV register                   |                                                                                                                                                                                                                                                                                                                                                                                                             |

| GPIOIE register                    | 3-8                                                                                                                                                                                                                                                                                                                                                                                                         |

| GPIORIS register                   | 3-8                                                                                                                                                                                                                                                                                                                                                                                                         |

| GPIOMIS register                   | 3-9                                                                                                                                                                                                                                                                                                                                                                                                         |

| GPIOIC register                    | 3-9                                                                                                                                                                                                                                                                                                                                                                                                         |

| GPIOAFSEL register                 | 3-9                                                                                                                                                                                                                                                                                                                                                                                                         |

| GPIOPeriphID0 register             | 3-11                                                                                                                                                                                                                                                                                                                                                                                                        |

| GPIOPeriphID1 register             | 3-11                                                                                                                                                                                                                                                                                                                                                                                                        |

| GPIOPeriphID2 register             | 3-12                                                                                                                                                                                                                                                                                                                                                                                                        |

| GPIOPeriphID3 register             | 3-12                                                                                                                                                                                                                                                                                                                                                                                                        |

| GPIOPCellID0 register              | 3-13                                                                                                                                                                                                                                                                                                                                                                                                        |

| GPIOPCellID1 register read bits    | 3-14                                                                                                                                                                                                                                                                                                                                                                                                        |

| GPIOPCellID2 register read bits    | 3-14                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                    | PrimeCell GPIO register summary<br>GPIODATA register<br>GPIODIR register<br>GPIOIS register<br>GPIOIEV register<br>GPIOIEV register<br>GPIOIE register<br>GPIORIS register<br>GPIONIS register<br>GPIOIC register<br>GPIOAFSEL register<br>GPIOPeriphID0 register<br>GPIOPeriphID1 register<br>GPIOPeriphID2 register<br>GPIOPeriphID3 register<br>GPIOPCellID0 register<br>GPIOPCellID1 register read bits |

| Table 3-19 | GPIOPCellID3 register read bits          | 3-14  |

|------------|------------------------------------------|-------|

| Table 4-1  | Test registers memory map                | . 4-4 |

| Table 4-2  | GPIOITCR register bits                   | . 4-5 |

| Table 4-3  | GPIOITIP1 register bits                  | . 4-5 |

| Table 4-4  | GPIOITIP2 register bits                  | . 4-5 |

| Table 4-5  | GPIOITOP1 register bits                  | . 4-6 |

| Table 4-6  | GPIOITOP2 register bits                  | . 4-6 |

| Table 4-7  | GPIOITOP3 register bits                  | . 4-7 |

| Table 4-8  | PrimeCell GPIO integration test strategy | 4-14  |

| Table 5-1  | AMBA APB signal descriptions             | . 5-2 |

| Table 5-2  | On-chip signal descriptions              | . 5-3 |

| Table 5-3  | Pad signal descriptions                  | . 5-4 |

## List of Figures ARM PrimeCell General Purpose Input/Output (PL061) Technical Reference Manual

| Key to timing diagram conventions                 | xi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PrimeCell GPIO block diagram and pads connections | 1-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PrimeCell GPIO block diagram                      | 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Example 2 Write to address 0x098                  | 2-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Example 2 Read from address 0x0C4                 | 2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Write to data direction register                  | 2-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

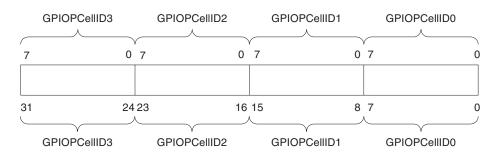

| Peripheral identification register bit assignment | 3-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| • •                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

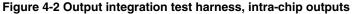

|                                                   | Key to timing diagram conventions<br>PrimeCell GPIO block diagram and pads connections<br>PrimeCell GPIO block diagram<br>Example 2 Write to address 0x098<br>Example 2 Read from address 0x0C4<br>Write to data direction register<br>PrimeCell GPIO interrupt registers<br>Mode control multiplexor<br>Peripheral identification register bit assignment<br>PrimeCell identification register bit assignment<br>Input integration test harness<br>Output integration test harness, intra-chip outputs<br>Output integration test harness, primary outputs |

List of Figures

## Preface

This preface introduces the ARM PrimeCell GPIO (PL061) and its reference documentation. It contains the following sections:

- *About this document* on page x

- Further reading on page xii

- *Feedback* on page xiii.

### About this document

This document is a technical reference manual for the ARM PrimeCell GPIO (PL061).

#### Intended audience

This document has been written for hardware and software engineers implementing System-on-Chip designs. It provides information to enable designers to integrate the peripheral into a target system as quickly as possible.

### Using this manual

This document is organized into the following chapters:

- Chapter 1 *Introduction* Read this chapter for an introduction to the ARM PrimeCell GPIO (PL061).

- Chapter 2 *Functional Overview* Read this chapter for a description of the major functional blocks of the PrimeCell GPIO.

- Chapter 3 *Programmer's Model* Read this chapter for a description of the PrimeCell GPIO registers and programming details.

- **Chapter 4** *Programmer's Model for Test* Read this chapter for a description of the logic in the PrimeCell GPIO for functional verification and production testing.

- Chapter 5 *Signal Descriptions* Read this appendix for details of the PrimeCell GPIO signals.

### Typographical conventions

The following typographical conventions are used in this document:

| bold       | Highlights ARM processor signal names, and interface elements<br>such as menu names. Also used for terms in descriptive lists,<br>where appropriate. |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| italic     | Highlights special terminology, cross-references, and citations.                                                                                     |

| typewriter | Denotes text that can be entered at the keyboard, such as commands, file names and program names, and source code.                                   |

| typewriter | Denotes a permitted abbreviation for a command or option. The<br>underlined text can be entered instead of the full command or<br>option name.       |

| typewriter italic | Denotes arguments to commands or functions where the argument<br>is to be replaced by a specific value. |

|-------------------|---------------------------------------------------------------------------------------------------------|

| typewriter bold   | Denotes language keywords when used outside example code.                                               |

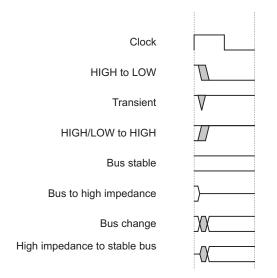

#### **Timing diagram conventions**

This manual contains one or more timing diagrams. The following key explains the components used in these diagrams. Any variations are clearly labeled when they occur. Therefore, no additional meaning should be attached unless specifically stated.

#### Key to timing diagram conventions

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

### **Further reading**

This section lists publications by ARM Limited, and by third parties.

ARM periodically provides updates and corrections to its documentation. See http://www.arm.com for current errata sheets and addenda.

See also the ARM Frequently Asked Questions list at: http://www.arm.com/DevSupp/Sales+Support/faq.html

### **ARM** publications

This document contains information that is specific to the ARM PrimeCell GPIO (PL061). Refer to the following documents for other relevant information:

- AMBA Specification (Rev 2.0) (ARM IHI 0011)

- ARM PrimeCell GPIO (PL061) Design Manual (PL061 DDES 0000)

- ARM PrimeCell GPIO (PL061) Integration Manual (PL061 INTM 0000).

### Feedback

ARM Limited welcomes feedback both on the ARM PrimeCell GPIO (PL061), and on the documentation.

### Feedback on the ARM PrimeCell GPIO (PL061)

If you have any comments or suggestions about this product, please contact your supplier giving:

- the product name

- a concise explanation of your comments.

### Feedback on this document

If you have any comments on about this document, please send email to errata@arm.com giving:

- the document title

- the document number

- the page number(s) to which your comments refer

- a concise explanation of your comments.

General suggestions for additions and improvements are also welcome.

Preface

## Chapter 1 Introduction

This chapter introduces the ARM PrimeCell GPIO (PL061). It contains the following section:

• About the ARM PrimeCell GPIO (PL061) on page 1-2.

### 1.1 About the ARM PrimeCell GPIO (PL061)

The PrimeCell GPIO is an *Advanced Microcontroller Bus Architecture* (AMBA) compliant *System-on-Chip* (SoC) peripheral that is developed, tested, and licensed by ARM.

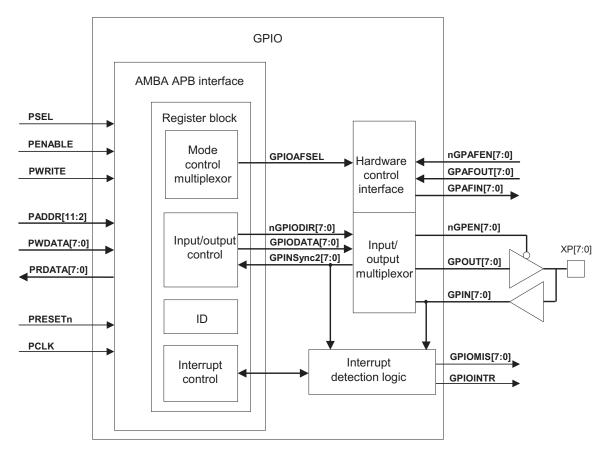

The PrimeCell GPIO is an AMBA slave module that connects to the *Advanced Peripheral Bus* (APB). The PrimeCell GPIO provides eight programmable inputs or outputs that you can control in two modes:

- software mode through an APB bus interface

- hardware mode through a hardware control interface.

You can create ports of different widths (for example 16, 24, 32, and 40 bits) by multiple instantiation. An interrupt interface is provided to configure any number of pins as interrupt sources. You can generate interrupts depending on a level, or a transitional value of a pin. At system reset, PrimeCell GPIO lines default to inputs. The PrimeCell GPIO interfaces with input and output pad cells using a data input, data output, and output enable per pad.

Figure 1-1 on page 1-3 shows the PrimeCell GPIO interfaces.

### 1.1.1 Features of the PrimeCell GPIO

The PrimeCell GPIO offers:

- Compliance to the AMBA Specification (Rev 2.0) onwards for easy integration into SoC implementation.

- Eight individually programmable input/output pins, default to input at reset.

- Scalability by multiple instantiation to 16, 24, 32, 40, or more bits.

- Programmable interrupt generation capability, from a transition or a level condition, on any number of pins.

- Hardware control capability of PrimeCell GPIO lines for different system configurations.

- Bit masking in both read and write operations through address lines.

- Identification registers that uniquely identify the PrimeCell GPIO.

## Chapter 2 Functional Overview

This chapter describes the major functional blocks of the ARM PrimeCell GPIO. It contains the following sections:

- *PrimeCell GPIO overview* on page 2-2

- PrimeCell GPIO functional description on page 2-4

- *PrimeCell GPIO operation* on page 2-7.

### 2.1 PrimeCell GPIO overview

The PrimeCell GPIO is an *Advanced Microcontroller Bus Architecture* (AMBA) bus slave that connects to the AMBA *Advanced Peripheral Bus* (APB). It provides eight programmable inputs or outputs that you can control in two modes:

- software mode through an APB bus interface

- hardware mode through a hardware control interface.

The CPU accesses data, control, and status information of the PrimeCell GPIO through the APB bus interface.

The PrimeCell GPIO peripheral includes the following registers:

- Data direction register

- Data register

- Interrupt control registers

- Mode control select register

- *Identification registers* on page 2-3.

### 2.1.1 Data direction register

The data direction register is eight bits wide and configures each pin as an input or output.

#### 2.1.2 Data register

The data register is eight bits wide and is used to:

- read the value input on those PrimeCell GPIO lines that are configured as inputs

- program the value on those PrimeCell GPIO lines that are configured as outputs.

The same data register appears at 256 locations in the memory map. This allows you to use the address bus [9:2] as an additional bit masking feature.

### 2.1.3 Interrupt control registers

The PrimeCell GPIO has interrupt generation capability. You can configure any number of the external PrimeCell GPIO lines independently to trigger an interrupt through its corresponding bit in the seven interrupt registers.

### 2.1.4 Mode control select register

The PrimeCell GPIO lines can be controlled by software through the APB bus or by hardware through the hardware control interface. The mode of each PrimeCell GPIO line is selected by the mode control select register.

When you enable hardware control in a particular line, control and data transfer over this line is provided from an auxiliary source.

### 2.1.5 Identification registers

The PrimeCell GPIO identification registers contain peripheral and BIOS information that uniquely identifies the peripheral. An automatically configuring BIOS can scan through memory searching for the BIOS ID number. Once found, the BIOS can read the peripheral ID numbers and automatically configure itself.

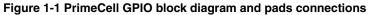

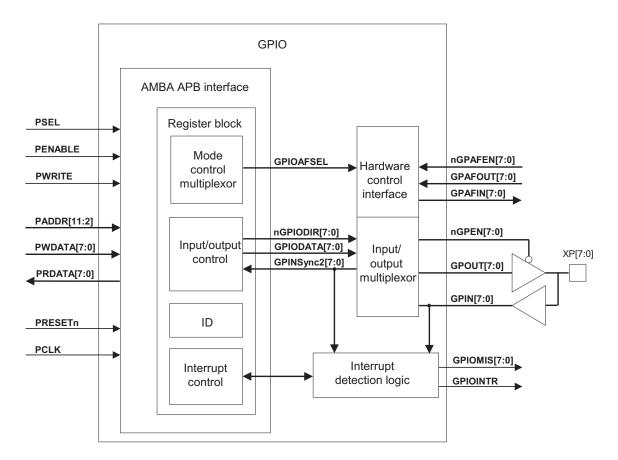

### 2.2 PrimeCell GPIO functional description

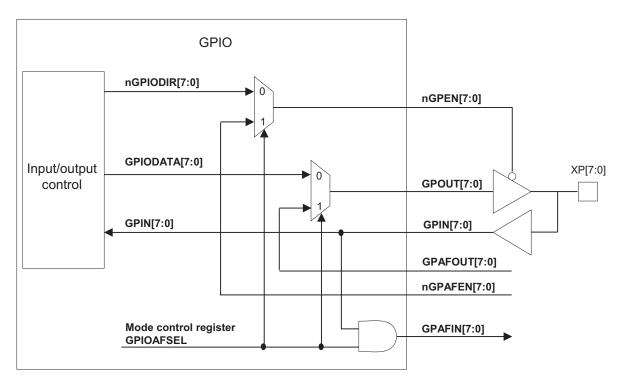

Figure 2-1 shows a block diagram of the PrimeCell GPIO.

### Figure 2-1 PrimeCell GPIO block diagram

The functions of the PrimeCell GPIO are described in the following sections:

- AMBA APB interface on page 2-5

- Interrupt detection logic on page 2-5

- *Mode control* on page 2-6.

### 2.2.1 AMBA APB interface

The AMBA APB is a local secondary bus that provides a low-power extension to the higher bandwidth AMBA *Advanced High-performance Bus* (AHB), within the AMBA system hierarchy. The AMBA APB groups narrow-bus peripherals to avoid loading the system bus, and provides an interface using memory-mapped registers that are accessed under programmed control.

The AMBA APB interface generates read and write decodes for accesses to control, interrupt, and data registers within the PrimeCell GPIO. A read-only decode is provided to access the ID codes.

The AMBA APB interface implements the storage elements for the data, data direction, mode control, interrupt interface, and identification registers.

### 2.2.2 Interrupt detection logic

The PrimeCell GPIO has the ability to generate mask-programmable interrupts based on the level, or transitional value of any of its PrimeCell GPIO lines.

The *General Purpose Input Output Interrupt* (GPIOINTR) indicates to an interrupt controller that an interrupt occurred in one or more of the PrimeCell GPIO lines. You can configure interrupts so that they are generated either on a change in the level, or on an edge of the PrimeCell GPIO line. The edge and level on which the interrupt must be generated is programmable. Seven registers in the AMBA APB interface, each controlling a different feature or condition in the interrupt triggering chain, allow the following functionality:

- interrupt generation either on a change in the level, one edge, or both edges of the PrimeCell GPIO line

- reading raw and masked interrupt status

- reading from and writing to the interrupt enable

- interrupt clear (write-only).

Each input/output line has a corresponding masked interrupt output line. Setting the appropriate mask bit HIGH enables the interrupt. GPIOINTR is the combined interrupt output of the PrimeCell GPIO masked interrupt status lines. It indicates to the interrupt controller that this block is requesting service from one or more of its interrupt sources.

Provision of individual outputs as well as a combined interrupt output, allows you to use either a global interrupt service routine or modular device drivers to handle interrupts.

### 2.2.3 Mode control

You can control the PrimeCell GPIO lines by software through the APB bus, or by hardware through the hardware control interface. Select the mode of each PrimeCell GPIO line using the mode control select register (GPIOAFSEL).

When software control mode is enabled (default) the data direction is controlled by the data direction register. Data writes and reads are then performed through the APB interface.

When hardware control mode is enabled, data direction is controlled through the auxiliary port direction control pins. Similarly, data is written and read through this port, but pin status can also be read through the APB interface.

### 2.3 PrimeCell GPIO operation

The operation of the PrimeCell GPIO is described in the following sections:

- Interface reset

- Interface configuration

- Operation of the input/output lines on page 2-8

- *Interrupt operation* on page 2-10

- *Mode control* on page 2-12.

### 2.3.1 Interface reset

All block registers are cleared during power-on-reset (LOW). This disables the output drivers for the Primecell GPIO lines, so that the pins are configured as inputs.

### 2.3.2 Interface configuration

On application of **PRESETn** as LOW:

- interrupts in the desired line are disabled by clearing the corresponding bit in GPIOIE

- all registers are cleared to zero

- input and output pins are configured as inputs

- interrupts to the external world are all masked as disabled

- raw interrupts are cleared to zero

- edge triggered interrupts are selected as source.

### Recommendations

If you want to generate edge-triggered interrupts you must perform the following initialization sequence to avoid spurious interrupts being interpreted by the system:

- program GPIOIBE appropriately as individual or both-edge detection

- program GPIOIEV, if you have selected individual edge transactions previously

- program GPIOIS to select edge-triggered path

- apply three clock pulses to clean interrupt pipeline

- ensure GPIN[7:0] bus remains stable throughout this operation

- clear all interrupts by writing 0xFF to GPIOIC

- program GPIOIE to enable interrupts.

### 2.3.3 Operation of the input/output lines

The Primecell GPIO block comprises eight programmable input/output lines. When the software control mode is enabled, data and control for these lines are provided by a data register and a data direction register. On reads, the data register contains the current status of the Primecell GPIO pins, whether they are configured as input or output. Writing to the data register only affects the pins that are configured as outputs.

### Data register

So that independent software drivers can set their GPIO bits without affecting any other pins in a single write operation, the address bus is used as a mask on read/write operations. The data register effectively covers 256 locations in the address space. The eight address lines used are **PADDR [9: 2]**. During a write, if the address bit associated with that data bit is HIGH, the value of the GPIODATA register is altered. If it is LOW, it is left unchanged. For example:

#### Writing to address GPIODATA + 0x098 = 0b000010011000

PADDR[9:2] = 0b0000100110. When a value of 0xFB is written to the address 0x098 then:

- bits 5, and 1 of the PrimeCell GPIO pins are set to 1, and bit 2 is set to 0

- the other bits are not changed.

Figure 2-2 shows the above effect of the address value of 0x098 operating on the data value of 0xFB.

| PADDR[9:2] | 9 | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7 | 6 | 5 | 4 | 3 | 2 |   |   |

|------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|---|

| 0x098      | 0 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 |

|            | + | The second secon | + | + | ¥ | ¥ | + | ¥ |   |   |

| 0xFB       | 1 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 | 1 | 1 | 0 | 1 | 1 |   |   |

|            |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | + |   |   | ¥ | ¥ |   | _ |   |

| GPIODATA   | u | u                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 | u | u | 0 | 1 | u | ] |   |

|            | 7 | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5 | 4 | 3 | 2 | 1 | 0 |   |   |

|            |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |   |   |   |   |   |   |   |

– Note –

### Figure 2-2 Example 2 Write to address 0x098

In Figure 2-2 u indicates that the bit value is unchanged.

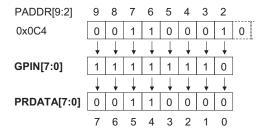

During a read if an address bit associated with data is HIGH the value is read, if it is LOW it is as zero. For example:

#### Read from address GPIODATA + 0x0C4 = 0b000011000100

PADDR[9:2] = 0b0000110001. When reading from 0x0C4 then:

- bits 5, 4, and 0 of the PrimeCell GPIO pins are returned

- the value of bits 7, 6, 3, 2, and 1 are returned as zero, regardless of their state.

Figure 2-3 shows a read from the address 0x0C4 and the output on the **PRDATA**[7:0] lines.

### Figure 2-3 Example 2 Read from address 0x0C4

### **Data direction registers**

The data direction registers operate in the following manner:

- 0 indicates the corresponding output pin is defined as an input

- 1 indicates the corresponding output pin is defined as an output.

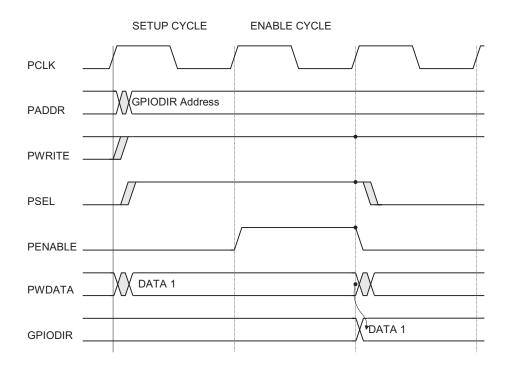

Figure 2-4 on page 2-10 shows a typical write, in this case to the data direction register.

### Figure 2-4 Write to data direction register

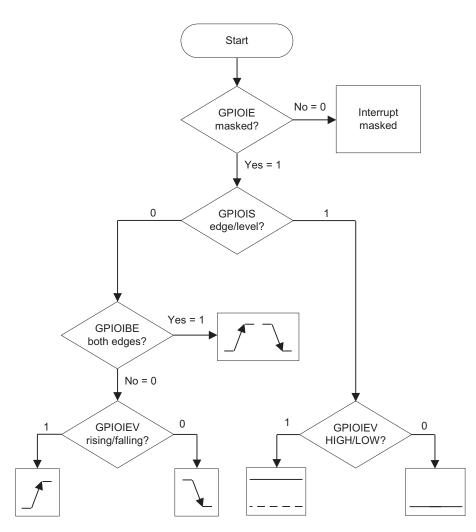

### 2.3.4 Interrupt operation

The interrupt section of the PrimeCell GPIO is controlled by a set of seven registers. You can select the source of the interrupt, its polarity, and edge properties. When one or more PrimeCell GPIO lines causes an interrupt, a single interrupt output **GPIOINTR** and/or the individual interrupts can be sent to the interrupt controller. For edge-triggered interrupts, software must clear the interrupt to enable any further interrupts. For a level case, it is assumed that the external source holds the level constant for the interrupt to be recognized by the processor.

Three registers are required to define the edge or sense that causes an interrupt:

- GPIOIS

- GPIOIBE

- GPIOIEV.

Figure 2-5 on page 2-11 shows how the bits of the three registers combine to select an interrupt source event.

Figure 2-5 PrimeCell GPIO interrupt registers

### Registers to be programmed

Table 2-1 shows how an interrupt is triggered by a rising edge detected on input pin 2.

| Register | Desired trigger                                             | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------|-------------------------------------------------------------|---|---|---|---|---|---|---|---|

| GPIOIS   | 0 = edge<br>1 = level                                       | х | x | x | x | x | 0 | x | x |

| GPIOIBE  | 0 = single edge<br>1 = both edges                           | х | Х | Х | X | X | 0 | X | х |

| GPIOIEV  | LOW level, or negative edge<br>HIGH level, or positive edge | х | Х | Х | X | X | 1 | X | X |

| GPIOIE   | 0 = masked<br>1 = not masked                                | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

Table 2-1 Triggering an interrupt from pin 2

#### — Note –

If any GPIOIE register bit is 0, the interrupt triggering on the associated line is disabled. In Table 2-1 an x indicates that the value of the associated bit is irrelevant, a consequence of the bit being masked by the GPIOIE register setting.

You must perform programming of the interrupt control registers when the respective interrupts are not enabled. Writing to interrupt control registers can generate spurious interrupts if the corresponding bits are enabled.

### 2.3.5 Mode control

You can control the PrimeCell GPIO lines through the hardware control interface. The mode of each line is selected by the mode control register. When hardware control is enabled in a particular line, the data and data direction control signals of the corresponding PrimeCell GPIO pins are ignored. Data and control transfers over these PrimeCell GPIO pins are then driven or read by some external auxiliary control block.

See Figure 2-6 on page 2-13 for a block diagram showing the mode control multiplexor.

### Figure 2-6 Mode control multiplexor

Table 2-2 shows how the pads are configured for hardware and software control.

### Table 2-2 Pad configuration

|                                     | Hardware |   |            |   |        | Software |       |   |  |

|-------------------------------------|----------|---|------------|---|--------|----------|-------|---|--|

|                                     | Output   |   | tput Input |   | Output |          | Input |   |  |

|                                     | 7        | 6 | 5          | 4 | 3      | 2        | 1     | 0 |  |

| Mode control register,<br>GPIOAFSEL | 1        | 1 | 1          | 1 | 0      | 0        | 0     | 0 |  |

| Hardware enable input,<br>nGPAFEN   | 0        | 0 | 1          | 1 | X      | X        | X     | Х |  |

| Hardware data input,<br>GPAFOUT     | А        | В | Х          | X | Х      | X        | X     | Х |  |

|                                    | Har    | dware |       |   | Sof    | tware |       |   |

|------------------------------------|--------|-------|-------|---|--------|-------|-------|---|

|                                    | Output |       | Input |   | Output |       | Input |   |

|                                    | 7      | 6     | 5     | 4 | 3      | 2     | 1     | 0 |

| Hardware data output,<br>GPAFIN    | A      | В     | с     | d | 0      | 0     | 0     | 0 |

| Software enable output,<br>GPIODIR | х      | X     | x     | x | 1      | 1     | 0     | 0 |

| Software data output,<br>GPIODATA  | х      | Х     | х     | х | E      | F     | g     | h |

| Software data input, GPIN          | А      | В     | с     | d | Е      | F     | g     | h |

| Pad enable, nGPEN                  | 0      | 0     | 1     | 1 | 0      | 0     | 1     | 1 |

| Pad output, GPOUT                  | А      | В     | х     | х | Е      | F     | х     | x |

| Pad input, GPIN                    | А      | В     | с     | d | Е      | F     | g     | h |

| Bidirectional pad, XP              | А      | В     | с     | d | Е      | F     | g     | h |

#### Table 2-2 Pad configuration (continued)

\_\_\_\_\_Note \_\_\_\_\_

A, B, E, F, are sources of output data. c, d, g, h, are sources of input data.

In hardware control mode the GPIODATA register can also read the values of lines configured as inputs.

Table 2-2 on page 2-13 is a concise truth table of operation when the GPIO PL061 has its data port pins configured as both software and hardware controlled. The values that exist on the bidirectional XP[7:0] lines are shown as the last row within the table, but it is realized that they have different sources as described below.

Table 2-2 on page 2-13 is best explained by considering each mode separately.

### Hardware control mode

The left hand four columns of Table 2-2 relate to the hardware mode of operation.XP[7:4] pins have been configured as being under hardware control by setting the respective bits to 1 within the GPIOAFSEL register.Pins configured as outputs:

- XP[7:6] pins are configured as outputs by applying a 0 value to the respective nGPAFEN port signals.

- XP[7:6] data values are sourced from the GPAFOUT[7:6] port input signals, shown as (A,B). These values are propagated and driven out onto the XP[7:6] pins. These values are also transferred back to the GPAFIN[7:6] port output signals through the GPIN[7:6] pins. This feature also allows the XP[7:0] values to be read through the APB interface GPIODATA register.

Pins configured as inputs:

- XP[5:4] pins are configured as inputs by applying a 1 value to the respective nGPAFEN port signals.

- XP[5:4] values are driven from an external source, and as above, these values (c, d), are transferred to GPAFIN[5:4] signals. Again, the XP[7:0] can be read through the APB interface GPIODATA register.

### Software control

The right hand four columns of Table 2-2 relate to the software mode of operation. In software mode the GPAFIN port signals are forced LOW as a power saving feature.XP[3:0] pins have been configured as being under software control by setting the respective bits to 0 within the GPIOAFSEL register.Pins configured as outputs:

- XP[3:2] pins are configured as outputs by setting the respective bits to 1 within the GPIODIR data direction register.

- XP[3:2] data values are sourced from the GPIODATA[3:2] register bits, shown as (E,F). These values are propagated and driven out onto the XP[3:2] pins. These values are transferred back to the GPIN[3:2] pins, but not to the GPAFIN pins as this route is disabled when in software mode.

- The XP[3:2] pin values can be read through the APB interface GPIODATA register.

Pins configured as inputs:

• XP[1:0] pins have been configured as inputs by setting the respective bits to 0 within the GPIODIR data direction register.

• XP[1:0] values are driven from an external source, shown as (g, h). The XP[1:0] pin values can be read through the APB interface GPIODATA register.

## Chapter 3 Programmer's Model

This chapter describes the ARM PrimeCell GPIO (PL061) registers and provides details needed when programming the peripheral. It contains the following sections:

- About the programmer's model on page 3-2

- Summary of PrimeCell GPIO registers on page 3-3

- *Register descriptions* on page 3-5.

### 3.1 About the programmer's model

The base address of the PrimeCell GPIO is not fixed, and can be different for any particular system implementation. However, the offset of any particular register from the base address is fixed. The following locations are reserved and must not be used during normal operation:

- locations at offsets 0x424 to 0xFCC are reserved for possible future extensions and test purposes

- locations at offsets +0xFDO to +0xFDC are reserved for future ID expansion.

# 3.2 Summary of PrimeCell GPIO registers

The PrimeCell GPIO registers are shown in Table 3-1.

| Address                                         | Туре       | Width | Reset value | Name          | Description                                  |

|-------------------------------------------------|------------|-------|-------------|---------------|----------------------------------------------|

| GPIO base +<br>0x000 to<br>GPIO base +<br>0x3FC | Read/write | 8     | 0x00        | GPIODATA      | PrimeCell GPIO data register                 |

| GPIO base +<br>0x400                            | Read/write | 8     | 0x00        | GPIODIR       | PrimeCell GPIO data direction register       |

| GPIO base +<br>0x404                            | Read/write | 8     | 0x00        | GPIOIS        | PrimeCell GPIO interrupt sense register      |

| GPIO base +<br>0x408                            | Read/write | 8     | 0x00        | GPIOIBE       | PrimeCell GPIO interrupt both edges register |

| GPIO base +<br>0x40C                            | Read/write | 8     | 0x00        | GPIOIEV       | PrimeCell GPIO interrupt event register      |

| GPIO base +<br>0x410                            | Read/write | 8     | 0x00        | GPIOIE        | PrimeCell GPIO interrupt mask                |

| GPIO base +<br>0x414                            | Read       | 8     | 0x00        | GPIORIS       | PrimeCell GPIO raw interrupt status          |

| GPIO base +<br>0x418                            | Read       | 8     | 0x00        | GPIOMIS       | PrimeCell GPIO masked interrupt status       |

| GPIO base +<br>0x41C                            | Write      | 8     | 0x00        | GPIOIC        | PrimeCell GPIO interrupt clear               |

| GPIO base +<br>0x420                            | Read/write | 8     | 0x00        | GPIOAFSEL     | PrimeCell GPIO mode control select           |

| GPIO base +<br>0x424-0xFCC                      | -          | -     | -           | -             | Reserved for future use and test purposes    |

| GPIO base +<br>0xFD0-0xFDC                      | -          | -     | -           | -             | Reserved for future ID expansion             |

| GPIO base +<br>0xFE0                            | Read       | 8     | 0x61        | GPIOPeriphID0 | Peripheral identification register bits 7:0  |

| Table 3-1 | PrimeCell | <b>GPIO</b> register | summary | (continued) |

|-----------|-----------|----------------------|---------|-------------|

|-----------|-----------|----------------------|---------|-------------|

| Address              | Туре | Width | Reset value | Name          | Description                                     |

|----------------------|------|-------|-------------|---------------|-------------------------------------------------|

| GPIO base +<br>0xFE4 | Read | 8     | 0x10        | GPIOPeriphID1 | Peripheral identification register<br>bits 15:8 |

| GPIO base +<br>0xFE8 | Read | 8     | 0x04        | GPIOPeriphID2 | Peripheral identification register bits 23:16   |

| GPIO base +<br>0xFEC | Read | 8     | 0x00        | GPIOPeriphID3 | Peripheral identification register bits 31:24   |

| GPIO base +<br>0xFF0 | Read | 8     | 0x0D        | GPIOPCellID0  | PrimeCell identification register bits 7:0      |

| GPIO base +<br>0xFF4 | Read | 8     | 0xF0        | GPIOPCellID1  | PrimeCell identification register bits 15:8     |

| GPIO base +<br>0xFF8 | Read | 8     | 0x05        | GPIOPCellID2  | PrimeCell identification register bits 23:16    |

| GPIO base +<br>0xFFC | Read | 8     | 0xB1        | GPIOPCellID3  | PrimeCell identification register bits 31:24    |

### 3.3 Register descriptions

The following PrimeCell GPIO registers are described in this section:

- Data register, GPIODATA

- Data direction register, GPIODIR on page 3-6

- Interrupt sense register, GPIOIS on page 3-6

- Interrupt both-edges register, GPIOIBE on page 3-7

- Interrupt event register, GPIOIEV on page 3-7

- Raw interrupt status register, GPIORIS on page 3-8

- Masked interrupt status register, GPIOMIS on page 3-8

- Interrupt clear register, GPIOIC on page 3-9

- Mode control select register, GPIOAFSEL on page 3-9

- Peripheral identification registers, GPIOPeriphID0-3 on page 3-10

- *PrimeCell identification registers, GPIOPCellID0-3* on page 3-12.

### 3.3.1 Data register, GPIODATA

The GPIODATA register is the data register. In software control mode, values written in the GPIODATA register are transferred onto the **GPOUT** pins if the respective pins have been configured as outputs through the GPIODIR register.

In order to write to GPIODATA, the corresponding bits in the mask, resulting from the address bus, **PADDR[9:2]**, must be HIGH. Otherwise the bit values remain unchanged by the write.

Similarly, the values read from this register are determined for each bit, by the mask bit derived from the address used to access the data register, **PADDR[9:2]**. Bits that are 1 in the address mask cause the corresponding bits in GPIODATA to be read, and bits that are 0 in the address mask cause the corresponding bits in GPIODATA to be read as 0, regardless of their value.

A read from GPIODATA returns the last bit value written if the respective pins are configured as output, or it returns the value on the corresponding input **GPIN** bit when these are configured as inputs. All bits are cleared by a reset.

Table 3-2 shows the bit assignment of the GPIODATA register. For examples of address masking on reads and writes, see *Data register* on page 2-2.

| Bits | Name     | Туре  | Function    |

|------|----------|-------|-------------|

| 7:0  | Data     | Read/ | Input data  |

|      | register | write | Output data |

### Table 3-2 GPIODATA register

### 3.3.2 Data direction register, GPIODIR

The GPIODIR register is the data direction register. Bits set to HIGH in the GPIODIR configure corresponding pin to be an output. Clearing a bit configures the pin to be input. All bits are cleared by a reset. Therefore, the GPIO pins are input by default.

Table 3-3 shows the bit assignment of the GPIODIR register.

### Table 3-3 GPIODIR register

| Bits | Name                    | Туре           | Function                                           |

|------|-------------------------|----------------|----------------------------------------------------|

| 7:0  | Data direction register | Read/<br>write | Bits set, pins output<br>Bits cleared, pins output |

### 3.3.3 Interrupt sense register, GPIOIS

The GPIOIS register is the interrupt sense register. Bits set to HIGH in GPIOIS configure the corresponding pins to detect levels. Clearing a bit configures the pin to detect edges. All bits are cleared by a reset.

Table 3-4 shows the bit assignment of the GPIOIS register.

### Table 3-4 GPIOIS register

| Bits | Name            | Туре  | Function                                          |

|------|-----------------|-------|---------------------------------------------------|

| 7:0  | Interrupt sense | Read/ | Bits clear, edge on corresponding pin is detected |

|      | register        | write | Bits set, level on corresponding pin is detected  |

### 3.3.4 Interrupt both-edges register, GPIOIBE

The GPIOIBE register is the interrupt both-edges register. When the corresponding bit in GPIOIS is set to detect edges, bits set to HIGH in GPIOIBE configure the corresponding pin to detect both rising and falling edges, regardless of the corresponding bit in the GPIOIEV (interrupt event register). Clearing a bit configures the pin to be controlled by GPIOIEV. All bits are cleared by a reset.

Table 3-5 shows the bit assignment of the GPIOIBE register.

### Table 3-5 GPIOIBE register

| Bits | Name                 | Туре       | Function                                                                                                                                                                                                        |

|------|----------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | Interrupt both edges | Read/write | Bits set, both edges on corresponding pin<br>trigger an interrupt.Bits cleared, interrupt<br>generation event is controlled by GPIOIEV.<br>Single edge, determined by corresponding bit<br>in GPIOIEV register. |

### 3.3.5 Interrupt event register, GPIOIEV

The GPIOIEV register is the interrupt event register. Bits set to HIGH in GPIOIEV configure the corresponding pin to detect rising edges or high levels, depending on the corresponding bit value in GPIOIS. Clearing a bit configures the pin to detect falling edges or low levels, depending on the corresponding bit value in GPIOIS. All bits are cleared by a reset.

Table 3-6 shows the bit assignment of the GPIOIEV register.

#### Table 3-6 GPIOIEV register

| Bits | Name                     | Туре       | Function                                                                                                                                                                         |

|------|--------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | Interrupt event register | Read/write | Bits set, rising edges, or high levels on<br>corresponding pins trigger interrupts.<br>Bits cleared, falling edges, or low<br>levels on corresponding pin trigger<br>interrupts. |

### 3.3.6 Interrupt mask register, GPIOIE

The GPIOIE register is the interrupt mask register. Bits set to HIGH in GPIOIE allow the corresponding pins to trigger their individual interrupts and the combined GPIOINTR line. Clearing a bit disables interrupt triggering on that pin. All bits are cleared by a reset.

Table 3-7 shows the bit assignment of the GPIOIE register.

| Bits | Name                    | Туре       | Function                                                                                                 |

|------|-------------------------|------------|----------------------------------------------------------------------------------------------------------|

| 7:0  | Interrupt mask register | Read/write | Bits set, corresponding pin is not<br>masked.<br>Bits cleared, corresponding pin<br>interrupt is masked. |

### 3.3.7 Raw interrupt status register, GPIORIS

The GPIORIS register is the raw interrupt status register. Bits read HIGH in GPIORIS reflect the status of interrupts trigger conditions detected (raw, prior to masking), indicating that all the requirements have been met, before they are finally allowed to trigger by GPIOIE. Bits read as zero indicate that corresponding input pins have not initiated an interrupt. This register is read only, and bits are cleared by a reset.

Table 3-8 shows the bit assignment of the GPIORIS register.

### Table 3-8 GPIORIS register

| Bits | Name                 | Туре | Function                                                                                                                                                                                   |

|------|----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|