# AHB CPU Wrappers Technical Reference Manual

Copyright © 2001, 2003 ARM Limited. All rights reserved. ARM DDI 0169D

### AHB CPU Wrappers Technical Reference Manual

Copyright © 2001, 2003 ARM Limited. All rights reserved.

#### **Release Information**

The following changes have been made to this document.

Change history

| Date           | Issue | Change                                 |

|----------------|-------|----------------------------------------|

| 18 April 2001  | А     | First release.                         |

| 18 May 2001    | В     | Second release. New Chapter 1 added.   |

| 23 June 2003   | С     | Third release. Changes to Chapter 1.   |

| 14 August 2003 | D     | Corrected product number in Chapter 1. |

#### **Proprietary Notice**

Words and logos marked with  $^{\otimes}$  or  $^{\bowtie}$  are registered trademarks or trademarks of ARM Limited in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM Limited in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

## Contents AHB CPU Wrappers Technical Reference Manual

|           | Prefa | ace                                       |      |

|-----------|-------|-------------------------------------------|------|

|           |       | About this document                       | vi   |

|           |       | Feedback                                  | viii |

| Chapter 1 | Intro | duction                                   |      |

|           | 1.1   | Delivery overview                         |      |

|           | 1.2   | CPU bus access wait states                | 1-4  |

|           | 1.3   | Use of ETM and coprocessor interfaces     | 1-7  |

| Chapter 2 | ARM   | 720T AHB Wrapper                          |      |

| -         | 2.1   | About the ARM720T AHB wrapper             | 2-2  |

|           | 2.2   | Signal interface                          | 2-3  |

|           | 2.3   | Description of the ARM720T wrapper blocks |      |

|           | 2.4   | Non-standard design practices             | 2-15 |

|           | 2.5   | Programmer's model exceptions             | 2-17 |

|           |       |                                           |      |

5.4

| Chapter 3 | ARM7TDMI AHB Wrapper |                                            |     |  |

|-----------|----------------------|--------------------------------------------|-----|--|

|           | 3.1                  | About the ARM7TDMI AHB wrapper             | 3-2 |  |

|           | 3.2                  | Signal interface                           | 3-4 |  |

|           | 3.3                  | Description of the ARM7TDMI wrapper blocks |     |  |

|           | 3.4                  | Non-standard design practices              |     |  |

| Chapter 4 | ARM                  | 920T AHB Wrapper                           |     |  |

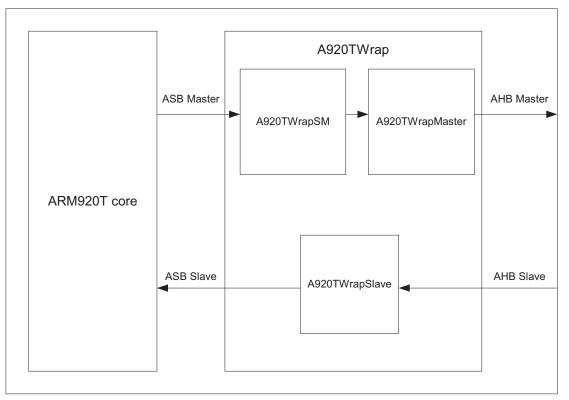

| •         | 4.1                  | About the ARM920T AHB wrapper              | 4-2 |  |

|           | 4.2                  | Signal interface                           |     |  |

|           | 4.3                  | Description of the ARM920T wrapper blocks  |     |  |

|           | 4.4                  | Non-standard design practices              |     |  |

|           | 4.5                  | Programmer's model exceptions              |     |  |

| Chapter 5 | ARM                  | 940T AHB Wrapper                           |     |  |

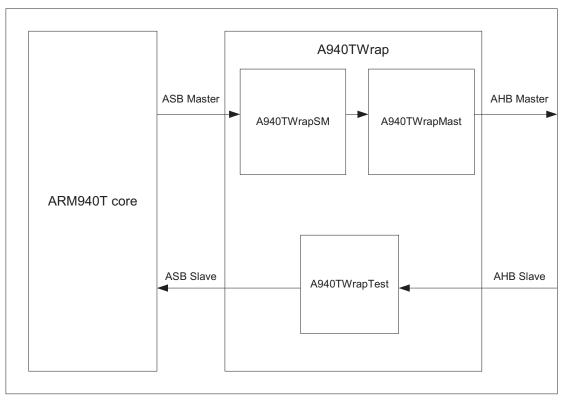

| •         | 5.1                  | About the ARM940T AHB wrapper              | 5-2 |  |

|           | 5.2                  | Signal interface                           |     |  |

|           | 5.3                  | Description of the ARM940T wrapper blocks  | 5-7 |  |

Non-standard design practices ..... 5-15

## Preface

This preface introduces the *Advanced High-performance Bus* (AHB) *Central Processor Unit* (CPU) Wrappers Technical Reference Manual. It contains the following sections:

- About this document on page vi

- *Feedback* on page viii.

### About this document

This document is the AHB CPU Wrappers Technical Reference Manual.

#### Intended audience

This document has been written for experienced hardware and software engineers to help them implement AHB wrappers on various ARM processor cores.

#### Using this manual

This document is organized into the following chapters:

#### **Chapter 1** Introduction

Read this chapter for a overview of the deliverable directory structure and a summary of the wait states, timing and critical paths, and use of the ETM and coprocessor interfaces.

#### Chapter 2 ARM720T AHB Wrapper

Read this chapter for a description of the ARM720T and ARM740T core wrappers as used with a AHB-based *Example Amba SYstem* (EASY). It introduces the wrapper block, and describes the AHB signals and the connections to the core.

#### Chapter 3 ARM7TDMI AHB Wrapper

Read this chapter for a description of the ARM7TDMI and ARM7TDMI-S core wrappers. It introduces the wrapper block, and describes the AHB signals and the connections to the core.

#### Chapter 4 ARM920T AHB Wrapper

Read this chapter for a description of the ARM920T and ARM922T core wrappers. It introduces the wrapper block, and describes the AHB signals and the connections to the core.

#### Chapter 5 ARM940T AHB Wrapper

Read this chapter for a description of the ARM940T core wrapper. It introduces the wrapper block, and describes the AHB signals and the connections to the core.

#### **Typographical conventions**

| italic            | Highlights important notes, introduces special terminology, denotes internal cross-references, and citations.                                             |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| bold              | Highlights interface elements, such as menu names. Denotes<br>ARM processor signal names. Also used for terms in descriptive<br>lists, where appropriate. |

| monospace         | Denotes text that can be entered at the keyboard, such as commands, file and program names, and source code.                                              |

| <u>mono</u> space | Denotes a permitted abbreviation for a command or option. The<br>underlined text can be entered instead of the full command or<br>option name.            |

| monospace italic  | Denotes arguments to commands and functions where the argument is to be replaced by a specific value.                                                     |

| monospace bold    | Denotes language keywords when used outside example code.                                                                                                 |

The following typographical conventions are used in this book:

#### **Further reading**

This section lists publications by ARM Limited.

ARM periodically provides updates and corrections to its documentation. See http://www.arm.com for current errata sheets, addenda, and the ARM Frequently Asked Questions list.

#### **ARM publications**

This document contains information that is specific to the AHB CPU wrappers. Refer to the following document for other relevant information:

• AHB Example AMBA System Technical Reference Manual (ARM DDI 0170).

## Feedback

ARM Limited welcomes feedback both on the ARM AHB CPU wrappers, and on the documentation.

#### Feedback on the AHB CPU wrappers

If you have any comments or suggestions about this product, contact your supplier giving:

- the product name

- a concise explanation of your comments.

#### Feedback on this document

If you have any comments on about this document, send an email to errata@arm.com giving:

- the document title

- the document number

- the page number(s) to which your comments refer

- a concise explanation of your comments.

General suggestions for additions and improvements are also welcome.

## Chapter 1 Introduction

This chapter gives a summary of the wait states, timing and critical paths, use of the ETM and coprocessor interfaces, and the release directory structure for the CPU wrappers. It contains the following sections:

- Delivery overview on page 1-2

- *CPU bus access wait states* on page 1-4

- Use of ETM and coprocessor interfaces on page 1-7.

## **1.1** Delivery overview

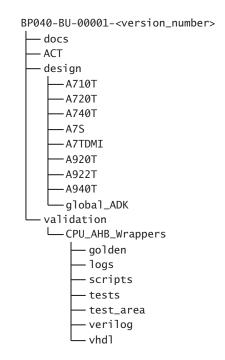

The ARM CPU AHB wrapper pack contains four primary directories:

- design Contains the HDL sources for all wrappers.

- validation Contains the AMBA Compliance Testbench (ACT) components for all wrappers.

- ACT Contains the ACT-e tool required by the testbenches.

- docs Contains documents pertaining to the CPU AHB wrappers.

The complete directory structure is shown in Figure 1-1.

#### Figure 1-1 Directory structure

Each subdirectory (apart from global\_ADK) within the design directory contains the HDL source files plus simple example synthesis scripts for the relevant CPU. The global\_ADK directory is part of the ADK product, and contains the core synthesis scripts used by all CPU wrappers.

For a description of the contents of the directories within the validation hierarchy, and for details of using the files within the ACT and validation directories, see the *ARM CPU AHB Wrapper ACT User Guide* which can be found in the docs directory.

### 1.2 CPU bus access wait states

The number of wait states added to CPU bus accesses by each of the CPU AHB wrappers is shown in Table 1-1.

Some wait states added by the AHB wrappers are unavoidable, but others can be masked by wait states from the slave which was accessed in the previous cycle. That is, if the previous access were to a zero-delay slave, the extra wait states added by the AHB wrapper are added to the number of cycles taken to complete the transaction. If the slave previously accessed asserted wait states, no extra cycles are required.

| CPU AHB<br>wrapper | Added<br>wait state | Reason                                                                                                                            | Comment                                                                                                                                    |

|--------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| ARM7TDMI<br>and    | 1                   | For each NONSEQ access from the core (except SWP accesses)                                                                        | These are masked by wait states from the slave<br>being accessed in the previous access cycle.                                             |

| ARM7TDMI-S         | 2                   | At the start of a SWP instruction                                                                                                 | -                                                                                                                                          |

| ARM720T            | 1                   | At the start of a SWP instruction                                                                                                 | These are masked by wait states from the slave<br>being accessed if a waited access immediately<br>precedes the SWP.                       |

| ARM920T            | 1                   | For each access in a nonbuffered<br>burst of writes (including single<br>accesses, which appear as bursts<br>of undefined length) | -                                                                                                                                          |

|                    | 1                   | At the start of a SWP instruction                                                                                                 | -                                                                                                                                          |

| ARM940T            | 1                   | At the start of each cacheable/<br>bufferable burst                                                                               | -                                                                                                                                          |

|                    | 1                   | For each beat of a nonbuffered burst write                                                                                        | These are masked by wait states from the slave<br>being accessed EXCEPT for the final wait state<br>added at the end of the burst.         |

|                    | 1                   | For each beat of a noncacheable burst read                                                                                        | These are masked by wait states from the slave<br>being accessed EXCEPT for the initial wait state<br>added at the beginning of the burst. |

|                    | 2                   | For the read access of a SWP instruction                                                                                          | -                                                                                                                                          |

|                    | 1                   | For the write access of a SWP instruction                                                                                         | -                                                                                                                                          |

#### Table 1-1 CPU bus access wait states

#### 1.2.1 Timing and critical paths

This section describes the timing and critical paths for the various CPU wrappers.

#### Timing

The desired timing for I/O pins on the AHB is as follows:

- all outputs to be valid within 40% of HCLK period after the rising edge of HCLK

- all inputs to require no more than 30% of **HCLK** period as setup before the rising edge of **HCLK**.

To minimize the number of wait states added when converting from the native core bus interface to AHB, some combinatorial paths from core pins to the AHB exist. Because of the large output delays and input setup times of some core pins, this can lead to non-ideal timing on the AHB interface. Therefore, although each CPU AHB wrapper can be synthesized to meet the maximum possible frequency of the attached core, doing so degrades timings on the AHB.

The synthesis of the AHB wrappers performed at ARM used the following conditions, each using the Avant! CB25 (0.25um) cell library:

- For ARM7TDMI, ARM7S, and ARM720, the AHB is synthesized to 50MHz, using a generic core timing library capable of achieving 66MHz

- For ARM920 and ARM940, the AHB is synthesized to 100MHz, using a generic core timing library capable of achieving 125MHz.

#### **Critical paths**

This section describes the critical paths for each AHB wrapper for the synthesized timing conditions given in *Timing*. If the frequency of **HCLK** relative to the maximum operating frequency of the core is reduced (for example, using an ARM920 capable of achieving 200MHz attached to a 100MHz AHB bus), the critical paths improve because of core pin timings.

Conversely, if the frequency of **HCLK** is chosen to match the maximum operating frequency of the core (for example, using an ARM7TDMI capable of achieving 88MHz attached to an 88MHz AHB bus), the timing of the critical paths degrade, as a percentage of the **HCLK** period.

The critical paths for each AHB wrapper are:

#### **ARM7TDMI**

**HTRANSM** valid after 50% of **HCLK** period because of output delays on **nMREQ** and **SEQ** plus combinatorial logic.

**HWDATAM** valid after 36% of **HCLK** period because of delays on **DOUT**.

**HREADYM** requires 30% of **HCLK** period as setup in order to create clock enable for ARM core

ARM7S HTRANS valid after 50% of HCLK period because of output delays on TRANS plus combinatorial logic.

**HWDATAM** valid after 35% of **HCLK** period because of delays on **DOUT**.

**HREADY** requires 30% of **HCLK** period as setup to create clock enable for ARM core

ARM720T HTRANSM and HBUSREQM are generated from BTRAN and AREQ, respectively. Each of these signals is generated from the falling edge of HCLK. HTRANSM and HBUSREQM do not become valid until very late in the HCLK cycle. HTRANSM and HBUSREQM are constrained in the supplied synthesis scripts, and are valid within 80% of HCLK period after the rising edge of HCLK.

**HWDATAM** valid after 50% of **HCLK** period because of output delays on **BD**.

**ARM920T HADDRM** valid after 42% of **HCLK** period because of complex combinatorial logic.

HTRANSM valid after 48% of HCLK period because of output delays on NCMAHB and LOK.

**HREADYM** requires 30% of **HCLK** period as setup because of complex combinatorial paths.

## 1.3 Use of ETM and coprocessor interfaces

The CPU AHB wrappers are designed to interface purely between the bus interface of the CPU and the AHB bus (the exception is the ARM7TDMI AHB wrapper which also contains test logic for all core pins). All other interfaces on the CPUs are unaffected by the AHB wrappers. Because of this, interfacing to the ETM or coprocessor ports must be carried out in exactly the same way as for a design which does not include the AHB wrapper.

Each AHB wrapper HDL release includes a top-level file which instantiates both the ARM CPU core and the AHB wrapper. These top-level files are intended as examples only, and are provided to enable use of the supplied synthesis scripts. If used in a design, they must be modified to allow tie-off and connection of the non-AHB wrapper related pins as appropriate.

Introduction

## Chapter 2 ARM720T AHB Wrapper

This chapter describes the ARM720T and ARM740T processor core wrappers that you can use with an AHB-based EASY system. It contains the following sections:

- About the ARM720T AHB wrapper on page 2-2

- Signal interface on page 2-3

- Description of the ARM720T wrapper blocks on page 2-6

- Non-standard design practices on page 2-15

- *Programmer's model exceptions* on page 2-17.

## 2.1 About the ARM720T AHB wrapper

The ARM720T AHB wrapper module interfaces between the ARM720T core and the AHB. This wrapper can also be used with the following cores:

- ARM710T

- ARM740T.

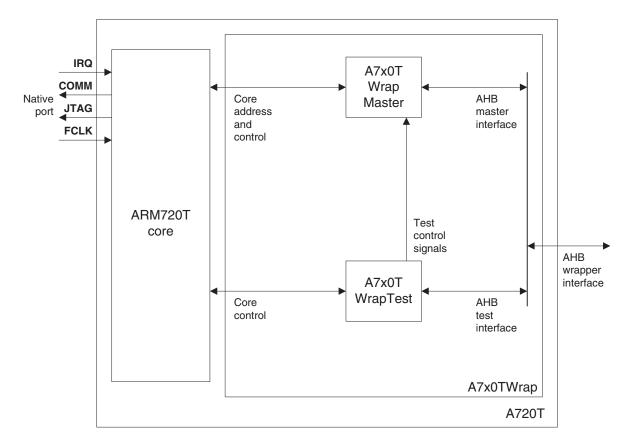

The top-level block diagram is shown in Figure 2-1, which shows how the wrapper interfaces to the ARM720T. The AHB input signals are routed through the wrapper before becoming inputs to the ARM720T. The outputs are also routed through the wrapper before being driven onto the AHB.

#### Figure 2-1 ARM720T AHB AMBA wrapper block diagram

## 2.2 Signal interface

The ARM720T AHB wrapper contains both AHB master and AHB slave interfaces. The master interface is used during normal system operation. The slave interface is used during testing of the ARM720T when the *Test Interface Controller* (TIC) is acting as the current AHB bus master.

This section describes the signal interface of A720TWrap. It does not describe the ARM720T. Only those signals from the ARM720T core that are used by the AHB wrapper are described. All other core signals (for example, coprocessor interface and interrupt inputs) must be connected to the external system in the same way as for an ASB-native design. See the *ARM720T Datasheet* for the relevant information.

Table 2-1 describes the signals used by the ARM720T AHB wrapper.

| Signal         | Direction | Description                                                                                                                                                                                                                                                                               |

|----------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System inputs  |           |                                                                                                                                                                                                                                                                                           |

| HCLK           | Input     | Bus clock. This clock times all bus transfers. All signal timings are related to the rising edge of <b>HCLK</b> .                                                                                                                                                                         |

| HRESETn        | Input     | Reset. The bus reset signal is active LOW and is used to reset the system and the bus. This is the only active LOW AHB signal.                                                                                                                                                            |

| Master inputs  |           |                                                                                                                                                                                                                                                                                           |

| HRDATAM[31:0]  | Input     | Read data bus. Used to transfer data to the ARM720T in master mode.                                                                                                                                                                                                                       |

| HREADYM        | Input     | Transfer done. When HIGH the <b>HREADYM</b> signal indicates that a transfer has finished on the bus. This signal can be driven LOW to extend a transfer.                                                                                                                                 |

| HRESPM[1:0]    | Input     | Transfer response. Indicates an OKAY, ERROR, RETRY, or SPLIT response.                                                                                                                                                                                                                    |

| HGRANTM        | Input     | Bus grant. Indicates that the ARM720T is currently the highest priority master.<br>Ownership of the address/control signals changes at the end of a transfer when<br><b>HREADYM</b> is HIGH, so a master gains access to the bus when both <b>HREADYM</b><br>and <b>HGRANTM</b> are HIGH. |

| Master outputs |           |                                                                                                                                                                                                                                                                                           |

| HADDRM[31:0]   | Output    | This is the 32-bit system address bus.                                                                                                                                                                                                                                                    |

| HTRANSM[1:0]   | Output    | Transfer type. Indicates the type of the current transfer, which can be NONSEQUENTIAL, SEQUENTIAL, or IDLE.                                                                                                                                                                               |

| HWRITEM        | Output    | Transfer direction. When HIGH this signal indicates a write transfer and when LOW a read transfer.                                                                                                                                                                                        |

#### Table 2-1 ARM720T AHB signal descriptions

#### Table 2-1 ARM720T AHB signal descriptions (continued)

| Signal        | Direction | Description                                                                                                                                                                                                                          |

|---------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HSIZEM[2:0]   | Output    | Transfer size. Indicates the size of the transfer, which can be byte (8-bit), halfword (16-bit), or word (32-bit).                                                                                                                   |

| HBURSTM[2:0]  | Output    | Burst type. Indicates if the transfer forms part of a burst. The ARM720T only performs incrementing bursts of type INCR.                                                                                                             |

| HPROTM[3:0]   | Output    | Protection control. These signals indicate if the transfer is an opcode fetch or data access, and if the transfer is a Supervisor mode access or User mode access. This is not supported by the ARM720T wrapper, and is always 0000. |

| HWDATAM[31:0] | Output    | Write data bus. Used to transfer data from the ARM720T in master mode.                                                                                                                                                               |

| HBUSREQM      | Output    | Bus request. A signal from the wrapper to the bus arbiter which indicates that it requires the bus.                                                                                                                                  |

| НЬОСКМ        | Output    | Locked transfers. When HIGH this signal indicates that the master requires locked access to the bus and no other master must be granted the bus until this signal is LOW.                                                            |

| Slave inputs  |           |                                                                                                                                                                                                                                      |

| HSELS         | Input     | This signal selects the ARM720T as slave.                                                                                                                                                                                            |

| HWRITES       | Input     | Transfer direction. When HIGH this signal indicates a write transfer and when LOW a read transfer.                                                                                                                                   |

| HTRANS1S      | Input     | Transfer type. This is attached to bit 1 of the AHB <b>HTRANS[1:0]</b> bus. It indicates an active (NONSEQ or SEQ) or inactive (IDLE or BUSY) transfer.                                                                              |

| HWDATAS[31:0] | Input     | Write data bus. Used to transfer data to the ARM720T in slave mode.                                                                                                                                                                  |

| HREADYS       | Input     | Transfer done. Indicates that the current transfer on the AHB is finished.                                                                                                                                                           |

| Slave outputs |           |                                                                                                                                                                                                                                      |

| HRDATAS[31:0] | Output    | Read data bus. Used to transfer data from the ARM720T in slave mode.                                                                                                                                                                 |

| HREADYOUTS    | Output    | Transfer done. In test mode, this signal indicates when a transfer can complete.                                                                                                                                                     |

| HRESPS[1:0]   | Output    | Transfer response. Indicates a fixed OKAY response.                                                                                                                                                                                  |

Table 2-2 on page 2-5 describes the signals to the ARM720T core.

### Table 2-2 Signals to ARM720T core

| Signal     | Direction    | Description                                                                                                                                                                                                                                      |

|------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BCLK       | Output       | Bus clock. This times all transfers to and from the ARM720T.                                                                                                                                                                                     |

| BnRES      | Output       | Bus reset signal which is active LOW.                                                                                                                                                                                                            |

| BERROR     | Output       | Error response. Not supported. <b>BERROR</b> is LOW and a fixed OKAY response is supplied.                                                                                                                                                       |

| BLAST      | Output       | Last response. Not supported. <b>BLAST</b> is LOW and a fixed continue burst response is supplied.                                                                                                                                               |

| BWAIT      | Output       | Wait response. Fixed for zero wait state response, <b>BWAIT</b> is LOW. Wait states are controlled by gating <b>BCLK</b> to the ARM720T.                                                                                                         |

| AREQ       | Input        | Bus request. Indicates the ARM720T is requesting the bus.                                                                                                                                                                                        |

| BA[31:0]   | Input        | This is the 32-bit system address bus.                                                                                                                                                                                                           |

| BLOK       | Input        | Locked transfer. The ARM720T requires a locked bus transfer during a SWP instruction.                                                                                                                                                            |

| BSIZE[1:0] | Input        | Transfer size. Indicates the size of the transfer, which is either byte (8-bit), halfword (16-bit) or word (32-bit).                                                                                                                             |

| BTRAN[1:0] | Input        | Transfer type. Indicates the type of the current transfer, which can be NONSEQUENTIAL, SEQUENTIAL, or ADDRESS-ONLY.                                                                                                                              |

| BWRITE     | Input/output | Transfer direction. When HIGH this signal indicates a write transfer and when LOW a read transfer. During test this signal is driven by the wrapper. During normal operation, it is driven by the ARM720T core.                                  |

| BD[31:0]   | Input/output | Data bus. For master mode write <b>BD</b> is connected to <b>HWDATAM</b> and read <b>BD</b> is connected to <b>HRDATAM</b> .<br>For test mode write <b>BD</b> is connected to <b>HWDATAS</b> and read <b>BD</b> is connected to <b>HRDATAS</b> . |

| AGNTarm    | Output       | Bus grant. In test mode this signal degrants the ARM720T the use of the bus. This is set LOW by the test wrapper state machine.                                                                                                                  |

| DSEL       | Output       | Slave select. In test mode this signal selects the ARM720T as slave. This is set HIGH by the test wrapper state machine.                                                                                                                         |

## 2.3 Description of the ARM720T wrapper blocks

This section contains descriptions of the following blocks:

- A720T

- *A7x0TWrap*

- A7x0TWrapMaster

- A7x0TWrapTest on page 2-11.

#### 2.3.1 A720T

This is the top-level wrapper which contains A7x0TWrap, and the ARM720T core instantiated as a C model. This wrapper is connected to all native core signals that are not part of the AMBA bus. This allows the wrapper to be easily extracted after RTL simulation for logic synthesis.

#### 2.3.2 A7x0TWrap

This wrapper is used to bind the A7x0TWrapMaster block and the A7x0TWrapTest block. It provides a two-port interface that connects, on one side both the master and test mode interfaces directly to the AHB system, and on the other side it connects directly to the native ASB interface of the core.

#### 2.3.3 A7x0TWrapMaster

This block handles all the bus interface requirements when the ARM720T is acting as a bus master.

There are eight main sections to this block:

- Main state machine

- Address generation on page 2-9

- HTRANSM generation on page 2-10

- *HLOCKM generation* on page 2-10

- *Clock generation* on page 2-10

- *Holding registers* on page 2-10

- *BD generation* on page 2-11

- *BWAIT, BERROR, and BLAST generation* on page 2-11.

#### Main state machine

The main state machine controls the majority of the functionality of the wrapper and indicates:

• whether the master is granted the use of the bus

- whether the ARM720T needs to perform a transfer

- when a transfer has received a SPLIT or RETRY response.

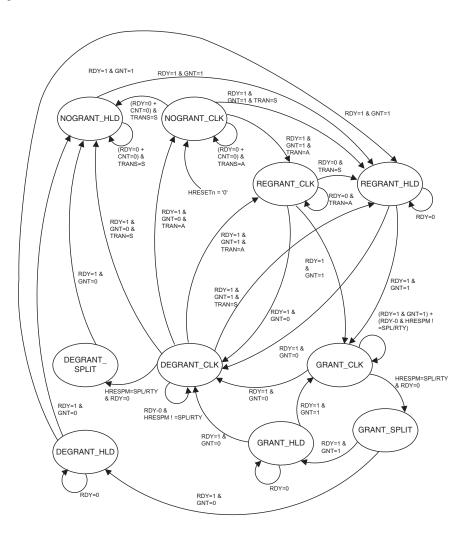

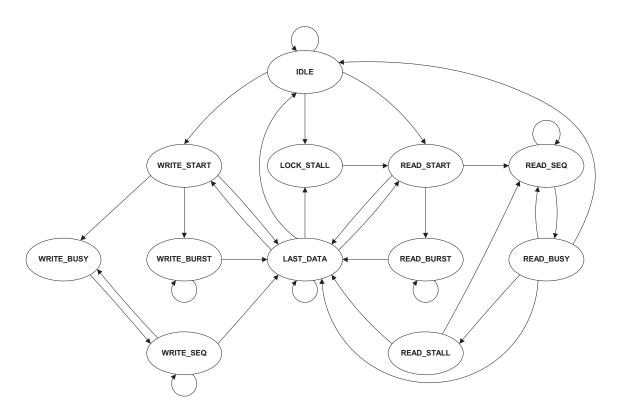

Figure 2-2 shows the main state machine.

Figure 2-2 ARM720T AHB wrapper main state machine

There are ten states:

#### NOGRANT\_CLK

This state indicates that the ARM720T is not granted use of the bus, but as it does not require the bus to perform a transfer, it can be clocked. When in this state, if the ARM720T has to perform a transfer, it moves to the NOGRANT\_HLD state to prevent clocking until it is granted use of the bus.

#### NOGRANT\_HLD

In this state the ARM720T is not granted use of the bus and wishes to perform a transfer, so it is not clocked. The ARM720T remains in this state until it is granted the bus and moves to the REGRANT\_HLD state.

#### **REGRANT\_CLK**

The two REGRANT states are entered when the ARM720T is first granted use of the bus and the ARM720T has ownership of the address/control signals, but does not yet have ownership of the data bus. In the REGRANT\_CLK state the ARM720T does not have to perform a transfer and therefore it can be clocked.

#### **REGRANT\_HLD**

The REGRANT\_HLD state is similar to the REGRANT\_CLK state as it is entered when the ARM720T is first granted the bus. However, in this state the ARM720T has to perform a transfer and therefore cannot be clocked.

#### GRANT\_CLK

The GRANT\_CLK state is the usual state when the ARM720T is granted the bus. The ARM720T is clocked whenever the **HREADYM** signal is HIGH and is not clocked when wait states are inserted on the bus by the slave driving **HREADYM** LOW.

The GRANT\_CLK state is exited in two ways:

- if the ARM720T loses ownership of the bus then the state machine moves to the DEGRANT\_CLK state

- if a transfer that is being performed receives either a SPLIT or RETRY response then the GRANT\_SPLIT state is entered.

#### GRANT\_SPLIT

This state is entered when a transfer receives either a SPLIT or RETRY response. In this state the wrapper forces an IDLE transfer on to the bus to cancel the following transfer. The GRANT\_SPLIT state is only ever

occupied for a single cycle and is followed either by the GRANT\_HLD state if the ARM720T remains granted on the bus. Alternatively, it exits to the DEGRANT\_HLD state if ownership of the bus is lost.

#### GRANT\_HLD

This state indicates second stage of a SPLIT or RETRY transfer. In this state the wrapper drives out the address and control signals in the holding register in order to restart the transfer that received the SPLIT or RETRY response.

#### DEGRANT\_CLK

The DEGRANT states indicate the ARM720T is losing ownership of the bus, but the last access is still completing. In the DEGRANT\_CLK state the ARM720T is clocked according to the level of the **HREADYM** signal.

#### DEGRANT\_SPLIT

This state is only entered when the last transfer on the bus receives a SPLIT response.

#### DEGRANT\_HLD

This state is only entered when ownership of the bus is lost just after a transfer receives either a SPLIT or RETRY response. In this state the ARM720T is not clocked as it must repeat the transfer that received a SPLIT or RETRY response before it can be clocked.

#### **Address generation**

The address generation logic has three sources for the address of the next transfer:

- A registered version of the address from the ARM720T, **BA**. This source of the address is used when the ARM720T performs an ADDRESS-ONLY transfer and effectively reloads the address generation logic with a new address.

- The same as the current transfer. This address source is used when wait states are inserted on the bus.

- An incremented version of the current address. The size of the increment (either +2 or +4) depends on the size of the current transfer. This source of the address is used when the ARM720T is performing a SEQUENTIAL transfer.

#### **HTRANSM** generation

The **HTRANSM** signals are generated from the **BTRANS** signals from the ARM720T. The signals from the ARM720T are modified when:

- the transfer source is from the holding registers then the transfer type is forced to be NONSEQUENTIAL

- the current transfer receives either a SPLIT or RETRY response then the next transfer is canceled by forcing **HTRANSM** to IDLE

- the current transfer is the first in a burst then the transfer type is forced to NONSEQUENTIAL.

#### **HLOCKM** generation

The **HLOCKM** signal on the bus is generated directly from the **BLOK** signal. The ARM is stalled during the first cycle of a locked transfer to ensure that the **HLOCKM** signal is always asserted a cycle prior to the locked transfer being started on the bus. This is required to meet the AHB specification and allow sufficient time for the arbiter to ensure that the ARM720T has locked access to the bus.

#### **Clock generation**

The clock generation logic is used to modify the **BCLK** signal to the ARM720T. The ARM720T clock is removed when:

- the current transfer is waited because the slave has driven HREADYM LOW

- the current transfer receives either a SPLIT or RETRY response

- the ARM is not granted the bus, but wishes to perform a transfer.

#### **Holding registers**

The address and control signal holding registers are used to store the address and control information for the current transfer. This information is required if the transfer receives either a SPLIT or RETRY response and must be restarted.

The holding registers are also used when the ARM720T loses ownership of the bus. In this case the core has to be clocked to complete the final transfer on the bus, but the address from the ARM720T is not driven onto the bus for the next transfer. Therefore the holding registers are used to store the address until the ARM720T is next granted use of the bus.

#### **BD** generation

Because the ARM720T has a single bidirectional data bus, the wrapper is required to combine the AHB read and write data buses. The wrapper does this by only driving the read data, **HRDATAM**, on to **BD** during read transfers. At all other times during normal operation the wrapper does not drive **BD**, avoiding bus clash when the ARM720T drives data on to **BD** for write transfers.

#### **BWAIT, BERROR, and BLAST generation**

During normal operation **BWAIT**, **BERROR**, and **BLAST** are all driven LOW. These signals are not required because:

- the wait state control is provided by gating the main clock, **BCLK**, to the ARM720T

- the AHB wrapper does not support ERROR responses from the system, because the ARM720T is expected to make use of the memory management and protection unit provided with the ARM720T.

These signals are all driven by tristate buffers so that they can be set to high impedance during test mode when the ARM720T becomes a bus slave and drives these signals.

#### 2.3.4 A7x0TWrapTest

This block handles all the bus interface requirements when the ARM720T is operating in test mode. Its main functions are to ensure a clean entry and exit from the test mode, and to maintain synchronization between the TIC interface and the embedded test mode state machine within the ARM720T.

There are two main sections to this block:

- Test state machine

- *Test logic output* on page 2-14.

#### Test state machine

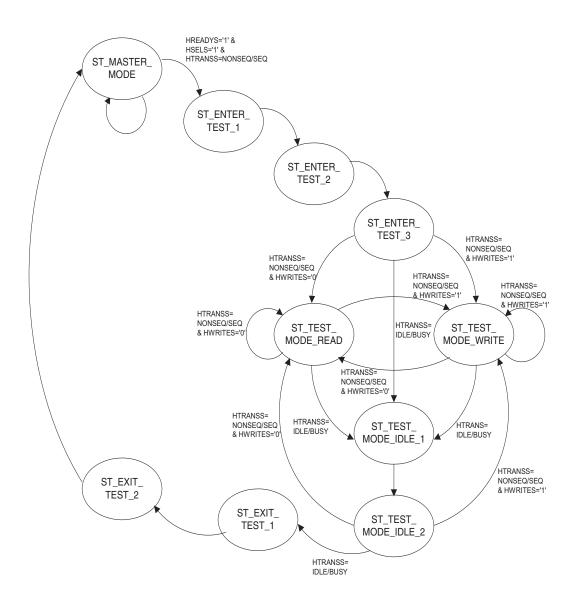

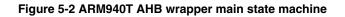

A test state machine is used as the central controller to provide control of the AHB bus for all test mode transaction types.

Figure 2-3 on page 2-12 shows the test state machine.

Figure 2-3 Test state machine

There are ten states in the test state machine:

#### ST\_MASTER\_MODE

This is the IDLE state for the test state machine. During this state the ARM720T is acting as a bus master and the test logic is disabled. This state is exited when the first transfer of a test sequence is detected.

#### ST\_ENTER\_TEST\_1

This is the first state on the entry into test and during this state the **AGNTarm** signal is removed from the ARM720T.

#### ST\_ENTER\_TEST\_2

During the second state on entry in to test the ARM720T clock is enabled so that the ARM720T becomes degranted and tristates all the output signals that must become inputs for test.

#### ST\_ENTER\_TEST\_3

During the third state on entry in to test the **BWRITE** signal to the ARM720T becomes driven from the test wrapper.

#### ST\_TEST\_MODE\_WRITE

This state is entered whenever a WRITE transfer to the ARM720T is being performed. During this state the **HWDATAS** is driven on to the bidirectional data bus (**BD**) of the ARM720T.

#### ST\_TEST\_MODE\_READ

In this state a READ transfer from the ARM720T occurs. During this state the bidirectional data bus (**BD**) of the ARM720T is driven on to **HRDATAS**.

#### ST\_TEST\_MODE\_IDLE\_1

This state is the first of two IDLE states that occur when the ARM720T is moving between READ and WRITE transfers.

#### ST\_TEST\_MODE\_IDLE\_2

This state is the second of two IDLE states that occur when the ARM720T is moving between READ and WRITE transfers. If this state is followed by another IDLE transfer then this indicates the end of the test process and the next state will be ST\_EXIT\_TEST\_1, otherwise this state is followed by a READ or WRITE transfer.

#### ST\_EXIT\_TEST\_1

In the first exit from test state, the signals that are driven from the wrapper during test become tristate.

#### ST\_EXIT\_TEST\_2

In the second exit from test state, the ARM720T is regranted as a bus master by driving **AGNTarm** HIGH. After this state the ARM720T returns to the ST\_MASTER\_MODE state which indicates that the ARM720T has returned to normal operation.

#### Test logic output

The output signals generated from the test state machine are:

- AGNTarm This signal is driven LOW throughout the test process to degrant the ARM720T so that it can be tested as a slave.

- **TestEnable** This signal is used to clock the core throughout the test process. The ARM720T is always clocked except in the ST\_TEST\_MODE\_IDLE\_2 state.

- SelArmTest The tristate control of signals, such as BWAIT, BERROR, and BLAST is controlled by the SelArmTest signal. This ensures that the wrapper does not drive these signals during test when the ARM720T is driving them to respond to slave transfers.

- DSEL The DSEL select signal to the core is generated from the test state machine before the ST\_TEST\_MODE\_READ or ST\_TEST\_MODE\_WRITE states. A transparent latch is used in the generation of the DSEL signal to allow for designs that have late HTRANSS timing. In low speed designs it is possible to replace this latch with a falling edge register.

- **BWRITE** The write signal to the ARM720T is generated from the **HWRITES** signal and is a tristate signal which is only driven during test. The write signal must be timed with reference to the rising edge of **BCLK** and therefore a falling edge **HCLK** register must be used to generate this signal.

- **BD** The bidirectional data bus to the ARM720T is driven with the write data, **HWDATAS**, during write transfers to the ARM720T.

#### HREADYOUTS

The **HREADYOUTS** signal is used to insert wait states on the bus during transfers to the test wrapper. Wait states are only required during the entry in to test and at all other times during the test process transfers receive a zero wait state OKAY response.

- **HRESPS** The response signals are fixed to provide an OKAY response.

- **HRDATAS** During test read transfers the data from **BD** must be driven on to **HRDATAS**. At all other times this bus is driven LOW to prevent unnecessary toggling.

## 2.4 Non-standard design practices

The following non-standard design practices are described:

- Clock gating

- Transparent latches

- *Tristate drivers* on page 2-16.

#### 2.4.1 Clock gating

A clock inverter is instantiated within A7x0TWrap (instance name *uClockInv*) to provide **nHCLK** (inverted **HCLK**). This signal is used in the following places:

#### A7x0TWrapMaster

Creation of **BclkEn**, the enable term for **BCLK**.

A7x0TWrapTest Creation of DriveBwrite and Write, the tristate enable and value used to create **BWRITE**.

An inverted version of the clock is used so that all HDL code describes only rising-edge sequential logic. This is done because some cell libraries do not contain falling-edge registers, and also to avoid possible insertion of unwanted clock gating during synthesis.

A clock NAND gate is used within A7x0TWrapMaster (instance name *uClockNand*) to create **BCLK**, the bus clock for the ASB interface of the ARM720T.

The clock gates are described in the design block ClockInv and ClockNand. The methodology chosen within the supplied synthesis scripts synthesizes these blocks first, sets them as *dont\_touch*, and then links them in when synthesizing the wrapper. This ensures that the clock gate instances have known references, and also prevents the optimization routines during later synthesis from altering the gates.

#### 2.4.2 Transparent latches

A transparent latch is instantiated within A7x0TWrapMaster (instance name *uLATS*). This is used to create **BclkEn**, the enable term for **BCLK**. The latch operation is described in the design block LATS (transparent latch with asynchronous set).

A transparent latch is instantiated within A7x0TWrapTest (instance name *uLATR*). This is used to create **DSEL**, the slave select signal for the ARM720T core. The latch operation is described in the design block LATR (transparent latch with asynchronous reset).

The synthesis methodology for the latch blocks is the same as for the clock gates described above.

#### 2.4.3 Tristate drivers

Tristate drivers are used within the wrapper:

- in A7x0TWrap, a tristate driver can be found for **BDOUT**

- in A7x0TWrapTest, tristate drivers can be found for **BWAIT**, **BLAST**, **BERROR**, and **BWRITE**.

Most ASIC design flows require Buskeepers to be added to any signals that might be tristated. For the A7x0T wrapper, the following signals must have Buskeepers added:

- BA

- BLOK

- BSIZE

- BPROT

- BTRAN

- **BWRITE**

- BD

- BWAIT

- BERROR

- BLAST

- CPdata.

## 2.5 Programmer's model exceptions

The ARM720T AHB wrapper does not support the ERROR response on **HRESP**. This means that instruction and data aborts are not supported.

ARM720T AHB Wrapper

## Chapter 3 ARM7TDMI AHB Wrapper

This chapter describes the ARM7TDMI and ARM7TDMI-S processor core wrapper that you can use with an AHB-based EASY system. It contains the following sections:

- About the ARM7TDMI AHB wrapper on page 3-2

- Signal interface on page 3-4

- Description of the ARM7TDMI wrapper blocks on page 3-15

- Non-standard design practices on page 3-27.

## 3.1 About the ARM7TDMI AHB wrapper

The ARM7TDMI AHB wrapper interfaces between the ARM7TDMI or ARM7TDMI-S core and the AHB bus. The modules that translate access from the core to AHB accesses when the core is the current master are common to both cores. The wrapper itself sits alongside the core, intercepting the memory bus. An example higher-level module is also included for each core. This shows how the core and wrapper can be connected, and is used by the synthesis scripts provided to allow the wrapper to be synthesized alongside a timing file for the core.

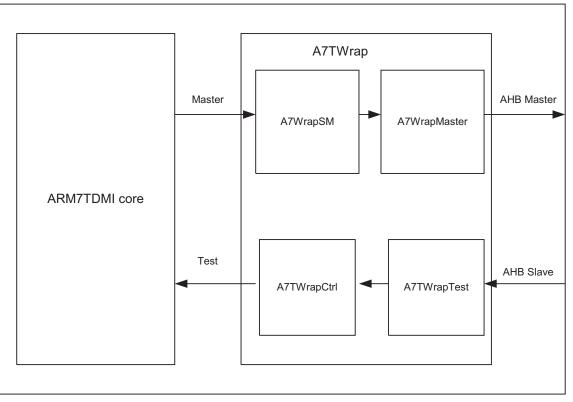

For the ARM7TDMI only, the wrapper also allows testing of the ARM7TDMI core when the *Test Interface Controller* (TIC) is the current AHB master, allowing the TIF-format production test vectors supplied by ARM to be used with AHB-based designs. Figure 3-1 shows a top-level block diagram of the ARM7TDMI AHB wrapper.

A7TDMI

#### Figure 3-1 ARM7TDMI AHB wrapper block diagram

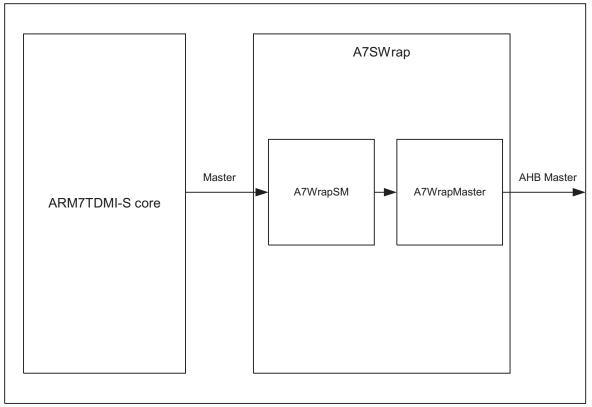

Figure 3-2 shows a top-level block diagram of the ARM7TDMI-S AHB wrapper.

A7SAHB

Figure 3-2 ARM7TDMI-S AHB wrapper block diagram

## 3.2 Signal interface

The ARM7 signals are described in the following sections:

- A7TWrap signals

- A7SWrap signals on page 3-11.

#### 3.2.1 A7TWrap signals

This section describes the signal interface of A7TWrap. It does not describe the ARM7TDMI. Only those signals from the ARM7TDMI core that are used by the AHB wrapper are described. All other core signals must be connected to the external system in the same way as for a native core design. See the *ARM7TDMI Datasheet* for the relevant information.

— Note —

The exception is **DOUT[31:0**], which must be connected directly to the **HWDATA[31:0**] AHB bus and the **DOUT[31:0**] input on A7TWrap.

Table 3-1 describes the signals used by the ARM7TDMI AHB wrapper.

| Signal                                                                 | Direction | Description                                                                                                                                                                                                                                                                                |  |

|------------------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| System inputs                                                          |           |                                                                                                                                                                                                                                                                                            |  |

| HCLK                                                                   | Input     | Bus clock. This clock times all bus transfers. All signal timings are related to the rising edge of <b>HCLK</b> .                                                                                                                                                                          |  |

| HRESETn                                                                | Input     | Reset. The bus reset signal is active LOW and is used to reset the system and the bus. This is the only active LOW AHB signal.                                                                                                                                                             |  |

| Master inputs                                                          |           |                                                                                                                                                                                                                                                                                            |  |

| HRDATAM[31:0]                                                          | Input     | Read data bus. Used to transfer data to the ARM7TDMI in master mode.                                                                                                                                                                                                                       |  |

| HREADYM                                                                | Input     | Transfer done. When HIGH, the <b>HREADYM</b> signal indicates that a transfer has finished on the bus. This signal can be driven LOW to extend a transfer.                                                                                                                                 |  |

| HRESPM[1:0]                                                            | Input     | Transfer response. Indicates an OKAY, ERROR, RETRY, or SPLIT response.                                                                                                                                                                                                                     |  |

| Ownership of the address/control signals changes at the end of a trans |           | Bus grant. Indicates that the ARM7TDMI is currently the highest priority master.<br>Ownership of the address/control signals changes at the end of a transfer when<br><b>HREADYM</b> is HIGH, so a master gains access to the bus when both <b>HREADYM</b><br>and <b>HGRANTM</b> are HIGH. |  |

#### Table 3-1 ARM7TDMI AHB signal descriptions

| Signal Direction Description |        | Description                                                                                                                                                               |  |

|------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Master outputs               |        |                                                                                                                                                                           |  |

| HADDRM[31:0]                 | Output | This is the 32-bit system address bus.                                                                                                                                    |  |

| HTRANSM[1:0]                 | Output | Transfer type. Indicates the type of the current transfer, that can be NONSEQUENTIAL, SEQUENTIAL, or IDLE.                                                                |  |

| HWRITEM                      | Output | Transfer direction. When HIGH, this signal indicates a write transfer and when LOW a read transfer.                                                                       |  |

| HSIZEM[2:0]                  | Output | Transfer size. Indicates the size of the transfer, that can be byte (8-bit), halfword (16-bit), or word (32-bit).                                                         |  |

| HBURSTM[2:0]                 | Output | Burst type. This signal indicates if the transfer forms part of a burst. The ARM7TDMI performs incrementing bursts of type INCR.                                          |  |

| HPROTM[3:0]                  | Output | Protection control. These signals indicate if the transfer is an opcode fetch or data access, and if the transfer is a Supervisor mode access or User mode access.        |  |

| HBUSREQM                     | Output | Bus request. A signal from the wrapper to the bus arbiter that indicates that it requires the bus.                                                                        |  |

| HLOCKM                       | Output | Locked transfer. When HIGH, this signal indicates that the master requires locked access to the bus and no other master must be granted the bus until this signal is LOW. |  |

| Slave inputs                 |        |                                                                                                                                                                           |  |

| HTRANS1S                     | Input  | Transfer type. This is attached to bit 1 of the AHB <b>HTRANS[1:0]</b> bus. It indicate an active (NONSEQ or SEQ) or inactive (IDLE or BUSY) transfer.                    |  |

| HWRITES                      | Input  | Transfer direction. When HIGH, this signal indicates a write transfer and when LOW a read transfer.                                                                       |  |

| HWDATAS[31:0]                | Input  | Write data bus. Used to transfer data to the ARM7TDMI in slave mode.                                                                                                      |  |

| HSELS                        | Input  | Slave select. Selects the ARM7TDMI as slave.                                                                                                                              |  |

| HREADYS                      | Input  | Transfer done. When HIGH, this signal indicates that a transfer has finished on the bus. This signal can be driven LOW to extend a transfer.                              |  |

| Slave outputs                |        |                                                                                                                                                                           |  |

| HRDATAS[31:0]                | Output | Read data bus. Used to transfer data from the ARM7TDMI in slave mode.                                                                                                     |  |

| HREADYOUTS                   | Output | Transfer done. When HIGH, this signal indicates that a transfer to the ARM7TDMI has finished. This signal can be driven LOW to extend a transfer.                         |  |

| HRESPS[1:0]                  | Output | Transfer response. Indicates an OKAY, ERROR, RETRY, or SPLIT response. The ARM7TDMI always responds with OKAY.                                                            |  |

#### Table 3-1 ARM7TDMI AHB signal descriptions (continued)

#### Table 3-2 describes the signals to the ARM7TDMI core.

## Table 3-2 Signals to ARM7TDMI core

| Signal             | Direction | Description                                                                                                                                                                                                                                  |  |

|--------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Shared master/slav | e signals |                                                                                                                                                                                                                                              |  |

| nRESET             | Output    | Active LOW reset to core.                                                                                                                                                                                                                    |  |

| MCLK               | Output    | Core clock for ARM7TDMI.                                                                                                                                                                                                                     |  |

| DIN[31:0]          | Output    | Data bus. For master mode this is connected to <b>HRDATAM</b> , for test mode it is connected to <b>HWDATAS</b> .                                                                                                                            |  |

| DOUT[31:0]         | Input     | Data bus. For master mode this is connected to <b>HWDATAM</b> , for test mode it is connected to <b>HRDATAS</b> .                                                                                                                            |  |

| Master inputs      |           |                                                                                                                                                                                                                                              |  |

| A[31:0]            | Input     | Address bus                                                                                                                                                                                                                                  |  |

| LOCK               | Input     | Indicates a locked transfer (such as SWP).                                                                                                                                                                                                   |  |

| MAS[1:0]           | Input     | Transfer size. Indicates the size of the transfer, which is typically byte (8-bit), halfword (16-bit) or word (32-bit).                                                                                                                      |  |

| nMREQ              | Input     | Not memory access.                                                                                                                                                                                                                           |  |

| nOPC               | Input     | Not opcode access.                                                                                                                                                                                                                           |  |

| nRW                | Input     | Not read/write.                                                                                                                                                                                                                              |  |

| nTRANS             | Input     | Not memory translate. When LOW, this signal indicates that the processor is in user mode.                                                                                                                                                    |  |

| SEQ                | Input     | Sequential access.                                                                                                                                                                                                                           |  |

| Master outputs     |           |                                                                                                                                                                                                                                              |  |

| ABORT              | Output    | Indicates that an access has aborted (that is, received an ERROR response on the AHB).                                                                                                                                                       |  |

| nFIQ               | Output    | Fast interrupt request.                                                                                                                                                                                                                      |  |

| nIRQ               | Output    | Standard interrupt request.                                                                                                                                                                                                                  |  |

| nWAIT              | Output    | Indicates that current access is waited.                                                                                                                                                                                                     |  |

| Test inputs        |           |                                                                                                                                                                                                                                              |  |

| BUSDIS             | Input     | Bus disable. When INTEST is selected on scan chain 0, 4, or 8 this is HIGH. It can be used to disable external logic driving onto the bidirectional data bus during scan testing. This signal changes after the falling edge of <b>TCK</b> . |  |

#### Description Signal Direction **COMMRX** Input When the communications channel receive buffer is full this is HIGH. This signal changes after the rising edge of MCLK. COMMTX Input When the communications channel transmit buffer is empty this is HIGH. This signal changes after the rising edge of MCLK. DBGACK Input Debug acknowledge. When the processor is in a debug state this is HIGH. DBROI Internal debug request. This is the logical OR of **DBGRQ** and bit 1 of the debug Input control register. HIGHZ Input When the HIGHZ instruction has been loaded into the TAP controller this signal is HIGH. **RANGEOUT0** EmbeddedICE macrocell. When the EmbeddedICE watchpoint unit 0 has matched Input the conditions currently present on the address, data, and control buses, then this is HIGH. This signal is independent of the state of the watchpoint enable control bit. RANGEOUT1 Input EmbeddedICE macrocell. As RANGEOUT0 but corresponds to the EmbeddedICE watchpoint unit 1. nCPI Input Not coprocessor instruction. LOW when a coprocessor instruction is processed. The processor then waits for a response from the coprocessor on the CPA and CPB lines. If **CPA** is HIGH when **MCLK** rises after a request has been initiated by the processor, then the coprocessor handshake is aborted, and the processor enters the undefined instruction trap. If CPA is LOW at this time, the processor enters a busy-wait period until CPB goes LOW before completing the coprocessor handshake. **nENOUT** Input Not enable output. During a write cycle, this signal is driven LOW before the rising edge of MCLK, and remains LOW for the entire cycle. This can be used to aid arbitration in shared bus applications. **nENOUTI** Input Not enable output. During a write cycle, this signal is driven LOW before the rising edge of MCLK, and remains LOW for the entire cycle. This can be used to aid arbitration in shared bus applications. nEXEC Input Not executed. This is HIGH when the instruction in the execution unit is not being executed because, for example, it has failed its condition code check. nM[4:0] Input Not processor mode. These are the inverse of the internal status bits indicating the current processor mode. **nTDOEN** Input Not **TDO** enable. When serial data is being driven out on **TDO** this is LOW. Usually used as an output enable for a **TDO** pin in a packaged part.

| Signal        | Direction Description |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|---------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SCREG[3:0]    | Input                 | Scan chain register. These reflect the ID number of the scan chain currently selected by the TAP controller. These change on the falling edge of <b>TCK</b> when the TAP state machine is in the UPDATE-DR state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| TBIT          | Input                 | Thumb state. When the processor is executing the THUMB instruction set, this is HIGH. It is LOW when executing the ARM instruction set. This signal changes in phase two in the first execute cycle of a BX instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| xnTRST        | Input                 | JTAG reset input from external tester.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| xTCK          | Input                 | JTAG clock input from external tester.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| xTDI          | Input                 | JTAG data input from external tester.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| xTMS          | Input                 | JTAG mode select input from external tester.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| xTDO          | Input                 | JTAG data input from core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

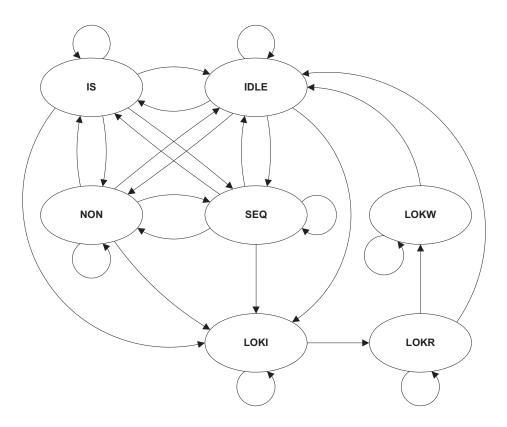

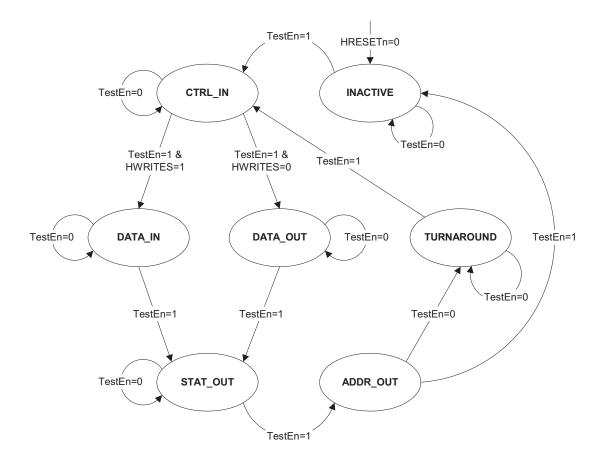

| Slave outputs |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |