# ARM PrimeCell<sup>®</sup> Smart Card Interface (PL130)

**Technical Reference Manual**

Copyright © 1999 ARM Limited. All rights reserved. ARM DDI 0148B

### ARM PrimeCell Smart Card Interface (PL130) Technical Reference Manual

Copyright © 1999 ARM Limited. All rights reserved.

#### **Release Information**

Change history

| Date         | Issue | Confidentiality  | Change          |  |

|--------------|-------|------------------|-----------------|--|

| January 1996 | А     | Non-Confidential | First release.  |  |

| March 1998   | В     | Non-Confidential | Second release. |  |

#### **Proprietary Notice**

Words and logos marked with  $^{\otimes}$  or  $^{\sim}$  are registered trademarks or trademarks of ARM Limited in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

# Contents ARM PrimeCell Smart Card Interface (PL130) Technical Reference Manual

|           |       | About this Technical Reference Manual                |     |

|-----------|-------|------------------------------------------------------|-----|

|           |       | Feedback                                             | xv  |

| Chapter 1 | Intro | duction                                              |     |

| -         | 1.1   | About the ARM PrimeCell Smart Card Interface (PL130) | 1-2 |

|           | 1.2   | AMBA compatibility                                   | 1-6 |

| Chapter 2 | Func  | tional Overview                                      |     |

| -         | 2.1   | ARM PrimeCell Smart Card Interface (PL130) overview  | 2-2 |

|           | 2.2   | PrimeCell SCI functional description                 | 2-4 |

|           | 2.3   | PrimeCell SCI operation                              | 2-9 |

| Chapter 3 | Prog  | rammer's Model                                       |     |

| -         | 3.1   | About the programmer's model                         | 3-2 |

|           | 3.2   | Summary of PrimeCell SCI registers                   |     |

|           | 3.3   | Register descriptions                                | 3-6 |

| Chapter 4 | Prog  | rammer's Model for Test                              |     |

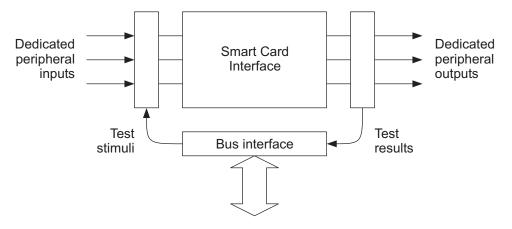

| -         | 4.1   | PrimeCell SCI test harness overview                  | 4-2 |

|           | 4.2   | Scan testing                                         |     |

|           |       |                                                      |     |

|            | 4.3 | Test registers                                            | . 4-4 |

|------------|-----|-----------------------------------------------------------|-------|

| Appendix A | ARM | PrimeCell Smart Card Interface (PL130) Signal Description | ns    |

|            | A.1 | AMBA APB signals                                          | . A-2 |

|            | A.2 | On-chip signals                                           | . A-3 |

|            | A.3 | Signals to pads                                           | . A-5 |

# List of Tables ARM PrimeCell Smart Card Interface (PL130) Technical Reference Manual

|            | Change history                                    | ii   |

|------------|---------------------------------------------------|------|

| Table 2-1  | Initial configuration values                      | 2-11 |

| Table 3-1  | PrimeCell SCI register summary                    | 3-3  |

| Table 3-2  | SCIDATA register read/write bits                  | 3-7  |

| Table 3-3  | SCICR0 register read/write bits                   | 3-8  |

| Table 3-4  | SCICR1 register read/write bits                   |      |

| Table 3-5  | SCICR2 register write bits                        | 3-11 |

| Table 3-6  | SCIIER register read/write bits                   | 3-11 |

| Table 3-7  | SCIRETRY register read/write bits                 | 3-13 |

| Table 3-8  | SCITIDE register read/write bits                  | 3-14 |

| Table 3-9  | SCITXCOUNT/SCITXCOUNTCLR register read/write bits | 3-14 |

| Table 3-10 | SCIRXCOUNT/SCIRXCOUNTCLR register read/write bits | 3-15 |

| Table 3-11 | SCIFR register read bits                          | 3-15 |

| Table 3-12 | SCIRXTIME register read/write bits                | 3-16 |

| Table 3-13 | RXTIME ranges and resolutions                     | 3-16 |

| Table 3-14 | SCIISTAT register read/write bits                 | 3-17 |

| Table 3-15 | SCISTABLE register read/write bits                |      |

| Table 3-16 | SCIATIME register read/write bits                 | 3-19 |

| Table 3-17 | SCIDTIME register read/write bits                 | 3-19 |

| Table 3-18 | SCIATRSTIME register read/write bits              | 3-20 |

| Table 3-19 | SCIATRSTIME register read/write bits              | 3-20 |

| Table 3-20 | SCIBLKTIME register read/write bits    | 3-21 |

|------------|----------------------------------------|------|

| Table 3-21 | SCICHTIME register read/write bits     | 3-22 |

| Table 3-22 | SCICLKICC register read/write bits     | 3-22 |

| Table 3-23 | SCIBAUD register read/write bits       | 3-23 |

| Table 3-24 | SCIVALUE register read/write bits      | 3-23 |

| Table 3-25 | SCICHGUARD register read/write bits    | 3-23 |

| Table 3-26 | SCIVALUE register read/write bits      | 3-24 |

| Table 3-27 | SCIBLKGUARD register read/write bits   | 3-25 |

| Table 3-28 | SCISYNCCR register read/write bits     | 3-25 |

| Table 3-29 | SCISYNCDATA register read/write bits   | 3-26 |

| Table 3-30 | SCIRAWSTAT register read bits          | 3-26 |

| Table 3-31 | SCIIIR/SCIICR register read/write bits | 3-27 |

| Table 4-1  | Test registers memory map              | 4-4  |

| Table 4-2  | SCITCR register read/write bits        | 4-5  |

| Table 4-3  | SCITMR register read/write             | 4-7  |

| Table 4-4  | SCITISR register read/writebits        | 4-7  |

| Table 4-5  | SCITOCR register read bits             | 4-8  |

| Table 4-6  | SCIDATATIME register read bits         | 4-9  |

| Table 4-7  | SCIBAUDCNT register read bits          | 4-9  |

| Table 4-8  | SCIVALUECNT                            | 4-9  |

| Table 4-9  | SCIRTSTBPRECNT register read bits      | 4-9  |

| Table 4-10 | SCIACTTIME register read bits          | 4-10 |

| Table 4-11 | SCICLKICCCNT register read bits        | 4-10 |

| Table 4-12 | SCISTATE register read bits            | 4-10 |

| Table 4-13 | SCITCER register read/write bits       | 4-11 |

| Table A-1  | AMBA APB signal descriptions           | A-2  |

| Table A-2  | On-chip signals                        | A-3  |

| Table A-3  | Signals to pads                        | A-5  |

# List of Figures ARM PrimeCell Smart Card Interface (PL130) Technical Reference Manual

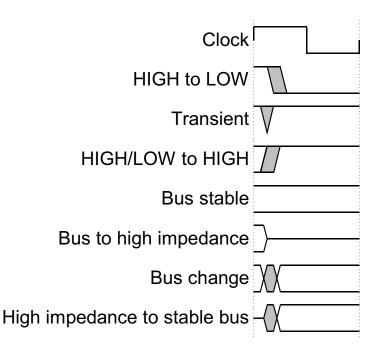

|            | Key to timing diagram conventions                | xii  |

|------------|--------------------------------------------------|------|

| Figure 1-1 | PrimeCell SCI block diagram and PADS connections | 1-3  |

| Figure 2-1 | PrimeCell SCI block diagram                      |      |

| Figure 2-2 | Initial etu equation                             | 2-19 |

| Figure 2-3 | Current etu equation                             | 2-19 |

| Figure 2-4 | 1 etu                                            | 2-20 |

| Figure 2-5 | Satisfied equation                               | 2-20 |

| Figure 2-6 | Character structure                              | 2-21 |

| Figure 2-7 | Character timing                                 | 2-21 |

| Figure 2-8 | To transmit request                              | 2-22 |

| Figure 3-1 | Smart card frequency                             | 3-22 |

| Figure 4-1 | PrimeCell SCI test harness                       | 4-2  |

List of Figures

# Preface

This preface introduces the ARM PrimeCell Smart Card Interface (PL130) Technical Reference Manual. It contains the following sections:

- About this Technical Reference Manual on page x

- *Feedback* on page xv.

### About this Technical Reference Manual

This is the *Technical Reference Manual* (TRM) for the *ARM PrimeCell Smart Card Interface*.

### Intended audience

This Technical Reference Manual is written for system designers, system integrators, and programmers who are designing or programming a *System-on-Chip* (SoC).

### Using this Technical Reference Manual

This Technical Reference Manual is organized into the following chapters:

### Chapter 1 Introduction

Read this chapter for a preamble on the ARM PrimeCell Smart Card Interface (SCI) and its features.

### **Chapter 2** Functional Overview

Read this chapter for a description of the block diagram and functionality of the PrimeCell SCI.

### Chapter 3 Programmer's Model

Read this chapter for a description of the block diagram and functionality of the PrimeCell SCI.

### Chapter 4 Programmer's Model for Test

Read this chapter for a description of the test registers and signals of the PrimeCell SCI.

Appendix A ARM PrimeCell Smart Card Interface (PL130) Signal Descriptions

Read this chapter for a description of the AMBA APB signals, on-chip signals and signals to pads.

### Conventions

Conventions that this Technical Reference Manual can use are described in:

- *Typographical* on page xi

- Timing diagrams on page xi

- Signals on page xii

- *Numbering* on page xiii.

### Typographical

The typographical conventions are:

| italic            | Highlights important notes, introduces special terminology, denotes internal cross-references, and citations.                           |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| bold              | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.   |

| monospace         | Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.                             |

| <u>mono</u> space | Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name. |

| monospace italic  | Denotes arguments to monospace text where the argument is to be replaced by a specific value.                                           |

| monospace bold    | Denotes language keywords when used outside example code.                                                                               |

| < and >           | Enclose replaceable terms for assembler syntax where they appear<br>in code or code fragments. For example:                             |

|                   | MRC p15, 0 <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd>                                                                   |

### **Timing diagrams**

The figure named *Key to timing diagram conventions* on page xii explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

### Key to timing diagram conventions

### Signals

The signal conventions are:

| Signal level | <ul> <li>The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:</li> <li>HIGH for active-HIGH signals</li> <li>LOW for active-LOW signals.</li> </ul> |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lower-case n | At the start or end of a signal name denotes an active-LOW signal.                                                                                                                                         |

| Prefix A     | Denotes global Advanced eXtensible Interface (AXI) signals.                                                                                                                                                |

| Prefix AR    | Denotes AXI read address channel signals.                                                                                                                                                                  |

| Prefix AW    | Denotes AXI write address channel signals.                                                                                                                                                                 |

| Prefix B     | Denotes AXI write response channel signals.                                                                                                                                                                |

| Prefix C     | Denotes AXI low-power interface signals.                                                                                                                                                                   |

| Prefix H     | Denotes Advanced High-performance Bus (AHB) signals.                                                                                                                                                       |

| Prefix P | Denotes Advanced Peripheral Bus (APB) signals. |

|----------|------------------------------------------------|

| Prefix R | Denotes AXI read data channel signals.         |

| Prefix W | Denotes AXI write data channel signals.        |

### Numbering

The numbering convention is:

### <size in bits>'<base><number>

This is a Verilog method of abbreviating constant numbers. For example:

- 'h7B4 is an unsized hexadecimal value.

- 'o7654 is an unsized octal value.

- 8'd9 is an eight-bit wide decimal value of 9.

- 8'h3F is an eight-bit wide hexadecimal value of 0x3F. This is equivalent to b00111111.

- 8'b1111 is an eight-bit wide binary value of b00001111.

### **Further reading**

This section lists publications by ARM and by third parties.

ARM provides updates and corrections to its documentation. See http://www.arm.com for current errata sheets, addenda, and the Frequently Asked Questions list.

### **ARM** publications

See the following documents for other relevant information:

- AMBA<sup>®</sup> Specification (Rev 2.0) (ARM IHI 0011).

- ARM PrimeCell Smart Card (PL130) Integration Manual (PL130 INTM 0000)

- ARM PrimeCell Smart Card (PL130) Design Manual (PL130 DDES 0000).

### Other publications

# *EMV '96 Integrated Circuit Card, Specifications for Payment Systems* (Version 3.0 June 1996) hereby referred to as *EMV Standard*.

Part I: Electromechanical characteristics, logical interface and transmission protocols. Published by Europay International S.A., Mastercard International Inc, and Visa International Association. *ISO/IEC* 7816-3: *Information technology - Identification cards - Integrated circuit(s) card(s) with contacts.*

Part 3: Electronic signals and transmission protocols.

### Feedback

ARM Limited welcomes feedback on both the ARM PrimeCell Smart Card Interface (PL130), and the documentation.

### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- the product name

- a concise explanation.

General suggestions for additions and improvements are also welcome.

### Feedback on this Technical Reference Manual

If you have any comments on this Technical Reference Manual, send an e-mail to errata@arm.com. Give:

- the title

- the number

- the relevant page number(s) to which your comments apply

- a concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

Preface

# Chapter 1 Introduction

This chapter introduces the ARM PrimeCell Smart Card Interface (PL130) and contains the following sections:.

- About the ARM PrimeCell Smart Card Interface (PL130) on page 1-2

- AMBA compatibility on page 1-6.

# 1.1 About the ARM PrimeCell Smart Card Interface (PL130)

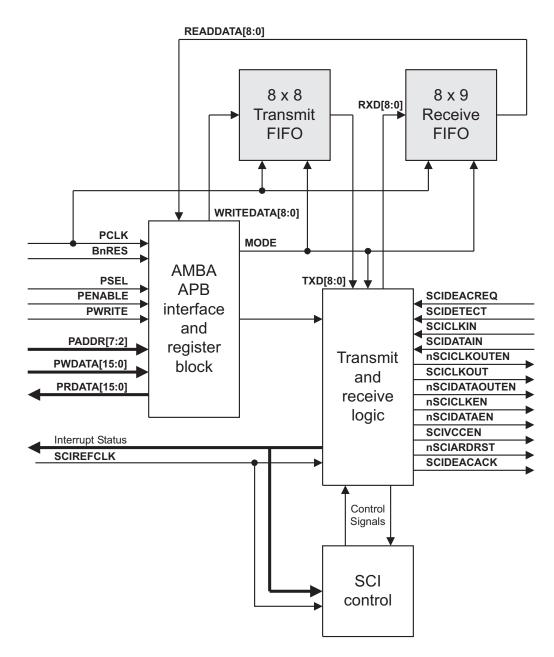

The PrimeCell *Smart Card Interface* (SCI) is an *Advanced Microcontroller Bus Architecture* (AMBA) compliant System-on-a-Chip peripheral that is developed, tested and licensed by ARM. Refer to Figure 1-1 on page 1-3 to for a block diagram of the SCI.

The PrimeCell SCI is an AMBA slave module and connects to the AMBA *Advanced Peripheral Bus* (APB), and interfaces to an external Smart Card reader. The SCI can autonomously control data transfer to and from the smart card. Transmit and receive data FIFOs are provided to reduce the required interaction between the CPU core or an AMBA *Advanced High-performance Bus* (AHB) master and the peripheral.

Figure 1-1 PrimeCell SCI block diagram and PADS connections

The features of the PrimeCell SCI are covered under the following headings:

- Features of the PrimeCell SCI

- *Programmable parameters.*

### 1.1.1 Features of the PrimeCell SCI

The following features are provided by the PrimeCell SCI:

- compliance to the *AMBA Specification (Rev 2.0)* onwards for easy integration into *System-on-a-Chip* (SoC) implementation

- Supports asynchronous T0 and T1 transmission protocols

- supports clock rate conversion factor F = 372, with bit rate adjustment factors D = 1, 2 or 4 supported

- eight character deep buffered TX and RX paths

- direct interrupts for TX and RX FIFO level monitoring

- interrupt status register

- hardware initiated card deactivation sequence on detection of card removal

- software initiated card deactivation sequence on transaction complete

- limited support for synchronous smart cards via registered input/output.

### 1.1.2 Programmable parameters

The following key parameters are programmable:

- Smart Card clock frequency

- communication baud rate

- protocol convention

- card activation time

- card deactivation time

- check for maximum time for first character of Answer To Reset (ATR) reception

- check for maximum duration of ATR character stream

- check for maximum time for receipt of first character of data stream

- check for maximum time allowed between characters

- character guard time

- clock guard time

- transmit character retry

- receive character retry

- transmit FIFO tide level

- receive FIFO tide level.

Additional test registers and modes are implemented to provide efficient testing.

# **1.2** AMBA compatibility

The PrimeCell SCI complies with the *AMBA Specification (Rev 2.0)* onwards. The fundamental differences from the *AMBA Specification Revision D* are:

- the timing of the strobe signal **PSTB** compared with the enable signal **PENABLE**

- the time at which read data is sampled

- a separate unidirectional read data bus **PRDATA**, and unidirectional write data bus **PWDATA** (instead of the bidirectional data bus **PD**)

- the address bus is named **PADDR** (instead of **PA**).

This document assumes little-endian memory organization, where bytes of increasing significance are stored in increasing addresses in memory, and hence low-order bytes are transferred on the low-order bits of the data bus. This block can also be used in a system with a big-endian memory organization, and several methods of achieving this are described in the *PrimeCell Smart Card Interface (PL130) Integration Manual*.

# Chapter 2 Functional Overview

This chapter describes the major functional blocks of the ARM PrimeCell Smart Card Interface (PL130).

- ARM PrimeCell Smart Card Interface (PL130) overview on page 2-2

- PrimeCell SCI functional description on page 2-4

- *PrimeCell SCI operation* on page 2-9.

# 2.1 ARM PrimeCell Smart Card Interface (PL130) overview

The PrimeCell Smart Card Interface (SCI) conforms to Part 1 of the Integrated Circuit Specification for Payment Systems Electromechanical Characteristics, Logical Interface, and Transmission Protocols (Version 3.0 June 1996). This standard is published jointly by Europay International S.A., Mastercard International Incorporated, and Visa International Service Association and is subsequently referred to as the EMV Standard. This standard refers to, and is based upon, the ISO 7816 series of standards. The user is expected to be familiar with both the EMV Standard and ISO 7816-3.

The PrimeCell SCI performs:

- serial to parallel conversion on data received

- parallel to serial conversion on data transmitted to an external smart card.

The host CPU reads and writes data and control information via the AMBA APB interface. The transmit and receive paths are buffered with internal FIFO memories allowing up to 8-bytes to be stored independently in both transmit and receive modes.

The PrimeCell SCI includes a programmable baud rate generator and, in conjunction with a secondary value counter, provides programmable *elementary time units* (etus).

This peripheral has been designed such that it allows close monitoring of all stages of a typical card session via mask enabled interrupts. The interrupt architecture allows a choice of:

- a polled approach by examining the interrupt status register on assertion of a single common interrupt

- the interrupt sources can be fed direct to the interrupt controller for immediate identification.

The transmit and receive FIFO interrupts are asserted and de-asserted automatically depending on their programmed trigger threshold levels.

Parity errors are automatically checked by hardware on received data.

Interpretation of the received data stream is always performed by the user's application software.

Card deactivation is initiated automatically via hardware on card removal, but it is also possible to deactivate the card via software by writing to the respective control register. Also a second deactivation request input is available for direct control via an alternative hardware source.

Although some parameter values are currently fixed by the *EMV Specification*, the design has taken into account that these may be changed in the future. The design strategy means that the user should be able to incorporate future changes to the specification with minimal effort.

A brief summary of the individual blocks of the design is given in the following sections.

# 2.2 PrimeCell SCI functional description

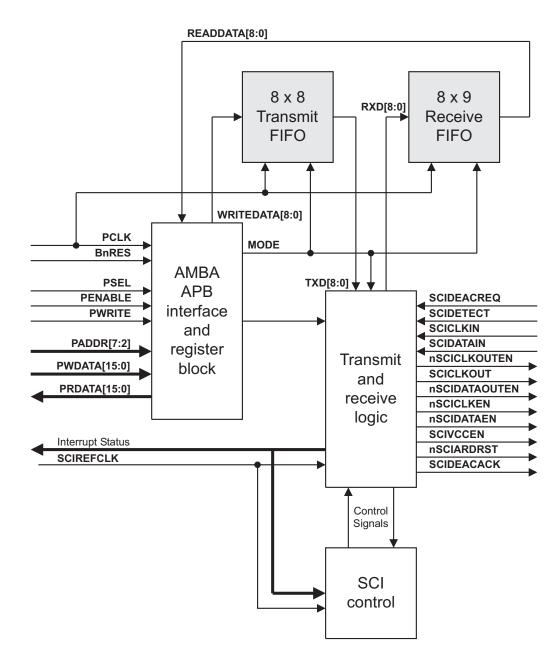

A diagrammatic view of the PrimeCell SCI is shown in Figure 2-1 on page 2-5.

\_\_\_\_\_ Note \_\_\_\_\_

For clarity test logic is not shown.

Figure 2-1 PrimeCell SCI block diagram

### 2.2.1 AMBA APB interface

The AMBA APB interface generates read and write decodes for accesses to the status/control registers and transmit/receive FIFO memories.

The AMBA APB is a local secondary bus which provides a low-power extension to the higher bandwidth AMBA *Advanced High-performance Bus* (AHB), or AMBA *Advanced System Bus* (ASB), within the AMBA system hierarchy. The AMBA APB groups narrow-bus peripherals to avoid loading the system bus, and provides an interface using memory-mapped registers which are accessed under programmed control.

### 2.2.2 Register block

The register block stores data written or to be read across the AMBA APB interface.

### 2.2.3 Transmit and receive logic

This block implements the main functionality of the PrimeCell SCI with the control information being fed from the PrimeCell SCI control block. It contains all the counters used for timing the various stages of transactions during a card session. Also, it drives all the card control signals with the exception of data.

In this implementation some counters are multi-purpose, that is, they are loaded with values required by a particular transaction stage, thereby minimizing the logic required to perform the overall function.

The SCIBAUDCNT and SCIVALUECNT counters provide the means of performing the bit rate conversion and bit rate adjustment. Together they define the *elementary time unit* (etu) period.

The card clock, **SCICLKOUT**, is derived from the output of the SCICLKICCCNT divide counter.

The SCIACTTIME counter is multi-purpose and is used for six different operations:

- debounce timing

- activation timing

- answer to reset (ATR) start time

- ATR duration time

- deactivation time

- warm reset timing.

The SCIDATATIME counter is a multi-purpose counter that is used to measure:

• block guard time

- character guard time

- time between characters

- time between characters and blocks.

The SCIACTTIME and SCIDATATIME counters are controlled by the SCI Control block.

The transmit and receive block controls the sequencing of the power, clock, reset and data line during activation and deactivation processes.

With the exception of the transmit and receive FIFO interrupts, this block generates all the remaining interrupts that provide a means of monitoring the individual stages of a card session.

### 2.2.4 SCI control logic

This block controls the PrimeCell SCI using the timeouts and other control signals received from the transmit and receive logic block.

### 2.2.5 Transmit FIFO

The transmit FIFO is an 8-deep 8-bit wide circular buffer. Reads and writes to the transmit FIFO result in an access to buffer locations pointed to by a read and write pointer respectively. The transmit FIFO is used to buffer data that is subsequently sent to the card.

The Transmit Tide Mark Interrupt **SCITXTIDEINTR** is generated from within this block and is asserted when the level falls below the programmed value.

If there is an unsuccessful transmission when using the T0 protocol, the PrimeCell SCI asserts the SCI Transmit Error Interrupt (**SCITXERRINTR**) and sets bit [4], the SCI Transmit Error Interrupt Status (SCITXERRIS) bit, of the SCIIIR register. The PrimeCell SCI will stop transmitting and before any further characters can be transmitted, the error condition must be cleared by flushing the transmit FIFO.

### 2.2.6 Receive FIFO

The receive FIFO is an 8-deep 9-bit wide circular buffer. Reads and writes to the receive FIFO result in an access to buffer locations pointed to by a read and write pointer respectively. Data is stored in the least significant eight bits, and the ninth bit is set when a parity error is detected on the received data.

The **SCIRXTIDEINTR** interrupt is generated from within this block and is asserted when the level rises above the programmed value.

An SCI Receive Timeout Interrupt (**SCIRTOUTINTR**) is asserted and bit [9], the SCI Receive Timeout Status (SCIRTOUTIS), of the SCIIIR register is set under the following condition:

The receive FIFO contains at least one character, and no characters have been read for a time corresponding to the value programmed in the SCIRXTIME register.

### 2.2.7 Test registers and logic

There are registers and logic for functional block verification, and manufacturing/production test using TICTalk vectors.

Test registers should not be read or written to during normal use.

The test logic allows generation of a special test clock enable signal to propagate the test vectors applied to the input signal of the block, and capture values at the block outputs.

### 2.3 PrimeCell SCI operation

The PrimeCell SCI provides a communication medium for the data transactions between a Smart Card and hardware/software that effectively form a Smart Card Reader.

The operation of the PrimeCell SCI is described in the following sections:

- Interface reset

- Clock signals

- Response to an ideal card session on page 2-10

- *Warm reset sequence* on page 2-16

- Response to a non-ideal card session on page 2-16

- Data transfer on page 2-19

- *Character framing* on page 2-20

- *EMV character timing for T=0 (character protocol)* on page 2-22

- Transmit on page 2-23

- *Receive* on page 2-24

- Block time and time between barriers on page 2-24

- *Parity error* on page 2-24

- *RXREAD interrupt* on page 2-25.

### 2.3.1 Interface reset

The PrimeCell SCI is reset by the global reset signal **BnRES** and a block-specific reset signal **nSCIRST**. An external reset controller must use **BnRES** to assert **nSCIRST** asynchronously and negate it synchronously to **SCIREFCLK**. **BnRES** should be asserted LOW for a period long enough to reset the slowest block in the on-chip system, and then taken HIGH again. The PrimeCell SCI requires **BnRES** to be asserted for at least one period of **PCLK** and **nSCIRST** to be asserted for at least one period of **SCIREFCLK**.

The values of the registers after reset are detailed in Chapter 3 Programmer's Model.

### 2.3.2 Clock signals

The PrimeCell SCI has two input clock signals, PCLK and SCIREFCLK.

The **SCIREFCLK** frequency value should be selected in accordance with the chosen method of operation. For further details refer to

It is allowable to drive **SCIREFCLK** using the **PCLK** signal when the frequency value is suitable for the chosen method of operation, but separate clock signals may be required due to other system constraints.

However, there is a recommended constraint on the ratio of frequencies for **PCLK** and **SCIREFCLK**.

$\mathbf{F}_{\mathbf{SCIREFCLK}} \leq 2 \mathbf{X} \mathbf{F}_{\mathbf{PCLK}}$

The frequency of **SCIREFCLK** must be less than twice the frequency of **PCLK**. If **SCIREFCLK** is more than twice the frequency of **PCLK** then transmission rates may not be fast enough to comply with the specification.

There is no restraint if the frequency of **SCIREFCLK** is less than the frequency of **PCLK**.

### 2.3.3 Response to an ideal card session

This section gives a brief overview of an ideal transaction sequence, and how it is monitored. Following this is a section that describes the typical errors that may occur during a non-ideal transaction and the ensuing actions.

Notification of errors is provided to the host by the PrimeCell SCI via a choice of:

- 12 direct interrupts

- a single ORed version, the SCI Interrupt signal **SCIINTR**, coupled with subsequent reading of the SCI Interrupt Identification Register status register SCIIIR.

\_\_\_\_\_Note \_\_\_\_\_

In the following descriptions, setting of any of the 12 individual inputs implies that the **SCIINTR** signal is also consequently set.

### Stages of a card session

A card session comprises the following stages:

- PrimeCell SCI reset and initial configuration on page 2-11

- Stages of a card session

- Contact activation and cold reset sequence on page 2-13

- Answer To Reset sequence on page 2-13

- *Execution of a transaction* on page 2-14

- *Contact deactivation sequence and card removal* on page 2-14.

### PrimeCell SCI reset and initial configuration

The PrimeCell SCI is reset by the asynchronous LOW application of **BnRES** and **nSCIRST**. These signals are then synchronously removed with reference to their respective clocks. The PrimeCell SCI is then configured by writing the initial values listed in Table 2-1 in preparation for a card being inserted into a Smart Card Reader and subsequent communication.

— Note —

The SCIDTIME register controls the timing of the card deactivation sequence and must be initialized before the activation sequence takes place. This is mandatory. Failure to carry out this action may result in damage to the card if it is removed prematurely.

| Register    | Value  | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCICR0      | 0x0    | The control register 0 is set to direct convention, even parity, receive/transmit handshaking disabled.                                                                                                                                                                                                                                                                                                                                    |

| SCICR1      | 0x0    | Receive mode, timeouts initially disabled.                                                                                                                                                                                                                                                                                                                                                                                                 |

| SCIIER      | 0xfff  | Enable all interrupts.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SCISTABLE   | 0x64   | For a 48MHz (21ns) reference clock, the stable (debounce) time is in terms of multiples of 1.38ms (0xffff x 21ns). An initial value of 136ms is proposed.                                                                                                                                                                                                                                                                                  |

| SCIATIME    | 0xafc8 | The SCIATIME register must be programmed to between 40000 and 45000 (0xafc8) smart card clock cycles to satisfy the minimum cold and warm reset <b>nSCICARDRST</b> LOW time requirements.                                                                                                                                                                                                                                                  |

| SCIDTIME    | 0x2710 | The SCIDTIME is in terms of reference clock periods. It times<br>the three stages of the deactivation sequence. The total time of<br>the deactivation sequence must not take longer than 1ms to<br>complete. An initial value of 10000 (0x2710) periods is<br>suggested which is equivalent to an SCIDTIME of<br>approximately 0.21ms for a 48MHz (21ns) reference clock.<br>This gives a total deactivation time of approximately 0.65ms. |

| SCIATRSTIME | 0x9c40 | The SCIATRSTIME is in terms of smart card clock cycles.<br>After de-assertion of the reset <b>nSCICARDRST</b> signal, the<br>start of the ATR sequence must occur within 40000 (0x9c40)<br>smart card cycles.                                                                                                                                                                                                                              |

### Table 2-1 Initial configuration values

| Register    | Value  | Comments                                                                                                                                                                                                                                                                                                       |

|-------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCIATRDTIME | 0x4b00 | The SCIATRDTIME is in terms of <i>elementary time units</i> (etus). The complete ATR character sequence must be received within 19200 (0x4b00) etus.                                                                                                                                                           |

| SCICHTIME   | 0x2580 | The SCICHTIME is in terms of etus and is the maximum interval between the leading edges of two consecutive characters. In the case of the ATR sequence this is 9600 (0x2580) etus. It is also applicable to characters in the transaction data stream and is $T = 0$ , or $T = 1$ mode dependent.              |

| SCIRXTIDE   | 0x0    | This is the receive FIFO tide level. Although a value of zero is proposed, any value between 0x0 and 0x7 can be used. With a value of zero, the <b>SCIRXTIDEINTR</b> interrupt is generated when the initial TS character is loaded into the receive FIFO.                                                     |

| SCICLKICC   | 0x17   | The SCICLKICC value is used to divide down the reference clock to provide the smart card clock. The final smart card frequency should be within the range 1-5MHz. For a 48MHz reference clock, SCICLKICC should be programmed with a value of 23 (0x17) to provide an initial 1MHz Smart Card clock frequency. |

| SCIBAUD     | 0x174  | For a 48MHz reference clock, 1MHz smart card clock, and an SCI value of 10 (0xA), then SCIBAUD should be programmed to 178A (0x6f8)                                                                                                                                                                            |

| SCIVALUE    | 0x10   | An SCIVALUE value of 10 (0xa) is proposed as the sample value.                                                                                                                                                                                                                                                 |

### Table 2-1 Initial configuration values (continued)

### Smart card insertion and detection

A Smart Card is inserted into the Smart Card Reader.

The Smart Card Reader signals to the PrimeCell SCI that a card has been detected by setting the **SCIDETECT** signal high. In response to this, the PrimeCell SCI starts its *debounce* timer.

The Smart Card must remain in the interface for the debounce period, which is initially defined by the value written to the SCISTABLE register.

On expiry of the debounce period, the PrimeCell SCI notifies the host that a card has been successfully inserted by asserting the SCI Card In Interrupt signal **SCICARDININTR** and setting bit [0], the SCICARDINIS bit, of the SCIIIR status register.

At this point there are no clocks or power applied to the Smart Card and the input/output signals are held LOW by the interface. These signals are then applied in a controlled manner by the activation sequence.

### Contact activation and cold reset sequence

The host now signals the PrimeCell SCI that it can activate the card, that is power up the inserted card in an ordered manner. The PrimeCell SCI activation sequence has been divided into three equal phases, timed by the value programmed in the SCI activation time register SCIATIME.

The PrimeCell SCI activation sequence includes the *cold* reset sequence which must be in effect for between 40000 and 45000 Smart Card clock cycles. This is programmed using the SCIATIME register.

The PrimeCell SCI performs the following activation sequence:

- 1. Assert **nSCICARDRST** low.

- 2. Wait for SCIATIME Smart Card clock cycles.

- 3. Enable VCC, configure **SMDATA** signal as high impedance.

- 4. Wait for SCIATIME Smart Card clock cycles.

- 5. Enable **SCICLKOUT** clock.

- 6. Wait for SCIATIME Smart Card clock cycles.

- 7. De-assert **nSCICARDRST** high.

The host initiates the activation sequence by writing a 1 to bit 0 (STARTUP) of the SCI control register 2 (SCICR2).

The PrimeCell SCI notifies the host that the activation sequence is complete by asserting the SCI card up interrupt signal **SCICARDUPINTR** and setting bit [2], SCICARDUPIS, within the SCIIIR.

The ATR on the input/output line from the Smart Card will begin between 400 and 40000 cycles from reset de-assertion.

### Answer To Reset sequence

The ATR sequence contains information about the card requirements for subsequent data transactions. The first character within the ATR stream is called the TS character and contains the convention information (direct or inverse format) on how the remaining ATR and future data transaction characters will be interpreted.

On reception of the first character, the SCI RXTIDE interrupt **SCIRXTIDEINTR** signal is asserted and bit [10], the SCI RXTIDE interrupt status bit SCIRXTIDEIS is set within the SCIIIR status register.

The PrimeCell SCI should read this character, establish the respective required convention and then, if necessary, reprogram the SCI control register 0 (SCICR0). It is also recommended that the RXFIFO RXTIDE level be programmed to a higher value.

These processes should be completed prior to the start of reception of the next character.

In brief, the ATR sequence includes configuration values for:

- the clock frequency

- baud rate

- guard times

- protocol type.

The remainder of the ATR sequence is received, read via the RXFIFO in the selected convention, interpreted by the host software and the PrimeCell SCI programmed accordingly with the extracted values.

### **Execution of a transaction**

After the interface has been configured by extracting the parameters from the ATR stream, host to card communication, and vice versa, can now proceed.

The direction of flow is controlled via the value written to bit [2], the MODE bit, in the SCI control register 1 (SCICR1).

The host is always in control of how many characters it sends to the card and how many characters it expects to be returned by the card.

The character streams must meet the timing requirements of either the T0 or T1 protocol. These are covered in TBD *EMV character timing for* T=0 (*character protocol*) on page 2-21 and TBD *EMV character timing for* T=1 (*block protocol*) on page 2-22.

### Contact deactivation sequence and card removal

The final step in a typical card session is contact deactivation where the signals and power are removed in a defined sequence. Contact deactivation takes precedence over all other operations in order that the card is not electrically damaged.

The deactivation sequence can be initiated by software by writing a 1 to bit [1], the FINISH bit, of the SCICR2 register. Also, there are two hardware signals which can be used:

- On detection of a cards removal at any time in a session, signified by the **SMIDETECT** signal being low, then contact deactivation will be initiated. The **SMIDECTECT** signal usually originates from a Smart Card reader.

- In addition, it is possible to initiate contact deactivation by asserting the signal **SCIDEREQ** which may be fed from an alternative source other than a Smart Card reader.

The PrimeCell SCI deactivation sequence has been divided into three equal phases, timed by the value programmed in the SCI Deactivation Time (SCIDTIME) register and is in terms of reference clock **SCIREFCLK** periods.

The PrimeCell SCI deactivation sequence must complete within 1 millisecond. This means that the SCIDTIME register needs to be programmed with a third of the total time. For example, for an **SCIREFCLK** frequency of 48MHz (period 21ns) an SCIDTIME value of 10000 would equate to a total deactivation time of around 0.65ms.

The PrimeCell SCI performs the following deactivation sequence:

- 1. Assert **nSCICARDRST** low.

- 2. Wait for SCIATIME reference clock (SCIREFCLK) cycles.

- 3. Drive SCICLKOUT low.

- 4. Wait for SCIATIME reference clock (SCIREFCLK) cycles.

- 5. Drive nSCIDATAEN high.

- 6. Wait for SCIATIME reference clock (SCIREFCLK) cycles.

- 7. Drive VCC low.

On completion of the deactivation sequence, the PrimeCell SCI asserts the SCI Card Down Interrupt signal **SCICARDDNINTR** and sets bit [3], the SCI Card Down Interrupt Status bit SCICARDDNIS, of the SCIIIR status register.

The card may then be safely removed if desired, but it may remain and be re-activated for another transaction if so required by the host.

On recognition of the card being removed, that is, **SCIDETECT** transitioning from HIGH to LOW, the PrimeCell SCI asserts the SCI Card Out Interrupt **SCICARDOUTINTR** and sets bit [1], the SCI Card Out Interrupt Status bit (SCICARDOUTIS) of the SCIIIR register.

#### 2.3.4 Warm reset sequence

This section describes an ideal card session However, if the ATR sequence is found to be in error, as described in *Response to an ideal card session*, then the PrimeCell SCI will initiate a *warm* reset sequence in an attempt to restart reception of the ATR stream:

#### 1. Assert **nSCICARDRST** LOW.

- 2. Maintain VCC and clock stable

- 3. Put the PrimeCell SCI into reception mode

- 4. Wait for SCIATIME Smart Card clock cycles

- 5. De-assert **nSCICARDRST** HIGH.

The host initiates the activation sequence by writing a 1 to bit 0 (STARTUP) of the SCICR2 control register.

The ATR on the input/output line from the Smart Card will begin between 400 and 40000 cycles from reset de-assertion.

If the start bit of the ATR stream is not received within this time, then the PrimeCell SCI will automatically initiate the deactivation sequence without the need for software intervention.

#### 2.3.5 Response to a non-ideal card session

The PrimeCell SCI has to resolve non-ideal transactions such as:

- removal of the card before a transaction has completed

- timing/parity errors that may occur during the data flow.

The PrimeCell SCI monitors each transaction stage via interrupt and status generation, allowing software to respond accordingly. For more detailed information on the individual and final shared interrupts, refer to Chapter 3 *Programmer's Model*.

Notification of errors is provided to the host by the PrimeCell SCI via a choice of either twelve direct interrupts or their single ORed version, the SCI Interrupt Signal **SCIINTR**, coupled with subsequent reading of the SCI Interrupt Identification Register SCIIIR.

\_\_\_\_\_ Note \_\_\_\_\_

In the following descriptions, setting of any of the twelve individual inputs implies that the **SCIINTR** signal is also consequently set.

#### Card removed at any time between activation and deactivation

The PrimeCell SCI must ensure that no electrical damage is caused to the card if it is removed whilst still powered up, that is, it must immediately be deactivated in a defined sequence.

Card deactivation takes precedence over any other operation and can be initiated by software or hardware. The card must be powered down in less than 1 millisecond. See *Contact deactivation sequence and card removal* on page 2-14 for details of this sequence.

On recognition of the card being removed, that is, **SCIDETECT** transitioning from HIGH to LOW, the PrimeCell SCI asserts the SCI Card Out Interrupt **SCICARDOUTINTR** and sets bit [1], the SCI Card Out Interrupt Status bit (SCICARDOUTIS) of the SCIIIR register.

### Card inserted, debounce time not met, then card removed

This is very similar to the above, though not as critical, as power will not been applied to the card. The card is only activated on successful completion of the debounce period. As above the card must immediately be deactivated using the controlled deactivation sequence.

On recognition of the card being removed, that is **SCIDETECT** transitioning from HIGH to LOW, the PrimeCell SCI asserts the SCI Card Out Interrupt **SCICARDOUTINTR** and sets bit [1], the SCI Card Out Interrupt Status bit (SCICARDOUTIS) of the SCIIIR register.

# Card inserted, debounce time not met, no ATR start bit received within the specified time

The SCIATRSTIME register value is programmed with the value 40000. This represents the maximum number of Smart Card clock cycles after de-assertion of the **SCICARDRST** signal during which the start bit of the card's ATR sequence should be received.

If the ATR start bit is not received before this maximum number of Smart Card clock cycles has expired, then the PrimeCell SCI asserts the ATR Start Timeout Interrupt **SCIARTSTOUTINTR** and sets bit 5 of the SCIIIR register, the SCI Card Out Interrupt Status bit (SCIATRSTOTIS).

The PrimeCell SCI will automatically initiate the deactivation sequence without the need for software intervention.

# ATR start bit received, but time between two successive characters exceeds the specified time.

If the ATR start bit is received within the specified time, then the time between leading edges of the ATR characters is checked to be less than the specified maximum limit.

This value is programmed into the SCI Character Time register (SCICHTIME).

During the ATR, the delay between the leading edges of any two consecutive characters from the card shall be a minimum of 12, but not more than 9600 etus. See Table 2-1 on page 2-10 for more details of the definition of the initial etu values for ATR reception.

If the SCICHTIME value is exceeded at any time during reception of the ATR data stream, then the SCI Character TimeOut Interrupt signal (**SCICHTOUTINTR**) is asserted and bit 8, the SCI Character TimeOut Interrupt status bit (SCICHTOUTIS), of the SCIIIR register is set.

The host software will respond to the interrupt and initiate a warm reset sequence by writing a 1 to the WRESET bit of the SCICR2 control register.

# ATR start received, but the duration of the total ATR data stream exceeded the specified time

The card shall transmit all the characters to be returned during an ATR within 19200 etus. This time is measured between the leading edge of the start bit of the first character (TS) and 12 etus after the leading edge of the start bit of the last character.

The maximum value, which is currently fixed at 19200 by the *EMV Specification*, is programmed into the SCI ATR Duration Time register (SCIATRDTIME). If the SCIATRDTIME time is not met, then the SCI ATR Duration TimeOut Interrupt signal **SCIATRDTOUTINTR** is asserted and bit 6, the SCI ATR TimeOut Status bit (SCIATRDTOUTIS) of the SCIIIR register is set.

The host software will respond to the interrupt and initiate a warm reset sequence by writing a 1 to the WRESET bit of the SCICR2 control register.

## ATR received, but parity errors are found within the received data

If, during the reception of the ATR stream, an error such as parity failure is recognized by the PrimeCell SCI or the associated software, then the PrimeCell SCI will initiate a warm reset by writing a 1 to the WRESET bit of the SCICR2 control register.

#### Data transaction in progress, time for block arrival exceeded

If the maximum delay from start leading edges of the last character from the PrimeCell SCI, that gave the right to send to the card, and the first character sent by the card exceeds a specified time, then the PrimeCell SCI will assert the SCI Block TimeOut Interrupt (**SCIBLKTOUTINTR**) and set bit 7, the SCI Block TimeOut Interrupt Status (SCIBLKTOUTIS) bit, of the SCIIIR register.

The block timeout value is programmed by writing to the SCIBLKTIME register.

### 2.3.6 Data transfer

#### **Data rates**

The duration of a bit within a character is termed the *elementary time unit* (etu). The etu is set by programming the SCIBAUD and SCIVALUE registers.

## Value X BAUD rate clock

The value in the SCIBAUD register is used to define a clock which is a multiple of the baud rate. This is known as the Value X BAUD rate clock. The Value X BAUD rate clock is generated by dividing the reference clock by 1 + SCIBAUD. The SCIVALUE register defines the number of Value X BAUD rate clock periods which make up an etu. The etu is programmable and has different values dependent upon the stage of card processing.

During the ATR, the bit duration is known as the initial etu and is given by the following equation:

Initial etu =  $\frac{372}{f}$  seconds

#### Figure 2-2 Initial etu equation

where f is the Smart Card clock frequency in Hertz.

Following the ATR (and establishment of the global parameters F and D), the bit duration is known as the current etu, and is given by the following equation:

current etu =

$$\frac{F}{f} \times \frac{1}{D}$$

seconds

#### Figure 2-3 Current etu equation

where F and D are the clock rate conversion and bit rate adjustment parameters returned by the card, and f is the clock frequency applied to the Smart Card.

The etu is set by programming the SCIBAUD and SCIVALUE registers.

The SCIVALUE defines the number of baud rate clock periods that define the etu.

Therefore:

$1 \text{ etu} = \frac{(1 + \text{SCIBAUD})}{(\text{Reference Clock})} \times \text{SCIVALUE}$

Figure 2-4 1 etu

Thus the following equation must always be satisfied:

$$\frac{(1 + \text{SCIBAUD})}{(\text{Reference Clock})} \times \text{SCIVALUE} = \frac{F}{f} \times \frac{1}{D}$$

#### Figure 2-5 Satisfied equation

See ISO 7816-3 for the possible values of F and D that can be returned by the card.

—— Note ———

The EMV standard specifies that f must be in the range 1–5 MHz. ISO 7816-3 merely specifies a lower bound of 1 MHz.

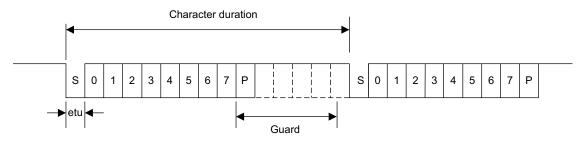

#### 2.3.7 Character framing

Figure 2-6 on page 2-21 shows the structure of a character. Each character consists of:

- a start bit

- eight data bits

- a parity bit

- a number of bits making up the *guard time* before the start bit of the next character.

The *guard time* is the delay between the trailing edge of the parity bit of a character, and the leading edge of the start bit of the next character. The guard time for characters transmitted by the interface is controlled by the SCICHGUARD register.

#### Figure 2-6 Character structure

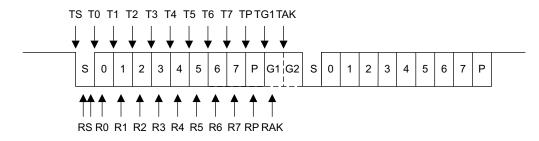

Figure 2-7 shows how the interface interprets characters transmitted from the card. At time TS, the card pulls the bidirectional input/output line LOW to begin the start bit.

#### Figure 2-7 Character timing

The interface detects the leading edge of the start bit after four reference clock cycles. The input/output line is sampled at RS, approximately half an etu after the leading edge of the start bit. If the input/output line is not LOW, the start bit is deemed to be invalid and is ignored by the interface.

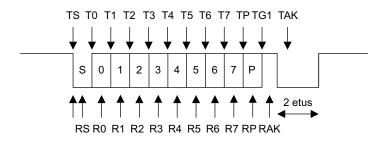

The first data bit is sampled at 1 etu after RS, and subsequent data bits (including the parity bit) are sampled at 1 etu intervals. The T0 protocol defines a mechanism whereby the receiver can request retransmission of a character by pulling the input/output line LOW during the guard time following the character. When a retransmission is requested, the interface starts to pull the input/output line LOW at RAK.

The transmitter (the card in this case) samples the input/output line at TAK. The interface holds the input/output line for a total of 2 etus. This is shown in Figure 2-8 on page 2-22.

Figure 2-8 To transmit request

### 2.3.8 EMV character timing for T=0 (character protocol)

The minimum interval between the leading edges of the start bits of two consecutive characters sent by the interface to the Smart Card is between 12 and 266 etus as indicated by the value of TC1 returned within the ATR stream.

The minimum interval between the leading edges of the start bits of two consecutive characters sent by the Smart Card to the interface is 12 etus.

The maximum interval between the start leading edge of any character sent by the Smart Card and the start leading edge of the previous character sent either by the Smart Card or the interface (the *work waiting time*) will not exceed 960 x D x WI = 9600 etus. (The bit rate conversion factor, D, will have a default value of 1. WI will not have a default value of 10 as TC2, which would contain the value, is not returned in the ATR.)

The minimum interval between the leading edges of the start bits of two consecutive characters sent in opposite directions will be 16 etus.

— Note — Note — The minimum interval between the leading edges of the start bits of two characters sent by interface to the Smart Card is always governed by the value of TC1. It may be less than minimum interval of 16 etus allowed between two characters sent in opposite directions.

#### 2.3.9 EMV character timing for T=1 (block protocol)

The minimum interval between the leading edges of the start bits of two consecutive characters, sent by the interface to the Smart Card will be between 11 and 266 etus as indicated by the value of TC1 returned within the ATR stream.

The minimum interval between the leading edges of the start bits of two consecutive characters sent by the Smart Card to the interface will be 11 etus.

The maximum interval between the leading edges of the start bits of to consecutive characters in the same block the *Character Waiting Time* (CWT) will not exceed (2\*CWI + 11) etus. The *Character Waiting Integer* (CWI) will have a value of 0 to 5, resulting in the CWT having the range 12 to 43 etus.

The maximum interval between the leading edge of the start bit of the last character that gave the right to send to the Smart Card and the leading edge of the first character sent by the Smart Card the *Block Waiting Time* (BWT) will not exceed ((2\*BWI x 960) + 11) etus. The *Block Waiting Integer* (BWI) will have a value in the range 0 to 4, resulting in the BWT having the range 971 to 15371 etus.

The minimum interval between the leading edges of the start bits of two consecutive characters sent in opposite directions the *Block Guard Time* (BGT) will be 22 etus.

## 2.3.10 Transmit

Characters that are to be sent to the card are first written into the SCIDATA FIFO and then automatically transmitted to the card at timed intervals. Direction of communication is controlled by the MODE bit of the SCICR1 register. Changing from transmit to receive does not take place until the last character stored in the transmit FIFO has been sent. This enables the MODE bit to be written immediately after writing the last character in a block. This is necessary because the card can respond to the transmission almost immediately (minimum turnaround time measured from start bit to start bit is 16 etus for T0 and 22 etus for T1).

If character-transmit handshaking is enabled (mandatory for T0), the input/output line is sampled at 1 etu after the parity bit. If the card indicates that it did not receive the character correctly, the character is retransmitted a maximum of TXRETRY times (set using the SCIRETRY register) before the transmission is aborted and a SCITXERRINTR interrupt generated. The interface waits for four etus after an error is detected before the character is retransmitted. If a character fails to be transmitted and a SCITXERRINTR interrupt is generated, the transmit/receive interlock mechanism must be reset by flushing the transmit FIFO before any subsequent transmit or receive operation.

The interval between successive characters sent by the interface is governed by the SCICHGUARD register, which defines the character guard time. SCICHGUARD is only used to control the transmission of characters and is not used by the receive hardware.

The minimum interval between the last character sent by the card and the next character sent by the interface is governed by the SCIBLKGUARD register, which defines the block guard time.

When the number of characters held in the transmit FIFO falls below the level defined in the SCITXTIDE register, a **SCITXTIDEINTR** interrupt is generated. The number of characters held in the transmit FIFO can be determined by reading the SCITXCOUNT register. Writing to the SCITXCOUNT register flushes the transmit FIFO.

#### 2.3.11 Receive

Characters are read from the interface by reading the SCIDATA register. When read, SCIDATA has 9 bits:

- eight data bits

- one parity status bit.

See SCIDATA: [9] (+ 0x00) on page 3-6 for more information.

Before characters can be read from the interface, the MODE bit of the SCICR1 register must be set to 0. An interlock mechanism ensures that if the MODE bit is set to receive and there are still characters remaining in the transmit FIFO, these are transmitted before any characters are read from the card.

To switch from receive mode to transmit mode, write a 1 to the MODE bit within the SCICR1 control register during or after reception of the final byte within the incoming datastream.

#### 2.3.12 Block time and time between barriers

Two registers define an upper limit on the time waited for a character to be transmitted by the card:

- **SCIBLKTIME** defines the timeout limit for the first character in a block

- **SCICHTIME** defines the maximum allowed time between characters (excluding the first character in a block).

The SCICHTIME counter is linked to the SCIBLKTIME counter and not start until the SCIMBLKTIME counter has stopped (That is, the first character in the block has arrived, or if the block timer has been disabled). The transmit/receive interlock mechanism prevents the SCICHTIME and SCIBLKTIME counters from running while characters are still present in the transmit FIFO.

#### 2.3.13 Parity error

If character-transmit handshaking is enabled (RXNAK = 1) and the interface detects a parity error, it signals this to the card by pulling the input/output line down for 2 etus at 10.5 etus after the leading edge of the start bit.

The maximum number of times the interface attempts to receive a character is governed by the SCIRETRY register. If, after RXRETRY further attempts, the character has not be successfully received, a parity error for the character is flagged. When this character is read, bit 8 of SCIDATA is set to 1 to indicate that a parity error has occurred.

### 2.3.14 RXREAD interrupt

An RXREAD interrupt can be caused either:

- by the receive FIFO exceeding its tide mark (defined by SCITIDE)

- by a read access timeout (defined by SCIRXTIME).

The read access timeout limit can be reprogrammed dynamically, which provides a way of enabling the receive timeout mechanism only at the end of blocks. This is achieved by initially setting the receive timeout threshold to a high enough value to guarantee that an **RXREAD** interrupt can only have been caused by a tide mark condition (excluding an error condition where a card stops transmitting part way through a block). When the end of the block is reached, **RXTIME** is reprogrammed with the correct value to process the trailing characters in the block.

Functional Overview

# Chapter 3 Programmer's Model

This chapter describes the ARM PrimeCell Smart Card Interface (PL130) registers and provides details needed when programming the microcontroller. It contains the following:

- About the programmer's model on page 3-2

- Summary of PrimeCell SCI registers on page 3-3

- *Register descriptions* on page 3-6.

## 3.1 About the programmer's model

The base address of the PrimeCell SCI is not fixed, and may be different for any particular system implementation. The offset of any particular register from the base address, however, is fixed.

The following locations are reserved, and must not be used during normal operation:

- locations at offsets 0x70 through 0x7c are reserved for possible future extensions

- locations at offsets 0x80 through 0xff are reserved for test purposes.

# 3.2 Summary of PrimeCell SCI registers

The PrimeCell SCI registers are shown in Table 3-1.

#### Table 3-1 PrimeCell SCI register summary

| Address         | Туре          | Width | Reset<br>value | Name                        | Description                                                          |

|-----------------|---------------|-------|----------------|-----------------------------|----------------------------------------------------------------------|

| SCI Base + 0x00 | Read<br>Write | 9     | 0x             | SCIDATA<br>SCIDATA          | Data register.                                                       |

| SCI Base + 0x04 | Read<br>Write | 6     | 0x00           | SCICR0<br>SCICR0            | Control register 0.                                                  |

| SCI Base + 0x08 | Read<br>Write | 6     | 0x00           | SCICR1<br>SCICR1            | Control register 1.                                                  |

| SCI Base + 0x0c | Write         | 3     | 0x0            | SCICR2                      | Control register 2.                                                  |

| SCI Base + 0x10 | Read<br>Write | 12    | 0x000          | SCIIER<br>SCIIER            | Interrupt enable register.                                           |

| SCI Base + 0x14 | Read<br>Write | 6     | 0x00           | SCIRETRY<br>SCIRETRY        | Retry limit register.                                                |

| SCI Base + 0x18 | Read<br>Write | 8     | 0x00           | SCITIDE<br>SCITIDE          | FIFO tide mark register.                                             |

| SCI Base + 0x1c | Read<br>Write | 5/0   | 0x00           | SCITXCOUNT<br>SCITXCOUNTCLR | Transmit FIFO count register.<br>Transmit FIFO count clear register. |

| SCI Base + 0x20 | Read<br>Write | 5/0   | 0x00           | SCIRXCOUNT<br>SCIRXCOUNTCLR | Receive FIFO count register.<br>Receive FIFO count clear register.   |

| SCI Base + 0x24 | Read          | 4     | 0xa            | SCIFR                       | Flag register.                                                       |

| SCI Base + 0x28 | Read<br>Write | 16    | 0x0000         | SCIRXTIME<br>SCIRXTIME      | Receive read time-out register.                                      |

| SCI Base + 0x2c | Read<br>Write | 11    | 0x000          | SCIISTAT<br>SCIISTAT        | Smart Card status register.                                          |

| SCI Base + 0x30 | Read<br>Write | 16    | 0x0000         | SCISTABLE<br>SCISTABLE      | De-bounce timer.                                                     |

| Address         | Туре          | Width | Reset<br>value | Name                       | Description                                    |

|-----------------|---------------|-------|----------------|----------------------------|------------------------------------------------|

| SCI Base + 0x34 | Read<br>Write | 16    | 0x0000         | SCIATIME<br>SCIATIME       | Activation event time.                         |

| SCI Base + 0x38 | Read<br>Write | 16    | 0x0000         | SCIDTIME<br>SCIDTIME       | Deactivation event time.                       |

| SCI Base + 0x3c | Read<br>Write | 16    | 0x0000         | SCIATRSTIME<br>SCIATRSTIME | Time to start of ATR reception.                |

| SCI Base + 0x40 | Read<br>Write | 16    | 0x0000         | SCIATRDTIME<br>SCIATRDTIME | Maximum duration of the ATD character stream.  |

| SCI Base + 0x44 | Read<br>Write | 16    | 0x0000         | SCIBLKTIME<br>SCIBLKTIME   | Receive time-out between blocks.               |

| SCI Base + 0x48 | Read<br>Write | 16    | 0x0000         | SCICHTIME<br>SCICHTIME     | Character to character time-out.               |

| SCI Base + 0x4c | Read<br>Write | 8     | 0x00           | SCICLKICC<br>SCICLKICC     | External Smart Card clock frequency.           |

| SCI Base + 0x50 | Read<br>Write | 16    | 0x0000         | SCIBAUD<br>SCIBAUD         | Baud rate clock.                               |

| SCI Base + 0x54 | Read<br>Write | 8     | 0x00           | SCIVALUE<br>SCIVALUE       | SCIBAUD cycles.                                |

| SCI Base + 0x58 | Read<br>Write | 8     | 0x00           | SCICHGUARD<br>SCICHGUARD   | Character to character extra guard time.       |

| SCI Base + 0x5c | Read<br>Write | 8     | 0x00           | SCIBLKGUARD<br>SCIBLKGUARD | Block guard time.                              |

| SCI Base + 0x60 | Read<br>Write | 2     | 0x0            | SCISYNCCR<br>SCISYNCCR     | Asynchronous/synchronous multiplexing control. |

| SCI Base + 0x64 | Read<br>Write | 2     | 0x0            | SCISYNCDATA<br>SCISYNCDATA | Synchronous Smart Card data.                   |

| SCI Base + 0x68 | Read          | 2     | 0x0            | SCIRAWSTAT                 | Raw input/output and clock status.             |

## Table 3-1 PrimeCell SCI register summary (continued)

| Address                    | Туре          | Width | Reset<br>value | Name             | Description                                                 |

|----------------------------|---------------|-------|----------------|------------------|-------------------------------------------------------------|

| SCI Base + 0x6c            | Read<br>Write | 12    | 0x00a          | SCIIIR<br>SCIICR | Interrupt identification register/interrupt clear register. |

| SCI Base + 0x70<br>to 0x7c | -             | -     | -              | -                | Reserved.                                                   |

| SCI Base + 0x80<br>to 0xff | -             | -     | -              | -                | Reserved for test purposes.                                 |

## 3.3 Register descriptions

The following registers are described in this section:

- SCIDATA: [9] (+ 0x00) on page 3-7

- *SCICR0:* [6] (+ 0x04) on page 3-7

- *SCICR1:* [6] (+0x08) on page 3-9

- *SCICR2: [3] (+0x0c)* on page 3-10

- *SCIIER: [12] (+0x10)* on page 3-11

- *SCIRETRY:* [6] (+0x14) on page 3-12

- SCITIDE: [8] (+0x18) on page 3-13

- *SCITXCOUNT/SCITXCOUNTCLR:* [5/0] (+0x1c) on page 3-14

- SCIRXCOUNT/SCIRXCOUNTCLR: [5/0] (+0x20) on page 3-15

- SCIFR: [4] (+0x24) on page 3-15

- SCIRXTIME: [16] (+0x28) on page 3-15

- *SCIISTAT: [10] (+0x2c)* on page 3-16

- SCISTABLE: [16] (+0x30) on page 3-18

- *SCIATIME:* [16] (+0x34) on page 3-19

- *SCIDTIME:* [16] (+0x38) on page 3-19

- *SCIATRSTIME:* [16] (+0x3c) on page 3-19

- *SCIATRDTIME:* [16] (+0x40) on page 3-20

- *SCIBLKTIME:* [16] (+0x44) on page 3-20

- *SCICHTIME:* [16] (+0x48) on page 3-21

- SCICLKICC: [8] (+0x4c) on page 3-22

- *SCIBAUD:* [16] (+0x50) on page 3-22

- *SCIVALUE:* [8] (+0x54) on page 3-23

- SCICHGUARD: [8] (+0x58) on page 3-23

- *SCIBLKGUARD:* [8] (+0x5c) on page 3-24

- *SCISYNCCR:* [2] (+0x60) on page 3-25

- *SCISYNCDATA:* [4] (+0x64) on page 3-26

- *SCIRAWSTAT:* [2] (+0x68) on page 3-26

- *SCIIIR/SCIICR:* [12] (+0x6c) on page 3-27.

For each of the following register descriptions, the format of the title is:

Register name: [bit width] (Offset from Base).

### 3.3.1 SCIDATA: [9] (+ 0x00)

SCIDATA is the data register and is used for both transmitting and receiving characters. The write data is transmitted through nSCIDATAOUTEN. The read data is received through SCIDATAIN. Table 3-2 shows bit assignments for SCIDATA.

—— Note ———

Software should write to this register only after setting the MODE bit to 1. Writes to this register with the MODE but set to 0 will be ignored by the hardware.

| Bits | Name   | Туре       | Function                                                                                                                    |

|------|--------|------------|-----------------------------------------------------------------------------------------------------------------------------|

| 8    | PARITY | Read       | Parity error flag.<br>Set to 1 if a parity error was detected when receiving the<br>character corresponding to bits 7 to 0. |

| 7:0  | DATA   | Read/Write | Eight data bits. These correspond to the character being read or written.                                                   |

#### Table 3-2 SCIDATA register read/write bits

### 3.3.2 SCICR0: [6] (+ 0x04)

SCICR0 is control register 0. It configures the convention for interpreting characters, controls parity convention and enables the handshake mechanism to indicate that a parity error has occurred. The initial character returned by the card in the ATR sequence determines the convention.

There are two conventions:

**Inverse** A LOW state on the input/output line is interpreted as logic one and the *Most Significant Bit* (MSB) of the data byte is the first bit after the start bit.

**Direct** A LOW state on the input/output line is interpreted as logic zero and the *Least Significant Bit* (LSB) of the data byte is the first bit after the start bit.

Separate bits are used to control the logic sense and the bit ordering. This allows for nonstandard conventions to be configured.

The register bits (0 to 1) should be set to 00 before reading the initial (TS) character from the *Answer To Reset* (ATR) stream. The TS character determines the convention that the remainder of the ATR stream has been encoded with.

Inverse convention is configured by writing 11 to SCICR0[1:0] after reading the TS character and before reading any subsequent characters in the ATR.

The register bits 2 and 4 control the parity convention used (odd or even parity) and bits 3 and 5 are used to enable the handshaking mechanism. The handshaking mechanism is initiated by the receiver pulling down the input/output line whenever a parity error has occurred, and is ended by a character retry. Separate controls exist for the transmit and receive paths. The maximum number of attempts made to either transmit or receive a character is specified in the SCIRETRY register.

Character retry is not applied during ATR reception, hence this handshake should be programmed initially with the value 0x0.

Bits 2 to 5 should be set to 0xa if the T=0 protocol is requested by the contents of the initial (TS) character of the ATR stream. Table 3-3 shows bit assignments for SCICRO.

| Bits | Name     | Туре       | Function                                                                                                                                                                                                                                                                                                                                                    |

|------|----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5    | RXNAK    | Read/write | Enables character receipt handshaking.<br>If TXNAK = 0, the SCI pulls the input/output line<br>LOW if it detects a parity error.<br>If TXNAK = 1, the SCI does not pull the input/output<br>line LOW if it detects a parity error.                                                                                                                          |

| 4    | RXPARITY | Read/write | Receive parity setting.<br>0 = Even parity.<br>1 = Odd parity.                                                                                                                                                                                                                                                                                              |

| 3    | TXNAK    | Read/write | Enables character transmission handshaking.<br>If TXNAK = 0, the SCI does not check to see if the<br>receiver has pulled the input/output line LOW to<br>indicate a parity error.<br>If TXNAK = 1, the SCI checks, after each character<br>has been transmitted, to see if the receiver has pulled<br>the input/output line LOW to indicate a parity error. |