This document describes the legacy ARM *Embedded Cross Trigger* component. Do not confuse this with the CoreSight™ *Cross Trigger Interface* and related componets, that are described in the *CoreSight™ Components Technical Reference Manual* (ARM DDI 0341)

## **Embedded Cross Trigger**

Revision: r0p0

**Technical Reference Manual**

### Embedded Cross Trigger Technical Reference Manual

Copyright © 2003. All rights reserved.

#### **Release Information**

The following changes have been made to this document.

### Change history

| Date       |     | Issue | e Change             |

|------------|-----|-------|----------------------|

| 22 July 20 | 003 | A     | First issue for r0p0 |

### **Proprietary Notice**

Words and logos marked with  $^{\circ}$  or  $^{\text{tot}}$  are registered trademarks or trademarks owned by ARM Limited, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### **Web Address**

http://www.arm.com

### Contents

# **Embedded Cross Trigger Technical Reference Manual**

|           | Prefac     | About this book              |       |

|-----------|------------|------------------------------|-------|

| Chapter 1 | Introd     |                              |       |

|           | 1.1<br>1.2 | About the ARM debug system   |       |

| Chapter 2 | Functi     | onal Description             |       |

|           | 2.1        | Functional overview          |       |

|           | 2.2        | Trigger interface            |       |

|           | 2.3        | Channel interface            |       |

|           | 2.4        | AHB interface                |       |

|           | 2.5<br>2.6 | CTI register access          |       |

| Chapter 3 | Progra     | ammer's Model                |       |

|           | 3.1        | About the programmer's model | . 3-2 |

|           | 3.2        | Summary of CTI registers     |       |

|           | 3.3        | Register descriptions        |       |

| Chapter 4  | Programmer's Model for Test |                                      |       |  |

|------------|-----------------------------|--------------------------------------|-------|--|

| -          | 4.1                         | ECT/CTI test harness overview        | . 4-2 |  |

|            | 4.2                         | Scan testing                         |       |  |

|            | 4.3                         | Test registers                       |       |  |

| Appendix A | Sign                        | al Descriptions                      |       |  |

| • •        | A.1                         | ECT CTI AMBA AHB signals             | A-2   |  |

|            | A.2                         | ECT clock, enable, and reset signals |       |  |

|            | A.3                         | ECT synchronization bypass signals   |       |  |

|            | A.4                         | ECT CTI subsystem signals            | . A-6 |  |

|            | A.5                         | ECT channel interface signals        | . A-7 |  |

|            | A.6                         | Scan test control signals            | . A-8 |  |

|            |                             |                                      |       |  |

| Appendix B | Timi                        | ng Requirements                      |       |  |

|            | B.1                         | AHB interface timing                 | B-2   |  |

|            | B.2                         | ECTCTMCLK domain timing              | B-4   |  |

|            | B.3                         | ECTCTICLK domain timing              | B-5   |  |

|            |                             |                                      |       |  |

|            | Glos                        | sary                                 |       |  |

# List of Tables Embedded Cross Trigger Technical Reference Manual

|            | Change history                                          |      |

|------------|---------------------------------------------------------|------|

| Table 2-1  | Bypass modes                                            | 2-23 |

| Table 2-2  | Example subsystem wrapper inputs                        | 2-23 |

| Table 2-3  | Example subsystem wrapper outputs                       | 2-24 |

| Table 3-1  | CTI register summary                                    |      |

| Table 3-2  | CTI Control Register bit assignments                    | 3-5  |

| Table 3-3  | CTI Status Register bit assignments                     | 3-5  |

| Table 3-4  | CTI Lock Enable Register bit assignments                | 3-6  |

| Table 3-5  | CTI Protection Enable Register bit assignments          | 3-7  |

| Table 3-6  | CTI Interrupt Acknowledge Register bit assignments      | 3-7  |

| Table 3-7  | CTI Application Trigger Set Register bit assignments    | 3-8  |

| Table 3-8  | CTI Application Trigger Clear Register bit assignments  |      |

| Table 3-9  | CTI Application Pulse Register bit assignments          | 3-9  |

| Table 3-10 | CTI Trigger to Channel Enable Registers bit assignments | 3-9  |

| Table 3-11 | CTI Channel to Trigger Enable Registers bit assignments | 3-10 |

| Table 3-12 | CTI Trigger In Status Register bit assignments          | 3-10 |

| Table 3-13 | CTI Trigger Out Status Register bit assignments         | 3-11 |

| Table 3-14 | CTI Channel In Status Register bit assignments          | 3-11 |

| Table 3-15 | CTI Channel Out Status Register bit assignments         | 3-12 |

| Table 3-16 | CTIPERIPHID0 Register bit assignments                   | 3-13 |

| Table 3-17 | CTIPERIPHID1 Register bit assignments                   | 3-13 |

|            |                                                         |      |

| Table 3-18 | CTIPERIPHID2 Register bit assignments | 3-14 |

|------------|---------------------------------------|------|

| Table 3-19 | CTIPERIPHID3 Register bit assignments | 3-14 |

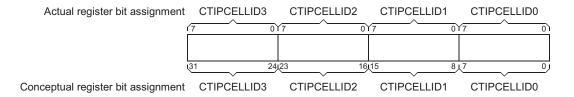

| Table 3-20 | CTIPCELLID0 Register bit assignments  | 3-15 |

| Table 3-21 | CTIPCELLID1 Register bit assignments  | 3-15 |

| Table 3-22 | CTIPCELLID2 Register bit assignments  | 3-16 |

| Table 3-23 | CTIPCELLID3 Register bit assignments  | 3-16 |

| Table 4-1  | Test registers memory map             | 4-5  |

| Table 4-2  | CTIITCR Register bit assignments      | 4-6  |

| Table 4-3  | CTIITIP0 Register bit assignments     | 4-6  |

| Table 4-4  | CTIITIP1 Register bit assignments     | 4-6  |

| Table 4-5  | CTIITIP2 Register bit assignments     | 4-7  |

| Table 4-6  | CTIITIP3 Register bit assignments     |      |

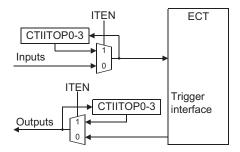

| Table 4-7  | CTIITOP0 Register bit assignments     |      |

| Table 4-8  | CTIITOP1 Register bit assignments     |      |

| Table 4-9  | CTIITOP2 Register bit assignments     |      |

| Table 4-10 | CTIITOP3 Register bit assignments     |      |

| Table A-1  | ECT CTI AMBA AHB signals              | A-2  |

| Table A-2  | Clock, enable, and reset signals      | A-4  |

| Table A-3  | CTI synchronization bypass signals    | A-5  |

| Table A-4  | ECT CTI subsystem signals             | A-6  |

| Table A-5  | ECT channel interface signals         | A-7  |

| Table A-6  | Scan test control signals             | A-8  |

| Table B-1  | AHB interface timing requirements     |      |

| Table B-2  | ECTCTMCLK domain timing requirements  |      |

| Table B-3  | ECTCTICLK domain timing requirements  | B-5  |

# List of Figures **Embedded Cross Trigger Technical Reference Manual**

| rigure i-i  | Example dual-core cross-ingger system     | . ।-৩ |

|-------------|-------------------------------------------|-------|

| Figure 2-1  | Example ECT system                        | . 2-3 |

| Figure 2-2  | Simple ECT system                         | . 2-4 |

| Figure 2-3  | Trigger interface                         |       |

| Figure 2-4  | Example of ARM core subsystem connections | . 2-6 |

| Figure 2-5  | CTI0 ports                                | . 2-7 |

| Figure 2-6  | CTI1 ports                                | . 2-8 |

| Figure 2-7  | Stacked ECT systems                       | . 2-9 |

| Figure 2-8  | Channel interface connections             | 2-10  |

| Figure 2-9  | Standard synchronization                  | 2-12  |

| Figure 2-10 | CTI structure overview                    | 2-16  |

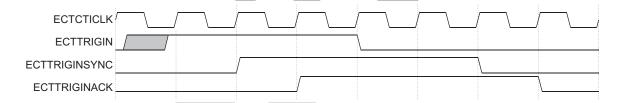

| Figure 2-11 | ECTTRIGIN handshaking                     | 2-17  |

| Figure 2-12 | ECTTRIGIN handshaking timing              | 2-17  |

| Figure 2-13 | Input wrapper signal synchronization      | 2-18  |

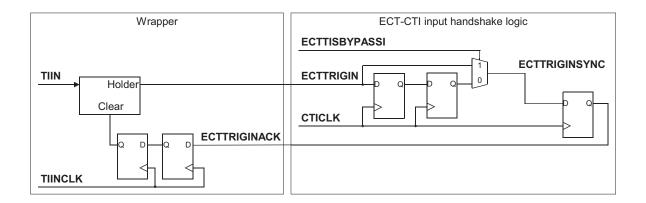

| Figure 2-14 | ECTTRIGOUT handshaking logic              | 2-19  |

| Figure 2-15 | ECTTRIGOUT timing                         | 2-20  |

| Figure 2-16 | Example output wrapper configurations     | 2-21  |

| Figure 2-17 | Single CI of CTM                          | 2-25  |

| Figure 2-18 | Handshaking signalling in the CTM         | 2-26  |

| Figure 2-19 | CTM timing                                | 2-27  |

| Figure 2-20 | Stacked CTMs                              | 2-29  |

|             |                                           |       |

| Figure 2-21 | ECTCHIN handshake                                   | 2-30 |

|-------------|-----------------------------------------------------|------|

| Figure 2-22 | ECTCHIN handshake timing                            | 2-30 |

| Figure 2-23 | ECTCHOUT circuit                                    | 2-31 |

| Figure 2-24 | ECTCHOUT handshake timing (ECTCISBYPASS = 0)        | 2-32 |

| Figure 2-25 | ECTCHOUT handshake timing (ECTCISBYPASS = 1)        | 2-32 |

| Figure 2-26 | ECTCHOUT handshake timing ECTCHOUT held             | 2-33 |

| Figure 2-27 | Channel handshake interface connections             |      |

| Figure 2-28 | AHB interface signals                               | 2-35 |

| Figure 2-29 | CTI structure                                       | 2-37 |

| Figure 2-30 | Registers controlling the events from the core      | 2-38 |

| Figure 2-31 | Registers controlling the events to the core        | 2-39 |

| Figure 2-32 | Application-driven trigger                          | 2-40 |

| Figure 2-33 | System deadlock                                     | 2-40 |

| Figure 2-34 | Wrapper to condition DBGRQ signal                   | 2-41 |

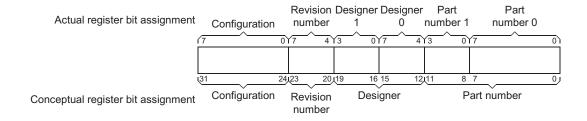

| Figure 3-1  | Peripheral Identification Registers bit assignments | 3-12 |

| Figure 3-2  | Identification Registers bit assignments            | 3-15 |

| Figure 4-1  | Integration logic                                   | 4-2  |

| Figure B-1  | AHB interface signals                               | B-2  |

| Figure B-2  | ECTCTMCLK domain signals                            | B-4  |

| Figure B-3  | FCTCTICLK domain signals                            | B-5  |

### **Preface**

This preface introduces the *Embedded Cross Trigger r0p0 Technical Reference Manual*. It contains the following sections:

- About this book on page x

- Feedback on page xiv.

### About this book

This book provides user information for the *Embedded Cross Trigger* (ECT).

### Intended audience

This book is written for hardware engineers implementing *System-on-Chip* (SoC) designs. It provides information to enable designers to integrate the ECT within their system.

### Using this book

This book is organized into the following chapters:

### Chapter 1 Introduction

Read this chapter for an introduction to the ARM Debug System, and ECT and its interfaces.

### Chapter 2 Functional Description

Read this chapter for a description of the major functional blocks of the ECT.

### Chapter 3 Programmer's Model

Read this chapter for a description of the registers and programming details of the ECT Cross Trigger Interface blocks.

### Chapter 4 Programmer's Model for Test

Read this chapter for a description of the test registers of the ECT Cross Trigger Interface blocks.

### Appendix A Signal Descriptions

Read this appendix for descriptions of signals that interface with the ECT.

### Appendix B Timing Requirements

Read this chapter for descriptions of the timing requirements for the ECT interfaces.

### Product revision status

The *rnpnvn* identifier indicates the revision status of the product described in this document, where:

**rn** Identifies the major revision of the product.

**pn** Identifies the minor revision or modification status of the product.

**vn** Identifies a version that does not affect the external functionality of the

product.

### Typographical conventions

The following typographical conventions are used in this book:

italic Highlights important notes, introduces special terminology,

denotes internal cross-references, and citations.

bold Highlights interface elements, such as menu names. Denotes

ARM processor signal names. Also used for terms in descriptive

lists, where appropriate.

monospace Denotes text that can be entered at the keyboard, such as

commands, file and program names, and source code.

monospace Denotes a permitted abbreviation for a command or option. The

underlined text can be entered instead of the full command or

option name.

monospace italic Denotes arguments to commands and functions where the

argument is to be replaced by a specific value.

monospace bold Denotes language keywords when used outside example code.

### Other conventions

This document uses other conventions. They are described in the following sections:

- Signals

- Bytes, halfwords, and words on page xii

- Bits, bytes, k, and M on page xii

- Register fields on page xii.

### **Signals**

When a signal is described as being asserted, the level depends on whether the signal is active HIGH or active LOW. Asserted means HIGH for active high signals and LOW for active low signals:

**Prefix n** Active LOW signals are prefixed by a lowercase n except in the case of

AHB or APB reset signals. These are named **HRESETn** and **PRESETn**

respectively.

**Prefix H** AHB signals are prefixed by an upper case H.

**Prefix P** APB signals are prefixed by an upper case P.

### Bytes, halfwords, and words

Byte Eight bits.

**Halfword** Two bytes (16 bits).

Word Four bytes (32 bits).

**Doubleword** Eight bytes (64 bits).

**Quadword** 16 contiguous bytes (128 bits).

### Bits, bytes, k, and M

**Suffix b** Indicates bits.

**Suffix B** Indicates bytes.

**Suffix k** When used to indicate an amount of memory means 1024. When used to

indicate a frequency means 1000.

**Suffix M** When used to indicate an amount of memory means  $1024^2 = 1048576$ .

When used to indicate a frequency means 1 000 000.

### Register fields

You must not access reserved or unused address locations because this can result in unpredictable behavior of the device.

You must write as 0 any reserved or unused bits of registers, and ignore them on read unless otherwise stated in the relevant text.

All registers bits are reset to logic 0 by a system reset unless otherwise stated in the relevant text.

Unless otherwise stated in the relevant text, all registers support read and write accesses. A write access updates the contents of the register and a read access returns the contents of the register.

All registers defined in this document can only be accessed using word reads and word writes, unless otherwise stated in the relevant text.

### **Further reading**

This section lists publications from both ARM Limited and third parties that provide additional information on developing code for the ARM family of processors.

ARM periodically provides updates and corrections to its documentation. See http://www.arm.com for current errata sheets, addenda, and the ARM Frequently Asked Questions list.

### **ARM** publications

This book contains information that is specific to the ECT. Refer to the following documents for other relevant information:

- AMBA Specification (Rev 2.0) (ARM IHI 0011)

- ETM9 Technical Reference Manual (ARM DDI 0157)

- ETM Specification (ARM IHI 0014)

- Embedded Trace Buffer Technical Reference Manual (ARM DDI 0242)

- ARM946E-S Technical Reference Manual (ARM DDI 0155).

### **Feedback**

ARM Limited welcomes feedback on both the ECT, and its documentation.

### Feedback on the ECT

If you have any problems with the ECT, contact your supplier. To help us provide a rapid and useful response, please give:

- details of the release you are using

- details of the platform you are running on, such as the hardware platform, operating system type, and version

- a small standalone sample of code that reproduces the problem

- a clear explanation of what you expected to happen, and what actually happened

- the commands you used, including any command-line options

- sample output illustrating the problem

- the version string of the tool, including the version number and date.

### Feedback on this book

If you have any comments on this book, send an email to errata@arm.com giving:

- the document title

- the document number

- the page number(s) to which your comments apply

- a concise explanation of your comments.

General suggestions for additions and improvements are also welcome.

## Chapter 1 Introduction

- About the ARM debug system on page 1-2

- About the ECT on page 1-6.

### 1.1 About the ARM debug system

The ARM debug system is described in the following sections:

- Debug system overview

- *Development tools* on page 1-5.

### 1.1.1 Debug system overview

The ARM debug system incorporates a number of *System-on-Chip* (SoC) peripherals that are specified by ARM. An example system can consist of the following blocks:

- Embedded Trace Macrocell (ETM)

- Embedded Trace Buffer (ETB)

- Embedded Cross Trigger (ECT)

- ARM microprocessor.

The ETMs consist of two peripherals:

- the embedded trace macrocell

- the ETB.

These macrocells are developed, tested, and licensed by ARM. Refer to the relevant documentation for a list of features.

The ECT provides an interface to the debug system. This enables ARM9/ETM9 subsystems to interact, that is *cross trigger*, with each other. The debug system enables debug support for multiple cores, together with cross triggering between the cores and their respective ETM9s.

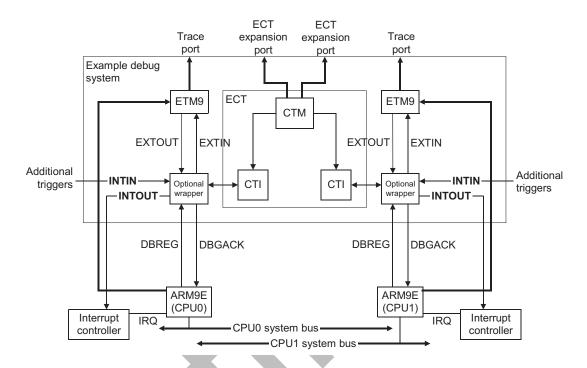

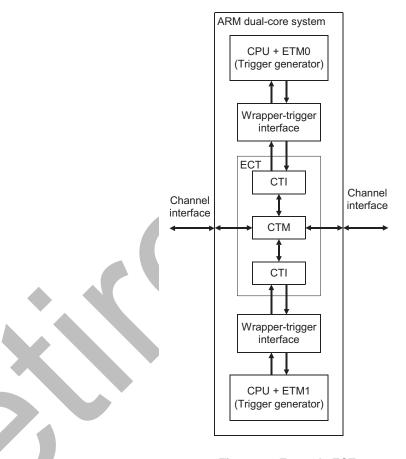

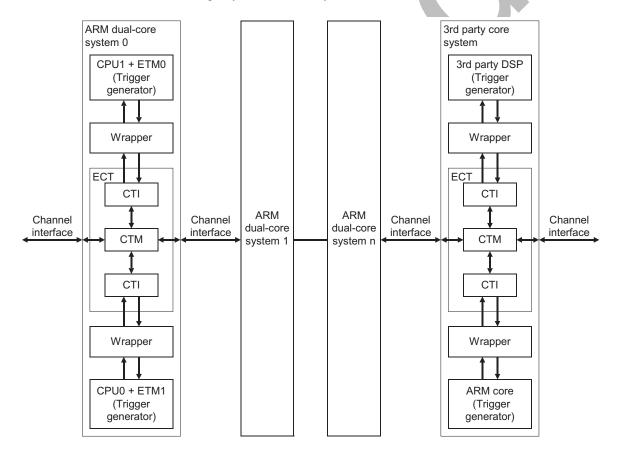

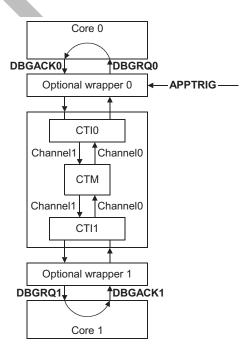

Figure 1-1 on page 1-3 shows a dual-core debug system diagram. The diagram shows two main parts:

- the embedded trace functions

- the cross trigger functions.

Figure 1-1 Example dual-core cross-trigger system

As well as the ETM9, and ECT (which contains the *Cross Trigger Interface* (CTI) and *Cross Trigger Matrix* (CTM)) there are the following components:

**ARM9E** CPU core.

### **Optional** wrapper

A simple wrapper circuit to connect the CPU core debug signals to the CTI. For an example, refer to the file Arm9CtiWrapper.v in the docs directory of the ECT deliverable.

### **Interrupt Controller (IC)**

The main function of the ECT (CTI and CTM) is to pass debug events from one processor to another. For example, the ECT can communicate debug state information from one core to another, so that program execution on both processors can be stopped at the same time if required.

Figure 1-1 on page 1-3 only contains two processors. However, you can expand the cross-trigger network to support more than two. You can also connect third-party CPU/DSP designs to the ECT providing that you have implemented a suitable wrapper. In this example, the system can have the trace function expanded to include an ETB (refer to *Embedded Trace Buffer Technical Reference Manual*).

You can connect additional sources of debug triggering signals to the ECT using the optional wrapper at the **INTIN** port as shown in Figure 1-1 on page 1-3.

You can connect the debug signals on the processor system directly to the CTI without the optional wrapper if:

- they use the same clock as the CTI

- the signals are glitch free and no special waveform shaping is required (for example edge detection).

### **Embedded trace**

In Figure 1-1 on page 1-3 the embedded trace function is supported by the use of two ETM9s. The ETMs can output directly to two independent trace ports, or you can route them to the ETBs, where you can access the trace data using the *Test Access Port* (TAP).

### **CTM**

This block combines the channel requests generated by the CTIs and broadcasts them to all other CTIs as channel triggers. This enables subsystems (ETM9 and ARM9) to cross trigger with each other.

You can also use the CTM to extend a system by connecting it to another CTM subsystem.

### CTI

This block is the interface to the CTM. Its implementation is specific to the core and other trigger sources. It provides a common programmer's model for use by the debug tools.

### ETM9

The ETM9 provides instruction and data trace information for ARM microprocessors. You can use this information with the debugger to enable easy cycle-accurate non-intrusive debugging on ARM core based embedded systems. The ETM9 provides extensive resources for event recognition to generate trigger events including:

up to sixteen address comparators

- eight data comparators

- four 16-bit counters

- a 3-state sequencer.

For further details, see the *ETM9 Technical Reference Manual* and the *ETM Specification*.

### 1.1.2 Development tools

You can use a JTAG interface to control the debug system as shown in Figure 1-1 on page 1-3, and you can access trace information through a trace port. You can access the CTI modules as a memory-mapped peripheral using its AHB interface. The debug system is supported by development tools such as *RealView® Debugger* (RVD).

### 1.2 About the ECT

The ECT provides a mechanism for multiple microprocessor based subsystems to send and receive debug triggers to and from each other. It is an *Advanced Microcontroller Bus Architecture* (AMBA) compliant *System-on-Chip* (SoC) peripheral that provides a common programmer's model for use by the debug tools.

The ECT consists of two modules:

### The Cross Trigger Interface (CTI)

This block controls the Trigger Interface (TI). The CTI combines and maps the trigger requests, and broadcasts them to all other interfaces on the ECT as channel events. When the CTI receives a channel event it maps this onto a trigger output. This enables subsystems to cross trigger with each other. The receiving and transmitting of triggers is performed through the TI.

### The Cross Trigger Matrix (CTM)

This block controls the distribution of channel events. It provides *Channel Interfaces* (CIs) for connection to either a CTI or CTM. This enables multiple ECTs to be connected to each other.

### 1.2.1 Features of the ECT

The ECT has the following features:

- cross triggering of multiple ARM9E cores

- support for glueless, multiple, stacked ECTs

- real-time access memory-mapped registers

- test registers for integration and production testing

- two channel interfaces, each with four event channels

- two trigger interfaces, each with eight input and output triggers

- standard handshaking interface that can be adapted to the user system with the use of a simple wrapper

- AHB mapped, you can access all the registers (4KB) through this interface

- ECT application trigger

- handshaking and synchronization bypass ports for lower latency triggering of synchronous systems

- lock register for protection against accidental register writes

- CTI Protection Enable Register to prevent User mode code access.

### 1.2.2 Trigger input events

The system supports the following examples of trigger input events:

**DBGACK** Enables debug cross triggering between cores.

**ETMEXTOUT** Enables triggering of one or more cores from an ETM trigger.

**INTIN** Enables cross triggering of one or more cores from an external

interrupt.

**APPTRIG** An internal event generated inside the CTI. This is accessible

using the AHB bus/tap controller and enables a debugger to force

a channel event using the configuration registers.

The ECT has two types of event interfaces:

- two *Trigger Interfaces* (TIs) connecting to the microprocessor subsystems

- two Channel Interfaces (CIs) connecting to other ECT CIs enabling ECTs to be connected to each other.

The microprocessor subsystem can be an ARM9/ETM9 combination or a user-specific subsystem, for example DSP. The ECT combines the trigger requests generated by the subsystems and broadcasts them to other subsystems as channel events. This enables subsystems to cross trigger with each other.

This Technical Reference Manual provides enough information for developers to design a subsystem that can interface to the ECT.

### 1.2.3 Events

The ECT provides a standard interface enabling the following classes of cross trigger event to be supported using a simple wrapper, four external events and one internal event:

**Conditioned** Keeps the output active for one clock cycle after an acknowledgement is received.

**Level/pulse** Used when trigger destination is level sensitive, the signal is active for only one clock cycle.

Keeps the output active until it is cleared by a corresponding clear

register.

Sticky

**NoAck** Used when the output follows the input trigger and does not require an acknowledgement.

### Software programmable

Used by the application to trigger events under software control, this enables a debugger to force an event using the configuration registers.

If you want to add a further class you have to add a wrapper to the TI to shape your specific signals to the required format. For more information see *Cross trigger events* on page 2-20.

# Chapter 2 Functional Description

This chapter describes the function of the blocks in the ECT. It contains the following sections:

- Functional overview on page 2-2

- Trigger interface on page 2-15

- *Channel interface* on page 2-25

- *AHB interface* on page 2-35

- CTI register access on page 2-36

- *ECT registers* on page 2-37.

### 2.1 Functional overview

This chapter describes how you can implement subsystems to enable a given core to interface to the ECT using a *Trigger Interface* (TI). The implementation of the ECT provides a common programmer's model for use by the debug tools.

This is described in the following sections:

- About the ECT system

- Interfaces handshake protocol on page 2-11

- Synchronization on page 2-11

- *Clock information* on page 2-13

- *Mapping* on page 2-14.

### 2.1.1 About the ECT system

The ECT function is supported by the use of the *Trigger Interface* (TI) and the *Channel Interface* (CI). The TI is the interface to the core subsystems,

Figure 2-1 on page 2-3 shows an example ECT system.

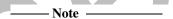

Figure 2-1 Example ECT system

Figure 2-1 shows the TI and the optional user-defined wrapper to the TI. The TI uses handshake signalling because it is robust with asynchronous systems, and it automatically adapts to changes in clock frequency of components connected to the ECT. The CI is generic so that you do not have to modify the ECT design if a different trigger generator subsystem is used. In most cases you require a simple wrapper to connect a trigger generator subsystem to the ECT.

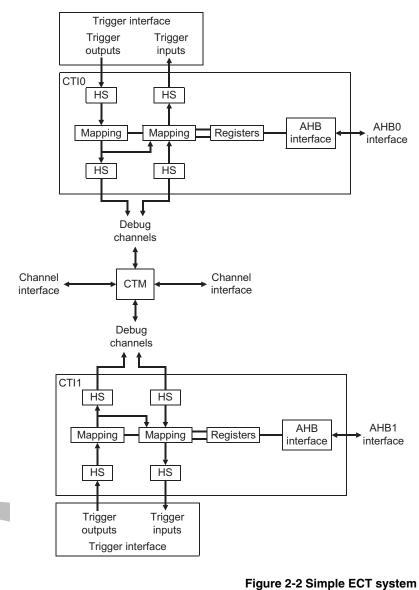

Figure 2-2 on page 2-4 shows a simple ECT system.

**3**

Figure 2-2 shows the following:

**ECT** Comprising two CTIs and one CTM.

CTI Interface between the cross trigger network (the CTM) and the processor system (for example, CPU and ETM).

**CTM**

The cross trigger network providing interconnections between CTIs. The CTM contains four ports, each port containing Debug Channel In and Debug Channel Out connections. When a Debug Channel In receives a signal, it is output to the Debug Channel Out of the three other ports.

**HS** Handshaking circuitry.

### **AHB** interface

Programs the configuration and status registers of the CTI. All transactions on the AHB slave programming bus of the ECTs are 32 bits wide. This eliminates endian issues when programming the ECTs.

The register block controls:

- the mapping from trigger inputs to debug channels

- the mapping from debug channels to trigger outputs.

You can control the registers using the AHB interface.

You can easily expand the system by using the two expansion ports provided by each ECT to stack the ECTs to each other without requiring external components (see *Stacking ECTs* on page 2-9).

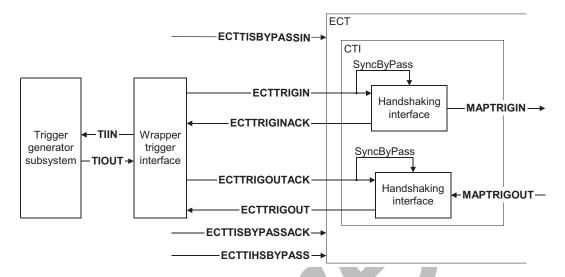

Figure 2-3 on page 2-6 shows the following TI buses:

- ECTTRIGIN[7:0] for trigger in

- ECTTRIGINACK[7:0] for trigger in acknowledge

- **ECTTRIGOUT[7:0]** for trigger out

- **ECTTRIGOUTACK[7:0]** for trigger out acknowledge

- inputs ECTTISBYPASSIN[7:0] and ECTTISBYPASSACK [7:0] enable the buses to bypass the synchronization logic on the respective bits of ECTTRIGIN and ECTTRIGOUTACK

- inputs **ECTTIHSBYPASS**[7:0] enable the handshaking for the respective bits of **ECTTRIGOUT**[7:0] to be bypassed, when the outputs do not require an acknowledgement.

Figure 2-3 Trigger interface

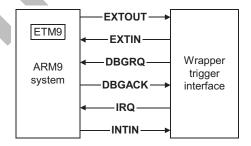

Figure 2-4 shows an example of the typical signals that make up the trigger interface input (**TIIN**) and trigger interface output (**TIOUT**) buses to the wrapper.

Figure 2-4 Example of ARM core subsystem connections

Depending on the subsystem:

- 1. An event on **EXTOUT**, **DBGACK**, and **INTIN** (all of which can make up the **TIIN** bus) can be propagated into the ECT through the wrapper block onto one of the **ECTTRIGIN** signals.

- 2. The **ECTTRIGIN** signal is propagated though the ECT onto the other TIs and CIs.

- 3. This event can be forwarded to the next core as:

- a debug request, **DBGRQ**

- an ETM event. EXTIN

- an interrupt, **IRQ**.

Each type of cross trigger event has a specific behavior that requires the wrapper to function in a certain way, as described in *Cross trigger events* on page 2-20.

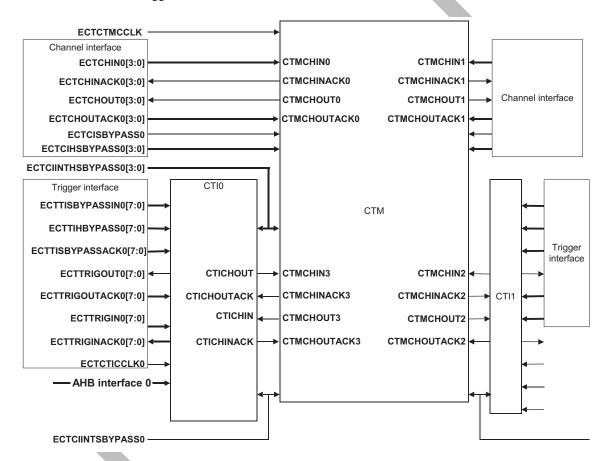

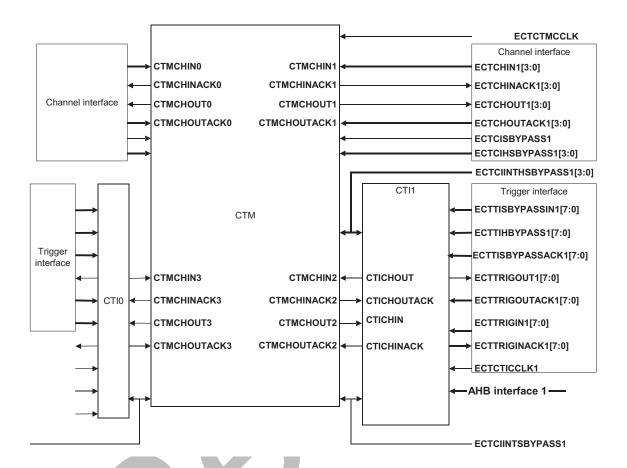

Figure 2-5 and Figure 2-6 on page 2-8 show that a single ECT within a system has two trigger interfaces and two channel interfaces.

Figure 2-5 CTI0 ports

Figure 2-6 CTI1 ports

The CTI takes the trigger inputs from the TI and enables them onto channels within the ECT. The ECT supports up to four channels equating to ECTCHIN[3:0] and ECTCHINOUT[3:0].

The CI comprises the following buses:

- ECTCHOUT[3:0] for channel out

- ECTCHOUTACK[3:0] for channel out acknowledge

- ECTCHIN[3:0] for channel in

- ECTCHINACK[3:0] for channel in acknowledge

- inputs ECTCISBYPASS[3:0] to enable the buses to bypass the handshaking and synchronization logic of ECTCHIN[3:0]

- inputs **ECTCIINTHSBYPASS**[3:0] and **ECTCIINTSBYPASS**[3:0] to bypass the same logic for the internal Channel Interfaces between the CTI and CTM.

### **Stacking ECTs**

Figure 2-7 shows how the CI enables the ECT to be connected to other ECT systems. Because there are two CIs you can stack the ECTs. This provides a very flexible solution for expanding debug access for multi-core products. You can stack the ECTs within a single system or across systems.

Figure 2-7 Stacked ECT systems

When you stack a number of ECTs together you must ensure that no timing violating paths are created. It is expected that timing violations will only occur when a large number of ECTs are used and all the synchronization bypasses are enabled. If violations are created you can pipeline the signal path by enabling the synchronization logic on some of the ECTs, so avoiding the timing violation.

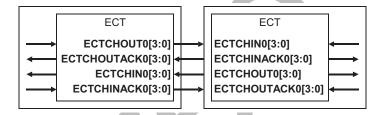

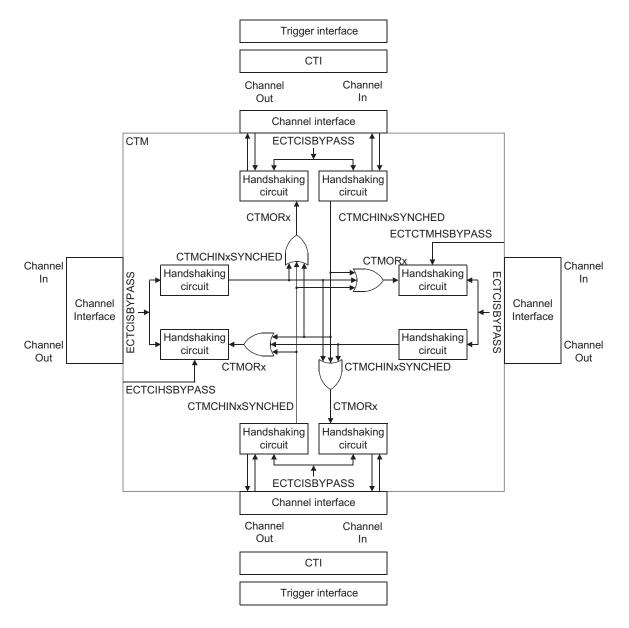

Figure 2-8 shows an example of how the generic debug CI is connected, as shown in Figure 2-7 on page 2-9. This figure shows an example of the connections required between the two CTMs.

Figure 2-8 Channel interface connections

You can connect the CI port to another CI port, as long as the connections are swapped, for example **ECTCHOUT** connected to **ECTCHIN**, and **CTMCHOUTACK** connected to **CTMCHINACK**.

When one TI sends a trigger:

- 1. It is propagated to the CTM, through the CTI.

- 2. The CTM propagates it to the other TIs and ECTs using its CIs.

- 3. These other ECTs send the trigger to all the TIs connected to it.

For example, if the CPU0 in Figure 2-7 on page 2-9 generates a trigger, and if its corresponding mapping logic in the CTI is enabled, this trigger event is mapped into a channel event and enters the CTM in the ARM dual-core system 0. The event is then sent to the CTI for CPU1, as well as all other ECTs in the system through the channel interface. The combinatorial path between one TI and another on a separate subsystem is increased by the propagation delay across the other CTMs. The synchronization between the systems is managed by the handshaking internal to the CTM components that you can bypass if required.

**ECTDGBEN** turns off the CI and TI inputs and outputs in the CTI modules, effectively turning off the mapping logic. To save power you can use this signal to ensure the ECT interfaces are off in non-debug mode.

### 2.1.2 Interfaces handshake protocol

There is no edge detection in the ECT. An event signal is transmitted as a level. If you want to have edge detection or single pulse output you must implement the required shaping logic in the external wrapper.

To avoid any incompatibility, the following protocol has been defined:

- Only logic 1 is interpreted as an event.

- If the handshake is enabled, an output must stay active until an acknowledgement by hardware (or optionally acknowledged by software for the TI) is received, even if the acknowledge signal driver is deactivated.

If the handshaking is not bypassed the ECT can only handle one-shot events. If events are close to one another (multi-shot) and mapped to the same channel they are possibly merged into one event on an output trigger. For debug events such as breakpoint, trace start, and trace stop this does not cause a problem because input events mapped to the same triggers are required to do the same thing.

Events arising from different interfaces but mapped to the same channel might also be merged. This is acceptable because the mapping logic would have been programmed to allow this. Events can be merged because blocks handshake between asynchronous clock domains or channels events are mapped onto the same output trigger.

If the events broadcast on the ECT emanate from synchronous clock domains then you can bypass the handshaking logic. The output does not receive an acknowledgement (Noack trigger class). In such cases you can use the ECT to transmit multiple shot events. The output has to remain active for at least one clock cycle to ensure it is captured at the destination interface.

### 2.1.3 Synchronization

Systems where events broadcast on the ECT can emanate from asynchronous clock domains must observe the following rules:

- 1. Register input events on page 2-12. Any signal that is an input of the ECT must be glitch free to avoid any false event. The wrapper can perform glitch removal as necessary.

- 2. *Synchronize output events* on page 2-12. The outputs of the ECT must be synchronized to the local clock domain before use by the subsystem, if such synchronization is not already present in the subsystem. The wrapper performs synchronization when necessary.

### Register input events

The concern here is that a glitch on an output of the subsystem is propagated in the ECT and can be interpreted as an event. Also, the synthesis tools do not provide the necessary mechanism to constrain signals so that they are glitch free.

As an example, in an ARM9E design, **DBGACK** is the output of a combinatorial circuit (three-input OR gate). There is no way to ensure that a change of state on the inputs does not result in a glitch on the **DBGACK** signal, which can be fetched by an asynchronous circuit.

Considering design approaches suitable for delivery as reusable IP, the events from the processor cores must be registered inside the wrapper before being sent to the ECT. A single register can be used in this case or you can enable synchronization logic in the ECT for that specific trigger input adding an extra clock cycle to the latency.

### Synchronize output events

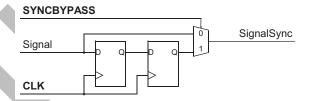

Figure 2-9 shows that a standard two-register synchronization is used.

Figure 2-9 Standard synchronization

It is important that you consult the design rules on the target process and the standard cell libraries to see if there are any restrictions or recommendation in relation to synchronizers. For example, the library rules might require the use of specially designed synchronization registers, or require that registers forming a synchronization chain must be placed in close proximity to each other.

### Latency

The latency corresponds to the number of cycles necessary from the time one signal enters a ECT until it is propagated to another processor. The path in the CTI and CTM is combinatorial, so that the latency is only due to the handshaking circuits. This means that, in the worst case, the latency is the sum of:

- one clock cycle of the CTI sending the event to the matrix (removal of the glitch)

- the combinatorial delay caused by the propagation of a **ECTTRIGIN** event to a **ECTTRIGOUT** output

- two clock cycles of the CTI receiving the event from the matrix (synchronization to the clock of the receiving device).

In certain cases, it might be possible to reduce this latency:

- If the signal sent by the processor is the output of a flip-flop. In this case you do not have to register the signal because it is glitch-free.

- If the core being interfaced to already features synchronization logic internally. For example the processor has been specified to receive an asynchronous signal.

- If all the subsystems are synchronous. In this case the TI bypass signals, **ECTTISBYPASSACK** and **ECTTISBYPASSIN**, and the CI bypass signals **ECTCISBYPASS** and **ECTCIINTSBYPASS**, can be activated. However, this path must respect the layout and synthesis timing constraints.

### 2.1.4 Clock information

When a processor clock is stopped (waiting for an interrupt for example), the corresponding CTI can receive an event from the CTM. When the CTI clock is the same as the subsystem and the handshaking is not bypassed, the CTM keeps the signal active until an acknowledgement is received, which only occurs when the clock is started again. In this case, out-of-date events can happen on the core. This does not inhibit the channel being used by other processors.

However, if the CTI clock differs from the local processor clock (for example, gated differently), it is possible for the CTI to raise an event to the core using **ECTTRIGOUT**, while the processor clock is off. If it has to be avoided, the processor must disable its CTI before stopping the clock.

It is assumed that in most systems the **ECTCTICLK** is connected to the same clock as its local processor and the **ECTCTMCLK** is connected to the fastest processor clock in the system so reducing the trigger latency and the requirement for clock enables ports.

If a CTI is going to be disabled while the processor enters a clock stopped mode, ARM recommends that:

- the CTI turns off the event-to-channel mapping, so that unwanted events are not generated to the CTM

- the channel-to-event mapping circuit is turned off or disabled for a few clock cycles after the clock is on.

### 2.1.5 Mapping

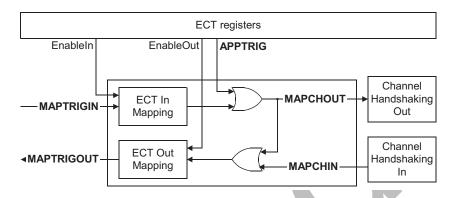

The mapping blocks control the driving of the CTIs output ports.

# 2.2 Trigger interface

The *Trigger Interface* (TI) is described in the following sections:

- About the TI

- ECTTRIGIN handshake on page 2-17

- Trigger interface wrapper input on page 2-17

- ECTTRIGOUT handshake on page 2-18

- Cross trigger events on page 2-20

- Example wrapper on page 2-23.

#### 2.2.1 About the TI

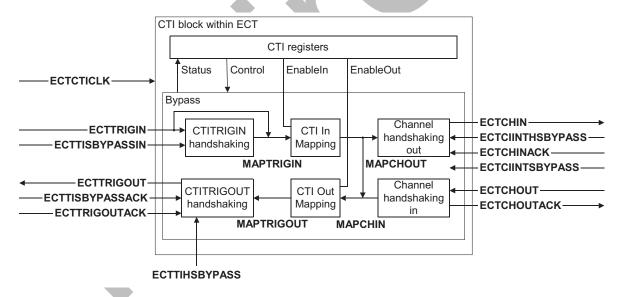

The TI is generic. This means that you do not have to modify the CTI design if you are using a different subsystem. In most cases you require a simple wrapper to connect a subsystem to the CTI. Figure 2-10 on page 2-16 shows an overview of the CTI, part of the ECT structure. The CTI interfaces to a subsystem with the CTM, which in turn communicates with the ECT interfaces. The CTI enables the subsystem to broadcast and respond to (enabled) events on the CTM.

Figure 2-10 CTI structure overview

The CTI maps:

- trigger inputs onto channels

- channel inputs onto trigger outputs.

The CTI takes cross trigger event inputs from its associated subsystem, or configuration register (an application-derived trigger event), and generates outputs on the appropriate channels as defined by the configuration registers for the CTM.

The subsystem programs the configuration registers of the CTI it is connected to by using the AHB interface on the CTI.

**ECTTRIGIN**, as shown in Figure 2-3 on page 2-6, is the collective name for any event from the subsystem. If the **ECTTRIGIN** signals do not require synchronization the synchronization block can be bypassed using the **ECTTISBYPASSIN** inputs. Depending on the configuration registers, the resultant signal can be mapped to a channel.

**ECTTRIGOUT** is the collective name for any event from the TI. You can bypass the **ECTTRIGOUTACK** synchronization block using the **ECTTISBYPASSACK** inputs.

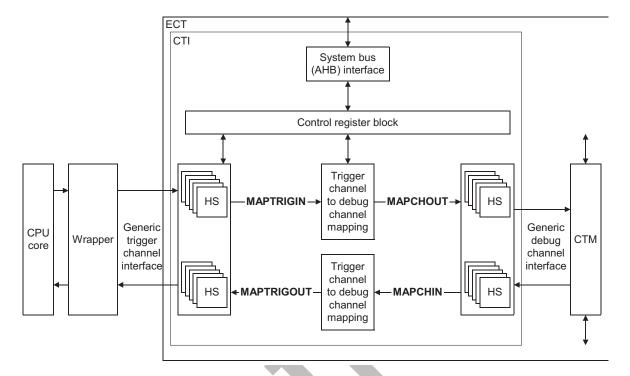

#### 2.2.2 ECTTRIGIN handshake

Figure 2-11 shows the circuit required for the **ECTTRIGIN** handshaking. You can bypass the synchronization if all the subsystems are synchronous, by asserting the relevant bit of **ECTTISBYPASSIN**[7:0] HIGH.

Figure 2-11 ECTTRIGIN handshaking

Figure 2-12 is an example of a timing diagram of the circuit shown in Figure 2-11, when **ECTTISBYPASSIN** is inactive so enabling the synchronization logic.

Figure 2-12 ECTTRIGIN handshaking timing

# 2.2.3 Trigger interface wrapper input

To interface the ECT into a system you might have to apply a wrapper to the TI. The implementation of the CTI only detects a level 1 as an event. Therefore the signal might have to pass through a wrapper to adapt its behavior (Inverter, convert for example). In most cases, where adaptation is not required and when the ECTCTICLK is synchronous or slower than the subsystem core clock, no wrapper is required. For example, TIIN is fed straight through to the ECTTRIGIN.

There might be a case where the trigger signals clock domain, **THNCLK** and **ECTCTICLK**, are not synchronous. Figure 2-13 on page 2-18 shows that if the triggers are operating in a higher frequency clock domain (**THNCLK**) the wrapper must have logic that captures and holds the trigger until it has been acknowledged by the ECT.

Figure 2-13 Input wrapper signal synchronization

If the input driver of **THN** requires an acknowledgement signal then the wrapper must ensure any necessary synchronization takes place.

Assuming the clock domains are synchronous, you can connect the **TIIN** inputs to the **ECTTRIGIN**. The example wrapper supplied with the ECT assumes this is the case. See *Cross trigger events* on page 2-20 and *Example wrapper* on page 2-23.

#### 2.2.4 ECTTRIGOUT handshake

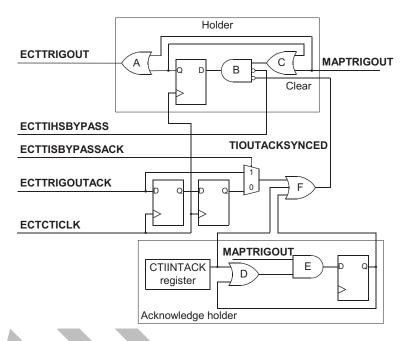

Figure 2-14 on page 2-19 shows the **ECTTRIGOUT** handshaking logic.

Figure 2-14 ECTTRIGOUT handshaking logic

When an event is detected on one bit of **MAPTRIGOUT**, it is propagated directly to the corresponding bit of **ECTTRIGOUT** through the OR gate A. If the **ECTTIHSBYPASS** signal is LOW, the signal **ECTTRIGOUT** is kept activated using the feedback loop though gates C and B, until the acknowledgement signal, **TIOUTACKSYNCED** (synchronized **ECTTRIGOUTACK**), is received into the not input of AND gate B. If you have to synchronize the **ECTTRIGOUT** signal for the subsystem you must implement the required logic in the wrapper.

Figure 2-15 on page 2-20 shows **ECTTRIGOUT** timing. If **MAPTRIGOUT** is HIGH while the acknowledgement signal has already been received, **ECTTRIGOUT** is also HIGH until **MAPTRIGOUT** is deactivated. If you are using a sticky class output, a write of HIGH to the **CTIINTACK** register is required to acknowledge the output trigger. The Acknowledge holder circuit is then used to hold the acknowledgement until the **MAPTRIGOUT** has been deactivated.

Figure 2-15 ECTTRIGOUT timing

In Figure 2-15 **ECTTIHSBYPASS** is LOW and **ECTTISBYPASSACK** is LOW (enabling acknowledgement synchronization logic). The acknowledgement signal **ECTTRIGOUTACK** is received at the same clock cycle as **ECTTRIGOUT** is propagated. This might be due to the subsystem running at a higher frequency or the **ECTTRIGOUT** being fed directly back into the **ECTTRIGOUTACK** port as in the case of level class trigger outputs as shown in Figure 2-16 on page 2-21.

If the **ECTTIHSBYPASS** signal is **HIGH**, handshake bypass is enabled and **ECTTRIGOUT** follows **MAPTRIGOUT** as gate B disables the holder and acknowledge logic so that only gate A is active.

# 2.2.5 Cross trigger events

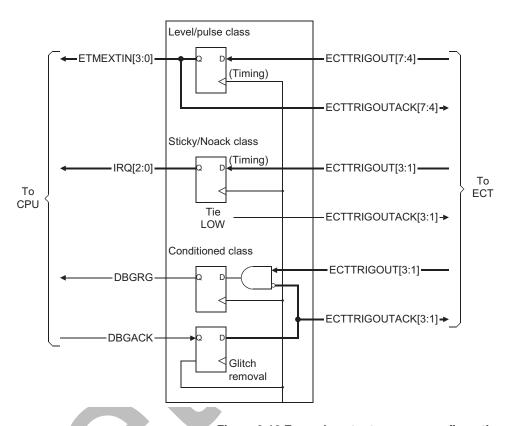

Figure 2-16 on page 2-21 shows an example wrapper for all external classes of cross trigger output event.

| Note |                                                                                                                  |

|------|------------------------------------------------------------------------------------------------------------------|

|      | ou can remove the registers with (Timing) in Figure 2-16 are included to simplify the synthesis process for this |

|      |                                                                                                                  |

Figure 2-16 Example output wrapper configurations

The external classes of cross trigger output event are:

Sticky class A typical function for a sticky class signal is an interrupt. When the ECTTRIGOUT is used to drive an interrupt signal, the output is kept active until it is cleared by a write to the corresponding bit of the CTIINTACK register. The Acknowledge holder holds the acknowledgement until the MAPTRIGOUT is deactivated. The ECTTRIGOUTACK is tied LOW, and the corresponding ECTTIHSBYPASS is LOW.

Noack class The wrapper used is the same as that for the sticky class. If the output trigger does not require an acknowledgement and all clock domains are the same, ECTTIHSBYPASS is HIGH. This means that the ECTTRIGOUT signal is the same as the MAPTRIGOUT signal.

This class is typically used where the clock domains between the source and destination are the same and the source is guaranteed to be at least one clock cycle. If the source signal is active for one clock cycle, you must ensure that there is no clock skew between source and destination.

In this class you can design the wrapper so that multiple shot events are supported. The ECT can be set up so that all handshaking is bypassed. The destination wrapper receives the source signal and then acknowledges it through another channel. When the source wrapper receives the acknowledgement it can then send another event. The logic design for the wrappers can vary according to your requirements.

#### Level/pulse class

A typical function for a level class is an ETM EXTIN signal. The ETM EXTIN input is level-sensitive. The ECTTRIGOUT has to keep the signal active for at least one clock cycle. This is achieved in the wrapper by feeding the ECTTRIGOUT back in to the ECTTRIGOUTACK. The ECTTISBYPASSACK is HIGH, ECTTIHSBYPASS is LOW, and the corresponding bit of the CTITRIGINCLEAR register is LOW.

| —— Note ———                                         |                                             |

|-----------------------------------------------------|---------------------------------------------|

| To generate a single clock cyc<br>From the wrapper. | cle pulse you must remove the timing D-type |

#### Conditioned class-

A typical function for a level class is a **DBGRQ/DBGACK** to and from an ARM core. **DBGRQ** is activated until **DBGACK** is received. The processor can enter debug mode without the ECT requesting it, for example after a breakpoint.

Most of the ARM cores do not support receiving a debug request while in debug mode. For this reason, the wrapper is required to gate the **DBGRQ** whenever **DBGACK** is asserted. The **DBGACK** signal from the CPU is a combinatorial output. Therefore even if the CTI operates in the same clock domain as the CPU, this signal must be registered in the wrapper before being used. You can also use **DBGACK** as an input trigger as shown in Figure 2-16 on page 2-21. The trigger can then be propagated to the other cores in the system. **ECTTIHSBYPASS** is LOW and **ECTCTISBYPASS** is set according to the clock domains.

If the output trigger has to be a single clock length pulse then you have to add the necessary logic to ensure correct signal shaping.

Table 2-1 shows the use of the **ECTTIHSBYPASS** and **ECTCTISBYPASS**.

Table 2-1 Bypass modes

| Bypass modes                                                                                                                                               | ECTCT | ISBYPASS | ECTTIHSBYPASS |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------|---------------|

| Handshaking and synchronization enabled. Used when clock domains are asynchronous.                                                                         | 0     |          | 0             |

| Handshaking enabled and synchronization disabled. Used when clock domains are synchronous but clock skew is unknown. Level class triggers.                 | 1     |          | 0             |

| Handshaking disabled, synchronization enable/disable. Used when clock domains are synchronous and clock skew allows. Used when no acknowledge is required. | X     |          |               |

#### 2.2.6 Example wrapper

The ECT is supplied with an example wrapper (in the docs directory) that supports an ARM9/ETM subsystem. Table 2-2 shows the configuration of the inputs from the subsystem to the wrapper.

Table 2-2 Example subsystem wrapper inputs

| Subsystem wrapper inputs | Class                        | Туре         |

|--------------------------|------------------------------|--------------|

| TIIN[0]                  | Conditioned (glitch removal) | DBGACK       |

| TIIN[1]                  | Level                        | INTIN[0]     |

| TIIN[2]                  | Level                        | INTIN[1]     |

| TIIN[3]                  | Level                        | INTIN[2]     |

| TIIN[4]                  | Level                        | ETMEXTOUT[0] |

| TIIN[5]                  | Level                        | ETMEXTOUT[1] |

| TIIN[6]                  | Level                        | ETMEXTOUT[2] |

| TIIN[7]                  | Level                        | ETMEXTOUT[3] |

The **INTIN** inputs are normally held until cleared by an interrupt service routine so in this case can be treated as a level class input.

Table 2-3 shows the configuration of the outputs from the example wrapper to the subsystem.

Table 2-3 Example subsystem wrapper outputs

| Subsystem<br>wrapper<br>outputs | Class                           | Туре        |

|---------------------------------|---------------------------------|-------------|

| TIOUT[0]                        | Conditioned (DBACK conditioned) | DBGRQ       |

| TIOUT[1]                        | Sticky                          | IRQ[0]      |

| TIOUT[2]                        | Sticky                          | IRQ[1]      |

| TIOUT[3]                        | Sticky                          | IRQ[2]      |

| TIOUT[4]                        | Level                           | ETMEXTIN[0] |

| TIOUT[5]                        | Level                           | ETMEXTIN[1] |

| TIOUT[6]                        | Level                           | ETMEXTIN[2] |

| TIOUT[7]                        | Level                           | ETMEXTIN[3] |

#### 2.3 Channel interface

This section describes the *Channel Interface* (CI):

- About the CI

- ECTCHIN handshake on page 2-29

- ECTCHOUT handshake on page 2-30

- *Channel interface connections* on page 2-33.

#### 2.3.1 About the CI

The CTM contains some sequential elements to complete the handshake signalling with the CTI.

The CI is controlled by the CTM which is a crossbar consisting of four channels and four CIs. For example **ECTCHOUT0[3:0**] represents four channels for CIo. Each channel provides a single bit output (for example **ECTCHOUT0[0]**) to each CI that is the logical OR of all the other CI input ports (for example **ECTCHINx[0]**).

You can use a channel to represent an occurrence or condition. A channel can have a dedicated meaning in a system, for example system error. Also, you can configure the use and meaning of a channel. The CI can be connected to another CI or a CTI. The ECT has four CIs, two internal and two external. The bypass controls for the internal CIs are brought to the top level of the ECT.

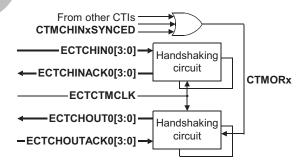

Figure 2-17 shows a block diagram for a single CI on the CTM with four channels.

Figure 2-17 Single CI of CTM

Each **ECTCHIN** input is synchronized, if required, and acknowledged. This is to inform the sending ECT or CTI that the **ECTCHIN** has been received and therefore can be cleared.

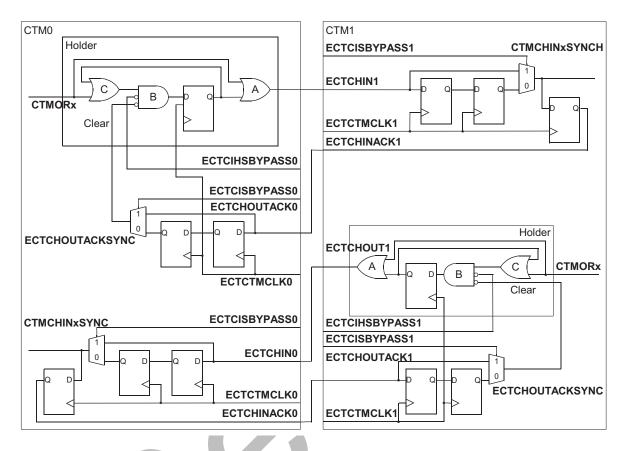

Figure 2-18 on page 2-26 shows the circuit used for CTM for all four CIs (each CI has four channels).

Figure 2-18 Handshaking signalling in the CTM

\_\_\_\_\_Note \_\_\_\_\_

The **ECTCHIN** is not routed back to its own **ECTCHOUT**. The CTI has logic to generate its own **ECTCHOUT** trigger.

The sequential elements for **ECTCHIN**, **ECTCHINACK**, **ECTCHOUT**, and **ECTCHOUTACK** signals are bused, one element for each channel, and an independent handshake is implemented for each bit.

You can synchronize the channel to capture the **ECTCHIN** if required:

- 1. The **ECTCHIN** is broadcast to each of the other CIs.

- 2. The blocks connected to these are then responsible for sending back an acknowledgement when required.

- 3. This causes the CTM to release the appropriate **ECTCHOUT** signal for that CI.

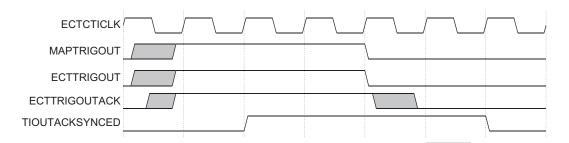

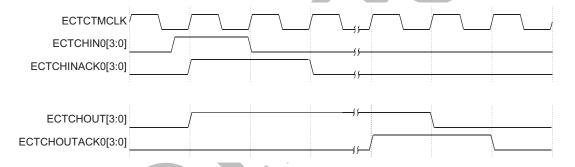

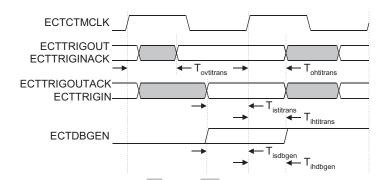

Figure 2-19 shows the timing diagram for this.

Figure 2-19 CTM timing

When the handshaking is enabled the trigger sources are decoupled from the trigger sinks, which can be in different clock domains. Also the trigger sinks are decoupled from each CI, so that a delayed ECTCHOUTACK signal from one of the blocks connected to the interface does not cause the system associated with another interface to stall. All signal synchronization and capture is achieved using ECTCTMCLK.

Handshake signalling is used because it is robust with asynchronous systems, and it automatically adapts to changes in clock frequency of components connected to the CTM. In this scheme, an event to the CTM must be held when asserted until an acknowledgement is received. The handshaking can be bypassed if required. However, the system clock domains must be the same and the source signal must be at least one clock cycle.

The CTM contains some sequential elements that generate the acknowledgement signals for each channel in the CI. The handshake is only dependent on the following clock domains:

the CTM clock domain, ECTCTMCLK

the clock domain of each block connected to the CI.

This removes the possibility of a protocol deadlock, which can occur when one core is powered off or its clock is disabled and the acknowledgement is dependent on an acknowledgement being received from all the devices subscribed to that channel.

If the handshaking is disabled **ECTCHOUT** does not require an acknowledgement. The signal follows the input **CTMORx** of the handshaking circuit. The handshaking can only be bypassed when the two clock domains are the same and clock skew is not a problem.

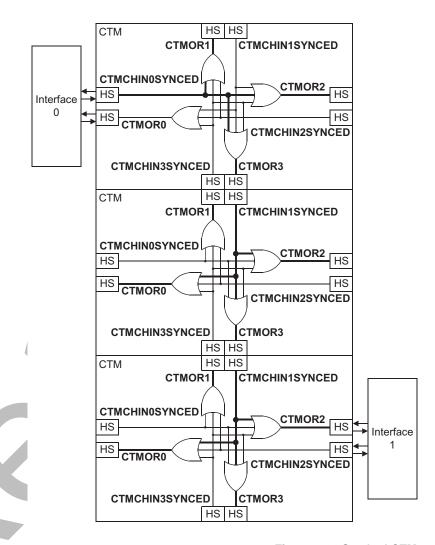

If the ECTs are stacked as shown in Figure 2-7 on page 2-9, the CTMs are connected as shown in Figure 2-20 on page 2-29. The Interface 0 generates a channel event. This event is propagated to Interface 1 as shown by the thick lines.

Figure 2-20 Stacked CTMs

# 2.3.2 ECTCHIN handshake

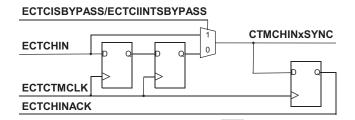

Figure 2-21 on page 2-30 shows the circuit required for the **ECTCHIN** handshaking.

Figure 2-21 ECTCHIN handshake

You can bypass the synchronization when all the subsystems are synchronous, by tying the port **ECTCISBYPASS** HIGH. This is the same circuit as used in the Figure 2-11 on page 2-17. The ECT has four **ECTCHIN** handshaking circuits and therefore four bypass ports **ECTCISBYPASS0** and **ECTCISBYPASS1** for the external CIs, and **ECTCHNTSBYPASS0** and **ECTCHNTSBYPASS1** for the internal CIs.

| Note                       | <del></del>                                              |

|----------------------------|----------------------------------------------------------|

| Both sets of bypass have t | he same function and ECTCISBYPASS is used in the rest of |

| this document.             |                                                          |

If ECTCISBYPASS is LOW the CTMCHINxSYNCHED signal is a synchronized version of the ECTCHIN signal. If HIGH, CTMCHINxSYNCH is ECTCHIN. The circuit uses CTMCHINxSYNCH, to generate the acknowledgement signal ECTCHINACK one clock cycle after CTMCHINxSYNCH is generated.

When a processor uses the same clock, you can tie the relevant bit of the **ECTCISBYPASS** HIGH so that the synchronization is not used.

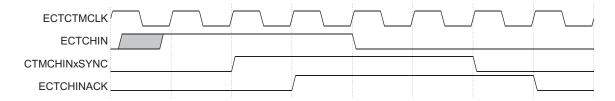

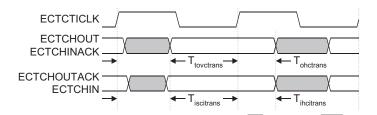

Figure 2-22 is a timing diagram of the circuit shown in Figure 2-22 when **ECTCISBYPASS** is inactive enabling the synchronization logic.

Figure 2-22 ECTCHIN handshake timing

#### 2.3.3 ECTCHOUT handshake

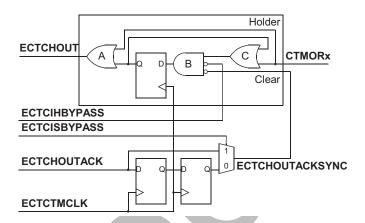

Figure 2-23 on page 2-31 shows the circuit used for the **ECTCHOUT** handshaking.

Figure 2-23 ECTCHOUT circuit

The circuit is clocked by the **ECTCTMCLK** signal, and is implemented once for each bit of the **ECTCHOUT** signal. The ECT has four **ECTCHOUT** handshaking circuits and therefore four handshaking bypass buses, **ECTCIHSBYPASS0** and **ECTCIHSBYPASS1** for the external CIs and **ECTCIINTHSBYPASS0** and **ECTCIINTHSBYPASS1** for the internal CIs.

Both sets of bypass have the same function and **ECTCIHSBYPASS** is used in the rest of this document.

When an event is detected on one bit of the **CTMORx**, it is propagated directly to the corresponding bit of **ECTCHOUT** using OR gate A. If **ECTCHSBYPASS** is LOW, the **ECTCHOUT** is kept activated using the feedback loop through gates C and B, until the acknowledgement signal **ECTCHOUTACKSYNC** is received into the Not input of AND gate B. If the **ECTCHOUT** signal has to be synchronized for the subsystem you must implement the required logic in either their CTI or CTM.

If **CTMORx** is HIGH while the acknowledgement signal has already been received, **ECTCHOUT** is also HIGH until **CMORx** is deactivated.

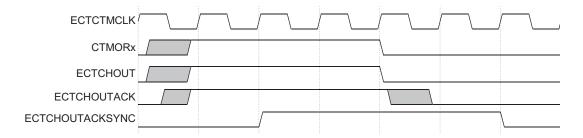

Figure 2-24 on page 2-32 shows the **ECTCHOUT** handshake timing diagram where **ECTCISBYPASS** = 0.

Figure 2-24 ECTCHOUT handshake timing (ECTCISBYPASS = 0)

In Figure 2-24 **ECTCISBYPASS** is inactive (enabling synchronization logic) and **ECTCIHSBYPASS** is inactive (enabling the handshake logic). The acknowledgement signal **ECTCHOUTACK** is received at the same clock cycle as **ECTCHOUT** is propagated. This might be because of the acknowledgement subsystem running at a higher frequency.

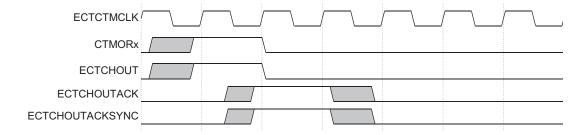

Figure 2-25 shows an example of a timing diagram for the **ECTCHOUT** handshake circuit when the frequency of the cross-trigger interface connected is the same as the cross-trigger matrix, and the acknowledgement signal **ECTCHOUTACK** is received a clock cycle after **CTMORx** is propagated.

Figure 2-25 ECTCHOUT handshake timing (ECTCISBYPASS = 1)

**ECTCISBYPASS** is HIGH and **ECTCIHSBYPASS** is LOW. The acknowledgement **ECTCHOUTACK** is received early enough so that the holding circuit is not required to hold the **CTMORx** value.

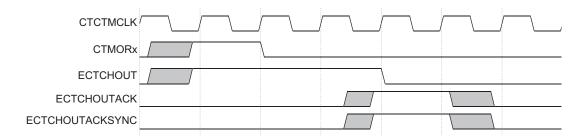

Figure 2-26 on page 2-33 shows the timing diagram for the **ECTCHOUT** handshake circuit when the frequency of the cross-trigger interface connected is slower than the cross-trigger matrix.

Figure 2-26 ECTCHOUT handshake timing ECTCHOUT held

The acknowledgement signal **ECTCHOUTACK** is received a number of clock cycles after **CTMORx** is propagated. **ECTCHOUT** is held through the feedback circuit gates B and C. The **ECTCISBYPASS** is HIGH and **ECTCIHSBYPASS** is LOW in this case. If **ECTCISBYPASS** is LOW the **ECTCHOUT** is held until **ECTCHOUTACKSYNC** is active on the Not input of gate B.

If **ECTCIHSBYPASS** is HIGH then the handshaking logic is disabled and the OR gate A effectively becomes the only active gate in the circuit, so **ECTCHOUT** is the same as **CTMORx**.

#### 2.3.4 Channel interface connections

Figure 2-27 on page 2-34 shows two CTMs connected together. A CTI connected to the CTM uses the same circuitry but with different port names. If the block connected to the CTM is operating at the same frequency then the bypass circuitry can be enabled.

Figure 2-27 Channel handshake interface connections

The ECTCISBYPASS ports are effectively one port for the CI. In Figure 2-27 ECTCISBYPASS0 and ECTCISBYPASS1 are connected to the same signal. The CI is either synchronous or asynchronous. Therefore, the same synchronization bypass can be used on both sides of the interface. There is one ECTCIHSBYPASS signal for each bit of the ECTCHOUT bus. As long as both CTMs are running in the same clock domain and there is no requirement for an acknowledgement signal, the handshaking can be bypassed on a bit-by-bit basis.

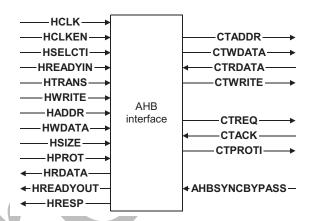

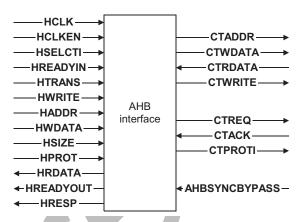

#### 2.4 AHB interface

The AHB interface is a standard AHB slave. Figure 2-28 shows the main inputs and outputs of the AHB interface.

Figure 2-28 AHB interface signals

When **ASYNCHBYPASS** is LOW, synchronization circuits are inserted to cope with **HCLK** and **ECTCTICLK** being asynchronous.

# 2.5 CTI register access

The CTI is accessed as a memory-mapped device.

ARM recommend that each core is responsible for the configuration of the CTI registers relevant to it. Working like this, the software running on each core, or the debugger attached to each core, can control directly cross-triggering events pertinent to that core.

#### 2.5.1 Access issues

Because you can use the ECT to generate intrusive debug events, it is important to ensure that these macrocells are only used during product development, and that their use (either inadvertently or maliciously) in a production system is prevented.

The following access mechanisms are implemented for protecting the CTI from unwanted configuration:

#### Debug enable

The DBGEN input enables a hardware signal to enable/disable the debug mapping in the CTI module. For example, this pin can be activated during development but tied LOW in production systems to eliminate the chance of the ECT generating debug activates in a finalized product. This signal can change during operation (though this is not recommended for ARM based processors) to prevent a CPU from generating/receiving debug triggers in certain situations, for example performing critical operations.

#### Access key, CTILOCK Register

This requires a suitable key to be presented to the CTI before it is enabled or configured.

#### Privileged access, CTIPROTECTION Register

This restricts access to the configuration registers so that only privileged (supervisor mode) code can access them. In Protection mode user access is effectively masked, so any reads from the ECT returns zeros. The ECT does not respond with an ERROR on the HRESP. This ensures that user code does not require an extra trap handler for DABORTS that occur if an ERROR condition is signalled.

# 2.6 ECT registers

The ECT registers control the behavior of the CTI attached to a specific core. The following features are implemented:

- the CTI is an AHB slave and all the registers (4kB) can be accessed through this interface

- the ECTDBGEN input disables the CTI mapping logic

- the access to registers is locked using a single register

- the registers can optionally be protected where they can only be accessed in supervisor mode

- the ECT has two CTIs.

The ECT registers are located in the two CTIs. Each CTI has its own AHB interface and it is recommended that each core is responsible for the configuration of the CTI registers relevant to it. Figure 2-29 shows the structure of the CTI.

Figure 2-29 CTI structure

The handshaking blocks are described in *ECTTRIGIN handshake* on page 2-17 and *ECTTRIGOUT handshake* on page 2-18. The registers within each CTI are exactly the same.

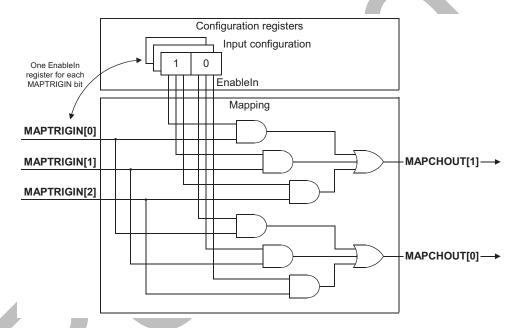

The configuration registers control the driving of source signals onto and out of the channels to the CTM. Chapter 3 *Programmer's Model* describes the register specification. The bus **MAPTRIGIN**[7:0] is the output of the **ECTTRIGIN** handshaking block as shown in Figure 2-29 on page 2-37.

Figure 2-30 shows an example of ECT In Mapping block registers where part of the **MAPTRIGIN**[7:0] bus bits [2:0] are mapped onto channels 0 and 1 (**MAPCHOUT**[3:0]). In this case, the EnableIn bus comes from the CTIINEN registers, one for each **MAPTRIGIN** bit (8 in total). Each bit of the register masks the input signal for the corresponding channel.

Figure 2-30 Registers controlling the events from the core

You might want to ensure that only one input signal is mapped to a channel (ECTCHOUT[x]), and that only one channel (ECTCHIN[x]) drives an output trigger. This is fully supported by the ECT. However there is no mechanism to determine which signal raised the event if more than one input signal is enabled onto an output trigger.

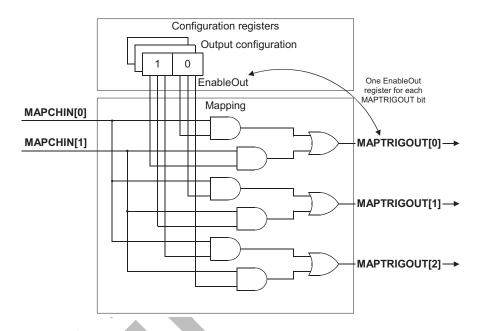

Figure 2-31 on page 2-39 shows an example of ECT Out Mapping block.

Note

Figure 2-31 Registers controlling the events to the core

Figure 2-31 shows the enable output registers where two bits of the **MAPCHIN**[3:0] bus are mapped onto three bits of the **MAPTRIGOUT**[7:0] bus. There are eight Output Configuration registers, CTIOUTEN0-7, one for each trigger. The registers have enable bits for each of the four channels.

# 2.6.1 Application trigger

The CTI enables the application to raise an event on one of the channels. Do this by writing a 1 to the CTIAPPSET register. To clear the application trigger you have to write a 1 to the corresponding bit in the CTIAPPCLEAR. This set and clear mechanism enables you to modify the application triggers without requiring a read/modify/write sequence in the code. Each register has one bit corresponding to each of the four channels.

You can also generate application triggers by writing a 1 to the CTIAPPPULSE register. The signal generated is only one cycle and you do not have to clear it by writing to another register. However, you can extend the width of the pulse to multi-cycle through the handshaking circuits.

Figure 2-32 on page 2-40 shows an example of the circuit used to implement the application trigger.

Figure 2-32 Application-driven trigger

This enables the application to raise a special event.

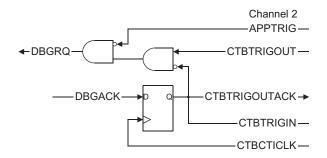

# 2.6.2 Possible system deadlock situation to avoid

You must consider carefully the use of the channels so that a possible system deadlock cannot occur. See Figure 2-33.

Figure 2-33 System deadlock

Figure 2-33 on page 2-40 shows the ECT mapping logic set up as follows:

- 1. A **DBGACK** from one core generates a **DBGRQ** on the other core.

- 2. **DBGRQ0** is generated by an **APPTRIG** signal.

- 3. Core0 responds with a **DBGACK0** signal when the core is in debug mode. This is propagated to **DBGRQ1** by the ECT Channel1.

- 4. Core1 responds with a **DBGACK1** that in turn is then propagated to Core0 through Channel0, so generating another **DBGRQ0** that starts the whole process again.

The deadlock situation occurs as both cores trigger the other back into debug mode as soon as it enters execution mode (**DBGACK** going LOW). You must avoid this situation in one of the following ways:

- Set up the system so that only one core can trigger the DBGRQ on the other core/s.

- Disable the mapping logic in Debug mode and then re-enable when all cores are out of debug.

- Include conditioning logic in the wrapper so that the **DBGRQ** signal is dependent on another channel as shown in Figure 2-34. An application trigger in the debug routine generates Channel2. The debug routine determines that all the cores mapped to the **DBGRQ** are out of debug (**DBGACK**s are LOW) before allowing the **DBGRQ** signal to be generated to the core.

Figure 2-34 Wrapper to condition DBGRQ signal

# Chapter 3 **Programmer's Model**

This chapter describes the ECT registers and provides information for programming the microcontroller. It contains the following sections:

- About the programmer's model on page 3-2

- Summary of CTI registers on page 3-3

- Register descriptions on page 3-5.

# 3.1 About the programmer's model

The base addresses of the CTIs are not fixed, and can be different for any particular system implementation. However, the offset of any particular register from the base address is fixed.

The following locations are reserved for future possible expansion and must not be used during normal operation:

- 0x040-0x09C

- 0x0C0-0x12C.

The following applies to all registers:

- reserved or unused bits of registers must be written as 0, and ignored on a read unless otherwise stated in the text

- all register bits are reset to 0 unless otherwise stated in the text

- all registers must be accessed as words and so are compatible with big and little endian systems.

# 3.2 Summary of CTI registers

Table 3-1 shows the CTI registers.

Table 3-1 CTI register summary

| Address offset | Register         | Туре           | Width | Reset<br>value | Description                                                             |

|----------------|------------------|----------------|-------|----------------|-------------------------------------------------------------------------|

| 0x000          | CTICONTROL       | Read/<br>write | 1     | 0x0            | See CTI Control Register, CTICONTROL on page 3-5                        |

| 0x004          | CTISTATUS        | Read           | 2     | 0x1 or 0x3     | See CTI Status Register, CTISTATUS on page 3-5                          |

| 0×008          | CTILOCK          | Write          | 32    | 0x00000000     | See CTI Lock Enable Register, CTILOCK on page 3-6                       |

| 0x00C          | CTIPROTECTION    | Read           | 1     | 0x0            | See CTI Protection Enable Register,<br>CTIPROTECTION on page 3-6        |

| 0×010          | CTIINTACK        | Write          | 8     | -              | See CTI Interrupt Acknowledge Register,<br>CTIINTACK on page 3-7        |

| 0x014          | CTIAPPSET        | Read/<br>write | 4     | 0x0            | See CTI Application Trigger Set Register,<br>CTIAPPSET on page 3-7      |

| 0x018          | CTIAPPCLEAR      | Read/<br>write | 4     | 0x0            | See CTI Application Trigger Clear Register,<br>CTIAPPCLEAR on page 3-8  |

| 0x01C          | CTIAPPPULSE      | Write          | 4     | 0x0            | See CTI Application Pulse Register,<br>CTIAPPPULSE on page 3-8          |

| 0x020-0x03C    | CTIINEN          | Read/<br>write | 4     | 0x00           | See CTI Trigger to Channel Enable<br>Registers, CTIINEN0-7 on page 3-9  |

| 0x0A0-0x0BC    | CTIOUTEN         | Read/<br>write | 4     | 0x00           | See CTI Channel to Trigger Enable<br>Registers, CTIOUTEN0-7 on page 3-9 |

| 0x130          | CTITRIGINSTATUS  | Read           | 8     | -              | See CTI Trigger In Status Register,<br>CTITRIGINSTATUS on page 3-10     |

| 0x134          | CTITRIGOUTSTATUS | Read           | 8     | 0x00           | See CTI Trigger Out Status Register,<br>CTITRIGOUTSTATUS on page 3-10   |

| 0x138          | CTICHINSTATUS    | Read           | 4     | -              | See CTI Channel In Status Register,<br>CTICHINSTATUS on page 3-11       |

| 0x13C          | CTICHOUTSTATUS   | Read           | 4     | 0x0            | See CTI Channel Out Status Register,<br>CTICHOUTSTATUS on page 3-11     |

Table 3-1 CTI register summary (continued)

| Address<br>offset | Register     | Туре | Width | Reset<br>value | Description                            |

|-------------------|--------------|------|-------|----------------|----------------------------------------|

| 0xFE0             | CTIPERIPHID0 | Read | 8     | 0×00           | See CTIPERIPHID0 Register on page 3-13 |

| 0xFE4             | CTIPERIPHID1 | Read | 8     | 0x19           | See CTIPERIPHID1 Register on page 3-13 |

| 0xFE8             | CTIPERIPHID2 | Read | 8     | 0x04           | See CTIPERIPHID2 Register on page 3-14 |

| 0xFEC             | CTIPERIPHID3 | Read | 8     | 0×00           | See CTIPERIPHID3 Register on page 3-14 |

| 0xFF0             | CTIPCELLID0  | Read | 8     | 0x0D           | See CTIPCELLID0 Register on page 3-15  |

| 0xFF4             | CTIPCELLID1  | Read | 8     | 0xF0           | See CTIPCELLID1 Register on page 3-15  |

| 0xFF8             | CTIPCELLID2  | Read | 8     | 0x05           | See CTIPCELLID2 Register on page 3-16  |

| 0xFFC             | CTIPCELLID3  | Read | 8     | 0xB1           | See CTIPCELLID3 Register on page 3-16  |

# 3.3 Register descriptions

This section describes the ECT CTI registers.

All register wait states are a minimum of three cycles for reads and four cycles for writes if **HCLK** and **ECTCTICLK** are the same. Otherwise wait states depend on the ratio between the two clocks.

# 3.3.1 CTI Control Register, CTICONTROL

CTICONTROL is a read/write register. This register enables the CTI.

Table 3-2 shows the bit assignments for the CTI Control Register.

Table 3-2 CTI Control Register bit assignments

| Bits   | Name     | Description                                                                                                                                                    |

|--------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:1] | Reserved | Reserved. read as zero, do not modify.                                                                                                                         |

| [0]    | GLBEN    | Enables or disables the ECT: 0 = disabled (reset) 1 = enabled. When disabled, all cross triggering mapping logic functionality is disabled for this processor. |

# 3.3.2 CTI Status Register, CTISTATUS

CTISTATUS is a read-only register. This register provides the locked and **ECTDBGEN** status of the CTI.

Table 3-3 shows the bit assignments for the CTI Status Register.

**Table 3-3 CTI Status Register bit assignments**

| Bits   | Name     | Description                                                                                                                                                                                                                                                                                                                                                                       |

|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|