# L210 Cache Controller

**Revision r0p5**

**Technical Reference Manual**

Copyright © 2003-2006 ARM Limited. All rights reserved. ARM DDI 0284G

### L210 Cache Controller Technical Reference Manual

Copyright © 2003-2006 ARM Limited. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

**Change History**

| Date              | Issue | Confidentiality      | Change                                                                                                                                |

|-------------------|-------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| May 2003          | А     | Limited Confidential | For Limited release                                                                                                                   |

| June 2003         | В     | NonConfidential      | Final, r0p1, latency signals added, Appendix E added                                                                                  |

| October 2003      | С     | NonConfidential      | R0p2. Product name corrected, Configurability of master and slave ports clarified,                                                    |

|                   |       |                      | Figure 4-5, L210 Miss, redrawn,                                                                                                       |

|                   |       |                      | Section 5.2 rewritten, LRB1 replaces LRB 0 as MBIST, HMASTERMx signal descriptions corrected,                                         |

|                   |       |                      | Appendix E extended to cover ARM 7 cores and ARM 9 cores                                                                              |

|                   |       |                      | Glossary updated, extended and corrected.                                                                                             |

| 23 April 2004     | D     | NonConfidential      | R0p3 updates. Minor modifications to register map and cache maintenance tables.                                                       |

|                   |       |                      | Additional comments to Cache Sync maintenance operation. Preventing or reducing cache<br>pollution section rewritten.                 |

|                   |       |                      | Sections on L210 Clocking, Idle, disabled states moved to chapter 4.                                                                  |

|                   |       |                      | Comments added to section 4.6.1 concerning additional piece of hardware provided.                                                     |

|                   |       |                      | Additional comments to unaligned burst accesses and known length bursts in section 4.6.2. Default value for <b>HMASTERM0</b> removed. |

|                   |       |                      | Additional comments for HMASTERM1, HMASTERM2, HPROTMx, HSIDEBANDx signals.                                                            |

|                   |       |                      | Additional appendix section D3 Mapping of slave to master port bursts.                                                                |

|                   |       |                      | Section E.2.1 program listing corrected.                                                                                              |

|                   |       |                      | Section E.2.2 only relevant to ARM926 revisions r0p0-r0p4, fixed from r0p5                                                            |

| 27 May 2005       | Е     | NonConfidential      | R0p4 updates.                                                                                                                         |

|                   |       |                      | Section 1.5 corrected.                                                                                                                |

|                   |       |                      | Section 2.2 Introductory text to Table 2-1 clarified. Table 2-4 added.                                                                |

|                   |       |                      | Section 2.3.5 Description of background operations clarified.                                                                         |

| 19 September 2005 | F     | NonConfidential      | R0p5 updates. Table 2-4 updated. Section 4.1.4 Cache Sync rewritten.                                                                  |

| 20 September 2006 | G     | NonConfidential      | Event Monitor text clarified.                                                                                                         |

|                   |       |                      | Product renamed to become ARM PrimeCell L210 Level 2 Cache Controller.                                                                |

|                   |       |                      | Section 3.2 removed.                                                                                                                  |

|                   |       |                      | Table C-5 on page C-7 rewritten for clarity.                                                                                          |

|                   |       |                      | Appendix E replaced by Applications Note Using the L210 Cache Controller with ARM7 an ARM9 cores (ARM DAI 0169A)                      |

|                   |       |                      | Table A-10 on page A-13 footnote reworded.                                                                                            |

#### **Proprietary Notice**

Words and logos marked with  $^{\otimes}$  or  $^{\sim}$  are registered trademarks or trademarks of ARM Limited in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate"

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

## Contents L210 Cache Controller Technical Reference Manual

|           | Prefa                           | ace                                                                                                                        |                                    |

|-----------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------|

|           |                                 | About this manual                                                                                                          | xii                                |

|           |                                 | Feedback                                                                                                                   | xvii                               |

| Chapter 1 | Intro                           | oduction                                                                                                                   |                                    |

| -         | 1.1                             | About the Cache Controller                                                                                                 | 1-2                                |

|           | 1.2                             | Cache controller block diagram                                                                                             | 1-3                                |

|           | 1.3                             | Functional description                                                                                                     |                                    |

|           | 1.4                             | Supported ARM architectures                                                                                                | 1-10                               |

|           | 1.5                             | L210 Cache Controller product revisions                                                                                    | 1-11                               |

| Chapter 2 | Prog                            | grammer's Model                                                                                                            |                                    |

| -         | 2.1                             | ARM register fields                                                                                                        | 2-2                                |

|           |                                 |                                                                                                                            |                                    |

|           | 2.2                             |                                                                                                                            |                                    |

|           |                                 | About the cache controller registers<br>Register summary                                                                   | 2-3                                |

|           | 2.2                             | About the cache controller registers<br>Register summary                                                                   | 2-3<br>2-4                         |

|           | 2.2<br>2.3                      | About the cache controller registers                                                                                       |                                    |

|           | 2.2<br>2.3<br>2.4               | About the cache controller registers<br>Register summary<br>Replacement strategy                                           |                                    |

|           | 2.2<br>2.3<br>2.4<br>2.5        | About the cache controller registers<br>Register summary<br>Replacement strategy<br>Register 15: Test and Debug            | 2-3<br>2-4<br>2-19<br>2-20<br>2-23 |

|           | 2.2<br>2.3<br>2.4<br>2.5<br>2.6 | About the cache controller registers<br>Register summary<br>Replacement strategy<br>Register 15: Test and Debug<br>Buffers |                                    |

|            | 2.9    | External abort support for L3 memory                | 2-28 |

|------------|--------|-----------------------------------------------------|------|

| Chapter 3  | RAM    | Interfaces                                          |      |

| -          | 3.1    | About RAM interfaces                                |      |

|            | 3.2    | RAM configuration versus associativity and way size |      |

|            | 3.3    | Data RAM                                            |      |

|            | 3.4    | Tag RAM                                             |      |

|            | 3.5    | Dirty RAM                                           | 3-11 |

| Chapter 4  | Using  | g the Cache Controller                              |      |

| -          | 4.1    | Configuring the cache controller                    | 4-2  |

|            | 4.2    | Clocking                                            |      |

|            | 4.3    | ldle                                                |      |

|            | 4.4    | Disabled                                            |      |

|            | 4.5    | Set-up sequence                                     |      |

|            | 4.6    | Behavior for ARMv5 memory systems                   |      |

|            | 4.7    | Behavior for ARMv6 memory systems                   |      |

|            | 4.8    | Timing diagrams                                     |      |

| Chapter 5  | Desid  | an for Test                                         |      |

| •          | 5.1    | About design for test                               | 5-2  |

|            | 5.2    | Memory built-in self-test, MBIST                    |      |

| Chapter 6  | Parity | y and RAM Error Support                             |      |

| -          | 6.1    | Parity and RAM error support                        | 6-2  |

|            | 6.2    | Error signaling and handling                        |      |

| Appendix A | Signa  | al Descriptions                                     |      |

|            | A.1    | Cache controller signals                            | A-2  |

| Appendix B | AC P   | arameters                                           |      |

|            | B.1    | Cache controller interface signal timing parameters | B-2  |

| Appendix C | Even   | t Monitor                                           |      |

|            | C.1    | Cache controller event monitor                      | C-2  |

|            | C.2    | Programmer's model                                  | C-4  |

|            | C.3    | Implementation details                              | C-9  |

|            | C.4    | Event monitor signals                               | C-12 |

| Appendix D | Maste  | er and Slave Port Configurations                    |      |

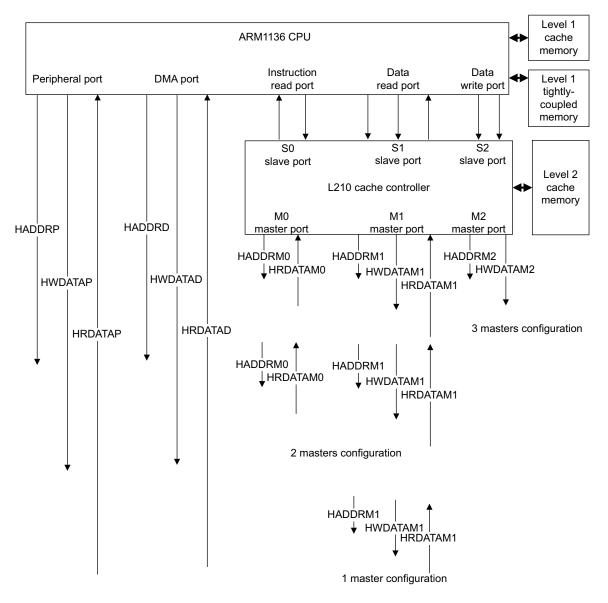

|            | D.1    | ARM1136 memory system configurations                |      |

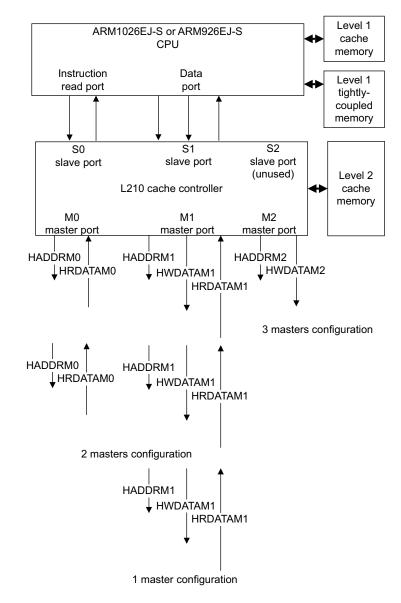

|            | D.2    | ARM926EJ-S and ARM1026EJ-S memory systems           |      |

|            | D.3    | Mapping of slave to master port bursts              | D-6  |

## Glossary

## List of Tables L210 Cache Controller Technical Reference Manual

|            | Change History                                              | ii   |

|------------|-------------------------------------------------------------|------|

| Table 1-1  | Typical memory sizes and access times                       |      |

| Table 1-2  | Transactions for a three-master port system                 |      |

| Table 1-3  | Transactions for a two-master port system                   | 1-9  |

| Table 1-4  | Transactions for a single-master port system                | 1-9  |

| Table 2-1  | Summary register map                                        | 2-3  |

| Table 2-2  | Register map                                                | 2-4  |

| Table 2-3  | ID Register encoding                                        | 2-7  |

| Table 2-4  | Release number index values and releases                    | 2-7  |

| Table 2-5  | Cache Type Register                                         | 2-8  |

| Table 2-6  | Control Register                                            | 2-9  |

| Table 2-7  | Auxiliary Control Register                                  | 2-10 |

| Table 2-8  | Cache maintenance operations                                | 2-12 |

| Table 2-9  | Writing or reading register to way bits                     | 2-15 |

| Table 2-10 | Line Tag Register mapping                                   | 2-21 |

| Table 2-11 | Debug Control Register                                      | 2-21 |

| Table 3-1  | Cache associativity and bits[15:13] of data RAM bus address | 3-3  |

| Table 3-2  | Way size and bits[12:0] of data RAM bus address             | 3-4  |

| Table 3-3  | Tag RAM and way size                                        | 3-4  |

| Table 3-4  | Way size and TAGADDR values                                 | 3-5  |

| Table 3-5  | Associativity and DIRTYRD and DIRTYWD values                | 3-6  |

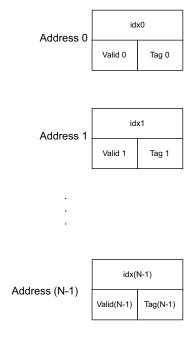

| Values for N in RAM size diagrams                       | 3-7                                                     |

|---------------------------------------------------------|---------------------------------------------------------|

| Total cache size compared to way size and associativity | 4-2                                                     |

| Asynchronous mode control pins                          |                                                         |

| HPROTSx[4:2] and TLB correspondences in an ARMv5 system | 4-11                                                    |

| Behavior for ARMv5 transactions                         |                                                         |

| HPROTSx[4-2] and TLB correspondences in ARMv6           | 4-14                                                    |

| Behavior with ARMv6 memory types                        |                                                         |

| Example uses of HBSTRBSx and HUNALIGNSx, little-endian  |                                                         |

|                                                         |                                                         |

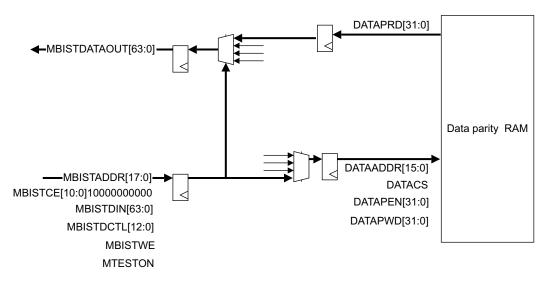

| MBISTADDR and MBISTDIN mappings for data RAM            | 5-6                                                     |

| MBISTADDR and MBISTDIN mappings for data parity RAM     | 5-7                                                     |

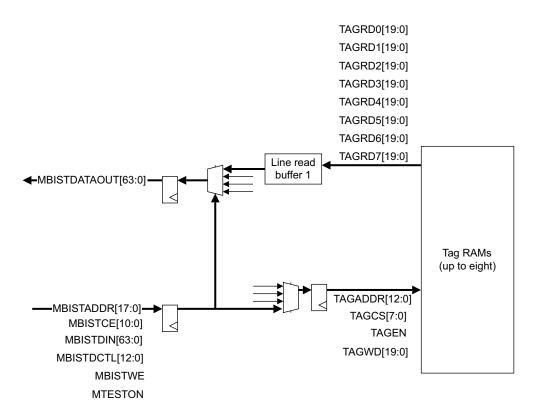

| MBISTADDR and MBISTDIN mapping for Tag RAMs             | 5-9                                                     |

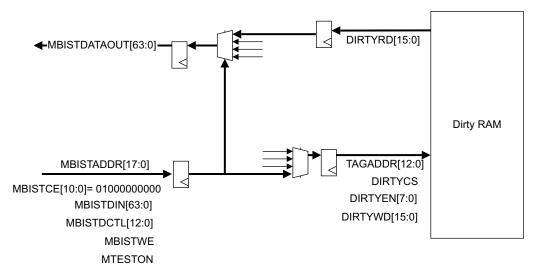

| MBISTADDR and MBISTIDIN mappings for dirty RAM          | 5-10                                                    |

| Slave port 0 signals                                    | A-2                                                     |

| Master port 0 signals                                   | A-3                                                     |

| Slave port 1 signals                                    | A-5                                                     |

| Master port 1 signals                                   | A-6                                                     |

| Slave port 2 signals                                    | A-8                                                     |

| Master port 2 signals                                   | A-9                                                     |

| Data RAM interface signals                              | A-11                                                    |

| Tag RAM interface signals                               |                                                         |

|                                                         |                                                         |

| Cache controller event bus output signals               | A-13                                                    |

| Cache controller MBIST block inputs and outputs         | A-15                                                    |

| Miscellaneous signals                                   | A-16                                                    |

| Event monitor registers                                 | C-4                                                     |

| EMMC bit fields descriptions                            | C-5                                                     |

| Counter Status Register                                 |                                                         |

|                                                         |                                                         |

| Event sources encodings                                 | C-7                                                     |

| AHB-Lite slave port interface signals                   | C-11                                                    |

| Event monitor input signals                             | C-12                                                    |

| WRAPn read access conversions on slave ports            | D-6                                                     |

|                                                         | Total cache size compared to way size and associativity |

## List of Figures L210 Cache Controller Technical Reference Manual

|             | Key to timing diagram conventions    | xiv  |

|-------------|--------------------------------------|------|

| Figure 1-1  | Cache controller internal data paths | 1-3  |

| Figure 2-1  | ID Register                          | 2-7  |

| Figure 2-2  | Cache Type Register                  | 2-8  |

| Figure 2-3  | Control Register                     | 2-9  |

| Figure 2-4  | Auxiliary Control Register format    | 2-10 |

| Figure 2-5  | Physical address format              | 2-14 |

| Figure 2-6  | Index Way combination format         | 2-14 |

| Figure 2-7  | Lockdown format C                    | 2-15 |

| Figure 2-8  | Test operation format                | 2-20 |

| Figure 2-9  | Word order in cache lines            | 2-20 |

| Figure 2-10 | Line Tag Register format             | 2-20 |

| Figure 3-1  | Data RAM bus address format          | 3-3  |

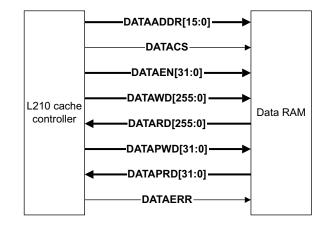

| Figure 3-2  | Data RAM signals                     | 3-7  |

| Figure 3-3  | Data RAM ways                        | 3-8  |

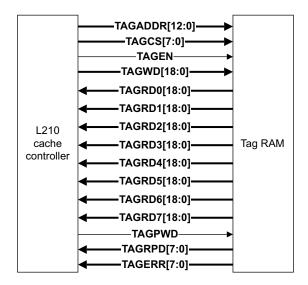

| Figure 3-4  | Tag RAM signals                      | 3-9  |

| Figure 3-5  | Tag RAM organization                 |      |

| Figure 3-6  | Dirty RAM signals                    | 3-11 |

| Figure 3-7  | Dirty RAM memory organization        | 3-12 |

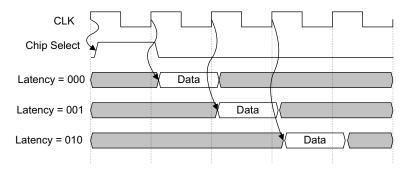

| Figure 4-1  | Compiled RAM latency                 | 4-3  |

| Figure 4-2  | Asynchronous interface, read data    | 4-5  |

| Figure 4-3 | Asynchronous interface, write data                                     | 4-5  |

|------------|------------------------------------------------------------------------|------|

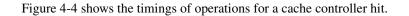

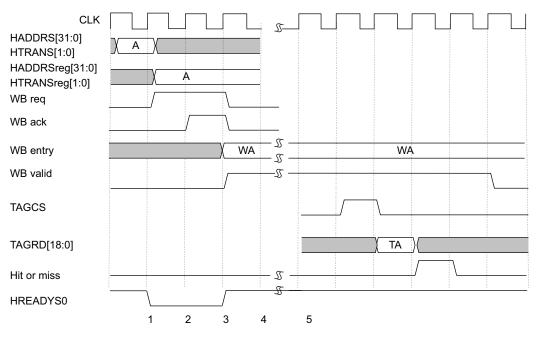

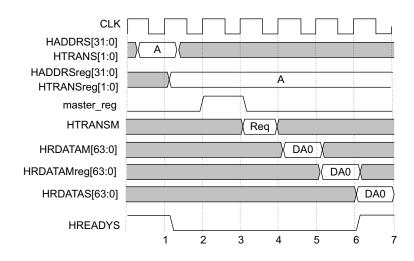

| Figure 4-4 | Hit                                                                    | 4-20 |

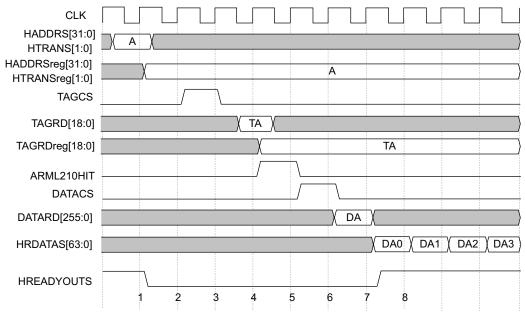

| Figure 4-5 | Miss                                                                   |      |

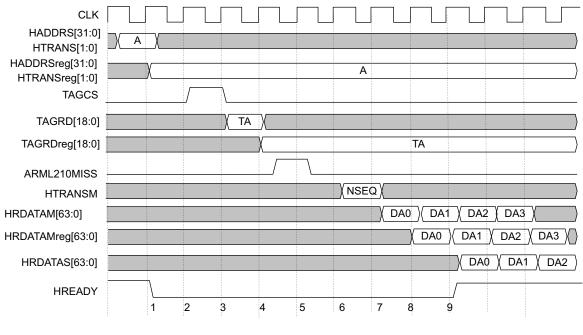

| Figure 4-6 | Simultaneous hits                                                      | 4-22 |

| Figure 4-7 | Buffered write timings                                                 | 4-23 |

| Figure 4-8 | Outer noncacheable access                                              | 4-24 |

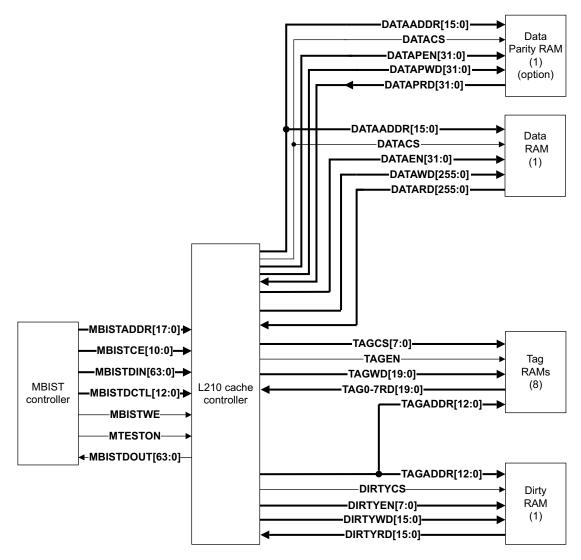

| Figure 5-1 | MBIST configuration                                                    | 5-4  |

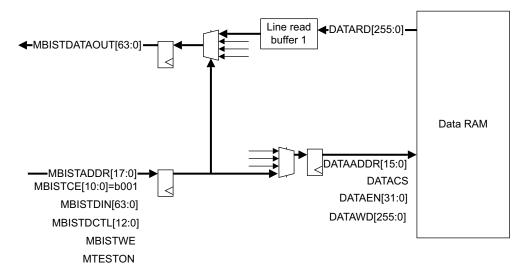

| Figure 5-2 | MBIST Data RAM test paths                                              | 5-7  |

| Figure 5-3 | Data parity RAM for test                                               |      |

| Figure 5-4 | MBIST paths for tag RAM testing                                        | 5-10 |

| Figure 5-5 | Dirty RAM testing paths using MBIST                                    | 5-11 |

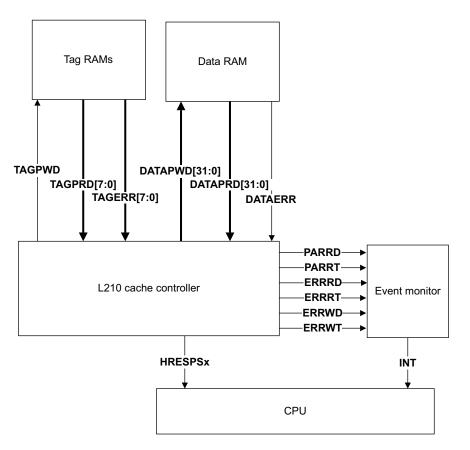

| Figure 6-1 | Parity and RAM error support                                           | 6-3  |

| Figure B-1 | Target timing parameters for unregistered signals                      | B-3  |

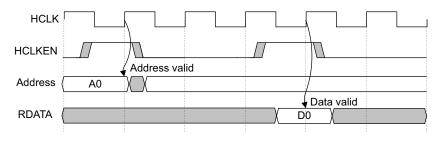

| Figure C-1 | HCLKEN usage for a read                                                |      |

| Figure D-1 | ARM1136 memory system with cache controller master port configurations | D-2  |

| Figure D-2 | ARM926EJ-S and ARM1026EJ-S memory system with cache                    |      |

|            | controller master port configurations                                  | D-5  |

## Preface

This preface introduces the *ARM PrimeCell L210 Level 2 Cache Controller Technical Reference Manual*. It contains the following sections:

- About this manual on page xii

- *Feedback* on page xvii.

### About this manual

This is the *Technical Reference Manual* (TRM) for the *ARM PrimeCell L210 Level 2 Cache Controller* (L210). For purposes of this manual the cache controller refers to the L210 Cache Controller.

#### **Product revision status**

| where:     |                                                                      |

|------------|----------------------------------------------------------------------|

| r <i>n</i> | Identifies the major revision of the product.                        |

| р <i>п</i> | Identifies the minor revision or modification status of the product. |

#### Intended audience

This manual is written for system designers, system integrators, and verification engineers who are designing a *System-on-Chip* (SoC) device that uses the L210 Cache Controller. The manual describes the external functionality of the cache controller.

#### Using this manual

This manual is organized into the following chapters:

#### **Chapter 1** Introduction

Read this chapter for an introduction to the functionality of the cache controller.

#### Chapter 2 Programmer's Model

Read this chapter for a description of the cache controller registers and for programming details.

#### Chapter 3 RAM Interfaces

Read this chapter for details of the RAM interfaces.

#### Chapter 4 Using the Cache Controller

Read this chapter for details of how to use the cache controller effectively.

#### Chapter 5 Design for Test

Read this chapter for details of the L210 features that help with design for test issues.

#### Chapter 6 Parity and RAM Error Support

Read this chapter for details of the parity and RAM error support.

#### **Appendix A** Signal Descriptions

Read this appendix for a description of the signals used in the cache controller.

#### Appendix B AC Parameters

Read this appendix for a description of the AC timing parameters of the cache controller signals.

#### Appendix C Event Monitor

Read this appendix for a description of the cache controller event monitor block.

#### Appendix D Master and Slave Port Configurations

Read this appendix for a description of the different master and slave port configurations of the cache controller.

#### Conventions

Conventions that this manual can use are described in:

- Typographical

- Timing diagrams on page xiv

- Signals on page xiv

- *Numbering* on page xv.

#### Typographical

The typographical conventions are:

| italic            | Highlights important notes, introduces special terminology, denotes internal cross-references, and citations.                           |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| bold              | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.   |

| monospace         | Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.                             |

| <u>mono</u> space | Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name. |

| monospace italic | Denotes arguments to monospace text where the argument is to be<br>replaced by a specific value.                                                                          |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| monospace bold   | Denotes language keywords when used outside example code.                                                                                                                 |

| < and >          | Angle brackets enclose replaceable terms for assembler syntax<br>where they appear in code or code fragments. They appear in<br>normal font in running text. For example: |

|                  | • MRC p15, 0 <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd>                                                                                                   |

|                  | • The Opcode_2 value selects which register is accessed.                                                                                                                  |

#### **Timing diagrams**

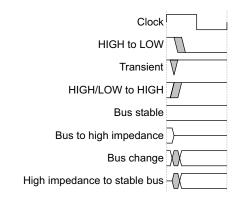

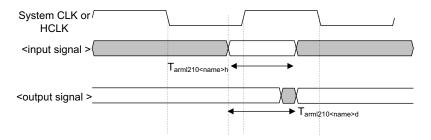

The figure named *Key to timing diagram conventions* explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

#### Key to timing diagram conventions

#### Signals

The signal conventions are:

Signal levelThe level of an asserted signal depends on whether the signal is<br/>active-HIGH or active-LOW. Asserted means HIGH for<br/>active-HIGH signals and LOW for active-LOW signals.Lower-case nDenotes an active-LOW signal.

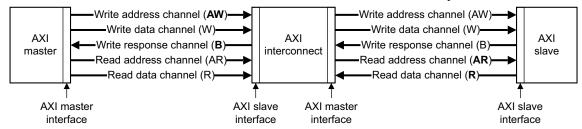

| Prefix A  | Denotes global Advanced eXtensible Interface (AXI) signals: |  |  |

|-----------|-------------------------------------------------------------|--|--|

| Prefix AR | Denotes AXI read address channel signals.                   |  |  |

| Prefix AW | Denotes AXI write address channel signals.                  |  |  |

| Prefix B  | Denotes AXI write response channel signals.                 |  |  |

| Prefix C  | Denotes AXI low-power interface signals.                    |  |  |

| Prefix H  | Denotes Advanced High-performance Bus (AHB) signals.        |  |  |

| Prefix P  | Denotes Advanced Peripheral Bus (APB) signals.              |  |  |

| Prefix R  | Denotes AXI read data channel signals.                      |  |  |

| Prefix W  | Denotes AXI write data channel signals.                     |  |  |

#### Numbering

The numbering convention is:

#### <size in bits>'<base><number>

This is a Verilog method of abbreviating constant numbers. For example:

- 'h7B4 is an unsized hexadecimal value.

- 'o7654 is an unsized octal value.

- 8'd9 is an eight-bit wide decimal value of 9.

- 8'h3F is an eight-bit wide hexadecimal value of 0x3F. This is equivalent to b00111111.

- 8'b1111 is an eight-bit wide binary value of b00001111.

#### **Further reading**

This section lists publications by ARM Limited, and by third parties.

ARM Limited periodically provides updates and corrections to its documentation. See http://www.arm.com for current errata sheets, addenda, and the Frequently Asked Questions list.

#### **ARM** publications

This manual contains information that is specific to the L210. See the following documents for other relevant information:

- ARM L210 Implementation Guide (ARM DII 0069)

- ARM L210 MBIST Controller Technical Reference Manual (ARM DDI 0302)

- *ARM1136J-S<sup>™</sup> Technical Reference Manual* (ARM DDI 0211)

- ARM1026EJ-S Technical Reference Manual (ARM DDI 0244)

- ARM926EJ-S PWP VC Technical Reference Manual (ARM DDI 0232)

- ARM720T Technical Reference Manual (ARM DDI 0229B)

- ARM11 AMBA (Rev 2.0) AHB Extensions (ARM IHI 0023)

- AMBA® Specification (Rev 2.0) (ARM IHI 0011)

- ARM Architecture Reference Manual (ARM DDI 0100).

- Using the L210 Cache Controller with ARM7 and ARM9 cores (ARM DAI 0169)

## Feedback

ARM Limited welcomes feedback on the L210 Cache Controller and its documentation.

#### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier giving:

- the product name

- a concise explanation of your comments.

#### Feedback on this manual

If you have any comments on this manual, send email to errata@arm.com giving:

- the title

- the number

- the relevant page number(s) to which your comments apply

- a concise explanation of your comments.

ARM Limited also welcomes general suggestions for additions and improvements.

Preface

## Chapter 1 Introduction

This chapter describes the cache controller and its features. It contains the following sections:

- *About the Cache Controller* on page 1-2

- Cache controller block diagram on page 1-3

- *Functional description* on page 1-5

- Supported ARM architectures on page 1-10

- *L210 Cache Controller product revisions* on page 1-11.

## 1.1 About the Cache Controller

The addition of an on-chip secondary cache (also referred to as a Level 2 cache, L2CC) is a recognized method of improving the performance of computer systems when significant memory traffic is generated by the *Central Processing Unit* (CPU). By definition a secondary cache assumes the presence of a Level 1 or primary cache, closely coupled or internal to the CPU.

Memory access is fastest to L1 cache, followed closely by the L2 cache controller. Memory access is significantly slower with L3 memory, main memory. Table 1-1 shows typical sizes and access times for different types of memory.

| Memory type                     | Size                  | Access time |

|---------------------------------|-----------------------|-------------|

| Processor registers             | 128 Bytes             | 1 cycle     |

| On-chip L1 cache                | 32KB                  | 1-2 cycles  |

| On-chip L210 Cache Controller   | 128KB                 | 8 cycles    |

| Main memory (L3) dynamic RAM    | MB<br>GB <sup>a</sup> | 16 cycles   |

| Back-up memory (hard disk) (L4) | MB<br>GB              | >500 cycles |

#### Table 1-1 Typical memory sizes and access times

Size limited by the processor core addressing. For example, a 32-bit core without memory management can directly address 4GB of memory.

## 1.2 Cache controller block diagram

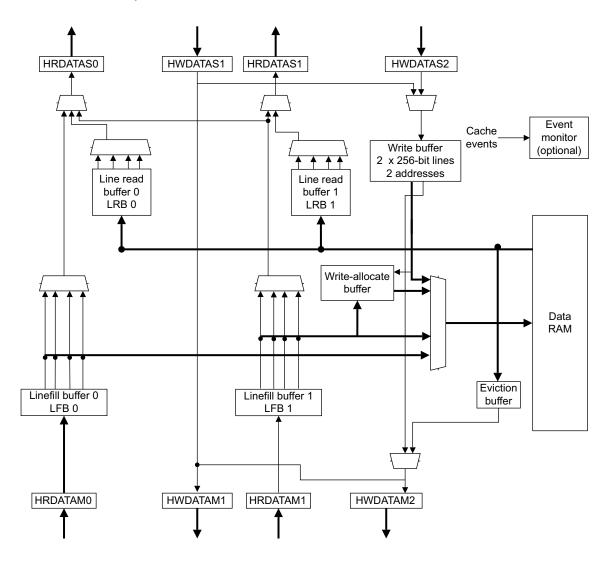

Figure 1-1 shows the internal data paths of the cache controller. It can be used in a system with an ARM1136 core, ARM1026 core, or ARM926EJ-S core.

Figure 1-1 Cache controller internal data paths

To enable flexibility, you can configure the cache controller to use one, two, or three ports. The cache controller ports are:

- 64-bit AHB-Lite slave ports

- One slave, S1

- Two slaves, S0 and S1

- Three slaves, S0, S1, and S2.

The cache controller arbitrates internally among them.

- 64-bit AHB-Lite master ports:

- One master, M1

- Two masters, M0 and M1

- Three masters, M0, M1, and M2.

If you decide not to use S0, you cannot configure M0. S1 always exists in all configurations.

The cache controller master ports are AHB-Lite compatible. ARM Limited can supply an AHB wrapper that converts the AHB-Lite interface to a multi-master AHB interface and that does not introduce any pipeline delays.

#### 1.2.1 Operating frequency

For AHB slaves the clock is **CLK**, the same clock as for internal cache controller logic. For AHB masters the clock is **HCLK**. **CLKEN**s are used as enables for slave ports clocked with **CLK**. **HCLKEN**s are used as enables for master ports clocked with **HCLK**

The CPU AHB ports of the cache controller can operate at the same frequency as the CPU core. This means that the CPU core clock and **CLK** operate in a 1:1 ratio.

#### **AHB** arbitration

All AMBA signals are considered valid on a rising clock edge with **HREADY** high and **HCLKEN** high.

*Timing diagrams* on page 4-20 shows examples of typical cache controller bus transactions.

### 1.3 Functional description

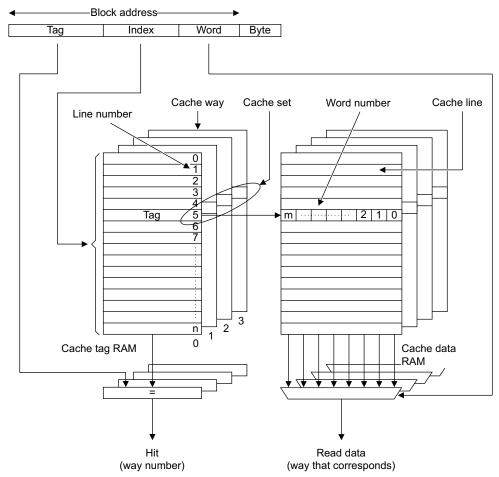

The L210 Cache Controller is an eight-way unified, physically addressed (indexed), physically tagged cache. The cache controller does not maintain coherency among caches. The cache controller can be locked on a way basis.

The following sections describe the cache controller:

- Features

- *Buffers* on page 1-6

- Error support and MBIST support on page 1-6

- Event bus on page 1-7

- *Configuring the cache controller* on page 1-7.

#### 1.3.1 Features

The features are:

- Size can be 16KB-2MB.

- Fixed line length of 32 bytes, eight words.

- 300 MHz worst case with 0.18 micron technology operating frequency range.

- Physically addressed and physically tagged.

- Lockdown format C supported, with separate way locking mechanisms for data and instructions.

- Eight-way associativity which can be direct mapped, depending on the use of lockdown registers.

- Data RAM is byte-writable.

- Support for these cache modes:

- Write-Through, read allocate

- Write-Back, read allocate

- Write-Back, read and write allocate, for systems using ARMv6 extensions only.

- Write allocate override option to always have allocation on write misses in the cache controller.

- Performs critical word first refilling, with the option of refilling starting with word 0. The same option is used to transform nonbufferable wrap write bursts and noncacheable wrap read bursts into linear accesses.

- Pseudo-random victim selection policy, can be made deterministic with use of lockdown registers.

- You can statically configure the following options:

- Single master port, master port 1

- Two master ports, master port 0 and master port 1

- Three master ports, master port 0, master port 1, and master port 2

- Static option to select synchronous or asynchronous master port interfaces

- Parity generation and error detection synthesis option.

#### 1.3.2 Buffers

The cache controller has the following buffers:

#### Two linefill buffers, LFB

These buffers capture linefill data from main memory, waiting for a complete line before writing to L2 memory. This makes the cache controller non-blocking for requests from the other slave ports

#### Two line read buffers, LRB

These buffers hold a line from the cache controller, for subsequent requests that hit on the line.

#### One eviction buffer, EB

This holds an evicted line from the cache controller, to be written back to main memory.

#### One write buffer, WB

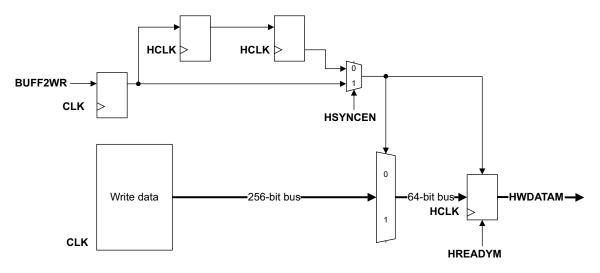

This holds buffered writes before their draining to main memory, as well as to the cache controller. The write buffer is made of two slots, each with a 256-bit data line and one address per slot. It enables multiple writes to the same line to be merged.

#### One write-allocate buffer, WA

If the write buffer line is not full, this buffer merges data from the write buffer and missing data, from master port 1 before requesting an allocation to the cache.

#### 1.3.3 Error support and MBIST support

Support is provided for:

- MBIST testing. See Chapter 5 Design for Test.

- Optional parity and RAM error detection. See Chapter 6 *Parity and RAM Error Support*.

#### 1.3.4 Event bus

The cache controller has an event bus. The event bus enables licensees to report specific events occurring in the cache controller. It can be used in conjunction with an event monitor so that performance statistics can be extracted. See Appendix C *Event Monitor* for details.

#### 1.3.5 Configuring the cache controller

The cache controller is configured using memory-mapped registers. See Chapter 2 *Programmer's Model* for details.

The cache controller is highly configurable. You do not have to resynthesize the module to reconfigure the cache controller for other applications. This means that you only have to harden the cache controller macrocell once, regardless of the number of cache controller configurations you use. You can use synthesis options to remove S0,S2, M0, and M2. If S0 is not implemented, then M0 must also be removed. S0,S2, M0, and M2, if present, can be disabled using the **MASTNUM** and **SLAVENUM** pins. This means that you can harden a cache controller with all ports and disable unused ones in a specific SoC. S1 always exists in all configurations.

#### Port configurations

This section describes the different configurations of slave ports and master ports:

- Slave ports

- *Master ports* on page 1-8.

#### Slave ports

There are three requesting ports to the cache controller, the AHB slave ports:

S0 AHB Slave port 0 Only services reads.

#### S1 AHB Slave port 1

Services both reads and writes, and services swaps. It is the only port that can read the internal cache controller registers. All configurations must support this port

#### S2 AHB Slave port 2 Only services writes.

#### All slave ports support exclusive accesses and locked accesses. For more

information see *Locked accesses* on page 4-19 and *Exclusive accesses* on page 4-19.

The cache controller can work with three, two, S0 and S1, or one, S1 only, slave ports. You choose the number of slave ports by forcing the correct value on the **SLAVENUM[1:0]** input pins. Clocks of unused slaves are inactive in functional mode (static high-level clock gating).

#### Master ports

Table 1-2, Table 1-3 on page 1-9, and Table 1-4 on page 1-9 show which transactions each master port is used for in the three possible master port configurations.

The cache controller can work with three, two, M0 and M1, or one, M1 only, master ports. You choose the number of slave ports by forcing the correct value on the **MASTNUM[1:0]** input pins. Clocks of unused slaves are inactive in functional mode (static high-level clock gating).

Table 1-2 shows the transactions on the three master ports in a three-master system. For certain types of transactions the default values for **HMASTERM1** and **HMASTERM2** are configurable in the cache controller RTL, see Appendix A *Signal Descriptions*.

\_\_\_\_\_Note \_\_\_\_\_

In Appendix A *Signal Descriptions*, the default values for **HMASTERM1** and **HMASTERM2** on certain types of transactions are configured as 0xF.

| Master port 0                    | Master port 1                                   | Master port 2                        |

|----------------------------------|-------------------------------------------------|--------------------------------------|

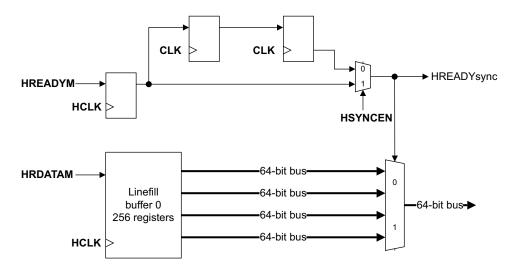

| Linefills with linefill buffer 0 | Linefills with linefill buffer 1                | Buffered stores with eviction buffer |

| Noncached reads                  | Noncached reads                                 | Buffered stores with write buffer    |

| -                                | Swaps, noncached reads and nonbufferable writes | Nonbuffered stores                   |

#### Table 1-2 Transactions for a three-master port system

Table 1-3 shows the transactions on the two master ports in a two-master system.

| Master port 1                                   |  |  |

|-------------------------------------------------|--|--|

| Linefills with linefill buffer 1                |  |  |

| Noncached reads                                 |  |  |

| Swaps, noncached reads and nonbufferable writes |  |  |

| Buffered stores with eviction buffer            |  |  |

| Buffered stores with write buffer               |  |  |

| Nonbuffered stores                              |  |  |

| -                                               |  |  |

#### Table 1-3 Transactions for a two-master port system

Table 1-4 shows the transactions on the single master port, master port 1, in a single-master port system.

#### Table 1-4 Transactions for a single-master port system

| Master port 1                                    |

|--------------------------------------------------|

| Linefills with linefill buffer 1 only            |

| <br>All noncached reads                          |

| Swaps, noncached reads, and nonbufferable writes |

| <br>Buffered stores with eviction buffer         |

| Buffered stores with write buffer                |

| Nonbuffered stores                               |

## 1.4 Supported ARM architectures

The cache controller supports ARM architecture v5 and ARM architecture v6 with ARM1136 AMBA extensions.

ARM processors do not support any form of hardware cache coherency maintenance. All caches have no cache coherency protocol and do no snooping.

## 1.5 L210 Cache Controller product revisions

This is the Technical Reference Manual for L210 Cache Controller silicon revision r0p5. See *Product revision status* on page xii for details of revision numbering.

There are no differences in functionality between the product revisions of the cache controller. See the engineering errata that accompanies the product deliverables for more information.

Introduction

## Chapter 2 Programmer's Model

This chapter describes the cache controller registers and provides information for programming the macrocell. It contains the following sections:

- ARM register fields on page 2-2

- About the cache controller registers on page 2-3

- *Register summary* on page 2-4.

- *Replacement strategy* on page 2-19

- Register 15: Test and Debug on page 2-20

- *Buffers* on page 2-23

- *Ports configuration* on page 2-25

- *Hazards* on page 2-27

- *External abort support for L3 memory* on page 2-28.

## 2.1 ARM register fields

All reserved or unused address locations must not be accessed because this can result in unpredictable behavior of the device.

All reserved or unused bits of registers must be written as zero, and ignored on read unless otherwise stated in the relevant text.

All register bits are reset to logic 0 by a system reset unless otherwise stated in the relevant text.

Unless otherwise stated in the relevant text, all registers support read and write accesses. A write updates the contents of the register and a read returns the contents of the register.

All registers defined in this document can only be accessed using word reads and word writes, unless otherwise stated in the relevant text.

### 2.2 About the cache controller registers

The cache controller is controlled by a set of 32-bit memory-mapped registers that occupy a relocatable 4KB memory space.

The cache controller registers can be written to using slave ports S1 or S2:

- if **HSELRS1** is HIGH and **HSELRS2EN** is LOW, slave port S1 can be written

- if HSELRS2 is HIGH and HSELRS2EN is HIGH, slave port S2 can be written.

If **HSELRS1** is HIGH, S1 can read registers. **HADDRSx[11:2]** is compared to see which register is being accessed.

All registers except some register 15 subregisters accept 32-bits accesses only. The results of 64-bit accesses are Unpredictable.

Register r1, the Auxiliary Control Register, must only be written with a read-modify-write type access when the cache is turned off.

Data line subregisters of register 15 support 64-bit transfer to enable setting or reading registers with LDM or STM instructions.

Reads to an unmapped register return 0. Table 2-1 shows the cache controller registers.

| Register | Reads                        | Writes                       |

|----------|------------------------------|------------------------------|

| 0        | System ID and Cache Type     | Ignored                      |

| 1        | Control                      | Control                      |

| 2-6      | Reserved                     | Reserved                     |

| 7        | Cache maintenance operations | Cache maintenance operations |

| 8        | Reserved                     | Reserved                     |

| 9        | Cache lockdown               | Cache lockdown               |

| 10-14    | Reserved                     | Reserved                     |

| 15       | Test and debug               | Test and debug               |

#### Table 2-1 Summary register map

## 2.3 Register summary

This section describes the following:

- *ID Register* on page 2-7

- Control Register on page 2-9

- Auxiliary Control Register on page 2-9

- *Cache maintenance operations* on page 2-12

- Register 9: Cache Lockdown on page 2-15

- Uses of Lockdown Format C on page 2-16.

Table 2-2 shows the cache controller registers, their base addresses, access types, and functions. The base address of the cache controller is not fixed, but is determined by an AHB decoder on the slave buses and can be different for any particular system implementation. However, the offset of any particular register from the base address is fixed.

| Register | Name              | Base<br>offset | Access<br>type                                | Reset<br>value          | Description                                            |

|----------|-------------------|----------------|-----------------------------------------------|-------------------------|--------------------------------------------------------|

| rO       | Cache ID          | 0x000          | RO                                            | 0x41000040 <sup>a</sup> | See <i>ID Register</i> on page 2-7                     |

| rO       | Cache Type        | 0x004          | RO                                            | 0x1C100100              | See <i>Cache Type</i><br><i>Register</i> on page 2-8   |

| r1       | Control           | 0x100          | -                                             | 0x00000000              | See <i>Control Register</i> on page 2-9                |

| r1       | Auxiliary Control | 0x104          | -                                             | 0x00020FFF              | See Auxiliary<br>Control Register on<br>page 2-9       |

| r7       | Cache Sync        | 0x730          | Always <i>Read</i><br><i>As Zero</i> ,<br>RAZ | 0x00000000              | See Cache<br>maintenance<br>operations on<br>page 2-12 |

| r7       | Invalidate By Way | 0x77C          | -                                             | 0x00000000              | See Cache<br>maintenance<br>operations on<br>page 2-12 |

#### Table 2-2 Register map

### Table 2-2 Register map (continued)

| Register | Name                                                  | Base<br>offset | Access<br>type | Reset<br>value | Description                                                     |

|----------|-------------------------------------------------------|----------------|----------------|----------------|-----------------------------------------------------------------|

| r7       | Invalidate Line By PA                                 | 0x770          | RAZ            | 0x00000000     | See Cache<br>maintenance<br>operations on<br>page 2-12          |

| r7       | Clean Line by Index Way combination                   | 0x7B8          | RAZ            | 0x00000000     | See Cache<br>maintenance<br>operations on<br>page 2-12          |

| r7       | Clean by Way                                          | 0x7BC          | -              | 0x00000000     | See Cache<br>maintenance<br>operations on<br>page 2-12          |

| r7       | Clean Line by PA                                      | 0x7B0          | RAZ            | 0x00000000     | See Cache<br>maintenance<br>operations on<br>page 2-12          |

| r7       | Clean and Invalidate Line by<br>Index Way combination | 0x7F8          | RAZ            | 0x00000000     | See Cache<br>maintenance<br>operations on<br>page 2-12          |

| r7       | Clean and Invalidate by Way                           | 0x7FC          | -              | 0x00000000     | See Cache<br>maintenance<br>operations on<br>page 2-12          |

| r7       | Clean and Invalidate Line by<br>PA                    | 0x7F0          | RAZ            | 0x00000000     | See Cache<br>maintenance<br>operations on<br>page 2-12          |

| r9       | Lockdown by Way – D Side                              | 0x900          | -              | 0x00000000     | See <i>Register 9:</i><br><i>Cache Lockdown</i> on<br>page 2-15 |

| r9       | Lockdown by Way – I Side                              | 0x904          | -              | 0x00000000     | See Register 9:<br>Cache Lockdown on<br>page 2-15               |

#### Table 2-2 Register map (continued)

| Register | Name                             | Base<br>offset | Access<br>type | Reset<br>value | Description                                         |

|----------|----------------------------------|----------------|----------------|----------------|-----------------------------------------------------|

| r15      | Test Operation                   | 0xF00          | RAZ            | 0x00000000     | See Register 15: Test<br>and Debug on<br>page 2-20  |

| r15      | Line Data (8 x Word)             | 0xF10          | -              | 0x00000000     | See Register 15: Test<br>and Debug on<br>page 2-20  |

| r15      | Line Tag {Tag, V, D0, D1,<br>RR} | 0xF30          | -              | 0x00000000     | See Register 15: Test<br>and Debug on<br>page 2-20  |

| r15      | L2 Debug Control Register        | 0xF40          | -              | 0x00000000     | See <i>Register 15: Test and Debug</i> on page 2-20 |

a. This value is pin dependent, depending on how external CACHEDID pins are tied.

Test and debug is implementation-specific, and must not be used by software.

## 2.3.1 ID Register

The read-only ID Register returns a 32-bit device ID code. The device id is specified by the value tied on the **CACHEID**[5:0] input.

You can access the ID Register by reading from the cache controller base address + 0x000. Figure 2-1 shows the format of the ID Register.

| 31      | 24       | 23 |     |      |   |   |   | 16 | 15     | 10 | 9                | 6    | 5 |                            | 0 |

|---------|----------|----|-----|------|---|---|---|----|--------|----|------------------|------|---|----------------------------|---|

| RTL imp | lementor | 0  | 0 0 | ) () | 0 | 0 | 0 | 0  | CACHEI | D  | Pa<br>num<br>inc | nber |   | Release<br>number<br>index |   |

#### Figure 2-1 ID Register

Table 2-3 shows the encoding of the ID Register.

#### Table 2-3 ID Register encoding

| Register bits | Function                          | Values        |

|---------------|-----------------------------------|---------------|

| [31:24]       | RTL implementor                   | 0x41          |

| [23:16]       | Read as zero (RAZ)                | -             |

| [15:10]       | Input pins for layout implementor | -             |

| [9:6]         | Part number index                 | 0x1           |

| [5:0]         | RTL release index                 | See Table 2-4 |

Table 2-4 shows the release number index values

#### Table 2-4 Release number index values and releases

| Release number index | Release |

|----------------------|---------|

| 0x0F                 | r0p5    |

| 0x0B                 | r0p4    |

| 0x03                 | r0p3    |

| 0x02                 | r0p2_01 |

| 0x01                 | r0p1    |

| 0x00                 | r0p2_02 |

## 2.3.2 Cache Type Register

This read-only register returns the 32-bit Cache Type, which makes the cache parameters a product of cache controller cache way size and the cache controller associativity. Figure 2-2 shows the format of the Cache Type Register.

| 31 29        | 9 28 2 | 5 24 | 23          | 12 | 11       |      | 0 |

|--------------|--------|------|-------------|----|----------|------|---|

| SBZ /<br>RAZ | C type | н    | DCache size |    | ICache s | size |   |

#### Figure 2-2 Cache Type Register

Table 2-5 shows the encoding of the Cache Type Register.

#### Table 2-5 Cache Type Register

| Bits    | Field                | Subfield      | Comments                                          |

|---------|----------------------|---------------|---------------------------------------------------|

| [31:29] | Should be Zero (SBZ) | -             | 0b00                                              |

| [28:25] | Cache type           | -             | 0b1110, Lockdown format C                         |

| [24]    | Н                    | -             | 0b0, unified                                      |

| [23:12] | DCache size          | -             | -                                                 |

|         | [23:20] <sup>a</sup> | Way size      | Read from Auxiliary Control Register bits [19:17] |

|         | [19:15] <sup>b</sup> | Associativity | Read from Auxiliary Control Register bits [16:13] |

|         | [14]                 | SBZ           | -                                                 |

|         | [13:12]              | Line length   | 0b00-32 bytes                                     |

| [11:0]  | ICache size          | -             | -                                                 |

|         | [11:8] <sup>c</sup>  | Way size      | Read from Auxiliary Control Register bits [19:17] |

|         | [7:3] <sup>d</sup>   | Associativity | Read from Auxiliary Control Register bits [16:13] |

|         | [2]                  | SBZ           | -                                                 |

|         | [1:0]                | Line length   | b00-32 bytes                                      |

a. The first bit is always 0.

b. The first bit is always 0.

c. The first bit is always 0.

d. The first bit is always 0.

*Sizes and associativity* on page 4-2 gives more information on cache size and associativity.

#### 2.3.3 Control Register

The Control Register, register 1, must be accessed using a read-modify-write sequence. Figure 2-3 shows the format of the Control Register.

| 31 |  |     |  | 1 | 0 |

|----|--|-----|--|---|---|

|    |  | SBZ |  |   |   |

#### **Figure 2-3 Control Register**

Table 2-6 shows the encodings of the Control Register.

#### **Table 2-6 Control Register**

| Bit    | Field                   | Description                                                |

|--------|-------------------------|------------------------------------------------------------|

| [31:1] | Reserved                | SBZ                                                        |

| [0]    | Unified cache<br>enable | 0 = Cache in bypass mode, default<br>1 = Cache is enabled. |

—— Note ———

Any change to the cache enable bit is seen by slave ports only at the start of a new transaction. If the bit is changed while a transaction is on going on a slave port, that transaction completes as if the enable bit did not change, so an ongoing linefill, and possible subsequent line eviction, completes even if the cache is turned off.

## 2.3.4 Auxiliary Control Register

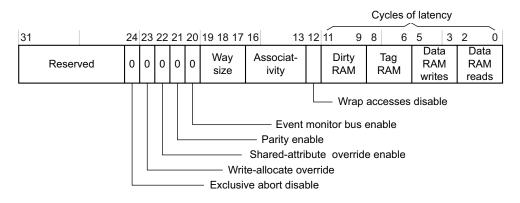

Figure 2-4 on page 2-10 shows the format of the Auxiliary Control Register.

## Figure 2-4 Auxiliary Control Register format

Table 2-7 shows the encodings for the Auxiliary Control Register.

| Table 2-7 Auxiliary Control Register |

|--------------------------------------|

|--------------------------------------|

| Bits    | Field                            | Description                                                                                                                                          |

|---------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:25] | Reserved                         | -                                                                                                                                                    |

| [24]    | Exclusive abort disable          | 0 = The cache controller sends an ERROR response back to exclusive access in a cacheable, shared memory region with shared override bit set, default |

|         |                                  | 1 = abort generation for exclusive access disabled. Treated as cacheable non-shared accesses.                                                        |

| [23]    | Write allocate override          | 0 = Use of <b>HPROT</b> attributes, default                                                                                                          |

|         |                                  | 1 = Override <b>HPROT</b> attributes. All Write-Through and write-back accesses are read-write-allocate.                                             |

| [22]    | Shared attribute override enable | 0 = Shared accesses treated as noncacheable, default                                                                                                 |

|         |                                  | 1 = Shared attribute internally ignored but still forwarded to L3 memory.                                                                            |

| [21]    | Parity enable                    | 0 = Disabled, default                                                                                                                                |

|         |                                  | 1 = Enabled.                                                                                                                                         |

| [20]    | Event bus enable                 | 0 = Disabled, default                                                                                                                                |

|         |                                  | 1 = Enabled.                                                                                                                                         |

| Bits    | Field                          | Description                                                                                                                                                                        |

|---------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [19:17] | Way size                       | 0b000 Reserved, and internally mapped to 16KB                                                                                                                                      |

|         |                                | 0b001 16KB, default                                                                                                                                                                |

|         |                                | 0b010 32KB                                                                                                                                                                         |

|         |                                | 0b011 64KB                                                                                                                                                                         |

|         |                                | 0b100 128KB                                                                                                                                                                        |

|         |                                | 0b101 256KB                                                                                                                                                                        |

|         |                                | 0b110-0b111 Reserved, and internally mapped to 256KB.                                                                                                                              |

| [16:13] | Associativity                  | 0b0000 Cache absent, default                                                                                                                                                       |

|         |                                | 0b0001 direct-mapped cache                                                                                                                                                         |

|         |                                | 0b0010 2-way cache                                                                                                                                                                 |

|         |                                | 0b0011 3-way cache                                                                                                                                                                 |

|         |                                | 0b0100 4-way cache                                                                                                                                                                 |

|         |                                | 0b0101 5-way cache                                                                                                                                                                 |

|         |                                | 0b0110 6-way cache                                                                                                                                                                 |

|         |                                | 0b0111 7-way cache                                                                                                                                                                 |

|         |                                | 0b1000 8-way cache                                                                                                                                                                 |

|         |                                | 0b1001-0b1111 Reserved, and internally mapped to 8-way associativity.                                                                                                              |

| [12]    | Wrap, accesses disable         | 0 = Master ports can perform wrap accesses, default.                                                                                                                               |

|         |                                | 1 = Wrap accesses requested on slave ports are converted to linear accesses<br>on master ports.                                                                                    |

| [11:9]  | Latency for dirty RAM          | 0b000 1 cycle of latency, no additional latency                                                                                                                                    |

| [8:6]   | Latency for tag RAMs           | 0b001 2 cycles of latency                                                                                                                                                          |

| [5:3]   | Latency for data RAM writes    | 0b010 3 cycles of latency<br>0b011 4 cycles of latency                                                                                                                             |

| [2:0]   | Latency for data RAM reads     | 0b100 5 cycles of latency                                                                                                                                                          |

| [2:0]   | Eatency for data for the feats | 0b101 6 cycles of latency                                                                                                                                                          |

|         |                                | 0b110 7 cycles of latency                                                                                                                                                          |

|         |                                | 0b111 8 cycles of latency, default.                                                                                                                                                |

|         |                                | The output signals DIRTYLAT[2:0], TAGLAT[2:0],                                                                                                                                     |

|         |                                | <b>WDATALAT</b> [2:0], and <b>RDATALAT</b> [2:0] reflect the values set in the Auxiliary Control Register in the respective fields. See <i>Miscellaneous signals</i> on page A-16. |

## Table 2-7 Auxiliary Control Register (continued)

## 2.3.5 Cache maintenance operations

The cache maintenance operations groups all Register 7 subregister functions. Table 2-8 shows cache maintenance operations.

| Operation                                 | Description                                                                                                                                                                                                                                                                                    | Bit assignment format          |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Cache Sync                                | Drain write buffer (WB) and eviction buffer (EB) to L3.<br>Drain write-allocate buffer (WA) to the data RAM.                                                                                                                                                                                   | N/A                            |

|                                           | The Cache Sync operation is considered to be complete when the write buffer (WB), eviction buffer (EB) and write-allocate buffer (WA) are empty, regardless of on-going linefills that could generate a new eviction.                                                                          |                                |

| Invalidate by Way                         | Invalidate all data in specified ways including dirty data. Completes<br>as a background task. Invalidate All operation is equivalent to<br>Invalidate by way while selecting all cache ways. Completes as a<br>background task with the selected way or ways locked preventing<br>allocation. | See Figure 2-7 on<br>page 2-15 |

| Invalidate Line by<br>PA                  | Specific line is marked as not valid.                                                                                                                                                                                                                                                          | See Figure 2-5 on page 2-14    |

| Clean Line by<br>Index Way<br>combination | Write the specific line within the specified way to main memory if<br>the line is marked as valid and dirty. The line is marked as not dirty.<br>The valid bit is unchanged.                                                                                                                   | See Figure 2-6 on page 2-14    |

| Clean by Way                              | Writes each line of the specified ways to main memory if the line is<br>marked as valid and dirty. The lines are marked as not dirty. The<br>valid bits are unchanged. Completes as a background task with the<br>selected way or ways locked preventing allocation.                           | See Figure 2-7 on page 2-15    |

| Clean Line by PA                          | Write the specific line to main memory if the line is marked as valid<br>and dirty. The line is marked as not dirty. The valid bit is unchanged.                                                                                                                                               | See Figure 2-5 on page 2-14    |

## Table 2-8 Cache maintenance operations

#### Table 2-8 Cache maintenance operations (continued)

| Operation                                                   | Description                                                                                                                                                                                                                     | Bit assignment format          |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Clean and<br>Invalidate Line by<br>Index Way<br>combination | Write the specific line within the specified way to main memory if<br>the line is marked as valid and dirty. The line is marked as not valid.                                                                                   | See Figure 2-6 on<br>page 2-14 |

| Clean and<br>Invalidate Line by<br>PA                       | Write the specific line to main memory if the line is marked as valid<br>and dirty. The line is marked as not valid.                                                                                                            | See Figure 2-5 on<br>page 2-14 |

| Clean and<br>Invalidate by Way                              | Writes each line of the specified ways to main memory if the line is<br>marked as valid and dirty. The lines are marked as not valid.<br>Completes as a background task with the selected ways locked<br>preventing allocation. | See Figure 2-7 on page 2-15    |

A Cache Sync operation is always performed automatically when an atomic or background cache maintenance operation is requested.

#### —— Note ———

Cache maintenance operations are always performed whatever the state of the cache enable bit, bit 0 of the Control Register, regardless of whether the cache is on or off.

## **Atomic operations**

The following operations stall the requesting slave ports until they complete:

- Clean Line

- Invalidate Line

- Clean and Invalidate Line

- Cache Sync.

## **Background operations**

The following operations run as background tasks. The subregister dedicated to the maintenance operation must be polled to see when a background cache operation has completed:

- Invalidate by Way

- Clean by Way

- Clean and Invalidate by Way.

Requesting slave ports are not stalled during the operation. Table 2-8 on page 2-12 shows what might happen. A background way maintenance operation does not prevent the cache controller from accessing that specific way. For example, accessing data in a line that was in the cache before the start of an Invalidate by Way operation, can cause a cache hit or not, depending on the progress of the background operation. In all cases the cache controller deals with the potential hazards and maintains data coherency.

If an atomic or a background task is requested before a previously requested task has completed, the second request is ignored.

During background operation the targeted way is considered locked. This means that no allocation occurs to that way on read or write misses.

#### Line-based and way-based cache maintenance operations

The cache maintenance operations are executed by writing to the cache operations register r7.

For cache maintenance operations on lines, the line can be accessed using:

- Physical Address

- Index Way combination.

For line-based operations, the PA or Index Way combination is given on **HWDATASx[31:0]**. The physical address format is shown in Figure 2-5.

| 31 |     |  |    |     | 54 |     | 0 |

|----|-----|--|----|-----|----|-----|---|

|    | Tag |  | In | dex |    | SBZ |   |

#### Figure 2-5 Physical address format

\_\_\_\_\_Note \_\_\_\_\_

Because the cache is configurable, the Index field can be one of several bit sizes. This is why it is undefined.

Figure 2-6 shows The Index Way combination format.

| 31 29 | 28 |     |  |       | 5 | 4   | 0 |

|-------|----|-----|--|-------|---|-----|---|

| Way   |    | SBZ |  | Index |   | SBZ |   |

#### Figure 2-6 Index Way combination format

Cache maintenance operations are atomic operations, and writing to the register starts the operation, on the line specified by either {Tag, Index} or {Way, Index}. Tag and Index fields sizes depend on cache way size. See *RAM configuration versus associativity and way size* on page 3-3. The requesting slave port, S1 or S2, remains blocked until the operation completes. Those registers are always read as 0.

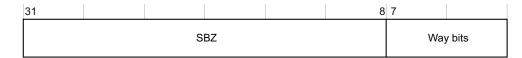

For way-based operations, the way is given on **HWDATASx[31:0**], using the Format C lockdown. Multiple ways can be selected at the same time, by setting the way bits to one. Figure 2-7 shows the format for Format C lockdown.

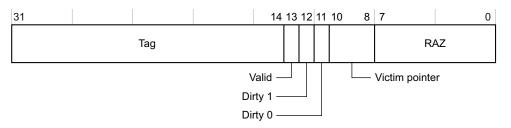

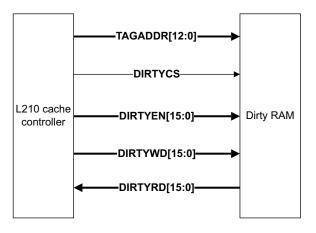

#### Figure 2-7 Lockdown format C