# AMBA<sup>®</sup> DMA Controller DMA-330

Revision: r1p0

**Technical Reference Manual**

Copyright © 2007, 2009 ARM Limited. All rights reserved. ARM DDI 0424B (ID112209)

# AMBA DMA Controller DMA-330 Technical Reference Manual

Copyright © 2007, 2009 ARM Limited. All rights reserved.

#### **Release Information**

The Change history table lists the changes made to this book.

| Date             | Issue | Confidentiality  | Change                           |

|------------------|-------|------------------|----------------------------------|

| 19 December 2007 | А     | Non-Confidential | First issue for the r0p0 release |

| 19 November 2009 | В     | Non-Confidential | First issue for the r1p0 release |

Change history

#### **Proprietary Notice**

Words and logos marked with  $^{\circ}$  or  $^{\sim}$  are registered trademarks or trademarks of ARM $^{\circ}$  in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

Unrestricted Access is an ARM internal classification.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

# Contents AMBA DMA Controller DMA-330 Technical Reference Manual

## Preface

| 1-2<br>1-4<br>1-5<br>1-6<br>1-7<br>1-8<br>1-9<br>. 1-11<br>. 1-12 |

|-------------------------------------------------------------------|

| 1-4<br>1-5<br>1-6<br>1-7<br>1-8<br>1-9<br>. 1-11                  |

| 1-5<br>1-6<br>1-7<br>1-8<br>1-9<br>. 1-11                         |

| 1-5<br>1-6<br>1-7<br>1-8<br>1-9<br>. 1-11                         |

| 1-6<br>1-7<br>1-8<br>1-9<br>. 1-11                                |

| 1-8<br>1-9<br>. 1-11                                              |

| 1-8<br>1-9<br>. 1-11                                              |

| . 1-11                                                            |

|                                                                   |

|                                                                   |

|                                                                   |

|                                                                   |

| 2-2                                                               |

| 2-4                                                               |

| 2-8                                                               |

| . 2-11                                                            |

| . 2-13                                                            |

| . 2-15                                                            |

| . 2-23                                                            |

| . 2-25                                                            |

| . 2-29                                                            |

| . 2-33                                                            |

| . 2-34                                                            |

| -<br>-<br>-                                                       |

About this book ...... x

| Chapter 3  | Prog  | grammers Model                 |     |

|------------|-------|--------------------------------|-----|

| -          | 3.1   | About this programmers model   |     |

|            | 3.2   | Register summary               |     |

|            | 3.3   | Register descriptions          |     |

| Chapter 4  | Instr | ruction Set                    |     |

| -          | 4.1   | Instruction syntax conventions |     |

|            | 4.2   | Instruction set summary        |     |

|            | 4.3   | Instructions                   |     |

|            | 4.4   | Assembler directives           |     |

| Appendix A | Sign  | al Descriptions                |     |

| ••         | A.1   | Clocks and resets              | A-2 |

|            | A.2   | AXI signals                    | A-3 |

|            | A.3   | APB signals                    |     |

|            | A.4   | Peripheral request interface   |     |

|            | A.5   | Interrupt signals              |     |

|            | A.6   | Tie-off signals                | A-9 |

| Appendix B | MFIF  | FO Usage Overview              |     |

| ••         | B.1   | About MFIFO usage overview     | B-2 |

|            | B.2   | Aligned transfers              |     |

|            | B.3   | Unaligned transfers            |     |

|            | B.4   | Fixed transfers                |     |

| Appendix C | Revi  | isions                         |     |

|            | Glos  | ssary                          |     |

|            |       |                                |     |

# List of Tables AMBA DMA Controller DMA-330 Technical Reference Manual

|            | Change history                                           | ii   |

|------------|----------------------------------------------------------|------|

| Table 2-1  | AXI characteristics for a DMA transfer                   | 2-6  |

| Table 2-2  | Handshake rules                                          | 2-16 |

| Table 3-1  | DMAC control register summary                            | 3-5  |

| Table 3-2  | DMA channel thread status register summary               | 3-6  |

| Table 3-3  | AXI status and loop counter register summary             | 3-7  |

| Table 3-4  | DMAC debug register summary                              |      |

| Table 3-5  | DMAC configuration register summary                      | 3-9  |

| Table 3-6  | Peripheral and component identification register summary | 3-10 |

| Table 3-7  | DSR Register bit assignments                             | 3-11 |

| Table 3-8  | DPC Register bit assignments                             | 3-12 |

| Table 3-9  | INTEN Register bit assignments                           | 3-13 |

| Table 3-10 | INT_EVENT_RIS Register bit assignments                   | 3-14 |

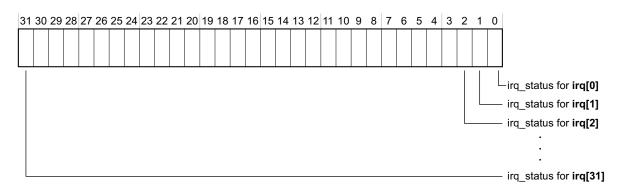

| Table 3-11 | INTMIS Register bit assignments                          | 3-15 |

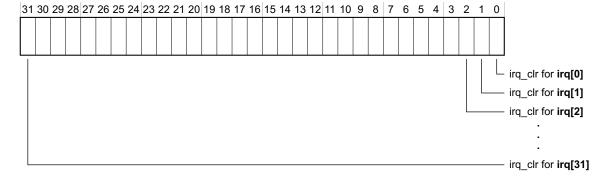

| Table 3-12 | INTCLR Register bit assignments                          | 3-16 |

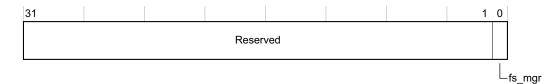

| Table 3-13 | FSRD Register bit assignments                            | 3-16 |

| Table 3-14 | FSRC Register bit assignments                            | 3-17 |

| Table 3-15 | FTRD Register bit assignments                            | 3-18 |

| Table 3-16 | FTRn Register bit assignments                            | 3-19 |

| Table 3-17 | CSRn Register bit assignments                            | 3-22 |

| Table 3-18 | CPCn Register bit assignments                            | 3-23 |

| Table 3-19 | SARn Register bit assignments                            | 3-24 |

| Table 3-20 | DARn Register bit assignments                            | 3-25 |

| Table 3-21 | CCRn Register bit assignments                            | 3-26 |

| Table 3-22 | Swap data                                                | 3-29 |

| Table 3-23 | LC0_n Register bit assignments                           | 3-30 |

| Table 3-24 | LC1_n Register bit assignments                           | 3-30 |

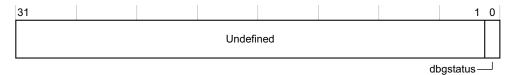

| Table 3-25 | DBGSTATUS Register bit assignments                     |      |

|------------|--------------------------------------------------------|------|

| Table 3-26 | DBGCMD Register bit assignments                        |      |

| Table 3-27 | DBGINST0 Register bit assignments                      |      |

| Table 3-28 | DBGINST1 Register bit assignments                      |      |

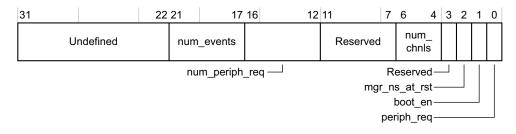

| Table 3-29 | CR0 Register bit assignments                           |      |

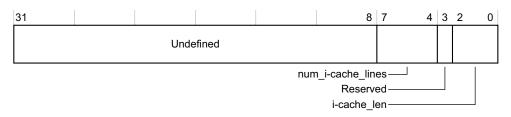

| Table 3-30 | CR1 Registers bit assignments                          |      |

| Table 3-31 | CR2 Register bit assignments                           |      |

| Table 3-32 | CR3 Register bit assignments                           |      |

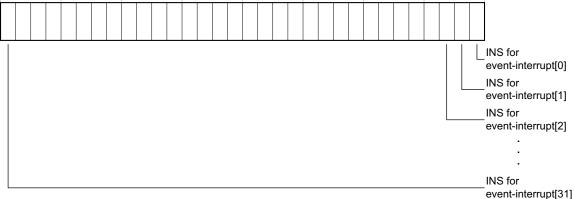

| Table 3-33 | CR4 Register bit assignments                           |      |

| Table 3-34 | CRD Registers bit assignments                          | 3-39 |

| Table 3-35 | WD Register bit assignments                            |      |

| Table 3-36 | Conceptual peripheral ID register bit assignments      | 3-41 |

| Table 3-37 | periph_id_0 Register bit assignments                   | 3-42 |

| Table 3-38 | periph_id_1 Register bit assignments                   | 3-42 |

| Table 3-39 | periph_id_2 Register bit assignments                   | 3-42 |

| Table 3-40 | periph_id_3 Register bit assignments                   | 3-42 |

| Table 3-41 | pcell_id Register bit assignments                      | 3-43 |

| Table 4-1  | Instruction syntax summary                             | 4-3  |

| Table 4-2  | DMAMOV CCR argument description and the default values | 4-21 |

| Table A-1  | Clock and reset                                        | A-2  |

| Table A-2  | AXI-AW signals                                         | A-3  |

| Table A-3  | AXI-W signals                                          | A-3  |

| Table A-4  | AXI-B signals                                          | A-4  |

| Table A-5  | AXI-AR signals                                         | A-4  |

| Table A-6  | AXI-R signals                                          | A-4  |

| Table A-7  | Non-secure APB interface signals                       | A-6  |

| Table A-8  | Secure APB interface signals                           | A-6  |

| Table A-9  | Peripheral request interface                           | A-7  |

| Table A-10 | Interrupt signals                                      | A-8  |

| Table A-11 | DMAC tie-off signals                                   |      |

| Table A-12 | Interrupt and peripheral tie-off signals               | A-9  |

| Table C-1  | Differences between issue A and issue B                | C-1  |

# List of Figures AMBA DMA Controller DMA-330 Technical Reference Manual

|             | Key to timing diagram conventions                                 | xi   |

|-------------|-------------------------------------------------------------------|------|

| Figure 1-1  | Interfaces on the DMAC                                            | 1-2  |

| Figure 1-2  | Example system                                                    | 1-2  |

| Figure 2-1  | DMAC block diagram                                                | 2-2  |

| Figure 2-2  | APB slave interfaces                                              | 2-4  |

| Figure 2-3  | AXI master interface connections                                  | 2-5  |

| Figure 2-4  | Peripheral request interface                                      | 2-7  |

| Figure 2-5  | Interrupt interface                                               | 2-7  |

| Figure 2-6  | Reset initialization interface                                    | 2-7  |

| Figure 2-7  | Thread operating states                                           | 2-8  |

| Figure 2-8  | Request and acknowledge buses on the peripheral request interface | 2-15 |

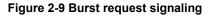

| Figure 2-9  | Burst request signaling                                           | 2-21 |

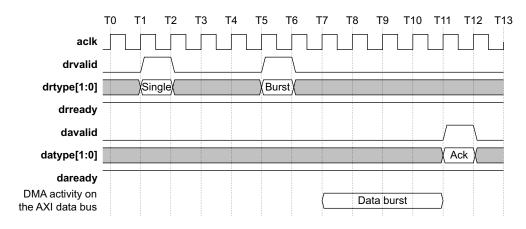

| Figure 2-10 | Single and burst request signaling                                | 2-21 |

| Figure 2-11 | Single transfers for a burst request                              | 2-22 |

| Figure 2-12 | Abort process                                                     | 2-27 |

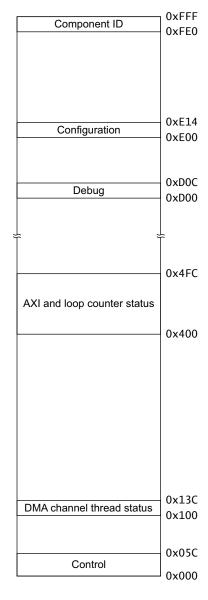

| Figure 3-1  | DMAC summary register map                                         | 3-3  |

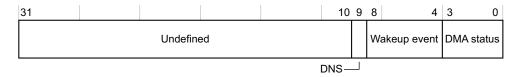

| Figure 3-2  | DSR Register bit assignments                                      | 3-11 |

| Figure 3-3  | DPC Register bit assignments                                      | 3-12 |

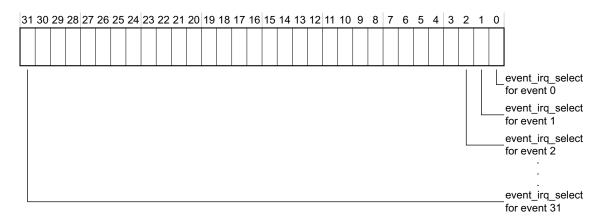

| Figure 3-4  | INTEN Register bit assignments                                    | 3-13 |

| Figure 3-5  | INT_EVENT_RIS Register bit assignments                            | 3-14 |

| Figure 3-6  | INTMIS Register bit assignments                                   | 3-15 |

| Figure 3-7  | INTCLR Register bit assignments                                   | 3-15 |

| Figure 3-8  | FSRD Register bit assignments                                     | 3-16 |

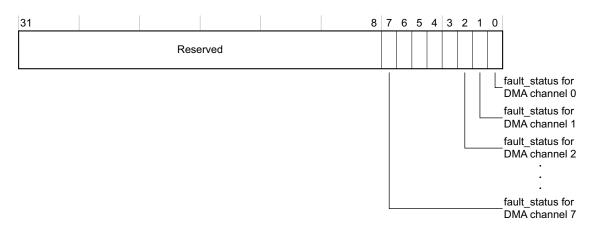

| Figure 3-9  | FSRC Register bit assignments                                     |      |

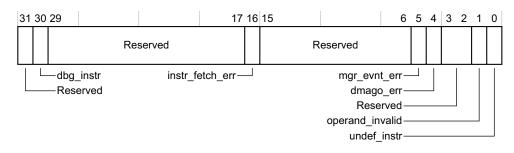

| Figure 3-10 | FTRD Register bit assignments                                     | 3-17 |

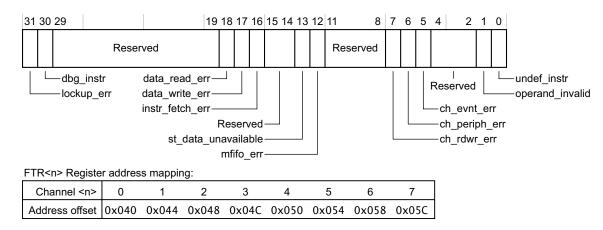

| Figure 3-11 | FTRn Register bit assignments                                     | 3-19 |

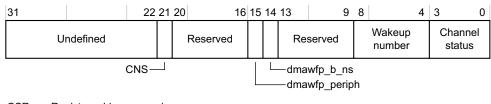

| Figure 3-12 | CSRn Register bit assignments                                     | 3-21 |

| Figure 3-13 | CPC Register bit assignments and address offsets                                   | 3-23 |

|-------------|------------------------------------------------------------------------------------|------|

| Figure 3-14 | SARn Register bit assignments and address offsets                                  |      |

| Figure 3-15 | DARn Register bit assignments and address offsets                                  |      |

| Figure 3-16 | CCRn Register bit assignments and base address offsets                             |      |

| Figure 3-17 | LC0 n Register bit assignments and base address offsets                            |      |

| Figure 3-18 | LC1_n Register bit assignments and base address offsets                            |      |

| Figure 3-19 | DBGSTATUS Register bit assignments                                                 | 3-31 |

| Figure 3-20 | DBGCMD Register bit assignments                                                    | 3-31 |

| Figure 3-21 | DBGINST0 Register bit assignments                                                  |      |

| Figure 3-22 | DBGINST1 Register bit assignments                                                  | 3-33 |

| Figure 3-23 | CR0 Register bit assignments                                                       |      |

| Figure 3-24 | CR1 Register bit assignments                                                       |      |

| Figure 3-25 | CR2 Register bit assignments                                                       | 3-36 |

| Figure 3-26 | CR3 Register bit assignments                                                       | 3-37 |

| Figure 3-27 | CR4 Register bit assignments                                                       | 3-38 |

| Figure 3-28 | CRD Register bit assignments                                                       | 3-38 |

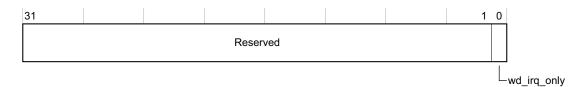

| Figure 3-29 | WD Register bit assignments                                                        | 3-40 |

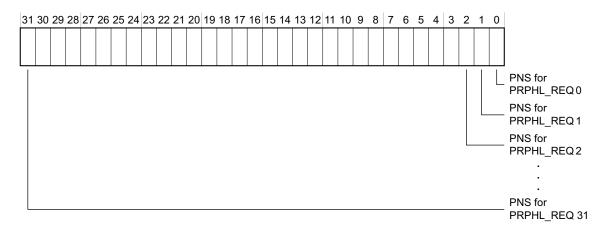

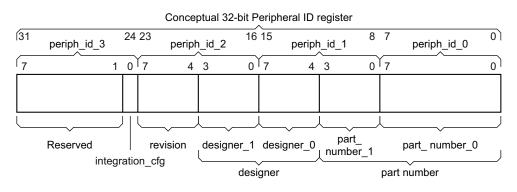

| Figure 3-30 | periph_id Register bit assignments                                                 | 3-41 |

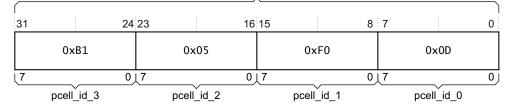

| Figure 3-31 | pcell_id Register bit assignments                                                  |      |

| Figure 4-1  | DMAADDH encoding                                                                   |      |

| Figure 4-2  | DMAEND encoding                                                                    | 4-4  |

| Figure 4-3  | DMAFLUSHP encoding                                                                 | 4-5  |

| Figure 4-4  | DMAGO encoding                                                                     | 4-6  |

| Figure 4-5  | DMAKILL encoding                                                                   | 4-7  |

| Figure 4-6  | DMALD[S B] encoding                                                                |      |

| Figure 4-7  | DMALDP <s b> encoding</s b>                                                        |      |

| Figure 4-8  | DMALP encoding                                                                     |      |

| Figure 4-9  | DMALPEND[S B] encoding                                                             |      |

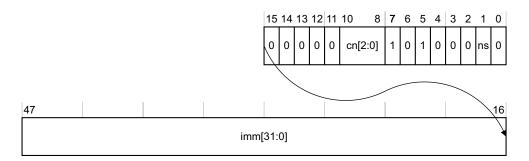

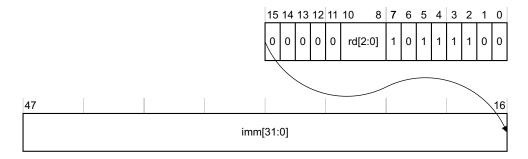

| Figure 4-10 | DMAMOV encoding                                                                    |      |

| Figure 4-11 | DMANOP encoding                                                                    |      |

| Figure 4-12 | DMARMB encoding                                                                    |      |

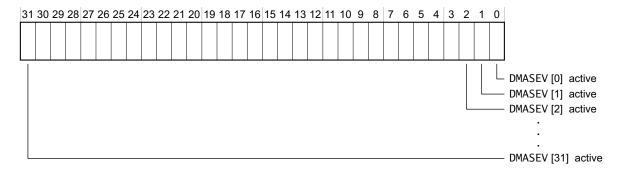

| Figure 4-13 | DMASEV encoding                                                                    |      |

| Figure 4-14 | DMAST[S B] encoding                                                                |      |

| Figure 4-15 | DMASTP <s b> encoding</s b>                                                        |      |

| Figure 4-16 | DMASTZ encoding                                                                    |      |

| Figure 4-17 | DMAWFE encoding                                                                    |      |

| Figure 4-18 | DMAWFP encoding                                                                    |      |

| Figure 4-19 | DMAWMB encoding                                                                    |      |

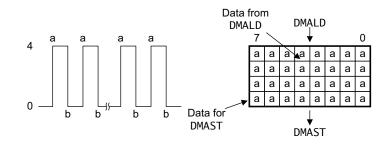

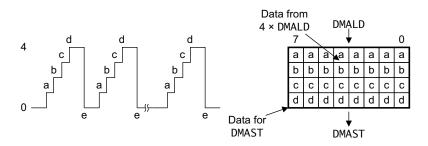

| Figure B-1  | Simple aligned program                                                             |      |

| Figure B-2  | Aligned asymmetric program with multiple loads                                     |      |

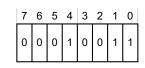

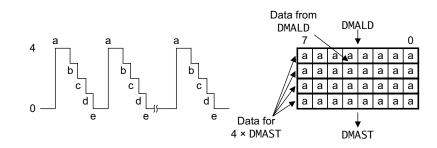

| Figure B-3  | Aligned asymmetric program with multiple stores                                    |      |

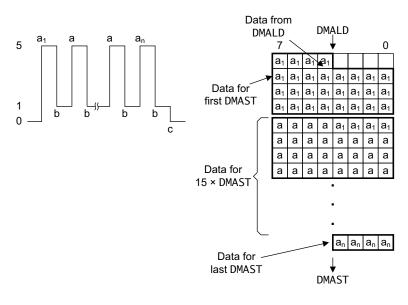

| Figure B-4  | Aligned to unaligned program                                                       |      |

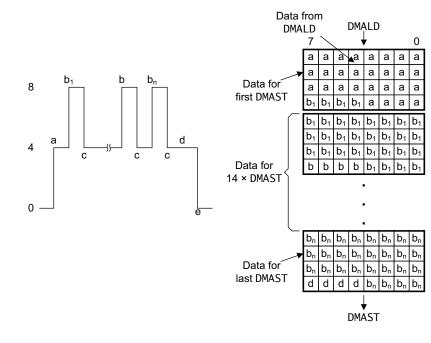

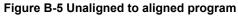

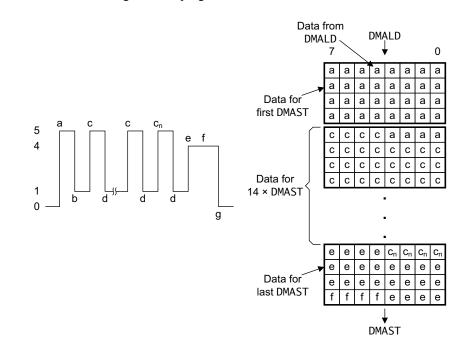

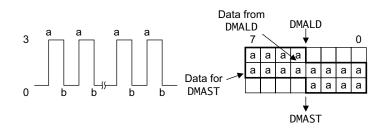

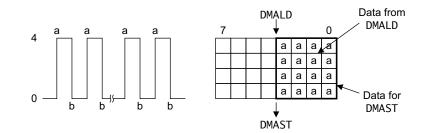

| Figure B-5  | Unaligned to aligned program                                                       |      |

| Figure B-6  | Unaligned to aligned with excess initial load                                      |      |

| Figure B-7  | Aligned burst with unaligned MFIFO width<br>Fixed destination with aligned address |      |

| Figure B-8  | I INCU UCOLINALIUN WILL ANY ICU AUUICOO                                            | D-Э  |

# Preface

This preface introduces the *AMBA DMA Controller DMA-330 Technical Reference Manual*. It contains the following sections:

- *About this book* on page x

- *Feedback* on page xiii.

# About this book

This is the Technical Reference Manual (TRM) for the AMBA DMA Controller DMA-330.

| Product revision status |                                                                                                        |                                                                                                                                                                |  |

|-------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                         | The <i>rnpn</i> identifier indicates the revision status of the product described in this book, where: |                                                                                                                                                                |  |

|                         | r <i>n</i>                                                                                             | Identifies the major revision of the product.                                                                                                                  |  |

|                         | р <i>п</i>                                                                                             | Identifies the minor revision or modification status of the product.                                                                                           |  |

| Intended audience       |                                                                                                        |                                                                                                                                                                |  |

|                         |                                                                                                        | written for system designers, system integrators, and programmers who are programming a <i>System-on-Chip</i> (SoC) device that uses the <i>DMA Controller</i> |  |

| Using this book         |                                                                                                        |                                                                                                                                                                |  |

|                         | This book is                                                                                           | organized into the following chapters:                                                                                                                         |  |

|                         | Chapter 1 In                                                                                           | ntroduction                                                                                                                                                    |  |

|                         |                                                                                                        | Read this for a high-level view of the DMAC.                                                                                                                   |  |

|                         | Chapter 2 F                                                                                            | unctional Overview                                                                                                                                             |  |

|                         |                                                                                                        | Read this for a description of the major interfaces and components of the DMAC. The chapter also describes how they operate.                                   |  |

|                         | Chapter 3 P                                                                                            | rogrammers Model                                                                                                                                               |  |

|                         |                                                                                                        | Read this for a description of the DMAC memory map and registers.                                                                                              |  |

|                         | Chapter 4 <i>In</i>                                                                                    | istruction Set                                                                                                                                                 |  |

|                         |                                                                                                        | Read this for a description of the instruction set.                                                                                                            |  |

|                         | Appendix A                                                                                             | Signal Descriptions                                                                                                                                            |  |

|                         |                                                                                                        | Read this for a description of the DMAC input and output signals.                                                                                              |  |

|                         | Appendix B                                                                                             | MFIFO Usage Overview                                                                                                                                           |  |

|                         |                                                                                                        | Read this for a description of how the DMAC uses the MFIFO.                                                                                                    |  |

|                         | Appendix C                                                                                             | Revisions                                                                                                                                                      |  |

|                         |                                                                                                        | Read this for a description of the technical changes between released issues of this book.                                                                     |  |

|                         | Glossary                                                                                               | Read this for definitions of terms used in this book.                                                                                                          |  |

| Conventions             |                                                                                                        |                                                                                                                                                                |  |

|                         | Conventions                                                                                            | that this book can use are described in:                                                                                                                       |  |

|                         | • Typogr                                                                                               | aphical on page xi                                                                                                                                             |  |

|                         | • <i>Timing diagrams</i> on page xi                                                                    |                                                                                                                                                                |  |

|                         | • Signals                                                                                              | on page xi.                                                                                                                                                    |  |

## Typographical

The typographical conventions are:

| lighlights important notes, introduces special terminology, denotes nternal cross-references, and citations.                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| lighlights interface elements, such as menu names. Denotes signal ames. Also used for terms in descriptive lists, where appropriate.                                               |

| Denotes text that you can enter at the keyboard, such as commands, file nd program names, and source code.                                                                         |

| Denotes a permitted abbreviation for a command or option. You can enter<br>the underlined text instead of the full command or option name.                                         |

| Denotes arguments to monospace text where the argument is to be eplaced by a specific value.                                                                                       |

| Denotes language keywords when used outside example code.                                                                                                                          |

| Enclose replaceable terms for assembler syntax where they appear in code<br>r code fragments. For example:<br>RC p15, 0 <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd> |

| h<br>H<br>H<br>H<br>H<br>H<br>H<br>H<br>H<br>H<br>H<br>H<br>H<br>H<br>H<br>H<br>H<br>H<br>H<br>H                                                                                   |

## **Timing diagrams**

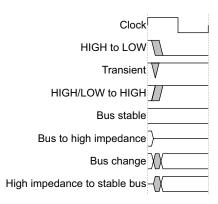

The figure named *Key to timing diagram conventions* explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

#### Key to timing diagram conventions

#### Signals

The signal conventions are:

| Signal level | The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means: |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------|--|--|

|              | • HIGH for active-HIGH signals                                                                              |  |  |

|              | • LOW for active-LOW signals.                                                                               |  |  |

|              |                                                                                                             |  |  |

Lower-case n At the start or end of a signal name denotes an active-LOW signal.

## Additional reading

This section lists publications by ARM and by third parties.

See Infocenter, http://infocenter.arm.com, for access to ARM documentation.

#### **ARM** publications

This book contains information that is specific to this product. See the following documents for other relevant information:

- AMBA DMA Controller DMA-330 Implementation Guide (ARM DII 0192)

- AMBA DMA Controller DMA-330 Integration Manual (ARM DII 0193)

- AMBA Designer (FD001) User Guide (ARM DUI 0333)

- AMBA DMA Controller DMA-330 Supplement to AMBA Designer (FD001) User Guide (ARM DSU 0009)

- ARM Architecture Reference Manual, ARMv7-A and ARMv7-R edition (ARM DDI 0406)

- AMBA AXI Protocol v1.0 Specification (ARM IHI 0022)

- AMBA 3 APB Protocol v1.0 Specification (ARM IHI 0024).

## Other publications

This section lists relevant documents published by third parties:

JEDEC Standard Manufacturer's Identification Code, JEP106, http://www.jedec.org.

# Feedback

ARM welcomes feedback on this product and its documentation.

## Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

## Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- the title

- the number, ARM DDI 0424B

- the page numbers to which your comments apply

- a concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

# Chapter 1 Introduction

This chapter introduces the DMA Controller (DMAC). It contains the following sections:

- *About the DMAC* on page 1-2

- *Compliance* on page 1-4

- *Features* on page 1-5

- *Interfaces* on page 1-6

- *Configurable options* on page 1-7

- *Test features* on page 1-8

- Product documentation, design flow, and architecture on page 1-9

- Product revisions on page 1-11

- *Terminology* on page 1-12.

—Note ——

The DMAC product designator is either PL330 or DMA-330 and depends on the product revision as follows:

**r0p0** PL330.

r1p0 or later DMA-330.

# 1.1 About the DMAC

The DMAC is an *Advanced Microcontroller Bus Architecture* (AMBA) compliant peripheral that is developed, tested, and licensed by ARM.

The DMAC provides an AXI interface to perform the DMA transfers and two APB interfaces that control its operation. The DMAC implements TrustZone<sup>®</sup> secure technology with one APB interface operating in the Secure state and the other operating in the Non-secure state. See the *ARM Architecture Reference Manual* for more information about TrustZone technology.

The DMAC includes a small instruction set that provides a flexible method of specifying the DMA operations. This enables it to provide greater flexibility than the fixed capabilities of a *Linked-List Item* (LLI) based DMA controller. To minimize the program memory requirements, the DMAC uses variable-length instructions.

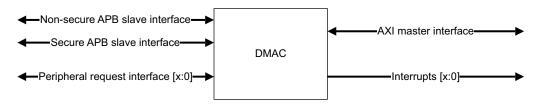

Figure 1-1 shows the interfaces that are available on the DMAC.

Figure 1-1 Interfaces on the DMAC

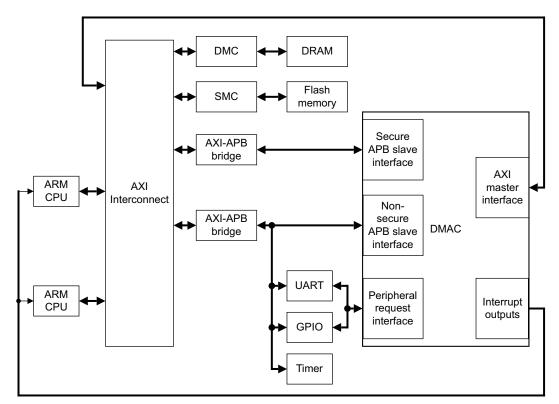

Figure 1-2 shows an example system that contains a DMAC.

# Figure 1-2 Example system

The example system contains:

AXI bus masters:

•

- a DMAC

- two ARM processors.

- an AXI interconnect and two AMBA protocol bridge components

- AMBA slaves:

- a Dynamic Memory Controller (DMC)

- a Static Memory Controller (SMC)

- a Timer

- a General Purpose Input-Output (GPIO)

- a Universal Asynchronous Receiver-Transmitter (UART).

The AXI interconnect enables each bus master to access the slaves. The ARM processors can access the APB interfaces of the DMAC by using the appropriate AXI to APB bridge component.

# 1.2 Compliance

The DMAC is compliant with the following standards and protocols:

- AMBA 3 AXI protocol

- AMBA 3 APB protocol.

# 1.3 Features

The DMAC provides the following features:

- an instruction set that provides flexibility for programming DMA transfers

- a single AXI master interface that performs the DMA transfers

- dual APB slave interfaces, designated as secure and non-secure, for accessing registers in the DMAC

- supports TrustZone technology

- supports multiple transfer types:

- memory-to-memory

- memory-to-peripheral

- peripheral-to-memory

- scatter-gather.

- configurable RTL that enables you to optimize the DMAC for the application

- programmable security state for each DMA channel

- signals the occurrence of various DMA events using the interrupt output signals.

# 1.4 Interfaces

The DMAC has the following external interfaces:

- AMBA AXI master interface, for transfer of memory data to or from an AMBA slave

- AMBA 3 APB slave interface, for programming the DMAC.

# 1.5 Configurable options

The DMAC has the following configurable options:

- AXI data bus width

- number of active AXI read transactions

- number of active AXI write transactions

- number of DMA channels

- depth of the internal data buffer

- number of lines in the instruction cache and how many words a line contains

- depth of the read instruction queue

- depth of the write instruction queue

- number of peripheral request interfaces

- request acceptance capability of a peripheral request interface

- number of interrupt output signals.

## —— Note ———

See the *AMBA DMA Controller DMA-330 Supplement to AMBA Designer (FD001) User Guide* for information about how to configure these features and the values that you can assign.

# 1.6 Test features

The DMAC does not provide test features.

# **1.7 Product documentation, design flow, and architecture**

This section describes the DMAC books, how they relate to the design flow, and the relevant architectural standards and protocols.

See *Additional reading* on page xii for more information about the books described in this section.

## 1.7.1 Documentation

The DMAC documentation is as follows:

### **Technical Reference Manual**

The *Technical Reference Manual* (TRM) describes the functionality and the effects of functional options on the behavior of the DMAC. It is required at all stages of the design flow. Some behavior described in the TRM might not be relevant because of the way that the DMAC is implemented and integrated. If you are programming the DMAC then contact:

- the implementer to determine the build configuration of the implementation

- the integrator to determine the signal configuration of the SoC that you are using.

The TRM complements protocol specifications and relevant external standards. It does not duplicate information from these sources.

## User Guide

The User Guide (UG) describes:

- the available build configuration options and related issues in selecting them

- how to use AMBA Designer to:

- configure the DMAC

- generate the *Register Transfer Level* (RTL).

The UG is a confidential book that is only available to licensees.

## **Implementation Guide**

The Implementation Guide (IG) describes:

- the *Out-Of-Box* instructions

- the synthesis constraints.

The ARM product deliverables include reference scripts and information about using them to implement your design.

The IG is a confidential book that is only available to licensees.

#### **Integration Manual**

The *Integration Manual* (IM) describes how to integrate the DMAC into a SoC. It includes describing the signals that the integrator must tie off to configure the macrocell for the required integration. Some of the integration is affected by the configuration options used when implementing the DMAC.

The IM is a confidential book that is only available to licensees.

## 1.7.2 Design flow

The DMAC is delivered as synthesizable RTL. Before it can be used in a product, it must go through the following process:

- 1. Implementation. The implementer configures and synthesizes the RTL to produce a hard macrocell.

- 2. Integration. The integrator connects the implemented design into an SoC. This includes connecting it to a memory system and peripherals.

- 3. Programming. The system programmer develops the software required to control the DMAC and tests the required application software.

Each stage of the process:

- can be performed by a different party

- can include options that affect the behavior and features at the next stage:

#### **Build configuration**

The implementer chooses the options that affect how the RTL source files are pre-processed. They usually include or exclude logic that can affect the area or maximum frequency of the resulting macrocell.

## **Configuration inputs**

The integrator configures some features of the DMAC by tying inputs to specific values. These configurations affect the start-up behavior prior to the software taking control. They can also limit the options available to the software. See *Tie-off signals* on page A-9.

#### Software control

The programmer updates the DMAC by programming particular values into software-visible registers. This affects the behavior of the DMAC.

#### **1.7.3 ARM** architecture and protocol information

The DMAC complies with, or implements, the ARM specifications described in:

Advanced Microcontroller Bus Architecture.

## Advanced Microcontroller Bus Architecture

The DMAC complies with the:

- AMBA AXI protocol, see the AMBA AXI Protocol Specification

- AMBA 3 APB protocol, see the AMBA 3 APB Protocol Specification.

# 1.8 **Product revisions**

This section describes the differences in functionality between the product revisions:

r0p0 First release.

**r0p0 - r1p0** This release includes:

- precise lockup detection, see *Watchdog abort* on page 2-26

- no store before load, see *Abort sources* on page 2-25

- addition of the WD Register, see *Watchdog Register* on page 3-40.

# 1.9 Terminology

This manual uses the following terminology:

#### Configurable

A parameter of the DMAC that you can only change prior to the RTL being generated. See the *AMBA DMA Controller DMA-330 Supplement to AMBA Designer (FD001) User Guide* for information about configuring the DMAC.

#### Programmable

A parameter of the DMAC that you can change after the RTL is generated. See Chapter 3 *Programmers Model* for information about programming the DMAC.

### Initialization

A feature of the DMAC that is initialized when it exits from reset, depending on the state of the *Tie-off signals* on page A-9. See *Initializing the DMAC* on page 2-11.

### **DMA channel**

A section of the DMAC that controls a DMA cycle by executing its own program thread. You can configure the number of channels that the DMAC contains.

**DMA cycle** All the DMA transfers that the DMAC must perform, to transfer the programmed number of data packets.

#### **DMA** manager

A section of the DMAC that manages the operation of the DMAC by executing its own program thread.

#### **DMA transfer**

The action of transferring a single byte, halfword, or word.

# Chapter 2 Functional Overview

This chapter describes the major interfaces and components of the DMAC, and how it operates. It contains the following sections:

- *Overview* on page 2-2

- DMAC interfaces on page 2-4

- *Operating states* on page 2-8

- Initializing the DMAC on page 2-11

- Using the APB slave interfaces on page 2-13

- Peripheral request interface on page 2-15

- Using events and interrupts on page 2-23

- Security usage on page 2-29

- *Aborts* on page 2-25

- Security usage on page 2-29

- Constraints and limitations of use on page 2-33

- *Programming restrictions* on page 2-34.

# 2.1 Overview

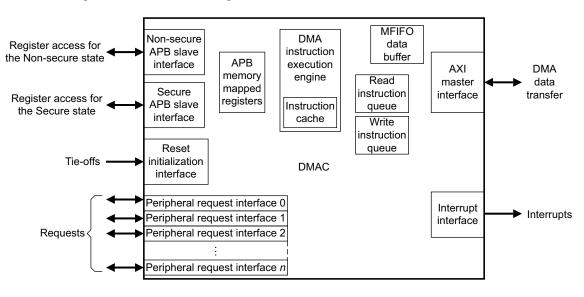

Figure 2-1 shows a block diagram of the DMAC.

#### Figure 2-1 DMAC block diagram

The DMAC contains an instruction processing block that enables it to process program code that controls a DMA transfer. The program code is stored in a region of system memory that the DMAC accesses using its AXI interface. The DMAC stores instructions temporarily in a cache. You can configure the line length and depth of the cache.

You can configure the DMAC with up to eight DMA channels, with each channel capable of supporting a single concurrent thread of DMA operation. In addition, a single DMA manager thread exists, and you can use it to initialize the DMA channel threads. The DMAC executes up to one instruction for each AXI clock cycle. To ensure that it regularly executes each active thread, it alternates by processing the DMA manager thread and then a DMA channel thread. It uses a round-robin process when selecting the next active DMA channel thread to execute.

The DMAC uses variable-length instructions that consist of one to six bytes. It provides a separate *Program Counter* (PC) register for each DMA channel. When a thread requests an instruction from an address, the cache performs a look-up. If a cache hit occurs, then the cache immediately provides the data. Otherwise, the thread is stalled while the DMAC uses the AXI interface to perform a cache line fill. If an instruction is greater than 4 bytes, or spans the end of a cache line, the DMAC performs multiple cache accesses to fetch the instruction.

\_\_\_\_\_Note \_\_\_\_\_

When a cache line fill is in progress, the DMAC enables other threads to access the cache, but if another cache miss occurs, this stalls the pipeline until the first line fill is complete.

When a DMA channel thread executes a load or store instruction, the DMAC adds the instruction to the relevant read or write queue. The DMAC uses these queues as an instruction storage buffer prior to it issuing the instructions on the AXI bus. The DMAC also contains a *Multi First-In-First-Out* (MFIFO) data buffer that it uses to store data that it reads, or writes, during a DMA transfer.

— Note —

To meet your system requirements you can configure the:

depth of the read queue

- depth of the write queue

- depth of the MFIFO.

٠

The DMAC provides multiple interrupt outputs to enable efficient communication of events to external microprocessors. The peripheral request interfaces support the connection of DMA-capable peripherals to enable memory-to-peripheral and peripheral-to-memory DMA transfers to occur, without intervention from a microprocessor.

Dual APB interfaces enable the operation of the DMAC to be partitioned into the Secure state and Non-secure state. You can use the APB interfaces to access status registers and also directly execute instructions in the DMAC.

# 2.2 DMAC interfaces

The DMAC contains the following interfaces:

- *APB slave interfaces*

- AXI master interface

- Peripheral request interfaces on page 2-6

- Interrupt interface on page 2-7

- *Reset initialization interface* on page 2-7.

## 2.2.1 APB slave interfaces

The DMAC provides the following APB interfaces:

- non-secure APB slave interface

- secure APB slave interface.

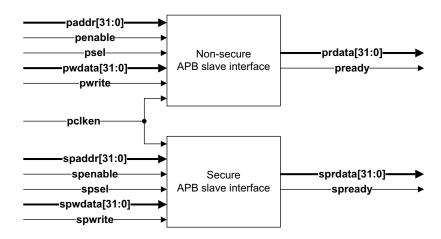

You can use these interfaces to access the registers that control the functionality of the DMAC. Figure 2-2 shows the signal connections for both interfaces.

#### Figure 2-2 APB slave interfaces

The DMAC allocates 4KB of memory for each APB interface and implements the memory map that Chapter 3 *Programmers Model* describes.

The same clock as the AXI domain clock, **aclk**, clock the APB interfaces. However, the DMAC provides a clock enable signal, **pclken**, that enables both APB interfaces to operate at a slower clock rate. The clock enable signal must be an integer divisor of **aclk**.

#### 2.2.2 AXI master interface

The DMAC contains a single AXI master interface that enables it to transfer data from a source AXI slave to a destination AXI slave.

The DMAC complies to the AMBA AXI protocol. See the *AMBA AXI Protocol Specification* for more information.

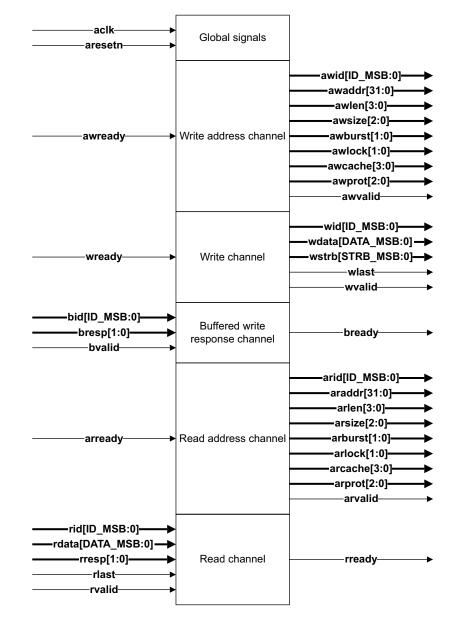

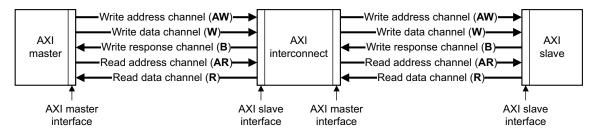

Figure 2-3 on page 2-5 shows the AXI master interface external connections.

#### Figure 2-3 AXI master interface connections

—— Note ———

In Figure 2-3:

- awcache[2] is tied LOW

- arcache[3] is tied LOW

- the DMAC does not support locked or exclusive accesses and therefore, **arlock[1:0]** and **awlock[1:0]** are tied LOW

- the value of ID\_MSB depends on the number of DMA channels in the configured DMAC

- the values of DATA\_MSB and STRB\_MSB depend on the data width of the configured DMAC.

When a DMA channel thread accesses the AXI interface, the DMAC signals the AXI identification tag to be the same number as the DMA channel. For example, when the program thread for DMA channel 5 performs a DMA store operation, the DMAC sets **AWID[2:0]** and **WID[2:0]** to b101.

When the DMA manager thread accesses the AXI interface, the DMAC signals the AXI identification tag to be the same number as the number of DMA channels that the DMAC provides. For example, if the DMAC is configured to provide eight DMA channels, when the DMA manager performs a read operation, the DMAC sets **ARID**[3:0] to b1000.

#### AXI characteristics for a DMA transfer

Table 2-1 shows how the DMAC controls the AXI control signals, depending on the type of DMA access it performs.

| Access type                   | AxPROT                                                                 | AxLEN                       | AxBURST             | AxSIZE                      | AxCACHE                     |

|-------------------------------|------------------------------------------------------------------------|-----------------------------|---------------------|-----------------------------|-----------------------------|

| DMA channel load              |                                                                        | See Channel Con             | trol Registers on p | page 3-25                   |                             |

| DMA channel store             |                                                                        | See Channel Con             | trol Registers on p | page 3-25                   |                             |

| DMA manager instruction fetch | Privileged.<br>Secure state from DNS <sup>a</sup> bit.<br>Instruction. | See ARLEN and<br>ARSIZE for | INCR                | See ARLEN and<br>ARSIZE for | Cacheable<br>write-through, |

| DMA channel instruction fetch | Privileged.<br>Secure state from CNS <sup>b</sup> bit.<br>Instruction. | instruction<br>fetches      | INCK                | instruction<br>fetches      | allocate on reads only.     |

## Table 2-1 AXI characteristics for a DMA transfer

a. The DSR Register contains the DNS bit. See DMA Manager Status Register on page 3-11.

b. The CSRn Register contains the CNS bit for DMA channel n. See Channel Status Registers on page 3-21.

#### **ARLEN and ARSIZE for instruction fetches**

When performing an instruction fetch, the DMAC sets ARLEN and ARSIZE as follows:

#### Instruction cache length $\leq$ AXI data bus width

- **ARLEN** = 1

- **ARSIZE** = length of instruction cache in bytes.

#### Instruction cache length > AXI data bus width

- **ARLEN** = ratio of the length of an instruction cache line in bytes to the width of the AXI data bus in bytes

- **ARSIZE** = width of AXI data bus in bytes.

#### 2.2.3 Peripheral request interfaces

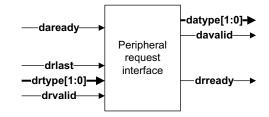

Figure 2-4 on page 2-7 shows the signals that a single peripheral request interface provides.

Figure 2-4 Peripheral request interface

The peripheral request interface supports the connection of DMA-capable peripherals. You must configure the number of peripheral request interfaces that you require, as the *AMBA DMA Controller DMA-330 Supplement to AMBA Designer (FD001) User Guide* describes.

#### 2.2.4 Interrupt interface

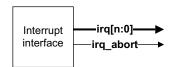

The interrupt interface enables efficient communications of events to an external microprocessor. Figure 2-5 shows the signals that this interface provides.

#### Figure 2-5 Interrupt interface

You must configure the number of interrupts that you require, as the AMBA DMA Controller DMA-330 Supplement to AMBA Designer (FD001) User Guide describes.

## 2.2.5 Reset initialization interface

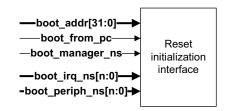

This interface enables you to initialize the operating state of the DMAC as it exits from reset. Figure 2-6 shows the tie-off signals that this interface provides.

Figure 2-6 Reset initialization interface

# 2.3 Operating states

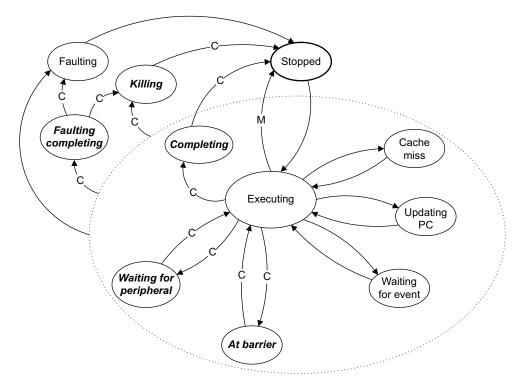

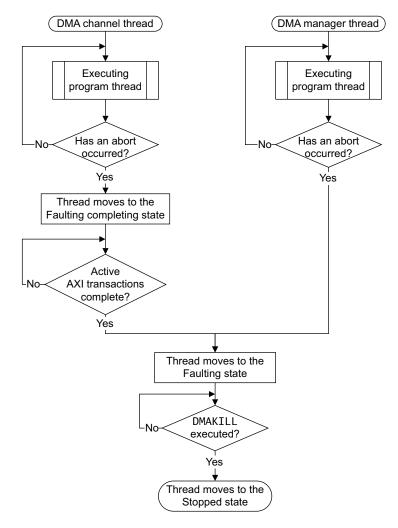

Figure 2-7 shows the operating states for the DMA manager thread and DMA channel threads. The DMAC provides a separate state machine for each thread.

Figure 2-7 Thread operating states

\_\_\_\_\_Note \_\_\_\_\_

In Figure 2-7, the DMAC permits that:

- only DMA channel threads can use states in bold italics

- arcs with no letter designator indicate state transitions for the DMA manager and DMA channel threads, otherwise use is restricted as follows:

- C DMA channel threads only.

- M DMA manager thread only.

- states within the dotted line can transition to the Faulting completing, Faulting, or Killing states.

After the DMAC exits from reset, it sets all DMA channel threads to the Stopped state, and the status of **boot\_from\_pc** controls the DMA manager thread state:

#### boot\_from\_pc is LOW

DMA manager thread moves to the Stopped state.

### boot\_from\_pc is HIGH

DMA manager thread moves to the Executing state.

The following sections describe the states:

- Stopped on page 2-9

- *Executing* on page 2-9

- *Cache miss* on page 2-10

- *Updating PC* on page 2-10

- *Waiting for event* on page 2-10

- At barrier on page 2-10

- *Waiting for peripheral* on page 2-10

- *Faulting completing* on page 2-10

- *Faulting* on page 2-10

- *Killing* on page 2-10

- *Completing* on page 2-10.

## 2.3.1 Stopped

The thread has an invalid PC and it is not fetching instructions. Depending on the thread type, you can cause the thread to move to the Executing state by:

#### DMA manager thread

With **boot\_from\_pc** HIGH and **aresetn** LOW then the DMA manager thread moves to the Executing state after **aresetn** goes HIGH.

### DMA channel thread

Programming the DMA manager thread to execute DMAGO for a DMA channel thread in the Stopped state.

## 2.3.2 Executing

The thread has a valid PC and therefore the DMAC includes the thread when it arbitrates. The thread can then change to one of the following states under the following conditions:

| Stopped             | When the DMA manager thread executes DMAEND.                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cache miss          | When the instruction cache does not contain the next instruction for either the DMA manager thread or the DMA channel thread.                                                                                                                                                                                                                                                                                                                                     |

| Updating PC         | When the DMAC calculates the address of the next access in the cache.                                                                                                                                                                                                                                                                                                                                                                                             |

| Waiting for event   | When a thread executes DMAWFE.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| At barrier          | <ul> <li>When a DMA channel thread either:</li> <li>executes DMARMB, DMAWMB, or DMAFLUSHP</li> <li>updates control registers that affect alignment, see <i>Updating DMA channel control registers during a DMA cycle</i> on page 2-34.</li> </ul>                                                                                                                                                                                                                 |

| Waiting for periph  | eral                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                     | When a DMA channel thread executes DMAWFP.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Killing             | When a DMA channel thread executes DMAKILL.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Faulting completing | g                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Faulting            | <ul> <li>For a DMA channel thread when either:</li> <li>the thread executes an undefined or invalid instruction</li> <li>an AXI bus error occurs during an instruction fetch or data transfer.</li> <li>For the DMA manager thread when either:</li> <li>the thread executes an undefined or invalid instruction</li> <li>an AXI bus error occurs during an instruction fetch.</li> <li>For a DMA channel thread when a watchdog timeout abort occurs.</li> </ul> |

**Completing** When a DMA channel thread executes DMAEND.

#### 2.3.3 Cache miss

The thread is stalled and the DMAC is performing a cache line fill. After it completes the cache fill, the thread returns to the Executing state.

#### 2.3.4 Updating PC

The DMAC is calculating the address of the next access in the cache. After it calculates the PC, the thread returns to the Executing state.

#### 2.3.5 Waiting for event

The thread is stalled and is waiting for the DMAC to execute DMASEV using the corresponding event number. After the corresponding event occurs, the thread returns to the Executing state.

#### 2.3.6 At barrier

A DMA channel thread is stalled and the DMAC is waiting for transactions on the AXI bus to complete. After the AXI transactions complete, the thread returns to the Executing state.

#### 2.3.7 Waiting for peripheral

A DMA channel thread is stalled and the DMAC is waiting for the peripheral to provide the requested data. After the peripheral provides the data, the thread returns to the Executing state.

#### 2.3.8 Faulting completing

A DMA channel thread is waiting for the AXI interface to signal that the outstanding load or store transactions are complete. After the transactions complete, the thread moves to the Faulting state.

#### 2.3.9 Faulting

The thread is stalled indefinitely. The thread moves to the Stopped state when you use the DBGCMD Register to instruct the DMAC to execute DMAKILL for that thread. See *Debug Command Register* on page 3-31.

#### 2.3.10 Killing

A DMA channel thread is waiting for the AXI interface to signal that the outstanding load or store transactions are complete. After the transactions complete, the thread moves to the Stopped state.

#### 2.3.11 Completing

A DMA channel thread is waiting for the AXI interface to signal that the outstanding load or store transactions are complete. After the transactions complete, the thread moves to the Stopped state.

# 2.4 Initializing the DMAC

The DMAC provides several tie-off signals that initialize its operating state when it exits from reset. The following sections describe the initialization of the tie-offs:

- How to set the security state of the DMA manager

- How to set the location of the first instruction for the DMAC to execute

- How to set the security state for the interrupt outputs on page 2-12

- *How to set the security state for a peripheral request interface* on page 2-12.

## 2.4.1 How to set the security state of the DMA manager

•

The **boot\_manager\_ns** signal is the only method to set the security state of the DMA manager. When the DMAC exits from reset, it reads the status of **boot\_manager\_ns** and sets the security of the DMA manager as Table A-11 on page A-9 shows.

\_\_\_\_\_Note \_\_\_\_\_

When set, the security state remains constant until a state transition on **aresetn** resets the DMAC.

See *DMA manager thread is in the Secure state* on page 2-29 and *DMA manager thread is in the Non-secure state* on page 2-29 for a description of how the security state of the DMA manager affects how the DMAC operates.

## 2.4.2 How to set the location of the first instruction for the DMAC to execute

After the DMAC exits from reset, the status of the **boot\_from\_pc** signal controls if the DMAC either:

- Enters the Executing state and:

- Updates the DPC Register using the address that boot\_addr[31:0] provides, see DMA Program Counter Register on page 3-12.

- Fetches and executes the instruction from the address that the DPC Register contains.

#### \_\_\_\_\_Note \_\_\_\_\_

- You must ensure that the state of the boot\_addr[31:0] bus, points to a region in system memory that contains the start address for the DMAC boot program.

- If you set boot\_manager\_ns so that the DMA manager operates in the Non-secure state, the boot program must reside in a non-secure region of memory.

- Enters the Stopped state. You must then provide the first instruction to the DMAC by using one of the slave APB interfaces.

—— Note ———

If **boot\_manager\_ns** was HIGH when the DMAC exited reset then to send instructions you must use the secure APB interface, see *Security usage* on page 2-29.

Table A-11 on page A-9 shows the function of **boot\_from\_pc**.

## 2.4.3 How to set the security state for the interrupt outputs

The DMAC provides the **boot\_irq\_ns[x:0]** signals to enable you to assign each **irq[x]** signal to a security state as Table A-12 on page A-9 shows.

— Note —

When set, the security state of each irq[x] remains constant until a state transition on **aresetn** resets the DMAC.

See *Security usage* on page 2-29 for a description of how the security state of the irq[x] signals affects how the DMAC executes the DMAWFE and DMASEV instructions.

# 2.4.4 How to set the security state for a peripheral request interface

The DMAC provides the **boot\_periph\_ns[x:0]** signals to enable you to assign each peripheral request interface to a security state as Table A-12 on page A-9 shows.

— Note ———

When set, the security state of each peripheral request interface remains constant until a state transition on **aresetn** resets the DMAC.

See *Security usage* on page 2-29 for how the security state of the peripheral request interfaces affects how a DMA channel thread executes the DMAWFP, DMALDP, DMASTP, or DMAFLUSHP instructions.

# 2.5 Using the APB slave interfaces

The APB slave interface connects the DMAC to the APB and enables a microprocessor to access the registers that Chapter 3 *Programmers Model* describes. Using these registers, a microprocessor can:

- access the status of the DMA manager thread

- access the status of the DMA channel threads

- enable or clear interrupts

- enable events

- issue an instruction for the DMAC to execute by programming the following debug registers:

- DBGCMD Register, see Debug Command Register on page 3-31

- DBGINST0 Register, see *Debug Instruction-0 Register* on page 3-32

- DBGINST1 Register, see *Debug Instruction-1 Register* on page 3-33.

## 2.5.1 Issuing instructions to the DMAC using an APB interface

When the DMAC is operating in real-time, you can only issue the following limited subset of instructions:

- DMAGO Starts a DMA transaction using a DMA channel that you specify.

- DMASEV Signals the occurrence of an event, or interrupt, using an event number that you specify.

- DMAKILL Terminates a thread.

You must ensure that you use the appropriate APB interface, depending on the security state in which the **boot\_manager\_ns** initializes the DMAC to operate. For example, if the DMAC is in the Secure state, you must issue the instruction using the secure APB interface, otherwise the DMAC ignores the instruction. You can use the secure APB interface, or the non-secure APB interface, to start or restart a DMA channel when the DMAC is in the Non-secure state.

\_\_\_\_ Note \_\_\_\_\_

Before you can issue instructions using the debug instruction registers or the DBGCMD Register, you must read the DBGSTATUS Register to ensure that debug is idle, otherwise the DMAC ignores the instructions. See *Debug Command Register* on page 3-31 and *Debug Status Register* on page 3-30.

When the DMAC receives an instruction from an APB slave interface, it can take several clock cycles before it can process the instruction, for example, if the pipeline is busy processing another instruction.

\_\_\_\_\_Note \_\_\_\_\_

Prior to issuing DMAGO, you must ensure that the system memory contains a suitable program for the DMAC to execute, starting at the address that the DMAGO specifies.

Example 2-1 on page 2-14 shows the necessary steps to start a DMA channel thread using the debug instruction registers.

#### Example 2-1 Using DMAGO with the debug instruction registers

- 1. Create a program for the DMA channel.

- 2. Store the program in a region of system memory.

Using one of the APB interfaces on the DMAC, program a DMAGO instruction:

- 3. Poll the DBGSTATUS Register to ensure that debug is idle, that is, the dbgstatus bit is 0. See *Debug Status Register* on page 3-30.

- 4. Write to the DBGINST0 Register and enter the:

- Instruction byte 0 encoding for DMAG0.

- Instruction byte 1 encoding for DMAGO.

- Debug thread bit to 0. This selects the DMA manager thread. See *Debug Instruction-0 Register* on page 3-32.

- 5. Write to the DBGINST1 Register with the DMAGO instruction byte [5:2] data, see *Debug Instruction-1 Register* on page 3-33. You must set these four bytes to the address of the first instruction in the program, that was written to system memory in step 2.

Instruct the DMAC to execute the instruction that the debug instruction registers contain by:

6. Writing zero to the DBGCMD Register. The DMAC starts the DMA channel thread and sets the dbgstatus bit to 1. See *Debug Command Register* on page 3-31.

After the DMAC completes execution of the instruction, it clears the dbgstatus bit to 0.

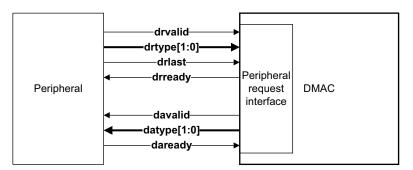

# 2.6 Peripheral request interface

Figure 2-8 shows that the peripheral request interface consists of a peripheral request bus and a DMAC acknowledge bus that use the prefixes:

- dr The peripheral request bus.

- da The DMAC acknowledge bus.

Both buses use the **valid** and **ready** handshake that the AXI protocol describes. For more information on the handshake process, see the *AMBA AXI Protocol v1.0 Specification*.

The peripheral uses drtype[1:0] to either:

- request a single transfer

- request a burst transfer

- acknowledge a flush request.

The DMAC uses datype[1:0] to either:

- signal when it completes the requested single transfer

- signal when it completes the requested burst transfer

- issue a flush request.

– Note

drlast enables the peripheral to notify the DMAC when the last DMA transfer commences.

If you configure the DMAC to provide more than one peripheral request interface, each interface is assigned a unique identifier,  $\_<x>$  where <x> represents the number of the interface. See *Peripheral request interface* on page A-7 for information about how the identifier is appended to the signal name.

The following sections describe:

- Mapping to a DMA channel

- *Handshake rules* on page 2-16

- *Request acceptance capability configuration* on page 2-16

- Peripheral length management on page 2-16

- *DMAC length management* on page 2-18

- *Peripheral request interface timing diagrams* on page 2-20.

# 2.6.1 Mapping to a DMA channel

The DMAC enables you to assign a peripheral request interface to any of the DMA channels. When a DMA channel thread executes DMAWFP, the value programmed in the peripheral [4:0] field specifies the peripheral associated with that DMA channel. See *DMAWFP* on page 4-18.

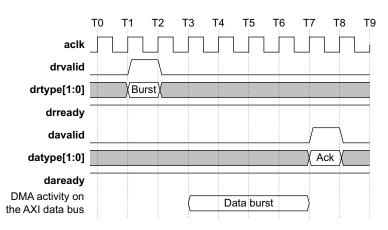

#### 2.6.2 Handshake rules

The DMAC uses the DMA handshake rules that Table 2-2 shows, when a DMA channel thread is active, that is, not in the Stopped state. See *Peripheral request interface timing diagrams* on page 2-20 for more information.

#### Table 2-2 Handshake rules

| Rule | Description <sup>a</sup>                                                                                                                   |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | <b>drvalid</b> can change from LOW to HIGH on any <b>aclk</b> cycle, but it must only change from HIGH to LOW when <b>drready</b> is HIGH. |

| 2    | <ul> <li>drtype can only change when either:</li> <li>drready is HIGH</li> <li>drvalid is LOW.</li> </ul>                                  |

| 3    | <ul> <li>drlast can only change when either:</li> <li>drready is HIGH</li> <li>drvalid is LOW.</li> </ul>                                  |

| 4    | <b>davalid</b> can change from LOW to HIGH on any <b>aclk</b> cycle, but it must only change from HIGH to LOW when <b>daready</b> is HIGH. |

| 5    | <ul> <li>datype can only change when either:</li> <li>daready is HIGH</li> <li>davalid is LOW.</li> </ul>                                  |

a. All signals are only permitted to change state when **aclk** changes state.

#### 2.6.3 Request acceptance capability configuration

During configuration of the DMAC, you can set the number of simultaneous active requests that a DMAC is able to accept, for each peripheral request interface. An active request is where the DMAC has not started the requested AXI data transfers.

The DMAC has a request FIFO, for each peripheral interface, which it uses to capture the requests from a peripheral. The depth of a FIFO depends on the number of simultaneous active requests that the corresponding peripheral request interface is configured to support. To store the state of an active request from the peripheral, the request FIFO uses two bits to store the state of:

- **drtype\_<x>[0]**. Indicates the request type, burst or single.

- **drlast\_<x>**. Indicates if the peripheral is signaling the last data transfer of the DMA transfer.

When a request FIFO is full then the DMAC sets the corresponding **drready\_<x>** LOW to signal that the peripheral must not send requests.

#### 2.6.4 Peripheral length management

The peripheral request interface enables a peripheral to control the quantity of data that a DMA cycle contains, without the DMAC being aware of how many data transfers it contains. The peripheral controls the DMA cycle by using:

- drtype[1:0] to select a single or burst transfer

- **drlast** to notify the DMAC when it commences the final request in the current series.

When the DMAC executes a DMAWFP periph instruction, it halts execution of the thread and waits for the peripheral to send a request. When the peripheral sends the request, the DMAC sets the state of the request flags depending on the state of the following signals:

drtype\_<x>[1:0] The DMAC sets the state of the request\_type flag: drtype\_<x>[1:0]=b00 request\_type<x> = Single. drtype\_<x>[1:0]=b01 request\_type<x> = Burst. drlast\_<x> The DMAC sets the state of the request\_last flag: drlast\_<x>=0 request\_last<x> = 0. drlast\_<x>=1 request\_last<x> = 1. \_\_\_\_\_Note \_\_\_\_\_

If the DMAC executes a DMAWFP single or DMAWFP burst instruction then the DMAC sets:

- the request\_type<x> flag to Single or Burst, respectively

- the request\_last < x > flag to 0.

DMALPFE is an assembler directive which forces the associated DMALPEND instruction to have its nf bit set to 0. This creates a program loop that does not use a loop counter to terminate the loop. The DMAC exits the loop when the request\_last flag is set to 1.

The DMAC conditionally executes the following instructions, depending on the state of the request\_type and request\_last flags:

DMALD, DMAST, DMALPEND

When these instructions use the optional B|S suffix then the DMAC executes a DMANOP if the request\_type flag does not match.

DMALDP<B|S>, DMASTP<B|S>

The DMAC executes a DMANOP if the request\_type flag does not match the B|S suffix.

DMALPEND When the nf bit is 0, the DMAC executes a DMANOP if the request\_last flag is set.

Use the DMALDB, DMALDPB, DMASTB and DMASTPB instructions if you require the DMAC to issue a burst transfer when the DMAC receives a burst request, that is,  $drtype_<x>[1:0] = b01$ . The values in the CCR*n* Register control the amount of data that the DMAC transfers, see *Channel Control Registers* on page 3-25.

Use the DMALDS, DMALDPS, DMASTS and DMASTPS instructions if you require the DMAC to issue a single transfer when the DMAC receives a single request, that is,  $drtype_{x>[1:0]} = b00$ . The DMAC ignores the value of the src\_burst\_len and dst\_burst\_len fields in the CCR*n* Register and sets the arlen[3:0] or awlen[3:0] buses to 0x0.

#### Example program for peripheral length management

Example 2-2 on page 2-18 shows a DMAC program that transfers 64 words from memory to peripheral zero, when the peripheral sends a burst request, that is,  $drtype_{x>[1:0]} = b01$ . When the peripheral sends a single request, that is,  $drtype_{x>[1:0]} = b00$ , then the DMAC program transfers one word from memory to peripheral zero.

To transfer the 64 words, the program instructs the DMAC to perform 16 AXI transfers. Each AXI transfer consists of a 4-beat burst (SB=4, DB=4) that moves a word of data (SS=32, DS=32).

#### Example 2-2 Peripheral length management program

```

# Set up for burst transfers (4-beat burst, so SB4 and DB4), (word data width, so SS32 and DS32)

DMAMOV CCR SB4 SS32 DB4 DS32

DMAMOV SAR ...

DMAMOV DAR ...

# Initialize peripheral '0'

DMAFLUSHP PØ

# Perform peripheral transfers

# Outer loop - DMAC responds to peripheral requests until peripheral sets drlast_0 = 1

DMALPFE

# Wait for request, DMAC sets request_type0 flag depending on the request type it receives

DMAWFP 0, periph

# Set up loop for burst request: first 15 of 16 sets of transactions

# Note: B suffix - conditionally executed only if request_type0 flag = Burst

DMALP 15

DMALDB

DMASTB

# Only loop back if servicing a burst, otherwise treat as a NOP

DMALPENDB

# Perform final transaction (16 of 16). Send the peripheral acknowledgement of burst request completion

DMALDB

DMASTPB P0

# Perform transaction if the peripheral signals a single request

# Note: S suffix - conditionally executed only if request_type0 flag = Single

DMALDS

DMASTPS P0

# Exit loop if DMAC receives the last request, that is, drlast_0 = 1

DMALPEND

DMAEND

```

In Example 2-2, the program shows the use of the:

- DMAWFP periph instruction. The DMAC waits for either a burst or single request from the peripheral.

- DMASTPB and DMASTPS instructions. The DMAC informs the peripheral when a transfer is complete.

#### 2.6.5 DMAC length management

DMAC length management is when the DMAC controls the total amount of data to transfer. The peripheral uses the peripheral request interface to notify the DMAC when it requires the DMAC to transfer data to or from the peripheral. The DMA channel thread controls how the DMAC responds to the peripheral requests.

The following constraints apply to DMAC length management:

• The total quantity of data for all the single requests from a peripheral must be less than the quantity of data for a burst request for that peripheral.

\_\_\_\_\_Note \_\_\_\_\_