# ASB Example AMBA<sup>®</sup> SYstem Technical Reference Manual

Copyright © 1998-1999 ARM Limited. All rights reserved. ARM DDI 0138D

## ASB Example AMBA SYstem Technical Reference Manual

Copyright © 1998-1999 ARM Limited. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

**Change History**

| Date         | Issue | Confidentiality  | Change                                  |

|--------------|-------|------------------|-----------------------------------------|

| October 1998 | А     | Non-Confidential | First release.                          |

| July 1999    | B & C | Non-Confidential | Note: Issues B and C were not released. |

| August 1999  | D     | Non-Confidential | Name change to ASB EASY.                |

#### **Proprietary Notice**

Words and logos marked with  ${}^{\otimes}$  or  ${}^{\mathbb{M}}$  are registered trademarks or trademarks of ARM Limited in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

## Contents ASB Example AMBA SYstem Technical Reference Manual

|           | Prefac | ce de la constante de la consta |      |

|-----------|--------|-----------------------------------------------------------------------------------------------------------------|------|

|           |        | About this manual                                                                                               |      |

|           |        | Feedback                                                                                                        | x    |

| Chapter 1 | Introd | uction                                                                                                          |      |

|           | 1.1    | Overview                                                                                                        | 1-2  |

| Chapter 2 | Micro  | controller                                                                                                      |      |

|           | 2.1    | Functional overview                                                                                             | 2-2  |

|           | 2.2    | The AMBA system components                                                                                      | 2-3  |

|           | 2.3    | Reference peripherals                                                                                           | 2-5  |

|           | 2.4    | Example components                                                                                              | 2-8  |

|           | 2.5    | System test methodology                                                                                         | 2-9  |

| Chapter 3 |        | <i>l</i> odules                                                                                                 |      |

| •         | 3.1    | APB bridge                                                                                                      | 3-2  |

|           | 3.2    | Arbiter                                                                                                         |      |

|           | 3.3    | Decoder                                                                                                         | 3-26 |

|           | 3.4    | Reset controller 3                                                                                              | 3-43 |

|           | 3.5    | Static memory interface 3                                                                                       | 3-49 |

|           | 3.6<br>3.7 | Example system external memory    |      |

|-----------|------------|-----------------------------------|------|

|           | 3.8        | AMBA ARM7TDMI interface           |      |

| Chapter 4 | APB        | Modules                           |      |

|           | 4.1        | Interrupt controller              | 4-2  |

|           | 4.2        | Remap and pause controller        | 4-15 |

|           | 4.3        | Timer                             | 4-24 |

| Chapter 5 | Test       | Interface Driver                  |      |

| -         | 5.1        | Introduction                      | 5-2  |

|           | 5.2        | TICBOX usage                      |      |

|           | 5.3        | TICTalk command language          | 5-6  |

| Chapter 6 | Desi       | gner's Guide                      |      |

| -         | 6.1        | Adding bus masters                | 6-2  |

|           | 6.2        | Adding ASB slaves                 |      |

|           | 6.3        | Adding APB peripherals            |      |

|           | 6.4        | Choosing a decoder implementation | 6-5  |

## Preface

This preface introduces the *ASB Example AMBA SYstem Techincal Reference Manual*. It contains the following sections:

- About this manual on page vi

- *Feedback* on page x.

## About this manual

This document is a comprehensive manual for the behavioral HDL model of the ASB Example AMBA SYstem (EASY) It gives detailed information about the function of the whole system, each module in the system, and describes how to design a new system module.

This document refers to the Advanced System Bus (ASB). For information on the Advanced High-performance Bus (AHB) refer to the *AHB Example AMBA SYstem Technical Reference Manual*.

## Using this manual

This manual is organized into the following chapters:

### **Chapter 1** Introduction

Read this chapter for an introduction to the ASB Example AMBA SYstem (EASY).

### Chapter 2 Microcontroller

Read this chapter for a description the microcontroller, which is the main unit of the EASY system.

### Chapter 3 ASB Modules

Read this chapter for a description of the data sheets for the modules that are connected to the *Advanced System Bus* (ASB)

## Chapter 4 APB Modules

Read this chapter for a description of the modules that comprise the *Advanced Peripheral Bus* (APB).

### Chapter 5 Test Interface Driver

Read this chapter for a description of the use of the external AMBA Test Interface Driver module. It includes a description of the TICTalk command language.

### Chapter 6 Designer's Guide

Read this chapter for a basic look at adding new modules to the EASY microcontroller.

## Conventions

Conventions that this manual can use are described in:

• *Typographical* on page vii

- Timing diagrams

- Signals on page viii

- *Numbering* on page ix.

## Typographical

The typographical conventions are:

| italic            | Highlights important notes, introduces special terminology, denotes internal cross-references, and citations.                           |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| bold              | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.   |

| monospace         | Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.                             |

| <u>mono</u> space | Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name. |

| monospace italic  | Denotes arguments to monospace text where the argument is to be<br>replaced by a specific value.                                        |

| monospace bold    | Denotes language keywords when used outside example code.                                                                               |

## **Timing diagrams**

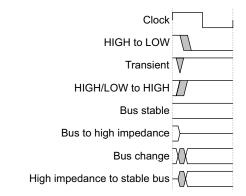

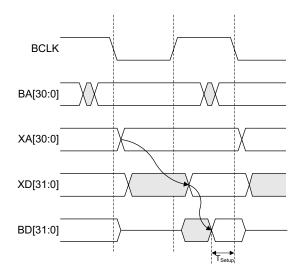

The figure named *Key to timing diagram conventions* on page viii explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

## Key to timing diagram conventions

Single-bit signals are sometimes shown as HIGH and LOW at the same time and they look similar to the bus change shown in *Key to timing diagram conventions*. If a single-bit signal is shown like this then its value does not affect the accompanying description.

## Signals

The signal conventions are:

| Signal level | <ul> <li>The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:</li> <li>HIGH for active-HIGH signals</li> <li>LOW for active-LOW signals.</li> </ul> |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lower-case n | At the start or end of a signal name denotes an active-LOW signal.                                                                                                                                         |

| Prefix A     | Denotes global Advanced eXtensible Interface (AXI) signals.                                                                                                                                                |

| Prefix AR    | Denotes AXI read address channel signals.                                                                                                                                                                  |

| Prefix AW    | Denotes AXI write address channel signals.                                                                                                                                                                 |

| Prefix B     | Denotes AXI write response channel signals.                                                                                                                                                                |

| Prefix C     | Denotes AXI low-power interface signals.                                                                                                                                                                   |

| Prefix H     | Denotes Advanced High-performance Bus (AHB) signals.                                                                                                                                                       |

| Prefix P     | Denotes Advanced Peripheral Bus (APB) signals.                                                                                                                                                             |

| Prefix R     | Denotes AXI read data channel signals.                                                                                                                                                                     |

**Prefix W** Denotes AXI write data channel signals.

## Numbering

The numbering convention is:

•

## <size in bits>'<base><number>

This is a Verilog method of abbreviating constant numbers. For example:

- 'h7B4 is an unsized hexadecimal value.

- 'o7654 is an unsized octal value.

- 8'd9 is an eight-bit wide decimal value of 9.

- 8'h3F is an eight-bit wide hexadecimal value of 0x3F. This is equivalent to b00111111.

- 8'b1111 is an eight-bit wide binary value of b00001111.

## Additional reading

This section lists publications by ARM and by third parties.

See http://infocenter.arm.com/help/index.jsp for access to ARM documentation.

## **ARM publications**

This manual contains information that is specific to the Abbreviated device name AMBA SYstem (EASY). See the following documents for other relevant information:

- AMBA<sup>®</sup> Specification (Rev 2.0) (ARM IHI 0011)

- ARM Architecture Reference Manual (ARM DDI 0100)

- ARM7TDMI Data Sheet (ARM DDI 0029)

- AMBA ARM7TDMI Interface Data Sheet ((ARM DDI 045)

- Example AMBA SYstem User Guide (ARM DUI 0092)

- AHB Example AMBA SYstem Technical Reference Manual (ARM DDI 0170).

## Other publications

This section lists relevant documents published by third parties:

• IEEE 1149.1 JTAG standard

## Feedback

ARM welcomes feedback on the ASB Example AMBA SYstem and its documentation.

## Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- the product name

- a concise explanation.

## Feedback on this manual

If you have any comments on this manual, send an e-mail to errata@arm.com. Give:

- the title

- the number

- the relevant page number(s) to which your comments apply

- a concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

## Chapter 1 Introduction

This chapter introduces the ASB Example AMBA SYstem (EASY). it contains the following:

• *Overview* on page 1-2.

## 1.1 Overview

The EASY microcontroller comprises the building blocks needed to create an example system based on the low-power, generic design methodology of the *Advanced Microcontroller Bus Architecture* (AMBA).

The EASY microcontroller:

- enables custom devices to be developed in very short design cycles

- allows the resulting sub-components to be easily re-used in future designs.

— Note ——

This document refers to the *Advanced System Bus* (ASB).For information on the Advanced High-performance Bus (AHB) refer to the AHB Example AMBA SYstem Technical Reference Manual.

## 1.1.1 EASY system blocks

The example design provides all the system modules needed to manage an AMBA system:

- reset controller

- arbiter

- decoder.

These system modules control the various aspects of the ASB.

### 1.1.2 EASY components

The example design contains:

- Two bus masters, the ASB, and the *Advanced Peripheral Bus*.

- The ARM processor, to allow execution of the ARM code.

- The *Test Interface Controller (TIC)*, to allow external control of the ASB during system test.

- A minimum set of basic microcontroller peripherals. These are supported, and are implemented as low-power designs on the APB. They include:

- an interrupt controller

- a remap and pause controller

- a 16-bit timer module.

- The Example *Static Memory Interface* (SMI). This demonstrates the minimum requirements for an *External Bus Interface* (EBI).

- A 1KB block of internal memory.

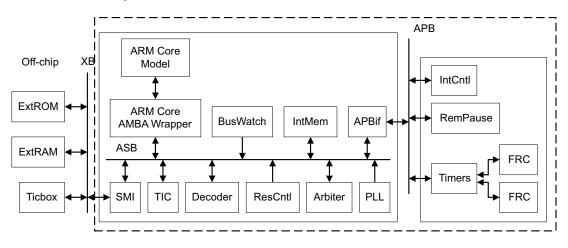

The EASY system consists of a microcontroller with some external memory as shown in Figure 1-1.

Figure 1-1 EASY system diagram

Introduction

## Chapter 2 Microcontroller

The microcontroller is the main unit of the EASY system. This chapter describes the microcontroller under the headings:

- *Functional overview* on page 2-2

- The AMBA system components on page 2-3

- *Reference peripherals* on page 2-5

- *Example components* on page 2-8

- System test methodology on page 2-9.

## 2.1 Functional overview

The modules of the EASY microcontroller are grouped in five classes:

- AMBA system components These are used to control the general operation of the system.

- **Peripherals** Low power peripherals, which are connected to the peripheral bus.

#### **Example components**

Demonstration parts that are only simulation models.

#### System test methodology

Modules used for testing the system.

**Processor core** The ARM processor core that is built into the EASY microcontroller.

With the exception of the processor core the above modules are fully described in this chapter. For details of the processor core, please refer to the relevant documentation.

## 2.2 The AMBA system components

The Advanced Microcontroller Bus Architecture (AMBA) system comprises:

- reset controller

- arbiter

- decoder

- Advanced System Bus (ASB) to Advanced Peripheral Bus (APB) Bridge.

The functions of each component are described below.

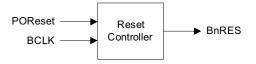

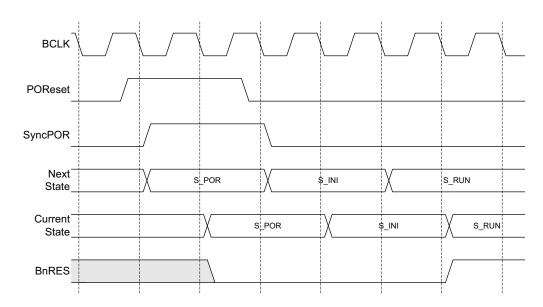

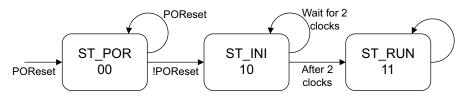

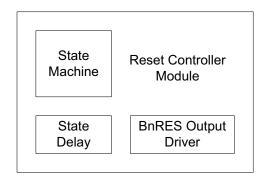

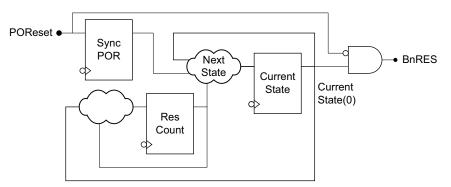

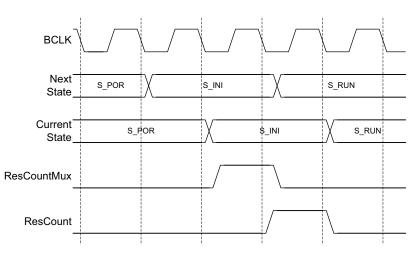

## 2.2.1 Reset controller

The reset controller consists of a state machine which controls the **BnRES** signal. This signal indicates the current reset state of the AMBA bus and is used by all the other elements in the EASY microcontroller, primarily for power-on initialization.

—— Note ———

All other reset modes, such as standby or warm reset, must be implemented separately.

## 2.2.2 Arbiter

The arbiter provides arbitration between bus masters competing for access to the ASB. Although there are only two bus masters in the EASY microcontroller (the ARM and the *Test Interface Controller* (TIC), the arbitr has provision for up to four masters. To extend the number of masters refer to *Adding bus masters* on page 6-2. The arbitration is currently assigned with a simple priority system, with the TIC as the highest priority, and the processor as the lowest reset default. The arbitration scheme is not defined in the *AMBA Specification* and can be dependent on implementation.

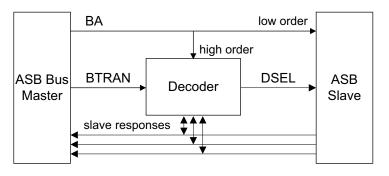

## 2.2.3 Decoder

The decoder manages all transfers on the ASB bus. Each bus transfer requires three components to act:

- a bus master to start the transfer

- the decoder to control the operation of the transfer

- a bus slave to accept a write transfer or control a read transfer.

The functions of these components are:

Bus Master This initiates a read or write transfer by driving BTRAN[1:0] (transfer type) and BA[31:0] (AMBA address bus) and control signals. This component drives BD[31:0] for a write transfer.

- DecoderBTRAN is used to determine how the transfer should proceed, whether a<br/>slave should be selected, if and in which state slave responses (BWAIT,<br/>BERROR and BLAST) should be driven. The high order bits of BA are<br/>used to generate the corresponding slave select line (DSEL).

- **Bus Slave** If selected, the slave will drive the slave responses. This component drives **BD[31:0]** for a write transfer.

Each transfer takes one or more cycles of the system clock (**BCLK**). The last cycle of each transfer occurs when **BWAIT** is driven LOW by the decoder or slave.

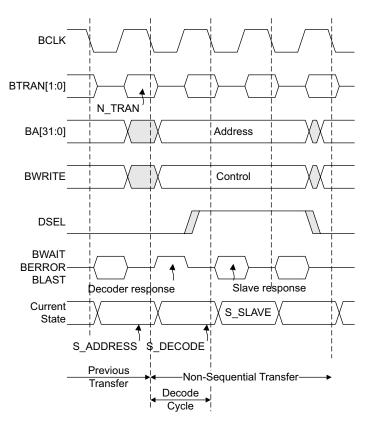

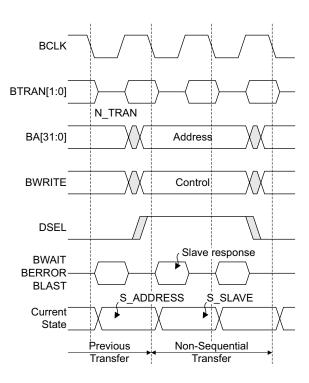

#### Figure 2-1 The role of the decoder in the AMBA bus

The EASY system provides a configurable decoder block, with or without decode cycles. A decode cycle can be inserted to improve the performance of the system.

—— Note ——

In some systems, typically those with a low clock frequency, transfers may occur without the addition of a decode cycle.

For more information on ASB transfers, see the AMBA Specification.

## 2.2.4 ASB to APB bridge

The ASB to APB bridge interface is an ASB slave. When accessed (in normal operation or system test) it initiates an access to the APB. All APB accesses are of the same duration (two **BCLK** cycles in the EASY). They also have their width fixed to one word, which means it is not possible to write only an 8-bit section of a 32-bit APB register. APB peripherals do not need a **BCLK** input as the APB access is timed with a strobe signal generated by the ASB to APB bridge interface. This makes APB peripherals low power consumption parts, because they are only strobed when accessed.

For more information on the APB bus refer to the AMBA Specification.

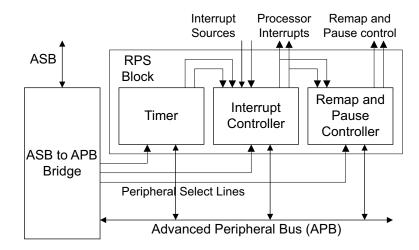

## 2.3 Reference peripherals

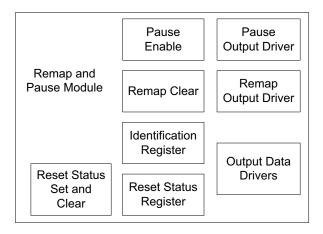

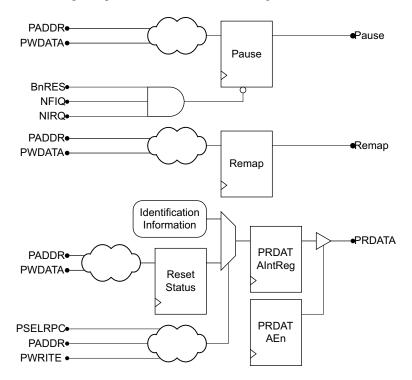

Figure 2-2 shows how the reference peripherals are interconnected within the *Reference Peripherals Specification* (RPS) block, and how they are connected to the bridge.

### Figure 2-2 Block diagram of the RPS block and bridge

The base addresses of each of the peripherals (timer, interrupt controller and remap and pause controller) are defined in the ASB to APB bridge interface (which selects the peripheral according to its base address). The whole APB address range is defined in the decoder (which selects the ASB to APB bridge interface according to its base address).

These base addresses can be implementation specific. The peripherals standard specifies only the register offsets (from an unspecified base address), register bit meaning and minimum supported function. Table 2-1 shows the three bases and their current addresses in the EASY microcontroller.

| Peripheral                 | EASY Base Address |

|----------------------------|-------------------|

| Interrupt controller       | 0x80000000        |

| Timer                      | 0x84000000        |

| Remap and pause controller | 0x88000000        |

### Table 2-1 Peripherals base addresses

|       | Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                     |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

|       | When writing software or test patterns to run on the system, the absolute her<br>must not be used within the code. Instead, define the base addresses in a head<br>use the offset to this base address.                                                                                                                                                                                                                                                                             |                                     |

|       | The APB data bus is split into two separate directions:                                                                                                                                                                                                                                                                                                                                                                                                                             |                                     |

|       | read (PRDATA) Data travels from the peripherals to the bridge.                                                                                                                                                                                                                                                                                                                                                                                                                      |                                     |

|       | write (PWDATA) Data travels from the bridge to the peripherals.                                                                                                                                                                                                                                                                                                                                                                                                                     |                                     |

|       | This simplifies driving the buses because turnaround time between the perip<br>bridge is avoided.                                                                                                                                                                                                                                                                                                                                                                                   | herals and                          |

|       | In the default system, because <b>PWDATA</b> is the only master on the bus, it is continuously by the bridge. <b>PRDATA</b> is tristated by all peripherals on the bronly driven when they are selected by the bridge during APB read transfers                                                                                                                                                                                                                                     | ous, and is                         |

|       | It is possible to combine these two buses into a single bidirectional bus, but p<br>must be taken to ensure that there is no bus clash between the bridge and the                                                                                                                                                                                                                                                                                                                   |                                     |

|       | Inside the RPS module is an APB bus keeper model for simulation purposes<br>not synthesizable). Bus keepers must be included on a real implementation<br><b>PRDATA</b> from floating, since a given peripheral might not drive all the dat<br>Although bus keepers are important to ensure low power consumption on the<br>data bus, they should not be relied upon to hold valid values. In designs based<br>bus keepers should be instantiated from the appropriate cell library. | to prevent<br>a bits.<br>e APB read |

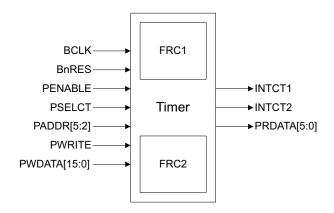

| Timer |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                     |

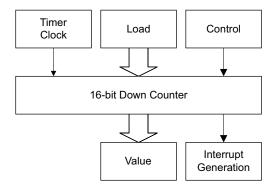

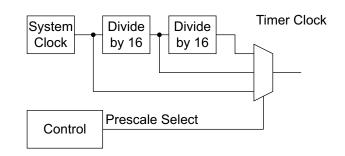

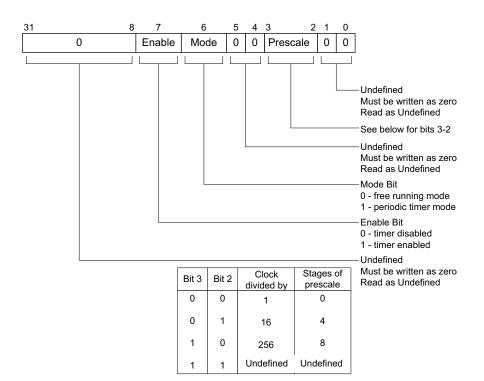

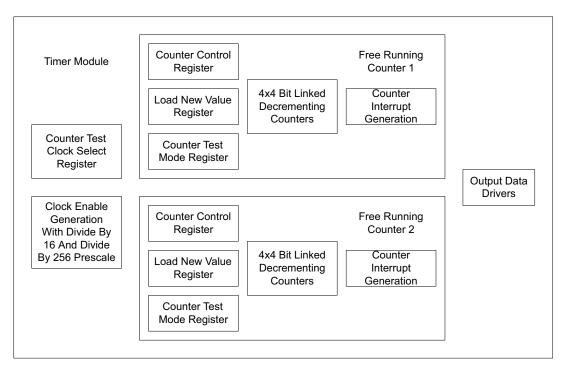

|       | The timer consists of two 16-bit periodic/free running down counters, a cloc (divide by 1, 16 or 256) and a test veneer. When the counters underflow (pa value and reloading) they can generate <i>Interrupt Requests</i> (IRQs) which are to the interrupt controller. Both counter values can be loaded, read and cont through addressable registers.                                                                                                                             | connected                           |

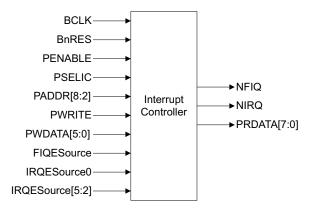

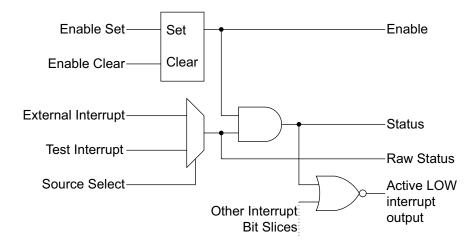

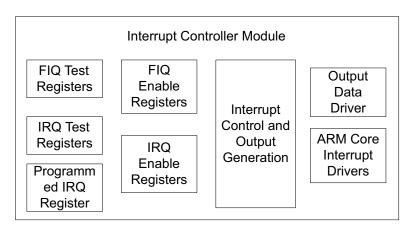

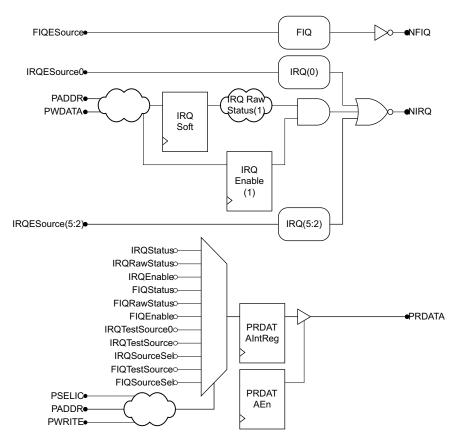

## 2.3.2 Interrupt controller

The interrupt controller contains a set of registers for using six IRQ sources and one *Fast Interrupt Request* (FIQ) source. These have the following functions:

- to enable or disable specific interrupt sources from triggering the ARM NIRQ or NFIQ interrupt lines

- to read the status of all interrupt sources at the inputs of the interrupt controller

2.3.1

- to read the status of the interrupt sources enabled to trigger the ARM interrupt lines

- to generate a software-triggered NIRQ signal to the ARM processor

- to isolate the interrupt controller for test.

The number of IRQ sources can easily be extended by increasing the number of IRQ registers.

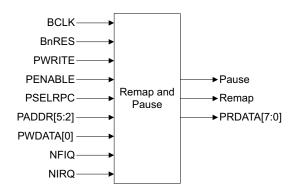

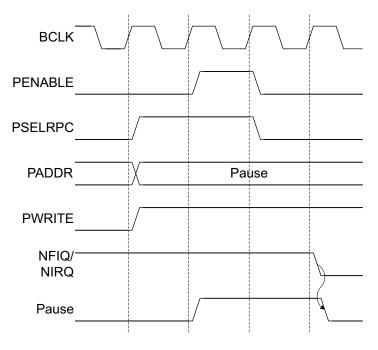

## 2.3.3 Remap and pause controller

The remap and pause controller has three functions:

- Reset status. This enables software to determine whether the last reset was a Power On Reset. (POR) or a soft reset. The latter function is redundant in the EASY microcontroller, since it does not have a soft reset. It is implemented only as an example for systems that might provide a soft reset state.

- Remap memory. On reset the internal RAM is mapped out and bank 7 of the external memory is mapped into location 0x00000000 which is the boot location for the ARM processor. The reset memory map is cancelled by writing to a register in this peripheral.

- Pause mode. The EASY microcontroller only supports one simple power saving mode, called Pause. This halts all bus activity (but not the system clock) and waits for an interrupt signal from the interrupt controller before restarting the system.

The remap and pause controller also contains an ID register which is currently only a single bit. This block can be extended in many ways including support for software-generated resets, more sophisticated power saving modes and more detailed ID information.

## 2.4 Example components

The example components include the internal memory and the *Static Memory Interface* (SMI).

Typically these blocks must be re-implemented according to the specific system requirements of the microcontroller being developed.

## 2.4.1 Internal memory

The internal memory is a very basic behavioral model of 1KB of zero wait state static memory, which is not synthesizable. The size of the memory can be extended by altering the MemSize setting in the HDL file behavioural/IntMem. If this is done the decoder must also be altered. Refer to *Choosing a decoder implementation* on page 6-5).

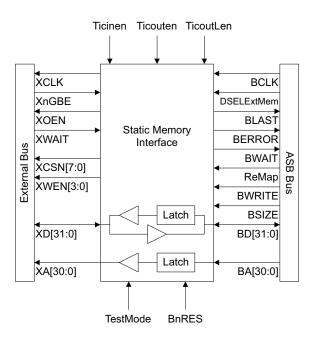

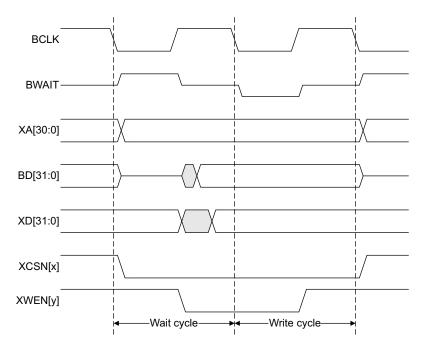

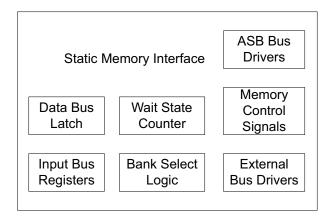

## 2.4.2 Static memory interface

The SMI is a 32-bit *External Bus Interface* (EBI) that can connect up to 2GB of zero to four wait state *Static Random Access Memory* (SRAM) to the EASY microcontroller. However, the number of wait states is set as a constant in the HDL (before synthesis), and is set for all eight banks of SRAM. The Example SMI also supports four signals from the TIC. These override the SMI's normal operation during a system test and directly control the tristate drivers and latches on the **XD** and **BD** buses.

## 2.5 System test methodology

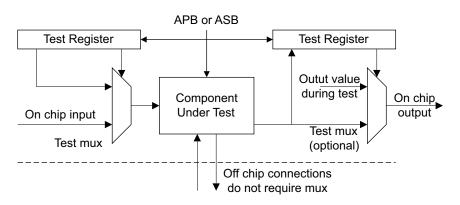

Each ASB slave, ASB master and APB peripheral should be tested in complete isolation. This means that components must be designed with test veneers that allow non-bus signals to be controlled and observed. When a component is tested, a special test bit is set. This test bit switches these multiplexed signals to test registers (accessible via the ASB), which effectively isolates each component from the rest of the system. Test vectors should be written to test the component in isolation, making as few assumptions about the rest of the system as possible.

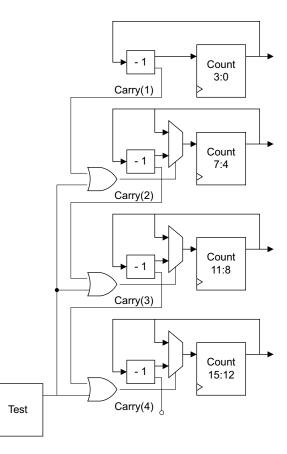

Figure 2-3 Simple test veneer example

A good example of this approach is provided by the test veneer for the ARM processor, which is described in the *AMBA ARM7TDMI Interface Data Sheet*. This approach is also used to test the peripherals on the APB bus.

Under normal conditions, when the TIC is not in use, the current bus master performs transfers to and from any one of the following slaves:

- internal memory

- ASB to APB bridge interface (to access the peripherals)

- external bus interface.

However, when test mode is entered, and the TIC is the current master, the following slaves can be accessed:

- internal memory

- ASB to APB bridge interface (to access the peripherals)

- ARM bus master (test veneer).

Bus masters can become slaves in the test mode. The SMI *cannot* be tested via the TIC. This is due to the method used to provide the test access to the ASB. During TIC testing, the normal function of the SMI is overridden, and it becomes a bidirectional channel between **TBUS** and **BD**. This means that during TIC testing the SMI cannot function as a slave.

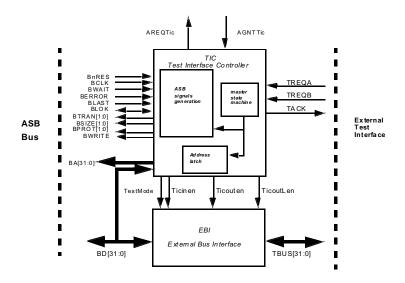

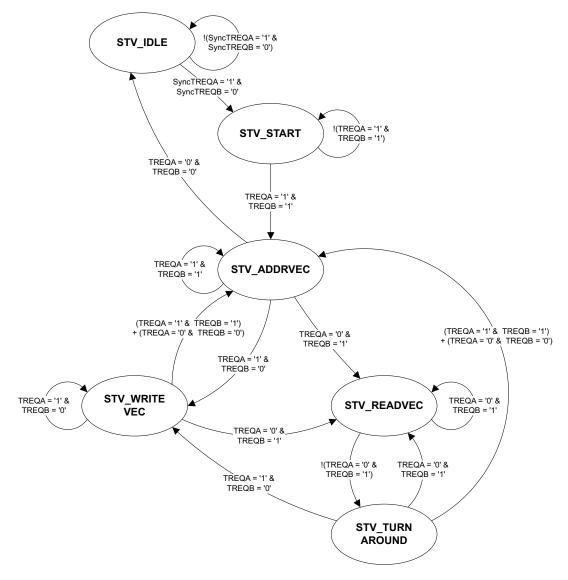

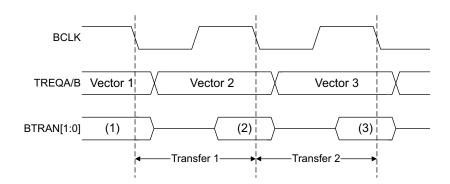

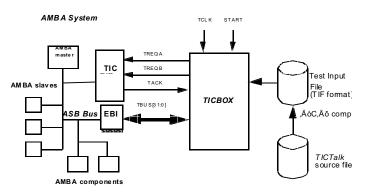

The EBI cannot be tested via the TIC because of the way test access is provided to the ASB bus. The TIC is a state machine driven by the test request inputs (**TREQA** and **TREQB**). It also contains a latch that allows it to read address information from the test bus (**TBUS**) and drive it onto **BA**. However, it cannot drive **BD**. Instead, it overrides the normal function of the EBI, forcing it to provide a 32-bit, bidirectional channel between **TBUS** and **BD**. Thus in test mode the EBI cannot function as a slave.

**TBUS** must be a 32-bit channel. Thus in a system which only supports a 16-bit or 8-bit external data bus, additional external pins such as external address lines must be forced into a special test mode in order to supply the full 32-bit bidirectional channel required.

For more information on:

– Note –

- the test interface, see the AMBA Specification

- on applying test vectors to an EASY-based microcontroller, see the *EASY User Guide*.

## Chapter 3 ASB Modules

This chapter describes the data sheets for the modules that are connected to the *Advanced System Bus* (ASB). It contains the following:

- *APB bridge* on page 3-2

- Arbiter on page 3-17

- *Decoder* on page 3-26

- *Reset controller* on page 3-43

- Static memory interface on page 3-49

- *Test interface controller* on page 3-62

- AMBA ARM7TDMI interface on page 3-71.

## 3.1 APB bridge

The APB bridge provides an interface between the ASB and the *Advanced Peripheral Bus* (APB). It continues the pipelining of the ASB by inserting wait cycles on the ASB only when they are needed. It inserts them for burst transfers or read transfers when the ASB must wait for the APB.

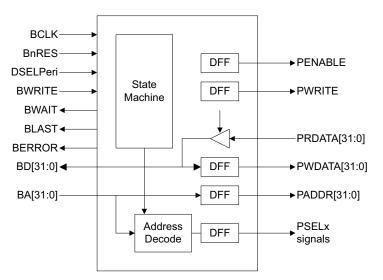

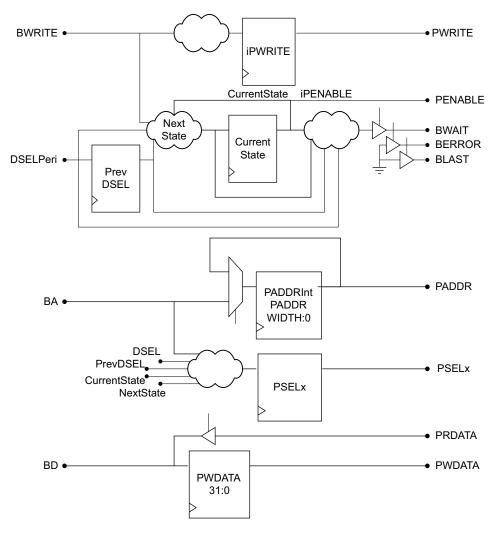

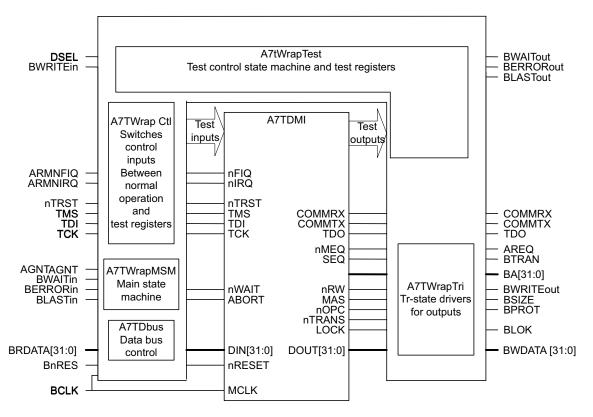

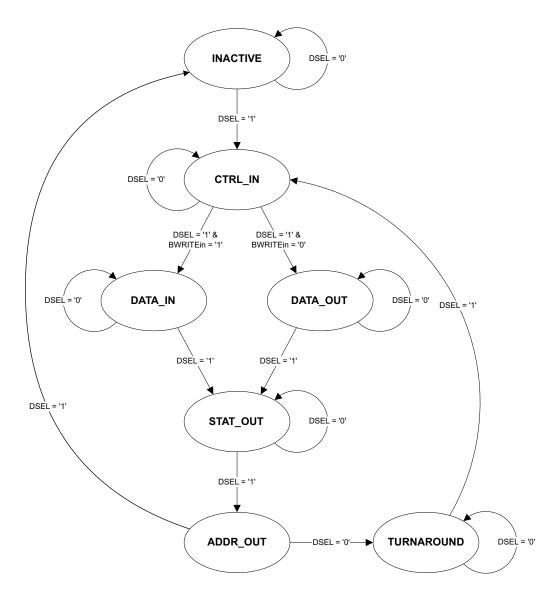

#### Figure 3-1 Block diagram of bridge module

The implementation of this block contains:

- a state machine, which is independent of the device memory map

- ASB address, and data bus latching

- combinatorial address decoding logic to produce **PSELx** signals.

To add new peripherals, or alter the system memory map only the address decode section needs to be modified.

## 3.1.1 Hardware interface and signal description

This module converts ASB transactions to APB transactions.

## Table 3-1 Signal descriptions for bridge module

| Name          | Туре         | Description                                                                                                                                                                                                                                                                                           |

|---------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BCLK          | Input        | This clock times all bus transfers.                                                                                                                                                                                                                                                                   |

| BnRES         | Input        | The bus reset signal is active LOW, and is used to reset the system and the bus.                                                                                                                                                                                                                      |

| BA[31:0]      | Input        | The system address bus, which is driven by the current bus master.                                                                                                                                                                                                                                    |

| BWRITE        | Input        | When HIGH this signal indicates a write transfer, when LOW, a read transfer. This signal is driven by the active bus master.                                                                                                                                                                          |

| DSELPeri      | Input        | This signal indicates that the peripheral bus controller has been selected. It becomes valid during the <b>BCLK</b> HIGH phase before the data transfer, and remains active until the last <b>BCLK</b> HIGH phase of the transfer.                                                                    |

| BD[31:0]      | Input/Output | This is the bidirectional system data bus. The data bus is driven by the current bus master during write transfers, and by this block during read transfers from peripherals.                                                                                                                         |

| BWAIT         | Output       | This signal is driven by the selected bus slave during reads and writes to indicate whether the current transfer may complete. When selected, the peripheral bus controller drives this signal in the LOW phase of <b>BCLK</b> , and it is valid set up to the rising edge of <b>BCLK</b> .           |

| BERROR        | Output       | A transfer error is indicated by the selected bus slave using the <b>BERROR</b> signal.<br>This signal is not used by the bridge, so when selected, it is always driven LOW in<br>the LOW phase of <b>BCLK</b> . It is valid set up to the rising edge of <b>BCLK</b> .                               |

| BLAST         | Output       | This signal is driven by the selected bus slave to indicate if the current transfer should be the last of a burst sequence. This signal is not used by the bridge, so wher selected, it is always driven LOW in the LOW phase of <b>BCLK</b> . It is valid set up to the rising edge of <b>BCLK</b> . |

| PRDATA[31:0]  | Input        | The peripheral read data bus is driven by the selected peripheral bus slave during read cycles (when <b>PWRITE</b> is LOW).                                                                                                                                                                           |

| PWDATA [31:0] | Output       | The peripheral write data bus is continuously driven by this block, changing during write cycles (when <b>PWRITE</b> is HIGH).                                                                                                                                                                        |

| PENABLE       | Output       | This enable signal is used to time all accesses on the peripheral bus. <b>PENABLE</b> goes HIGH on the second clock rising edge of the transfer, and LOW on the third (last) rising clock edge of the transfer.                                                                                       |

## Table 3-1 Signal descriptions for bridge module (continued)

| Name        | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PSELx       | Output | There is one of these signals for each APB peripheral present in the system. The signal indicates that the slave device is selected, and that a data transfer is required. This signal has the same timing as the peripheral address bus. It becomes HIGH at the same time as <b>PADDR</b> , but will be set LOW at the end of the transfer.                                                                                   |

| PADDR[31:0] | Output | This is the APB address bus, which may be up to 32 bits wide and is used by individual peripherals for decoding register accesses to that peripheral. The address becomes valid after the first rising edge of the clock at the start of the transfer. If there is a following APB transfer, then the address will change to the new value, otherwise it will hold its current value until the start of the next APB transfer. |

| PWRITE      | Output | This signal indicates a write to a peripheral when HIGH, and a read from a peripheral when LOW.<br>It has the same timing as the peripheral address bus.                                                                                                                                                                                                                                                                       |

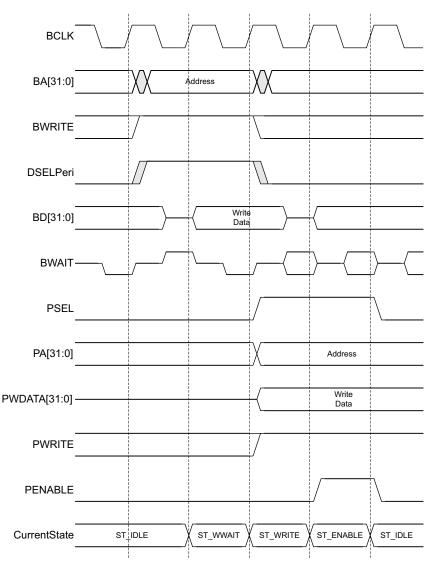

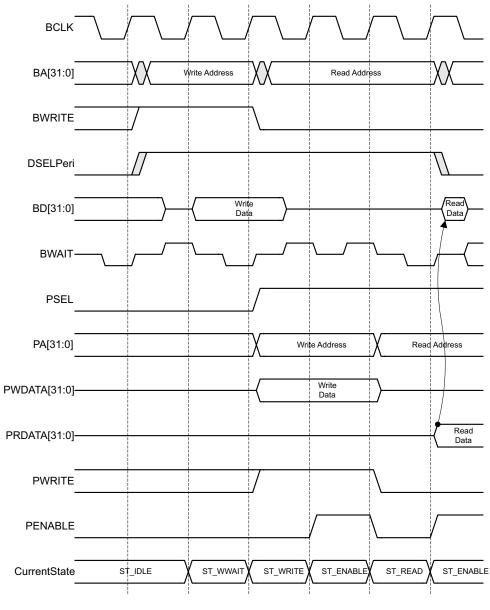

The timing and inputs and outputs of the module are shown in Figure 3-2 on page 3-5, Figure 3-3 on page 3-6 and Figure 3-4 on page 3-7.

Figure 3-2 on page 3-5 shows a single write cycle. There are four cycles between the start of the transfer on the ASB and the end of the transfer on the APB, but only one wait state is inserted on **BWAIT**. The write data (on **BD**) is sampled on the **BCLK** rising edge after it becomes valid.

## Figure 3-2 APB write cycle

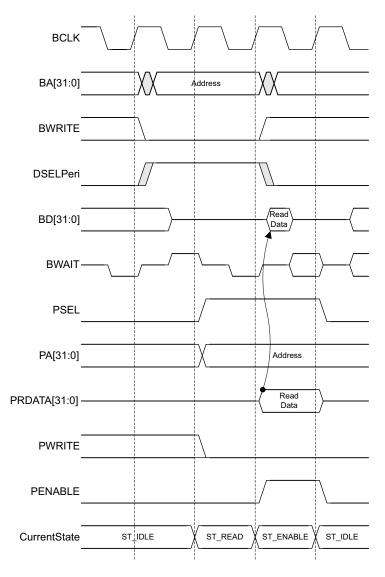

Figure 3-3 on page 3-6 shows a single APB read transfer. There are three cycles between the start of the transfer on the ASB and the end of the transfer on the APB, but only one wait state is inserted on **BWAIT**. The APB peripheral read data (**PRDATA**) is generated on the rising edge of **BCLK**, and sampled on the next falling edge of **BCLK**

by the ARM core. If the APB peripherals used cannot generate **PRDATA** early enough to be sampled on the falling edge, then the bridge must be modified to insert an extra ASB wait state.

## Figure 3-3 APB read cycle

Figure 3-4 on page 3-7 shows an APB write followed by an APB read. Two wait states are added before the APB read, this allows the APB write transfer time to end before the read starts.

Figure 3-4 APB burst cycle

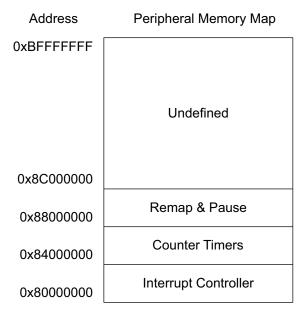

## 3.1.2 Peripheral memory map

The bridge controls the memory map for the peripherals, and generates a select signal for each peripheral. The default system memory map is shown in Figure 3-5.

Figure 3-5 Peripheral memory map

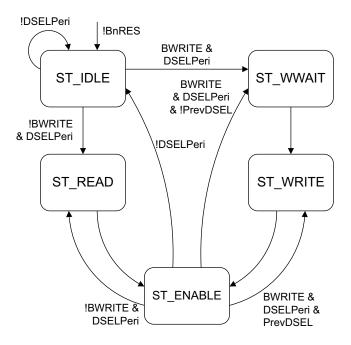

## 3.1.3 Function and operation of block

The APB bridge responds to transaction requests from the currently enabled ASB master. The ASB transactions are converted into APB transactions. The state machine, shown in Figure 3-6 on page 3-9, controls:

- the ASB transactions with the slave response signals

- the register enables for the **PADDR** and **PWDATA** buses

- the tristate driver controls for the **BD** bus.

It also produces the **PENABLE** signal. This design uses the **DSELPeri** signal from a centralized decoder to select the peripheral bus controller as an ASB slave.

The individual **PSELx** signals are decoded from **BA**, using the state machine to enable the outputs while the APB transaction is being performed.

If an undefined location is accessed, operation of the system continues as normal, but no peripherals are selected.

Figure 3-6 State machine for APB controller

## ST\_IDLE

The **ST\_IDLE** state is entered from:

- reset, when the system is initialized

- **ST\_IDLE** when there are no peripheral transactions being performed.

The APB buses and **PWRITE** are driven with the last values they had, and the **PSEL** and **PENABLE** lines are all set to zero.

The next state is:

- ST\_READ for a read transfer, when DSELPeri is HIGH and BWRITE is LOW

- ST\_WWAIT for a write transfer, when both DSELPeri and BWRITE are HIGH.

A wait state (setting **BWAIT** HIGH) is always inserted on exit from **ST\_IDLE** when **DSELPeri** is HIGH.

## ST\_READ

The **ST\_READ**state is entered from:

- **ST\_IDLE** during a nonsequential read cycle

- **ST\_ENABLE** during a sequential read cycle.

The address is decoded and driven onto **PADDR**, the relevant **PSEL** line is driven, and **PWRITE** is driven LOW.

The next state will always be ST\_ENABLE.

## ST\_WWAIT

The ST\_WWAIT state is entered from

- **ST\_IDLE** during a nonsequential write cycle

- **ST\_ENABLE** when there has been a single address cycle between two consecutive nonsequential writes.

Adding this state to a WRITE operation allows time for **BD** to be driven with the write data, ready to be sampled on the next rising edge of the clock.

The next state will always be ST\_WRITE.

## ST\_WRITE

The **ST\_WRITE**state is entered from:

- ST\_WWAIT during a nonsequential write cycle

- **ST\_ENABLE** during a sequential write cycle.

If a single write is being performed then BWAIT is set LOW. For a burst of writes, BWAIT is set HIGH (to delay the ASB transfer).

As for **ST\_READ**, the address is decoded and **PSEL** is driven, but **PWRITE** is driven HIGH. The next state will always be **ST\_ENABLE**.

## ST\_ENABLE

The ST\_ENABLE state is entered from

- **ST\_READ** during a read cycle

- **ST\_WRITE** during a write cycle.

If the reset transaction is a sequential read cycle, a wait cycle is added to allow the APB line to finish the current transaction before starting the read cycle. If the next transaction is a sequential write, no wait state is added as one will be inserted in the **ST\_WRITE** state.

For nonsequential writes, where **DSELPeri** is not held constantly HIGH (for example, when decode cycles are being inserted by the decoder), a wait state is inserted to allow time for **BD** to be driven with valid data.

The next state is:

- ST\_READ or ST\_WRITE for a burst transfer

- ST\_WWAIT for a burst of nonsequential writes with decode cycles

- **ST\_IDLE** for the last cycle in a burst, or for a single read or write cycle.

## 3.1.4 System description

The following paragraphs give a detailed description of how the HDL code for the bridge is set out. A simple system block diagram, with information about the main parts of the HDL code, is followed by details of all of the registers, and signals used in the system. This part should be read together with the HDL code.

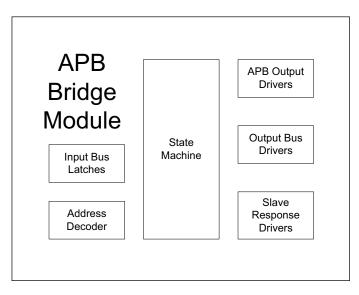

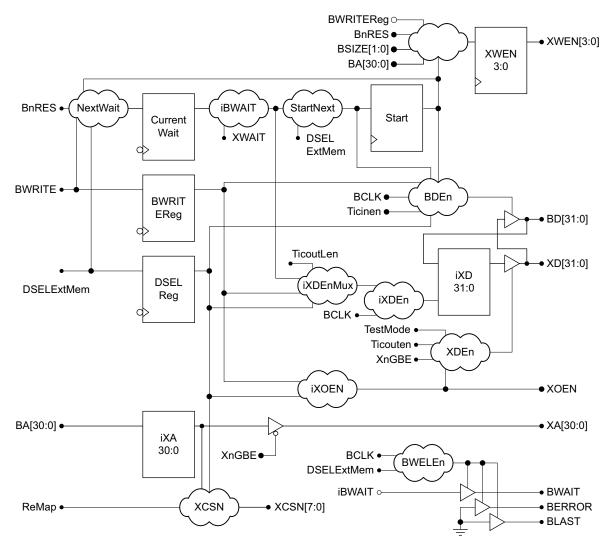

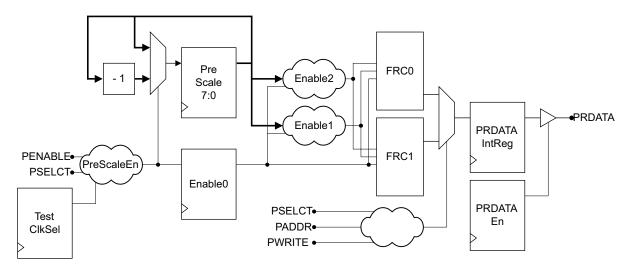

Figure 3-7 shows the APB bridge module block diagram.

## Figure 3-7 APB bridge module block diagram

The APB bridge system comprises:

the state machine which is used to control the generation of the output signals

• the address decoding which is used to generate the APB peripheral select lines.

All registers used in the system are clocked from the rising edge of the system clock **BCLK**. Enable signals are used to control the loading of the registers. All registers use the asynchronous reset **BnRES**.

A diagram of the APB bridge HDL file is shown in Figure 3-8.

### Figure 3-8 APB bridge module system diagram

The main parts and processes in the code are:

• Address decoder on page 3-13.

- *Next state logic* on page 3-14.

- State machine on page 3-14.

- *Current state decoding* on page 3-14.

- *PWRITEInt generation* on page 3-15.

- *Registered BA* on page 3-15.

- Internal PENABLE generation on page 3-15.

- *BD tristate enable* on page 3-15.

- *Slave response tristate enable* on page 3-15.

- *PWDATA generation* on page 3-15.

- *APB output signals* on page 3-15.

- *Tristate output drivers* on page 3-16.

Each of these is explained in the following paragraphs.

### **Constant and signal definitions**

The constant **PADDRWIDTH** sets the width of the peripheral address bus that is used, up to a maximum of 32 bits wide. This size depends on the size of address that is needed by the peripherals in the system. The default value is a 16-bit address bus.

The next five constants are the state machine states. They are explicitly defined so that the **ST\_ENABLE** state bit is not used by any other state, ensuring that there is no chance of getting any glitches on the **PENABLE** line. The signals that are used inside the module are then defined.

#### Address decoder

The address decoder decodes the current address on **BA**, and generates the internal **PSELxInt** signals that are used to drive the output ports on the APB. Constants are set with the address values for the peripherals (default uses bits 29:26 of the address), which are then compared with the current value of **BA** and the relevant peripheral select line is set.

For addresses outside the specified ranges, none of the **PSELxInt** lines will be set, but the read/write transfer will continue as normal.

### **Registered DSELPeri**

A rising edge registered copy of **DSELPeri** is required to generate **NextState** and **BWAITInt**, which is called **PrevDSEL**.

### Next state logic

The next state logic is the combinational part of the state machine. The next state of the state machine is calculated using the current state of the state machine and the **DSELPeri** and **BWRITE** inputs to the bridge. Figure 3-6 on page 3-9 shows the operation of the state machine.

The system resets into the **ST\_IDLE** state, and stays in this state until a transfer is requested. If the current cycle is a read or a write, the next state becomes **ST\_READ** or **ST\_WWAIT**, which is followed by **ST\_ENABLE**, or **ST\_WRITE** and **ST\_ENABLE**. If the transfer is only a single read or write operation, the system goes back to the **ST\_IDLE** state. If the transfer is a burst of reads or writes, the next state becomes **ST\_READ** or **ST\_WRITE**, and this continues until the transfer ends. For bursts of nonsequential writes, the state machine changes from **ST\_ENABLE** to **ST\_WAIT** to allow time for the write data to become valid on BD.

### State machine

With the state machine register **NextState** is loaded into **CurrentState** on the rising edge of **BCLK**.

#### **Current state decoding**

The current state decoding is used to generate two signals, BWAITInt and APBEn.

**BWAITInt** is set HIGH during four possible conditions:

- the start of the first APB transfer, when **DSELPeri** is set HIGH and the current state is still **ST\_IDLE**

- during a burst of sequential writes when the current state is **ST\_WRITE** and **DSELPeri** is still set HIGH

- during a burst of sequential reads when the current state is **ST\_ENABLE** and the next state will be **ST\_READ**.

- during a burst of nonsequential writes when the current state is **ST\_ENABLE**, **DSELPeri** is HIGH but **PrevDSEL** is LOW.

This signal is then used to drive the external **BWAIT** signal.

**APBEn** is set HIGH when a read or a write is being performed on the APB. The **APBEn** signal is then used to enable the **PWRITE**, **PADDR** and **PSEL** outputs.

### **PWRITEInt generation**

The signal **PWRITEInt** is a registered version of **BWRITE**. **BWRITE** is captured on the rising edge of **BCLK** when **APBEn** is HIGH with reset clearing it to zero.

## **Registered BA**

The signal **PADDRInt** is a rising edge registered version of **BA**(PADDRWidth-1:0). It is captured on the rising edge of **BCLK** when **APBEn** is HIGH, with reset clearing **PADDRInt** to all zeros.

### Internal PENABLE generation

**PENABLEInt** is generated from one of the Current State registers. This should be changed if the state encoding of the state machine is altered.

### **BD** tristate enable

The BD tristate enable is used to enable **BD** to be driven with the peripheral output data during a read cycle. It is set when **PWRITEInt** is LOW and **PENABLEInt** is HIGH, indicating a peripheral read.

### Slave response tristate enable

The slave response signals **BWAIT**, **BERROR** and **BLAST** are only driven by the slave when it is selected (that is **DSELPeri** is HIGH), and during the LOW phase of **BCLK**, so these two inputs are used to generate the slave response enable signal.

## **PWDATA** generation

The output signal **PWDATA** is a registered version of **BD** for a write cycle. In order to minimize the number of signal changes on **PWDATA**, the enable is only set when **NextState** is **ST\_WRITE**.

## **APB** output signals

In this part all the APB output ports are driven with their internal signals.

**PADDR, PWRITE** and **PENABLE** are driven directly by **PADDRInt** and **PWRITEInt** and **PENABLEInt** respectively.

The **PSEL** ports are registered versions of the **PSELInt** signals set on the rising edge of **BCLK**. The signals are registered when **APBEn** is HIGH (read or write cycle), and reset to zero when:

- **BnRES** is LOW

- at the end of the last APB transfer

- in the **ST\_WWAIT** state.

#### **Tristate output drivers**

The **BD** and slave response signals are all tristated, so can only be driven at the correct times to avoid any drive clashes by using the enable signals created earlier.

BD is driven with the current value of PRDATA when BDEn is HIGH.

**BWAIT** is driven with the current value of **BWAITInt** when **BWELEn** is HIGH. The module does not use the other two slave response signals **BERROR** and **BLAST**, which are driven LOW.

# 3.2 Arbiter

The AMBA bus specification is a multi-master bus standard. As a result, a bus arbiter is needed to ensure that only one bus master has access to the bus at any particular point in time. Each bus master can request the bus, the arbiter decides which has the highest priority and issues a grant signal accordingly.

Every system must have a default bus master which is granted use of the bus during reset, or when no other bus master requires the bus.

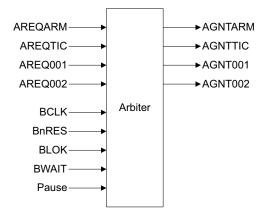

#### Figure 3-9 Arbiter block diagram

The arbiter included in the EASY design can support up to four bus masters, although only two are used. The operation of the arbiter is described under the following headings:

- Signal descriptions.

- Abitration process on page 3-18.

- Signal timing on page 3-19.

- *Arbitration priorities* on page 3-21.

- System description on page 3-22.

### 3.2.1 Signal descriptions

The signals are described in Table 3-2 on page 3-18.

— Note — — —

In systems that only have the ARM and the Test Interface Controller as potential bus masters, the unused **AREQxxx** lines must be tied LOW.

**Table 3-2 Signal descriptions**

| Name    | Туре   | Description                                                                                                                                                                                                                                                                                                                                                   |  |

|---------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BCLK    | Input  | This clock times all bus transfers. Both the LOW phase and HIGH phase of <b>BCLK</b> are used to control transfers on the bus.                                                                                                                                                                                                                                |  |

| BnRES   | Input  | The bus reset signal is active LOW and is used to reset the system<br>and the bus.                                                                                                                                                                                                                                                                            |  |

| BWAIT   | Input  | This signal is driven by the selected bus slave to indicate whether<br>the current transfer may complete. If <b>BWAIT</b> is HIGH a further<br>bus cycle is required. If <b>BWAIT</b> is LOW then the transfer may<br>complete in the current bus cycle. <b>BWAIT</b> is used by the arbiter<br>to determine when a turnaround cycle is happening on the bus. |  |

| BLOK    | Input  | A shared bus lock signal driven by the currently granted bus<br>master. When HIGH this signal indicates that the current transfer<br>and the next transfer are to be indivisible and no other bus master<br>should be granted the bus.                                                                                                                        |  |

| AREQarm | Input  | Request from the ARM processor indicating that it requires the bus. This signal must be set up to the falling edge of <b>BCLK</b> .                                                                                                                                                                                                                           |  |

| AREQtic | Input  | Request from the test interface controller.                                                                                                                                                                                                                                                                                                                   |  |

| AREQ001 | Input  | Request from the bus master 001.                                                                                                                                                                                                                                                                                                                              |  |

| AREQ002 | Input  | Request from the bus master 002.                                                                                                                                                                                                                                                                                                                              |  |

| Pause   | Input  | This signal allows the processor system to enter a low-power,<br>wait-for-interrupt state, when the system does not require the<br>processors to be active.                                                                                                                                                                                                   |  |

| AGNTarm | Output | Grant signal to the ARM processor. When HIGH, this signal indicates that the ARM bus master is granted the bus. This signal changes during the LOW phase of <b>BCLK</b> and remains valid through the HIGH phase.                                                                                                                                             |  |

| AGNTtic | Output | Grant signal to the test interface controller.                                                                                                                                                                                                                                                                                                                |  |

| AGNT001 | Output | Grant signal to bus master 001.                                                                                                                                                                                                                                                                                                                               |  |

| AGNT002 | Output | Grant signal to bus master 002.                                                                                                                                                                                                                                                                                                                               |  |

# 3.2.2 Abitration process

The ASB arbitration is controlled by the AREQ, AGNT, BLOK and BWAIT signals.

When an ASB master requires use of the bus, it sets its **AREQ** output line HIGH. This is sampled by the arbiter, on the falling edge of **BCLK**, and the **AGNT** outputs change according to the arbitration priority scheme used by the system.

The **BLOK** and **BWAIT** signals are used to extend the granted period to allow masters to finish transfers before bus master handover begins. If **BLOK** is set HIGH by the current master, and a higher priority master requests the bus, handover will not start until **BLOK** is set LOW, showing that the locked transfer has finished.

If **BLOK** is set HIGH after handover has begun, it is ignored, as it is too late to have an effect on the handover process.

If **BWAIT** is set HIGH after the handover process has begun, then the **AGNT** lines change as normal, but the new ASB master must allow the current master to finish the bus transfer (**BWAIT** LOW) before taking control of the bus.

## 3.2.3 Signal timing

The arbitration signal timing depends on:

- the priorities of the masters requesting the bus

- the status of **BLOK** when the request lines change

- the status of **BWAIT** during the handover cycle.

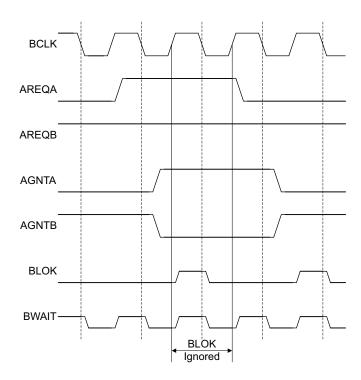

This is shown in Figure 3-10 on page 3-20, and Figure 3-11 on page 3-21, where master A has a higher priority than master B. The masters read their **AGNT** inputs and gain control of the bus on the rising edge of **BCLK**.

Figure 3-10 on page 3-20 shows a normal grant handover where the higher priority master is granted the bus for two cycles before handing it back to the lower priority master. During bus master handover **BLOK** is not driven and therefore the arbiter ignores this signal until the new master has control of the bus.

Figure 3-10 Arbitration timing

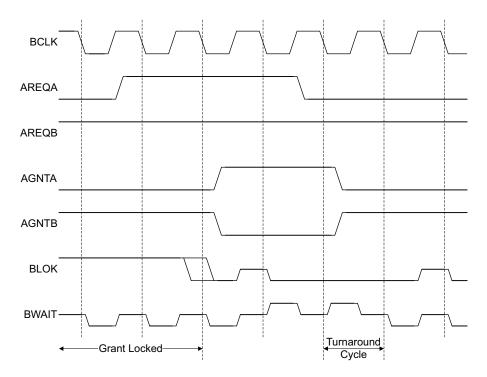

Figure 3-11 on page 3-21 shows the effect of the **BLOK** signal, as the grant to the lower priority master is held until the **BLOK** signal is released. If one current transfer is extended (**BWAIT** is HIGH), then the **AGNT** lines are set to their new values, but the masters in the system must monitor the **BWAIT** signal and wait until it is LOW before gaining control of the bus.

Figure 3-11 Arbitration timing with BLOK set and turnaround cycle

### 3.2.4 Arbitration priorities

During reset, when **BnRES** is LOW, the arbiter grants use of the bus to the default bus master, and holds all other grant signals inactive.

The following arbitration priorities (from highest to lowest) are implemented in the default system:

- Test interface controller (highest)

- Bus master1

- Bus master 2

- ARM processor (lowest).

There are four different methods for a bus master to be granted the bus at that time:

- if it is the highest priority master requesting the bus at that time

- if it is the standard master selected during reset

- if it is the standard master selected during pause mode (when **Pause** is set HIGH)

- if it is the default master selected when no masters are requesting the bus.

### 3.2.5 System description

The following paragraphs give a detailed description of how the HDL code for the system arbiter is set out. A simple system block diagram, with information about the main parts of the HDL code, is followed by details of all the registers, and signals used in the system. This part should be read together with the HDL code.

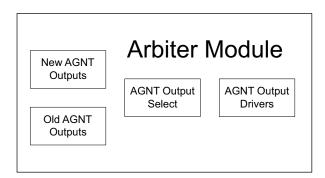

#### Figure 3-12 Arbiter module block diagram

The arbiter comprises the two versions of the **AGNT** output signals (new and old) and the output select that drives the **AGNT** lines with one of the internal **AGNT** values.

All registers used in the system are clocked from the same signal, the system clock **BCLK**, from either the rising or the falling edge. Enable signals are used to control the loading of the registers. All registers use the asynchronous reset **BnRES**.

A diagram of the arbiter HDL file is shown in Figure 3-13 on page 3-23.

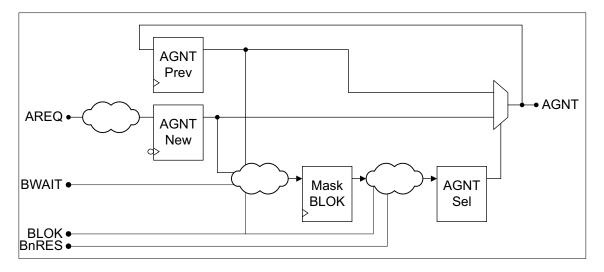

### Figure 3-13 Arbiter module system diagram

The parts and processes in the code are described in the following sections:

- Arbitration scheme.

- Stored previous AGNT outputs on page 3-24.

- AGNT comparator on page 3-24.

- *MaskBLOK generation* on page 3-24.

- AGNT output selection control on page 3-24.

- AGNT output select on page 3-24.

- AGNT output drivers on page 3-25.

### **Arbitration scheme**

This part defines the arbitration scheme that is used by the system, the default being a priority based system. The order that the inputs are checked in the if statement is the priority order of the system. **AREQtic** is the first input that is checked, then **Pause** (also the TIC), **AREQ001**, and through to the lowest priority. As the TIC is the highest priority master, if the **AREQtic** is HIGH, **AGNTticNew** will be driven HIGH no matter what values the other **AREQ** inputs have. If **AREQarm** is set HIGH, **AGNTarmNew** will only be set if all other **AREQ** inputs are LOW, as the **ARM** is the lowest priority master.

The **AGNTarmNew** output is set during reset when **BnRES** is LOW and when no other **AREQ** lines are set HIGH.

Falling edge registers are used to hold the generated AGNTNew values.

#### Stored previous AGNT outputs

The current **AGNT** outputs are not a direct reflection of the **AREQ**, **BnRES** and **Pause** inputs to the Arbiter. This is due to delays during the bus master handover, when **BLOK**, or **BWAIT** are set.

This means that the **AGNT** outputs have to be held at their current values during the handover process, and this is done by the **AGNTPrev** registers, which sample the **AGNT** outputs on the rising edge of the system clock.

#### **AGNT comparator**

The AGNT 4-bit comparator is used to compare the **AGNTNew** and the **AGNTPrev** signals to detect a bus master handover, and it sets **AGNTChange** HIGH when they are different.

### MaskBLOK generation

The **MaskBLOK** register is used to mask out the **BLOK** signal to the **AGNTSel** latch, so that the **AGNTNew** signals are held on the outputs during handover no matter what the status of **BLOK** is during the handover cycle.

#### AGNT output selection control

The AGNTSelNext signal is used to feed the AGNTSel latch, which is transparent when BCLK is LOW. A latch is used due to the timing of BLOK. AGNTSel is used to select either the AGNTNew or AGNTPrev signals to be driven onto the AGNT outputs.

During bus master handover **BLOK** must be ignored (as shown in Figure 3-10 on page 3-20). This is done using **MaskBLOK** in the generation of **AGNTSelNext**. If **BLOK** is set HIGH, **AGNTSelNext** will be driven LOW, but during handover **MaskBLOK** will also be HIGH, keeping **AGNTSelNext** driven HIGH.

During reset (when **BnRES** is HIGH), **AGNTSel** will be driven LOW, which selects the **AGNTPrev** signals to be driven onto the AGNT outputs.

### AGNT output select

A 4-bit multiplexor is used to select either the **AGNTNew** or **AGNTPrev** signals to drive the **iAGNT** signals with, depending on the value of **AGNTSel**. If the value of **AGNTSel** is HIGH, **AGNTNew** is selected. If it is LOW, **AGNTPrev** is selected.

# AGNT output drivers

The external AGNT ports are continuously driven with their internal iAGNT signals.

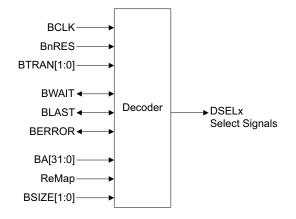

# 3.3 Decoder

#### 3.3.1 Overview

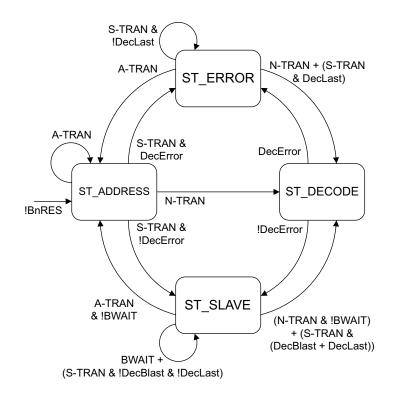

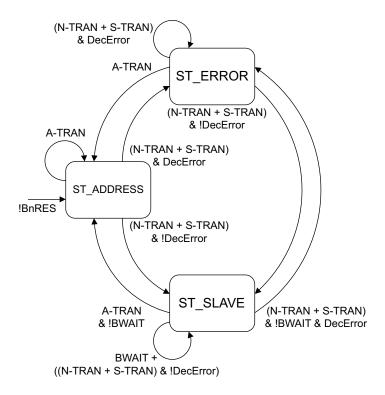

The decoder performs three functions:

- it generates the slave select signals (**DSELx**) for each of the bus slaves, indicating that a read or write access to that slave is required

- it generates the slave response signals (**BWAIT**, **BLAST** and **BERROR**) during Address-only transfers, when no slave is selected

- it can act as a simple protection unit which prevents attempts to access a protected area of the memory map.

Two implementations of the decoder are provided in one HDL file, using the value of **DECEN** to select between them:

- Decoder with decode cycles. This is the default mode, and is used in fast systems where the decoder might not have enough time to decode the address and assert the corresponding **DSELx** signal in a single clock HIGH phase. This implementation automatically inserts a decode cycle:

- at the start of a nonsequential transfer

- on a sequential transfer when **BLAST** has been asserted

- when 1KB memory boundaries are reached.

- Decoder without decode cycles. This implementation requires that all accesses can be decoded within a single bus cycle, and therefore will only be suitable for slow systems where this can be safely achieved.

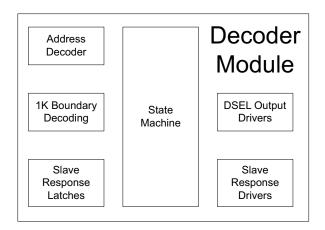

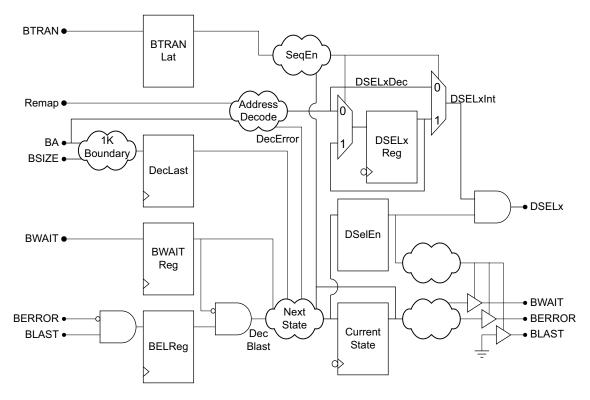

A block diagram of the decoder is shown in Figure 3-14 on page 3-27.

Figure 3-14 Decoder block diagram

## 3.3.2 Signal description

This section describes the signals that interface to the decoder.

### **Table 3-3 Signal descriptions**

| Name       | Туре         | Description                                                                                                                                                                                                                                                                                                    |  |

|------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BCLK       | Input        | This clock times all bus transfers. Both the LOW phase and HIGH phase of <b>BCLK</b> are used to control transfers on the bus.                                                                                                                                                                                 |  |

| BnRES      | Input        | The bus reset signal is active LOW, and is used to reset the system.                                                                                                                                                                                                                                           |  |

| BSIZE[1:0] | Input        | The transfer size signals indicate the size of the transfer, which may be byte, halfword or word.                                                                                                                                                                                                              |  |

| BTRAN[1:0] | Input        | These signals indicate the type of the next transaction, which may be address-only, nonsequential or sequential. These signals are driven by a bus master when its respective <b>AGNTx</b> signal is asserted.                                                                                                 |  |

| BA[31:0]   | Input        | The system address bus, which is driven by the active bus master.                                                                                                                                                                                                                                              |  |

| Remap      | Input        | When LOW, the internal memory is not part of the system memory map, and external memory is mapped from address 0x0000000 which normally contains the system startup code. In normal operation this signal is HIGH, allowing the use of the internal memory.                                                    |  |

| BWAIT      | Input/Output | This signal is driven by the selected bus slave to indicate if the current transfer may complete. If <b>BWAIT</b> is HIGH a further bus cycle is required, if <b>BWAIT</b> is LOW then the transfer may complete in the current bus cycle. When no slave is selected this signal is driven by the bus decoder. |  |

#### Table 3-3 Signal descriptions (continued)

| Name   | Туре         | Description                                                                                                                                                                                                                                                                                                                                                                   |

|--------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BERROR | Input/Output | A transfer error is indicated by the selected bus slave using the <b>BERROR</b> signal. When <b>BERROR</b> is HIGH a bus error has occurred. When <b>BERROR</b> is LOW, the transfer is successful. When no slave is selected, this signal is driven by this module.                                                                                                          |

| BLAST  | Input/Output | This signal is driven by the selected bus slave to indicate whether the current transfer should be the last of a burst sequence. When <b>BLAST</b> is HIGH, the decoder must allow sufficient time for address decoding. When <b>BLAST</b> is LOW, the next transfer may continue a burst sequence. When no slave is selected this signal is driven by the bus decoder.       |

| DSELx  | Output       | These are the select signals from the bus decoder to each individual bus slave, which indicate that the slave device is selected, and a data transfer is required. There is a <b>DSELx</b> signal for each ASB bus slave. This signal becomes valid during the HIGH phase before the data transfer is required, and remains active until the last HIGH phase of the transfer. |

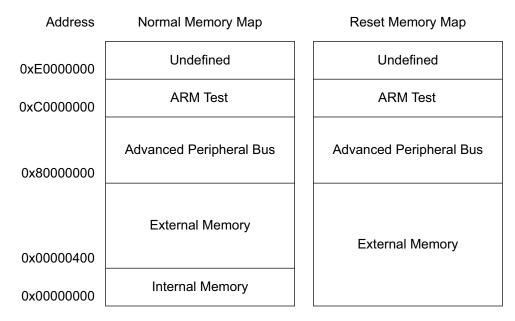

## 3.3.3 Memory map

The decoder controls the memory map of the system, and generates a slave select signal for each memory region.

The **Remap** signal is used to provide a different memory map at reset, when ROM is required at address 0, and during normal operation, when RAM may be used at address 0.

The **Remap** signal is typically provided by a remap and pause peripheral, which drives Remap LOW at reset. The signal is driven HIGH only after a particular address in the remap and pause peripheral is accessed.

Figure 3-15 on page 3-29 shows both the normal and reset memory maps.

### Figure 3-15 Memory map

# 3.3.4 Function and operation of block

At the start of every transfer on the bus, the decoder can perform a number of actions. The decoder is able to determine when a transfer is about to start by examining the **BWAIT** signal, which will be LOW when the previous transfer is completing. The actions the decoder may take depend on the type of transfer as shown in Table 3-4.

### Table 3-4 Types of transfer

| Transfer type                               | Decoder action                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

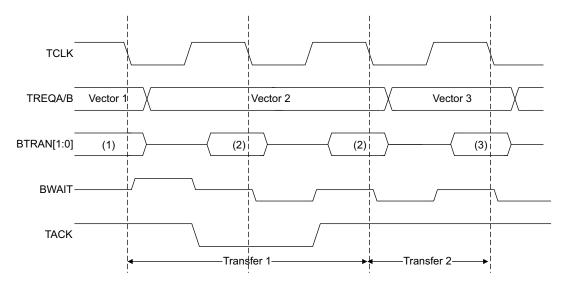

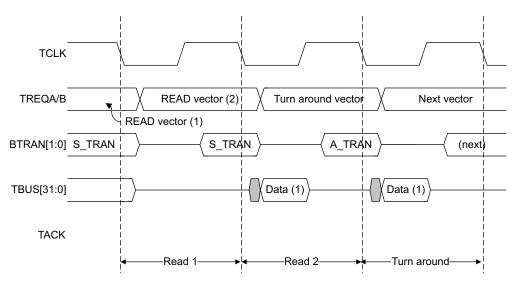

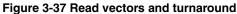

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|