# ARM1176JZF Development Chip

Revision: r0p0

**Technical Reference Manual**

Copyright © 2007 ARM Limited. All rights reserved. ARM DDI 0375A

# ARM1176JZF Development Chip Technical Reference Manual

Copyright © 2007 ARM Limited. All rights reserved.

#### **Release Information**

|                |       |                  | Change history         |

|----------------|-------|------------------|------------------------|

| Date           | Issue | Confidentiality  | Change                 |

| 31 August 2007 | А     | Non-Confidential | First release of r0p0. |

#### **Proprietary Notice**

Words and logos marked with  $^{\otimes}$  or  $^{\mathbb{M}}$  are registered trademarks or trademarks of ARM Limited in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM Limited in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

# Contents ARM1176JZF Development Chip Technical Reference Manual

|           | Prefa |                                        |      |

|-----------|-------|----------------------------------------|------|

|           |       | About this manual                      | xiv  |

|           |       | Feedback                               | xix  |

| Chapter 1 | Intro | oduction                               |      |

|           | 1.1   | About the ARM1176JZF Development Chip  | 1-2  |

|           | 1.2   | Component summary                      | 1-3  |

|           | 1.3   | Technology summary                     |      |

| Chapter 2 | Fund  | ctional Overview                       |      |

|           | 2.1   | About the ARM 1176JZF Development Chip |      |

|           | 2.2   | System controller                      | 2-26 |

|           | 2.3   | Intelligent Energy Management (IEM)    |      |

|           | 2.4   | Generic Interrupt Controller (GIC)     | 2-64 |

|           | 2.5   | CoreSight                              | 2-65 |

|           | 2.6   | Clock sources and domains              | 2-72 |

| Chapter 3 | Proc  | grammer's Model                        |      |

| •         | 3.1   | About the programmer's model           |      |

|           | 3.2   | Memory maps                            |      |

|           |       |                                        |      |

| 3.3 | SoC configuration                  | . 3-7 |

|-----|------------------------------------|-------|

| 3.4 | Controlling the power modes        | 3-20  |

| 3.5 | Configuring the IEC                | 3-25  |

| 3.6 | System controller                  |       |

| 3.7 | Generic Interrupt Controller (GIC) |       |

# Appendix A Electrical and Physical Characteristics

| A.1 | About electrical and physical characteristics | A-2  |

|-----|-----------------------------------------------|------|

| A.2 | Electrical requirements                       | A-3  |

| A.3 | Bonding and pinout                            | A-4  |

| A.4 | Physical characteristics                      | ₹-74 |

# Appendix B Component Revision Status

| B.1 | Components             | B-2 |

|-----|------------------------|-----|

| B.2 | Third party components | B-4 |

|     | IP modifications       |     |

| B.4 | Custom IP              | B-6 |

| B.5 | Configured IP          | B-7 |

# Glossary

# List of Tables ARM1176JZF Development Chip Technical Reference Manual

|            | Change history                                   | ii   |

|------------|--------------------------------------------------|------|

| Table 2-1  | L2C master port transactions                     | 2-7  |

| Table 2-2  | 64-bit AXI infrastructure arbitration priority   | 2-10 |

| Table 2-3  | 64-bit AXI make-up                               | 2-11 |

| Table 2-4  | ID merge function                                | 2-12 |

| Table 2-5  | DMC QoS options                                  | 2-12 |

| Table 2-6  | 32-bit AXI ID make-up                            | 2-13 |

| Table 2-7  | Interrupt source allocation                      | 2-18 |

| Table 2-8  | user_config Register functionality in PL340      | 2-23 |

| Table 2-9  | user_status Register functionality in PL340      | 2-24 |

| Table 2-10 | IEC Maxperf and wake-up sources                  | 2-36 |

| Table 2-11 | System clock divide ratio options                | 2-49 |

| Table 2-12 | Example system frequencies with 320MHz CPU speed | 2-50 |

| Table 2-13 | DCG resets                                       | 2-52 |

| Table 2-14 | Asynchronous resets                              | 2-53 |

| Table 2-15 | SoC reset signals                                | 2-54 |

| Table 2-16 | JTAG TAP selection                               | 2-67 |

| Table 2-17 | CTI #0 connectivity                              | 2-68 |

| Table 2-18 | CTI #1 connectivity                              | 2-68 |

| Table 2-19 | External clock sources                           |      |

| Table 2-20 | Internally generated clock sources               | 2-73 |

| Table 2-21 | Exported clocks                                          | 2-74  |

|------------|----------------------------------------------------------|-------|

| Table 3-1  | Remap options                                            | . 3-4 |

| Table 3-2  | Test mode configuration inputs                           | . 3-8 |

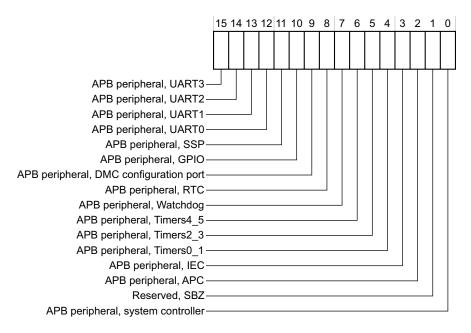

| Table 3-3  | TZPCDECPROT0 Register bit assignments                    |       |

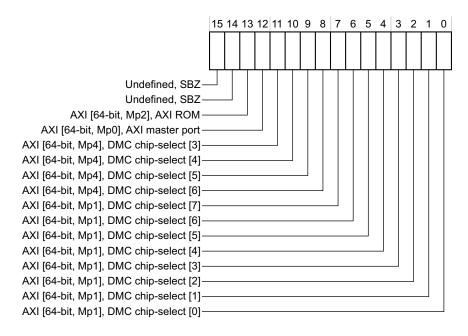

| Table 3-4  | TZPCDECPROT1 Register bit assignments                    | 3-14  |

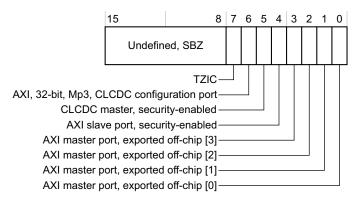

| Table 3-5  | TZPCDECPROT2 Register bit assignments                    | 3-16  |

| Table 3-6  | AXI slave port security override                         | 3-17  |

| Table 3-7  | Configuration block signals                              | 3-18  |

| Table 3-8  | IEC performance levels                                   | 3-28  |

| Table 3-9  | System controller register summary                       |       |

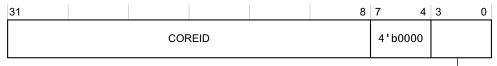

| Table 3-10 | CoreID Register bit assignments                          | 3-32  |

| Table 3-11 | SoCConfig1 Register bit assignments                      |       |

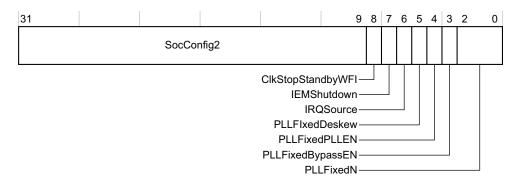

| Table 3-12 | SoCConfig2 Register bit assignments                      |       |

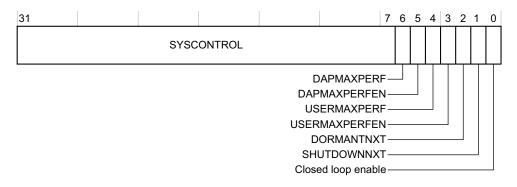

| Table 3-13 | System Control Register bit assignments                  |       |

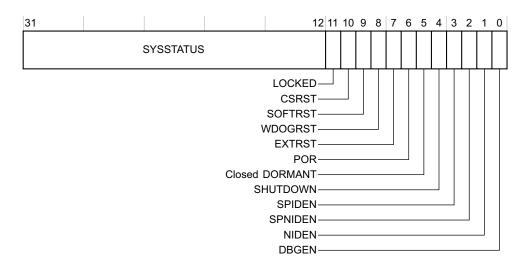

| Table 3-14 | System Status Register bit assignments                   |       |

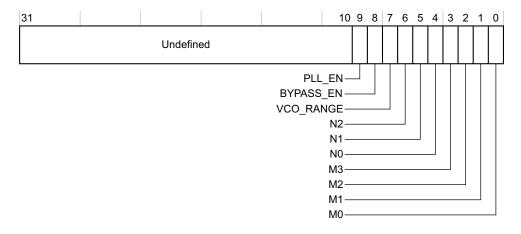

| Table 3-15 | PLL Configuration Settings Registers bit assignments     |       |

| Table 3-16 | 64-bit AXI Priority Register bit assignments             |       |

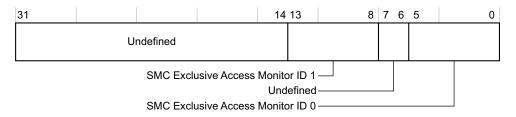

| Table 3-17 | SMC Exclusive Access Monitor ID Register bit assignments |       |

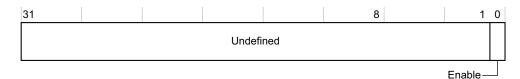

| Table 3-18 | DLL Calibrate Outputs Register bit assignments           |       |

| Table 3-19 | Distributor Register summary                             |       |

| Table 3-20 | Distributor Register Control Register bit assignments    |       |

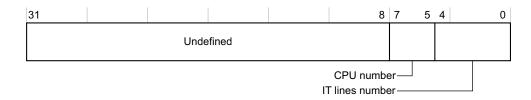

| Table 3-21 | Interrupt Controller Type Register bit assignments       |       |

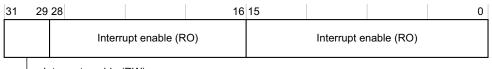

| Table 3-22 | Interrupt Set-Enable Register 0 bit assignments          | 3-49  |

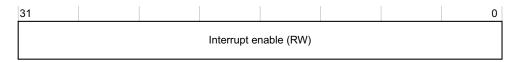

| Table 3-23 | Interrupt Set-Enable Register 1 bit assignments          |       |

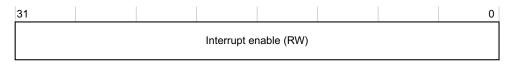

| Table 3-24 | Interrupt Clear-Enable Register 0 bit assignments        |       |

| Table 3-25 | Interrupt Clear-Enable Register 1 bit assignments        |       |

| Table 3-26 | Interrupt Set-Pending Register 0 bit assignments         |       |

| Table 3-27 | Interrupt Set-Pending Register 1 bit assignments         |       |

| Table 3-28 | Interrupt Clear-Pending Register 0 bit assignments       |       |

| Table 3-29 | Interrupt Clear-Pending Register 1 bit assignments       |       |

| Table 3-30 | Active Bit Register 0 and 1 bit assignments              |       |

| Table 3-31 | Interrupt Priority Register 0-3 bit assignments          |       |

| Table 3-32 | Interrupt Priority Register 4-6 bit assignments          |       |

| Table 3-33 | Interrupt Priority 7-15 Register bit assignments         |       |

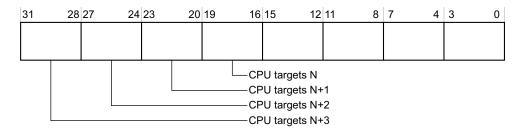

| Table 3-34 | Interrupt CPU Target Registers 0-6 bit assignments       |       |

| Table 3-35 | Interrupt CPU Target Register 7 bit assignments          |       |

| Table 3-36 | Interrupt CPU Target Register 8-15 bit assignments       |       |

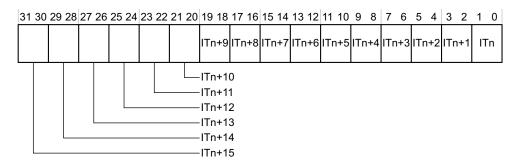

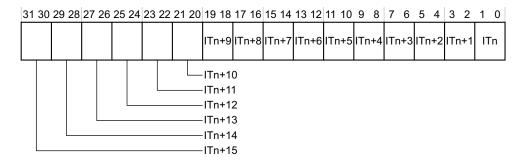

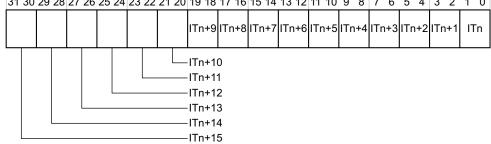

| Table 3-37 | Interrupt Configuration Register 0 bit definition        |       |

| Table 3-38 | Interrupt definition encoding                            |       |

| Table 3-39 | Interrupt Configuration Register 1 bit assignments       |       |

| Table 3-40 | Interrupt Configuration Register 2-3 bit definition      |       |

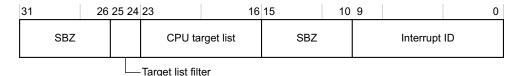

| Table 3-41 | Software Interrupt Register bit definition               |       |

| Table 3-42 | CPU interface registers                                  |       |

| Table 3-43 | CPU Interface Control register bit assignments           |       |

| Table 3-44 | Priority Mask Register bit assignments                   |       |

| Table 3-45 | Binary Pointer Register bit assignments                  |       |

| Table 3-46 | Binary Point value meanings                              | 3-69  |

| Table 3-47 | Interrupt Acknowledge Register bit assignments     | 3-69  |

|------------|----------------------------------------------------|-------|

| Table 3-48 | End of Interrupt Register bit assignments          | 3-70  |

| Table 3-49 | Running interrupt Register bit assignments         | 3-70  |

| Table 3-50 | Highest Pending interrupt Register bit assignments | 3-71  |

| Table A-1  | Pad type                                           | . A-4 |

| Table A-2  | Die bonding                                        | . A-5 |

| Table A-3  | I/O cell usage for inline design                   | A-79  |

| Table B-1  | Product revisions                                  | . B-2 |

| Table B-2  | Third party IP revisions                           | . B-4 |

| Table B-3  | IP modifications                                   | . B-5 |

| Table B-4  | Custom IP descriptions                             | . B-6 |

List of Tables

# List of Figures ARM1176JZF Development Chip Technical Reference Manual

|             | Key to timing diagram conventions                 | xvi  |

|-------------|---------------------------------------------------|------|

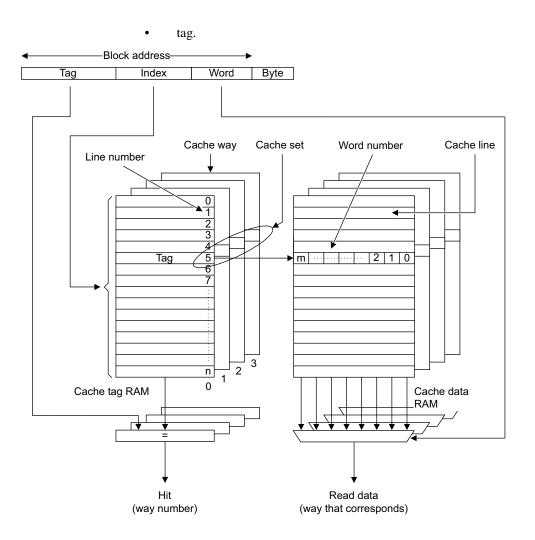

| Figure 2-1  | ARM1176JZF Development Chip block diagram         | 2-2  |

| Figure 2-2  | IEM subsystem                                     |      |

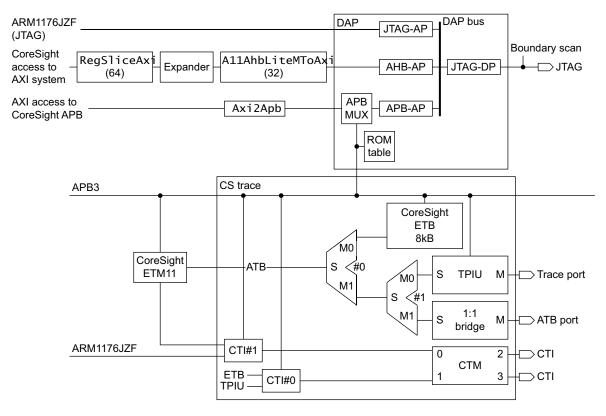

| Figure 2-3  | CoreSight subsystem                               |      |

| Figure 2-4  | APB peripherals                                   |      |

| Figure 2-5  | Secure and non-secure interrupt structure         | 2-17 |

| Figure 2-6  | SMC AXI interface logic                           | 2-21 |

| Figure 2-7  | user_config Register bit assignment               | 2-23 |

| Figure 2-8  | user_status Register bit assignment               | 2-24 |

| Figure 2-9  | System controller top-level                       | 2-27 |

| Figure 2-10 | IEM performance level and PLL controller          | 2-28 |

| Figure 2-11 | Performance decrease to running on PLL1 from PLL2 | 2-30 |

| Figure 2-12 | Performance decrease to running on PLL2 from PLL1 | 2-31 |

| Figure 2-13 | Performance increase to running on PLL2 from PLL1 | 2-32 |

| Figure 2-14 | Performance increase to running on PLL1 from PLL2 | 2-33 |

| Figure 2-15 | Increase to maximum performance                   | 2-34 |

| Figure 2-16 | Remap logic                                       | 2-37 |

| Figure 2-17 | IEM block diagram                                 | 2-39 |

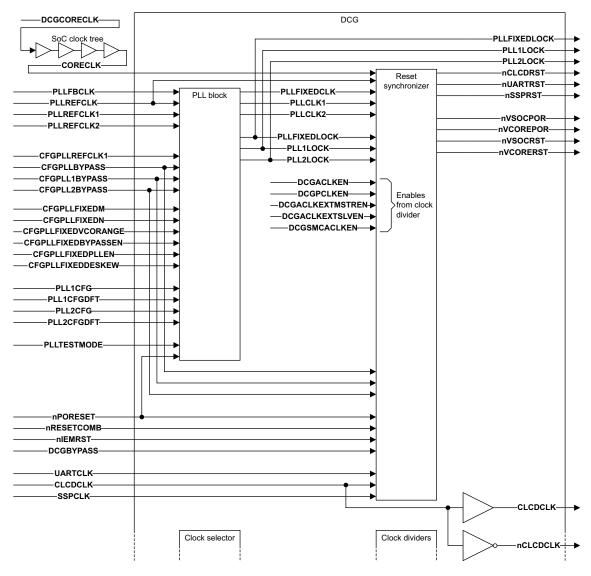

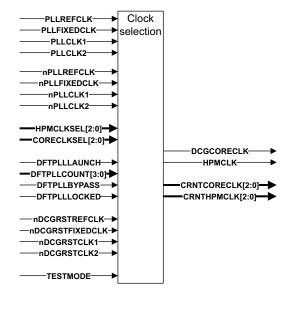

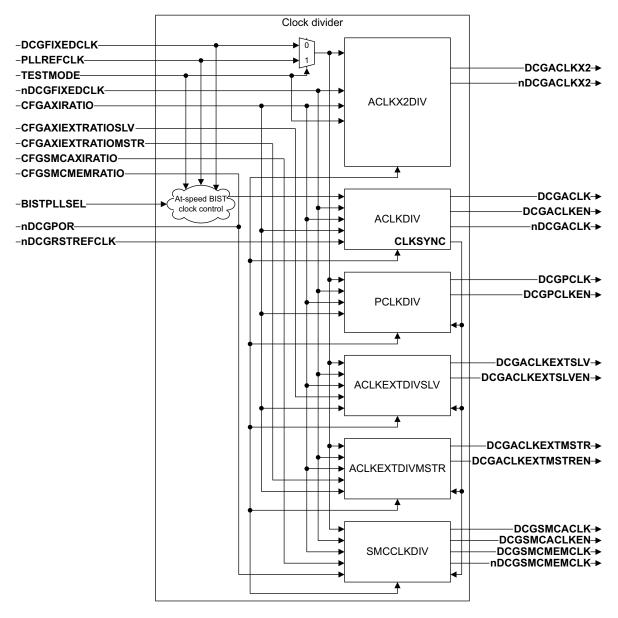

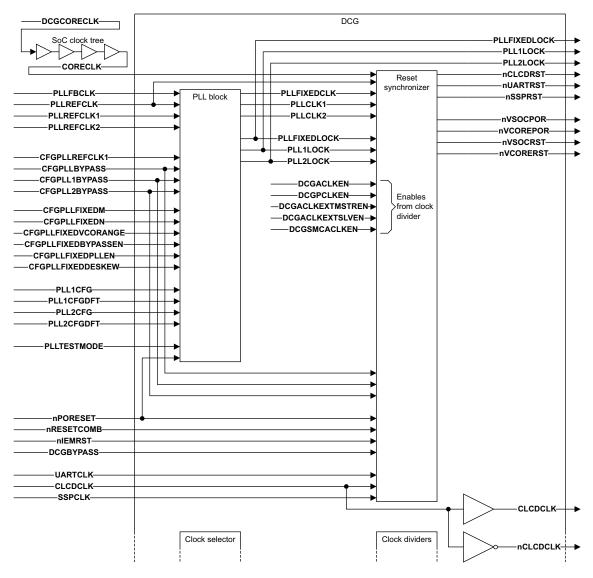

| Figure 2-18 | DCG block diagram part 1                          | 2-41 |

| Figure 2-19 | DCG block diagram part 2                          | 2-42 |

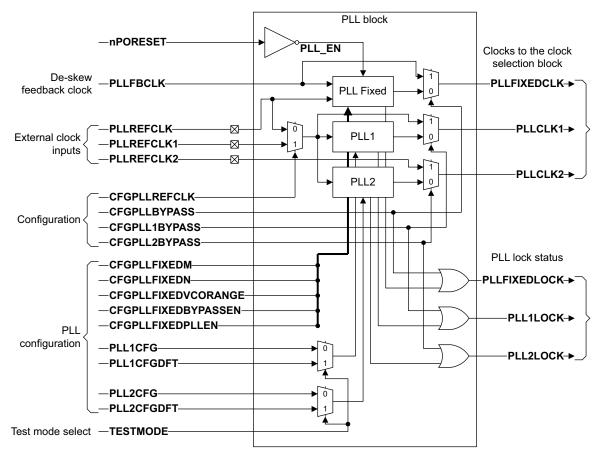

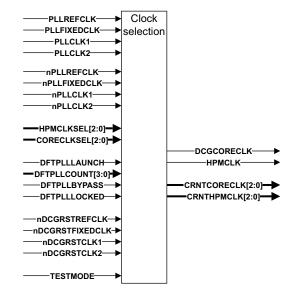

| Figure 2-20 | PLL block                                         | 2-44 |

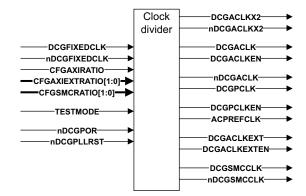

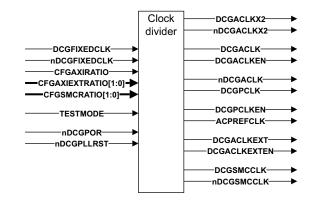

| Figure 2-21 | Clock divider block diagram                                     | 2-46 |

|-------------|-----------------------------------------------------------------|------|

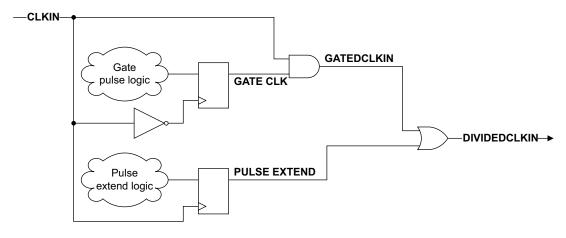

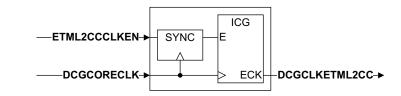

| Figure 2-22 | Clock divide circuit                                            | 2-48 |

| Figure 2-23 | Example divide by 4                                             | 2-48 |

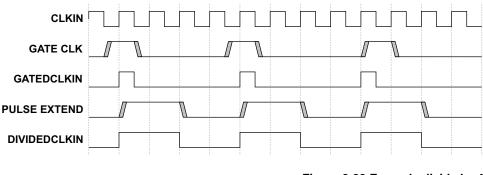

| Figure 2-24 | ETM and L2CC StandbyWFI clock gate                              | 2-51 |

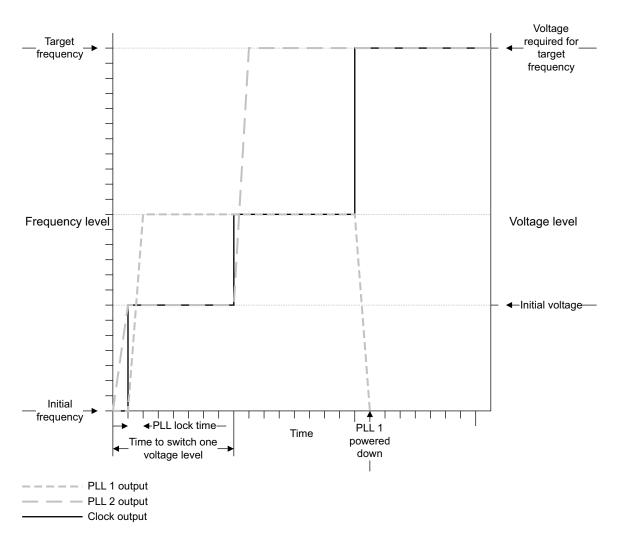

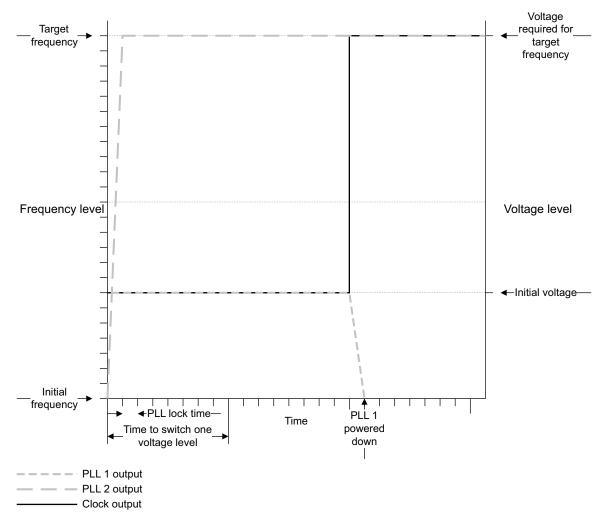

| Figure 2-25 | Switching with performance requirement optimization             | 2-56 |

| Figure 2-26 | Switching without performance requirement optimization          | 2-57 |

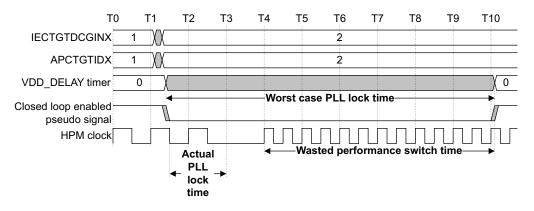

| Figure 2-27 | Standard APCI closed loop behavior                              |      |

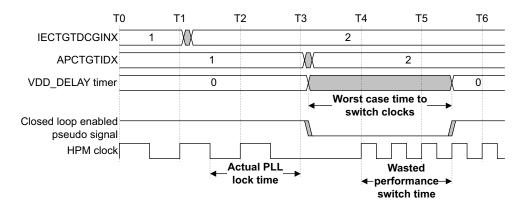

| Figure 2-28 | Improved closed loop with target voltage under DCG control      | 2-60 |

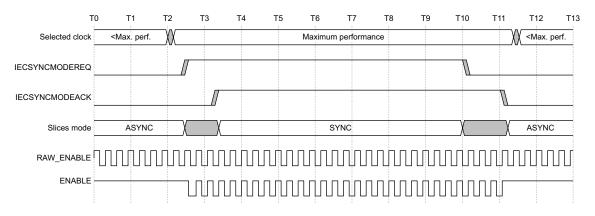

| Figure 2-29 | Clock enable control between synchronous and asynchronous modes | 2-61 |

| Figure 2-30 | DVS emulation example                                           |      |

| Figure 2-31 | CoreSight architecture                                          | 2-66 |

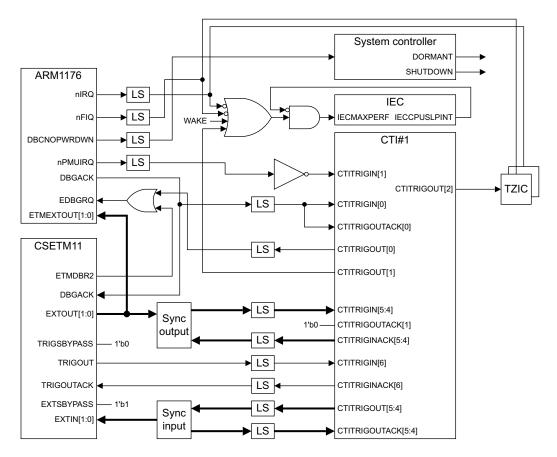

| Figure 2-32 | CoreSight trigger connectivity                                  | 2-70 |

| Figure 3-1  | ARM 1176JZF peripheral port memory map                          | 3-5  |

| Figure 3-2  | ARM 1176JZF DMA port, CLCDC, and CoreSight memory map           | 3-6  |

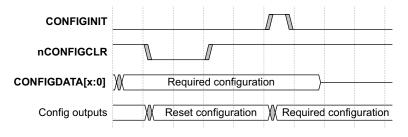

| Figure 3-3  | Configuration capture sequence                                  | 3-7  |

| Figure 3-4  | TZPCDECPROT0 Register bit assignments                           | 3-12 |

| Figure 3-5  | TZPCDECPROT1 Register bit assignments                           | 3-14 |

| Figure 3-6  | TZPCDECPROT2 Register bit assignments                           | 3-15 |

| Figure 3-7  | DCG block diagram part 1                                        | 3-26 |

| Figure 3-8  | DCG block diagram part 2                                        | 3-27 |

| Figure 3-9  | CoreID Register bit assignments                                 | 3-32 |

| Figure 3-10 | SoCConfig1 Register bit assignments                             | 3-33 |

| Figure 3-11 | SocConfig2 Register bit assignments                             | 3-34 |

| Figure 3-12 | System Control Register bit assignments                         | 3-35 |

| Figure 3-13 | System Status Register bit assignments                          | 3-37 |

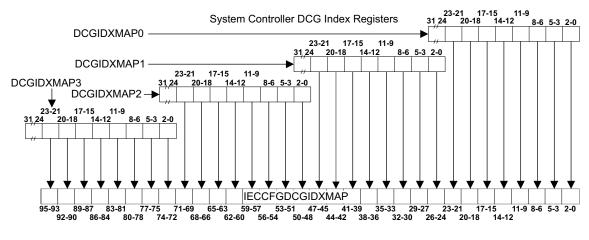

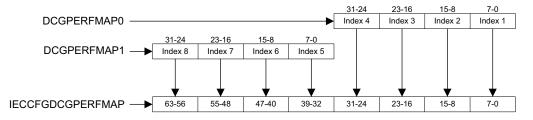

| Figure 3-14 | DCGIDXMAP registers to IECCFGDCGIDXMAP configuration inputs     | 3-39 |

| Figure 3-15 | DCGPERFMAP registers to IECCFGDCGPERFMAP configuration inputs   | 3-39 |

| Figure 3-16 | PLL Configuration Settings Register bit assignments             | 3-40 |

| Figure 3-17 | SMC Exclusive Access Monitor ID Register bit assignments        |      |

| Figure 3-18 | DLL Calibrate Register                                          |      |

| Figure 3-19 | Distributor Register Control Register bit assignments           | 3-47 |

| Figure 3-20 | Interrupt Controller Type Register bit assignments              |      |

| Figure 3-21 | Interrupt Set-Enable Register 0 bit assignments                 | 3-49 |

| Figure 3-22 | Interrupt Set-Enable Register 1 bit assignments                 |      |

| Figure 3-23 | Interrupt Clear-Enable Register 0 bit assignments               |      |

| Figure 3-24 | Interrupt Clear-Enable Register 1 bit assignments               |      |

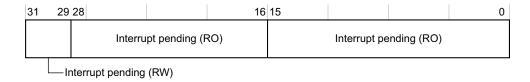

| Figure 3-25 | Interrupt Set-Pending Register 0 bit assignments                |      |

| Figure 3-26 | Interrupt Set-Pending Register 1 bit assignments                |      |

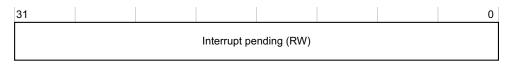

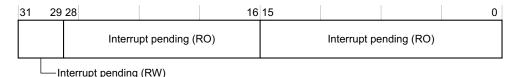

| Figure 3-27 | Interrupt Clear-Pending Register 0 bit assignments              |      |

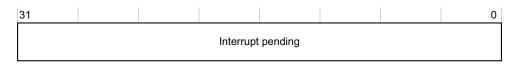

| Figure 3-28 | Interrupt Clear-Pending Register 1 bit assignments              |      |

| Figure 3-29 | Active Bit Register 0 and 1 bit assignments                     |      |

| Figure 3-30 | Interrupt Priority Register 0-3 bit assignments                 |      |

| Figure 3-31 | Interrupt Priority Register 4-6 bit assignments                 |      |

| Figure 3-32 | Interrupt Priority Register 7-15 bit assignments                |      |

| Figure 3-33 | Interrupt CPU Target Registers 0-6 bit assignments              |      |

| Figure 3-34 | Interrupt CPU Target Register 7 bit assignments                 |      |

| Figure 3-35 | Interrupt CPU Target Register 8-15                              | 3-60 |

| Figure 3-36 | Interrupt Configuration Register 0 bit assignments   | 3-61 |

|-------------|------------------------------------------------------|------|

| Figure 3-37 | Interrupt Configuration Register 1 bit assignments   | 3-63 |

| Figure 3-38 | Interrupt Configuration Register 2-3 bit assignments | 3-65 |

| Figure 3-39 | Software Interrupt Register bit assignments          | 3-66 |

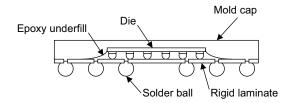

| Figure A-1  | Flipchip CABGA package cross-section                 | A-74 |

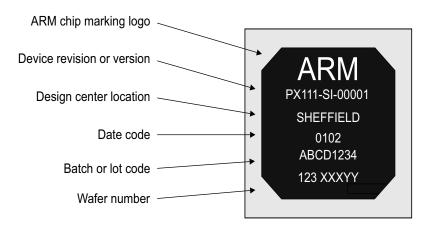

| Figure A-2  | Example package markings                             | A-76 |

List of Figures

# Preface

This preface introduces the ARM 1176JZF Development Chip Revision r0p0 Technical Reference Manual. It contains the following sections:

- About this manual on page xiv

- *Feedback* on page xix.

# About this manual

This is the *Technical Reference Manual* (TRM) for the *ARM 1176JZF Development Chip* subsystem. All references to the chip in this manual refer to the ARM 1176JZF Development Chip.

# Product revision status

| The rnpn   | identifier indicates the revision status of the product described in this manual, |

|------------|-----------------------------------------------------------------------------------|

| where:     |                                                                                   |

| r <i>n</i> | Identifies the major revision of the product.                                     |

| р <i>п</i> | Identifies the minor revision or modification status of the product.              |

## Intended audience

This manual is written for system designers, system integrators, and verification engineers who are implementing a *System-on-Chip* (SoC) device based on the ARM1176JZF development chip subsystem. The manual describes the VC.

## Using this manual

This manual is organized into the following chapters:

Many of the components used in the ARM1176JZF development chip subsystem have a separate TRM. See the component chapter in this manual before using any of the relevant TRMs. The component information in this manual is specifically provided for use with the subsystem.

### **Chapter 1** Introduction

– Note –––

Read this chapter for an introduction to the chip. It contains a brief description of each of the main components that the chip contains.

### Chapter 2 Functional Overview

Read this chapter for a description of the top-level functionality of the chip. It contains a block diagram of the development chip and describes the function of each block in detail.

### Chapter 3 Programmer's Model

Read this chapter for a description of how to program the chip registers.

# Appendix A Electrical and Physical Characteristics

Read this chapter for a description of the electrical and physical characteristics of the development chip.

### **Appendix B** Component Revision Status

Read this chapter for a list of the revision status of each of the components included in the chip.

**Glossary** Read the Glossary for definitions of terms used in this manual.

# Conventions

Conventions that this manual can use are described in:

- Typographical

- *Timing diagrams* on page xvi

- Signals on page xvi

- *Numbering* on page xvii.

# Typographical

The typographical conventions are:

| italic            | Highlights important notes, introduces special terminology, denotes internal cross-references, and citations.                                                                                                                                                          |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bold              | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.                                                                                                                                  |

| monospace         | Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.                                                                                                                                                            |

| <u>mono</u> space | Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.                                                                                                                                |

| monospace italic  | Denotes arguments to monospace text where the argument is to be replaced by a specific value.                                                                                                                                                                          |

| monospace bold    | Denotes language keywords when used outside example code.                                                                                                                                                                                                              |

| < and >           | <ul> <li>Angle brackets enclose replaceable terms for assembler syntax where they appear in code or code fragments. They appear in normal font in running text. For example:</li> <li>MRC p15, 0 <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd></li> </ul> |

The Opcode\_2 value selects the register that is accessed.

# **Timing diagrams**

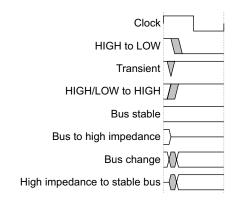

The figure named *Key to timing diagram conventions* explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

#### Key to timing diagram conventions

# Signals

The signal conventions are:

| Signal level | The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means HIGH for active-HIGH signals and LOW for active-LOW signals. |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

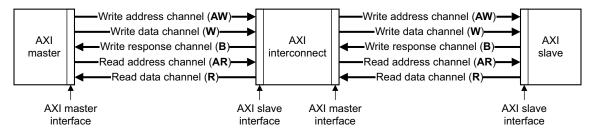

| Prefix A     | Denotes <i>Advanced eXtensible Interface</i> (AXI) global and address channel signals.                                                                                  |

| Prefix B     | Denotes AXI write response channel signals.                                                                                                                             |

| Prefix C     | Denotes AXI low-power interface signals.                                                                                                                                |

| Prefix H     | Denotes Advanced High-performance Bus (AHB) signals.                                                                                                                    |

| Prefix n     | Denotes active-LOW signals except in the case of AXI, AHB, or <i>Advanced Peripheral Bus</i> (APB) reset signals.                                                       |

| Prefix P | Denotes APB signals.                     |  |

|----------|------------------------------------------|--|

| Prefix R | Denotes AXI read channel signals.        |  |

| Prefix W | Denotes AXI write channel signals.       |  |

| Suffix n | Denotes AXI, AHB, and APB reset signals. |  |

# Numbering

The numbering convention is:

#### <size in bits>'<base><number>

This is a Verilog method of abbreviating constant numbers. For example:

- 'h7B4 is an unsized hexadecimal value.

- 'o7654 is an unsized octal value.

- 8'd9 is an eight-bit wide decimal value of 9.

- 8'h3F is an eight-bit wide hexadecimal value of 0x3F. This is equivalent to b00111111.

- 8'b1111 is an eight-bit wide binary value of b00001111.

# **Further reading**

This section lists publications by ARM Limited, and by third parties.

ARM Limited periodically provides updates and corrections to its documentation. See http://www.arm.com for current errata sheets, addenda, and the Frequently Asked Questions list.

# **ARM** publications

This manual contains information that is specific to the ARM1176JZF development chip. See the *Intelligent Energy Controller Technical Reference Manual* (ARM DDI 0304) for other relevant information.

—— Note ———

See the component chapter in this manual before using any of the relevant TRMs. The component information in this manual is specifically provided for use with the ARM1176JZF development chip.

• ARM1176JZF Development Chip Electrical Specification (PR168-PRDC-004363)

- Flow Guidelines for Generating an IEM Enabled ARM1176 Macrocell (PR114-PRDC-005381)

- Generic Interrupt Controller Architecture (PRD03-GENC-004392).

# Other publications

This section lists relevant documents published by third parties:

• *Adaptive Power Controller – APC1 – (SY751)*, National Semiconductor (SY751-DA-03001).

# Feedback

ARM Limited welcomes feedback on the ARM1176JZF development chip subsystem and its documentation.

# Feedback on this product

If you have any comments or suggestions about this product, contact your supplier giving:

- the product name

- a concise explanation of your comments.

# Feedback on this manual

If you have any comments on this manual, send email to errata@arm.com giving:

- the title

- the number

- the relevant page number(s) to which your comments apply

- a concise explanation of your comments.

ARM Limited also welcomes general suggestions for additions and improvements.

Preface

# Chapter 1 Introduction

This chapter describes the general properties and functionality of the chip and contains the following sections:

- About the ARM1176JZF Development Chip on page 1-2

- *Component summary* on page 1-3

- *Technology summary* on page 1-5.

# 1.1 About the ARM1176JZF Development Chip

The chip is a TSMC, 130nm generic implementation of the following:

- ARM1176JZF core

- Level 2 Cache Controller (L2CC)

- CoreSight ETM11

- peripherals supporting TrustZone, CoreSight, and *Intelligent Energy Management* (IEM).

The ARM1176JZF, L2CC and CoreSight ETM11 operate with dynamic voltage and frequency scaling under control of the ARM IEM system.

The IEM control system comprises the following:

- ARM Intelligent Energy Controller (IEC)

- National Semiconductor's Advanced Power Controller (APC1)

- a custom, SoC-specific, *Dynamic Clock Generator* (DCG).

Additionally, dynamic memory controller, PL340, is implemented with a 32-bit 166MHz Mobile DDR interface.

This document defines the functional specification and programmers view of the Development Chip. The ARM1176JZF Development Chip Requirements Capture [1] summarizes the features.

Full specifications are provided for modules created specifically for the design, such as the DCG and System controller. Modifications of incoming IP are also documented.

Implementation guidelines describing the IEM enabling of the application processor sub-system is presented in a separate document [4].

# 1.2 Component summary

The chip consists of the following components:

- ARM1176JZF Development Chip with 32KB, I and D, caches and 8KB, I and D, TCMs

- core, RAM and SoC voltage domains.

- level 2 cache and controller with 128KB unified cache

- clocked 1:1 with the core, I & R/D buses

- core, RAM and SoC voltage domains.

# 1.2.1 CoreSight components

The chip consists of the following CoreSight components:

- CoreSight ETM11

- clocked 1:1 with the core

- core and SoC voltage domains.

- CoreSight ETB11, 8KB memory

- TPIU for off-chip trace port, 32 bits implemented

- replicators to TPIU, ETB11 and off-chip ATB port.

- cross-trigger interface and ATB bus brought off-chip for multiple core debug support

- Debug Access Port (DAP)

- access ports: APB, CoreSight, JTAG, ARM1176JZF Development Chip, AHB, system access

- debug ports: JTAG.

# 1.2.2 System components

The chip consists of the following system components:

- Color LCD controller

- *Dynamic Memory Controller* (DMC), 32-bit mobile DDR at 166MHz. Memory interface operates synchronously to AXI clock for lowest latency

- Static Memory Controller (SMC), 32-bit

- UARTs, SSP, and GPIO

- RTC, timers & watchdog

- System controller

- Generic Interrupt Controller (GIC) and TrustZone Interrupt Controller (TZIC)

• Configurable AXI Interconnect (CAI).

# 1.2.3 TrustZone components

The chip consists of the following TrustZone components:

- TrustZone System Protection Controller, APB3 peripheral

- 16KB non-volatile RAM for boot-ROM emulation

- 512KB L3 RAM, configurable secure region watermark

- CAI modified to incorporate:

- DMC and SMC have per chip-select, or 64MB region, security blocking

- AXI master port has configurable security and four TrustZone decodes exported

- AXI slave port has configurable security blocking of **AxPROT**[1]

- CLCDC has configurable security enabling of **AxPROT**[1].

# 1.2.4 Intelligent Energy Manager (IEM) components

The chip consists of the following IEM components:

- Intelligent Energy Controller (IEC), APB3 peripheral

- dynamic clock generation and reset controller, APB3 peripheral

- Dynamic Voltage Controller (DVC), APB3 peripheral, National Semiconductor *Advanced Power Controller1* (APC1)

- *Hardware Performance Monitor* (HPM), National Semiconductor.

# 1.3 Technology summary

The technology that the chip uses has the following characteristics:

- TSMC 130nm generic process, nine layer metal, the 9th layer is reserved for flipchip bumps:

- 10 14mm silicon die

- IEM subsystem target: 332MHz

- DDR, AXI, and ATB Target: 166MHz

- APB Target: 83MHz

- 1.2V core, 3.3V input and output

- 1.8V LVCMOS for mobile DDR input and output.

- packaging:

- 1400 ball fully populated, flipchip

- package ball pitch: 1mm

- package bump pitch: 200μm.

- IEM subsystem libraries:

- ARM Q3 cell library

- ARM r2 RAMs, for the ARM1176JZF core

- Artisan HS HC RAMs, for L2CC, characterized by Artisan for IEM operation.

- SoC libraries:

- Artisan Sage-HS cell library

- Artisan HS HC RAMs

- Artisan supplied input and output libraries: 3.3V and 1.8V.

- third-party IP:

- Artisan 533MHz de-skew PLL, three instances, one de-skew

- Artisan 800Mbs DLL, one master & four slaves

- National Advanced Power Controller (APC1) and Hardware Performance Monitor (HPM) soft IP.

Introduction

# Chapter 2 Functional Overview

This chapter describes the functionality of the chip and contains the following sections:

- About the ARM 1176JZF Development Chip on page 2-2

- *System controller* on page 2-26

- Intelligent Energy Management (IEM) on page 2-38

- Generic Interrupt Controller (GIC) on page 2-64

- *CoreSight* on page 2-65

- *Clock sources and domains* on page 2-72.

# 2.1 About the ARM 1176JZF Development Chip

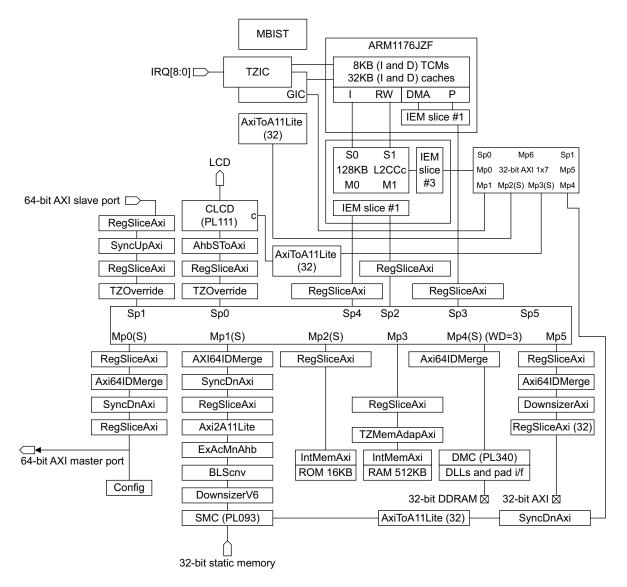

This section describes the chip. Figure 2-1 shows a top-level block diagram of the chip.

# Figure 2-1 ARM1176JZF Development Chip block diagram

Figure 2-2 on page 2-3 shows the IEM subsystem in detail.

### Figure 2-2 IEM subsystem

In Figure 2-2, you can configure the following components to be secure:

- Sp0

- AhbSToAxi

- RegSliceAxi

- TZOverdrive.

CLCD (PL111)

- Sp1 RegSliceAxi

- SyncUpAxi

- TZOverdrive.

- Sp2 RegSliceAxi.

- Sp3 RegSliceAxi.

- Sp4 RegSliceAxi.

- MpO(S) RegSliceAxi.

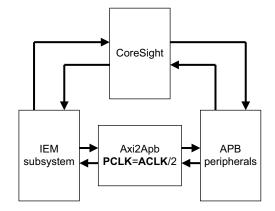

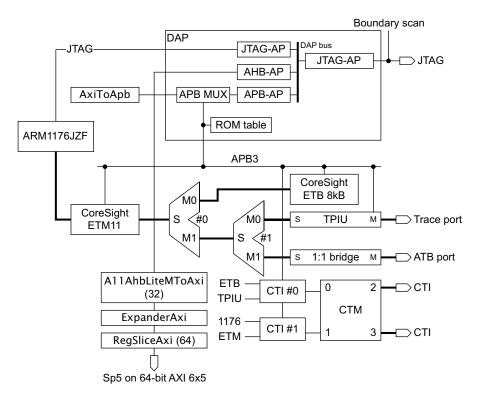

Figure 2-3 shows the CoreSight subsystem in detail.

### Figure 2-3 CoreSight subsystem

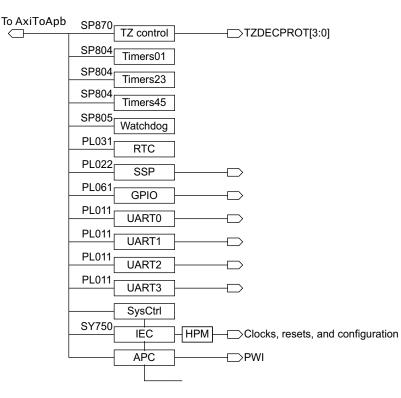

Figure 2-4 on page 2-5 shows the APB peripherals in detail.

### Figure 2-4 APB peripherals

This section contains the following subsections:

- *Processor subsystem* on page 2-6

- Level 2 Cache Controller on page 2-7

- Intelligent Energy Management (IEM) on page 2-8

- *Voltage domains* on page 2-8

- AXI infrastructure on page 2-9

- *Clocking* on page 2-15

- *Interrupt logic* on page 2-16

- *Interrupt sources* on page 2-18

- On-chip RAM on page 2-19

- *Exclusive access* on page 2-20

- *External static memory control* on page 2-20

- *External dynamic memory control* on page 2-21.

# 2.1.1 Processor subsystem

The processor sub-system consists of the following:

- ARM1176JZF core

- L2CC

- CoreSight ETM11.

The processor sub-system is subject to dynamic performance control of the core voltage domain. Level1 RAM, within the ARM1176JZF core, is a separate voltage domain that scales with the core voltage. It is isolated from it to enable data retention in dormant mode. Because the L2CC does not support data retention of Level2 RAM, the Level2 RAMs are supplied by the core voltage.

The IEM sub-system also contains:

- memory-BIST engines for the ARM1176JZF core and L2CC

- a Hardware Performance Monitor (HPM) to monitor the dynamic voltage

- ring oscillators to indicate voltage levels for diagnostic purposes.

The IEM sub-system is developed as a hard macro, with an approximate size of 6mm wide by 4mm high. Its primary purpose is to encapsulate all of the IEM enabling complexity, IP, and techniques within a macro.

All interfaces to and from the constant-voltage SoC domain are designed to operate asynchronously, and synchronously as appropriate. They incorporate level shifters and clamps. The whole IEM, application processor, sub-system supports:

- Run and standby modes, that is the IEM dynamic performance control of voltage and frequency.

- Dormant mode. The L1 RAMs are held at the retention voltage, the rest of the IEM sub-system is held at 0V, and the inputs and outputs are held clamped at the reset state.

- Shutdown mode. The whole IEM sub-system is held at 0V, and the inputs and outputs are held clamped at the reset state.

The ARM1176JZF DMA and peripheral port AXI buses incorporate specific synchronizing structures called IEM slices. These include *First In First Out* (FIFOs) to isolate the high-latency of the asynchronous AXI interface from the core. Similarly, the master ports and configuration port of the L2CC are isolated from AXI using the same FIFO-equipped slices.

The L2CC slave port 0, Sp0, is connected to the ARM1176JZF instruction port, and the L2CC slave port 1, Sp1, is connected to the ARM1176JZF data read and write port. These interfaces operate synchronously at a 1:1 clocking ratio.

The ARM1176JZF memories are 32KB I and D caches, and 8KB I and D *Tightly Coupled Memories* (TCMs).

Level2 cache is 128KB unified cache and is 8-way associative, so each way is 16KB. Tag parity and data parity RAMs are not implemented.

# 2.1.2 Level 2 Cache Controller

The L2CC is configured to use two master ports that interface to Level3 memory. This configuration enables you to position instruction fetches, that is high bandwidth demand on the DMC, at a lower arbitration priority than data and other system bus masters. Table 2-1 lists the L2C master port transactions to AXI.

| Table 2-1 | L2C master | port transactions |

|-----------|------------|-------------------|

|-----------|------------|-------------------|

| Master port 0                                     | Master port 1                                        |  |

|---------------------------------------------------|------------------------------------------------------|--|

| Non-cached reads and non-buffered stores from Sp0 | Non-cached reads and non-buffered stores from Sp1    |  |

| Linefills with LF buffer 0                        | Linefills with LF buffer 1                           |  |

| Buffered stores with write buffer                 | Buffered stores with write buffer or eviction buffer |  |

| Write allocations with LF buffer 0                | Write allocations with LF buffer 1                   |  |

At reset, the L2CC is disabled, bypassed. To enable the L2C, you must write to the L2C control register, Register 1, using a read-modify-write sequence.

—— Note ———

- Only a secure access can enable or disable the L2CC.

- Security control is performed on a register-by-register basis within the L2C AXI configuration port.

When the L2CC is not enabled, transactions on Sp0 and Sp1 pass straight through to the L3 memory system via the Mp0 and Mp1 master ports, respectively. There is a penalty introduced by having the L2C disabled and in the path. This penalty is twice the depth of the internal L2C pipeline. it is made up of once for slave to master, and the other for master to slave. The minimum L2C latency is one **CLK** cycle on the slave port, one **ACLK** cycle on the master port, and potentially one **ACLK** cycle for bus.

# 2.1.3 Intelligent Energy Management (IEM)

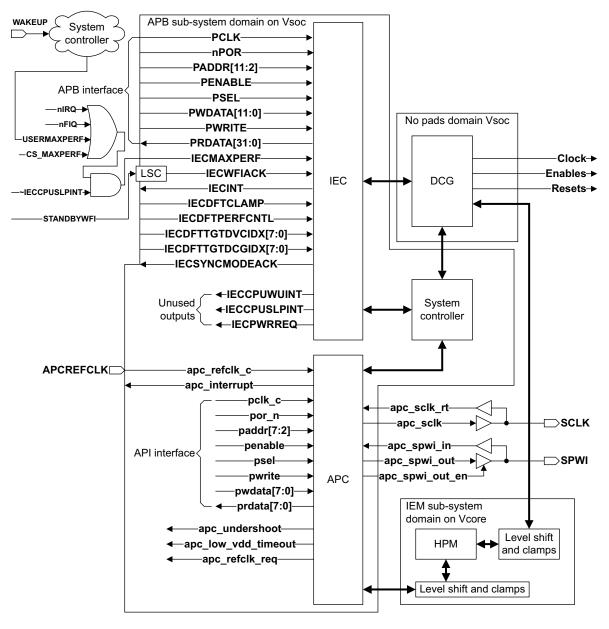

*Intelligent Energy Management* (IEM) control systems allow you to vary the frequency and core voltage in the IEM, application processor, sub-system domain. The system is based around the ARM *Intelligent Energy Controller* (IEC). The *Advanced Power Controller* (APC1) from National Semiconductor provides voltage control, and a SoC-specific *Dynamic Clock Generator* (DCG) provides frequency control.

DCG functionality includes *Design For Test* (DFT), clock, reset, power and clamp controls, including power and, L1 memory clamp sequencing to support the following IEM and core modes.

# **IEC** operation modes

The following are the IEC operational modes:

- Dynamic Voltage Scaling (DVS)

- DVS emulation.

## Application processor sub-system power modes

The following are the application processor sub-system power modes:

- run mode

- standby mode

- shutdown mode

- dormant mode.

— Note — —

The IEM implementation defaults to use one frequency per voltage performance level. Even though the IEC configuration is normally hard-wired, the configuration is soft in the development chip. Its default values at reset are stored in registers in the system controller. This enables additional exploration of multiple frequencies per voltage. Three PLLs perform dynamic clock generation and system clocks due to the flexibility the development chip requires.

### 2.1.4 Voltage domains

The chip contains the following voltage domains:

- IEM subsystem voltage domains on page 2-9

- SoC voltage domains on page 2-9.

# IEM subsystem voltage domains

The IEM subsystem contains the following voltage domains:

V<sub>core</sub> Core voltage for the ARM1176JZF core, CSETM11 and L2CC, plus MBIST logic. This voltage domain includes the L2C RAMs and is varied dynamically by the IEM control system between 0V and 1.2V.

V<sub>ram</sub> RAM voltage for the RAMs within the ARM1176JZF core. This voltage is held at V<sub>core</sub> except when operating in dormant mode when the RAMs are held in retention voltage, that is approximately 0.6V.

# SoC voltage domains

The SoC contains the following voltage domains:

| V <sub>soc</sub>     | 1.2V constant SoC voltage.                                                                                                                 |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>pllfa</sub>   | Fixed frequency PLL digital, 1.2V, and analog, 3.3V, rails. The analog rail is brought out of the SoC and isolated from all other rails.   |

| V <sub>pll1</sub>    | Dynamic frequency PLL digital, 1.2V, and analog, 3.3V, rails. The analog rail is brought out of the SoC and isolated from all other rails. |

| V <sub>pll2</sub>    | Dynamic frequency PLL digital, 1.2V, and analog, 3.3V rails. The analog rail is brought out of the SoC and isolated from all other rails.  |

| V <sub>dll</sub>     | DLL digital, 1.2V, and analog, 3.3V rails. The analog rail is brought out of the SoC and isolated from all other rails.                    |

| V <sub>io</sub>      | 3.3V input and output supply rail for all inputs and outputs other than MDDR.                                                              |

| V <sub>ddr</sub>     | 1.8V input and output supply rail for MDDR.                                                                                                |

| V <sub>ddr-pre</sub> | 2.5V supply rail for the MDDR pre-driver.                                                                                                  |

# 2.1.5 AXI infrastructure

The infrastructure is created using the *Configurable AXI Interconnect* (CAI) PL300 tool. Separate 64-bit and 32-bit interconnect structures exist to partition the main L3 memory and peripherals. A link exists between the 64-bit and 32-bit structures to primarily enable an external master, or the ARM1176JZF RW channel, to access peripheral space.

Conversion to and from AHB is performed where necessary to support legacy AHB components. All bus matrices feature full connectivity. All masters can access all slaves, subject to memory map, remap and run-time security configuration.

The 64-bit infrastructure has a  $6_6$ , fully wired structure, accommodating all system masters. All six slave ports have an interleaved write depth of one. The six master ports have interleaved write depths of one, except for Mp4. Mp4 is connected to the DMC and has an interleaved write depth of 3.

The 32-bit infrastructure has a  $2\times7$  structure. Its purpose is to connect all the system peripherals and configuration ports to the ARM1176JZF 32-bit peripheral port and to the 64-bit AXI interconnect. This facilitates external master access to peripheral space. All slave and master ports have an interleaved write depth of one.

Accesses to undefined or reserved AXI memory regions receive a DECERR response that results in a prefetch or data abort, defined by the access type.

This design does not use the AXI low power interface, c-channel, except as a work around for implementing Standby Wait For Interrupt on the L2CC in the IEM sub-system. See *Intelligent Energy Management (IEM)* on page 2-38.

# 64-bit AXI arbitration

Each AXI master port has an arbiter that mediates between the slave ports in the interconnect. The arbitration is identical for all master ports. The arbitration priorities listed in Table 2-2 lists are the development chip defaults.

| Slave port priority | Master                 | Alternative master          |

|---------------------|------------------------|-----------------------------|

| 0 = highest         | CLCDC                  | -                           |

| 1                   | AXI off-chip master    | -                           |

| 2                   | ARM1176JZF data        | Level 2 cache master port 1 |

| 3                   | ARM1176JZF DMA         | -                           |

| 4                   | ARM1176JZF instruction | Level 2 cache master port 0 |

| 5 = lowest          | CoreSight debug        | -                           |

| Table 2-2 64-bit AXI infrastructure | arbitration priority |

|-------------------------------------|----------------------|

|-------------------------------------|----------------------|

— Note ———

The arbitration this section describes is the system default and is effective at reset. Registers exist within the system controller to enable you to configure the arbitration priority. See *SoC configuration* on page 3-7.

Although the configurable arbitration priority affects only the address channel, the master ports prioritize data based on the order the addresses are received.

— Note —

The IDs are not altered when the arbitration is modified. IDs are based on the default arbitration priority this section describes.

## AXI IDs

Master ID in the system is formed by the configurable interconnect as follows:

ID = {max id\_bit\_width of any master, binary number of master}

The CAI appends the master ID number, a function of the default arbitration priority, to the ID from a master. Table 2-3 lists the master IDs visible in the 64-bit domain.

| Master                 | Slave port priority | ID width | AXI ID, slave side             |

|------------------------|---------------------|----------|--------------------------------|

| CLCDC                  | 0 = highest         | 0        | 00000-000                      |

| AXI off-chip master    | 1                   | 5        | 00000-00111111-001             |

| ARM1176JZF data        | 2                   | 1        | 00000-010 (S0), 00001-010 (S1) |

| ARM1176JZF DMA         | 3                   | 0        | 00000-011                      |

| ARM1176JZF instruction | 4                   | 0        | 00000-100                      |

| CoreSight debug        | 5 = lowest          | 0        | 00000-101                      |

Table 2-3 64-bit AXI make-up

There are no ID bits between the ARM1176JZF, I and RW ports, and the L2CC, S0 and S1 ports. Bit [0] of the L2CC M1 port ID bus is wired to the CAI. There are five bits of ID from the AXI slave port to enable the MPCore or Cortex-A8 test chips to be attached to this SoC. The ID width becomes nine bits if the 32-bit AXI matrix is cascaded with the 64-bit.

The L2CC configuration port only accepts 8-bit ID fields. Reducing the ID width and bit mapping, provides two benefits:

- enhanced use of the PL340 Quality of Service (QoS), continuous 4-bit ID window

- possible to reduce the pin count of the off-chip AXI master port.

Table 2-4 lists the ID merge functional values.

| Master                           | AXI ID Value                     | Merged ID Value     |

|----------------------------------|----------------------------------|---------------------|

| CLCDC                            | 00000-000                        | 000000              |

| ARM1176JZF Data S0               | 00000-010                        | 010111              |

| ARM1176JZF Data S1               | 00001-010                        | 010010              |

| ARM1176JZF DMA                   | 00000-011                        | 100011              |

| ARM1176JZF instruction           | 00000-100                        | 000100              |

| CoreSight debug                  | 00000-101                        | 110101              |

| AXI off-chip master, ExtSlv port | 00000-00111111-001 (= ABCDE-001) | AB1CDE <sup>a</sup> |

|                                  |                                  |                     |

Table 2-4 ID merge function

a. ABCDE = xID\_ExtSlv[5:0], giving merged ID values of 8-15, 24-31, 40-47, and 56-63.

The DMC (PL340) has a QoS feature that can window on four contiguous ID bits and enables QoS settings for 16 masters. Table 2-5 lists the DMC QoS options, values used by moving the DMC QoS window over the merged ID field.

| Master             | QoS using<br>[3:0] | Value | QoSusing<br>[4:1] | Value | QoS using<br>[5:2] | Value |

|--------------------|--------------------|-------|-------------------|-------|--------------------|-------|

| CLCDC              | 0000               | 0     | 0000              | 0     | 0000               | 0     |

| ARM1176JZF data S0 | 0111               | 7     | 1011              | 11    | 0101               | 5     |

| ARM1176JZF data S1 | 0010               | 2     | 1001              | 9     | 0100               | 4     |

| ARM1176JZF DMA     | 0011               | 3     | 0001              | 1     | 1000               | 8     |

## Table 2-5 DMC QoS options

| Master                           | QoS using<br>[3:0] | Value             | QoS using<br>[4:1] | Value                   | QoS using<br>[5:2] | Value                                        |

|----------------------------------|--------------------|-------------------|--------------------|-------------------------|--------------------|----------------------------------------------|

| ARM1176JZF instruction           | 0100               | 4                 | 0010               | 2                       | 0001               | 1                                            |

| CoreSight debug                  | 0101               | 5                 | 1010               | 10                      | 1101               | 13                                           |

| AXI off-chip master, ExtSlv Port | 1CDE               | 8-15 <sup>a</sup> | B1CD               | 4-7, 12-15 <sup>b</sup> | AB1C               | 2-3,<br>6-7,<br>10-11,<br>14-15 <sup>c</sup> |

## Table 2-5 DMC QoS options (continued)

a. Aliasing over bits xID\_ExtSlv[5:4].

b. Aliasing over bits xID\_ExtSlv[5] and [0].

c. Aliasing over bits xID\_ExtSlv[1:0].

Table 2-6 lists the 7-bit master IDs visible in the 32-bit domain.

| Master                    | Slave port priority | AXI ID, slave side                                                                                                                                                                |

|---------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARM1176JZF peripheral     | 0 = highest         | 000000-0                                                                                                                                                                          |

| AXI 64-bit infrastructure | 1 = lowest          | 000000-1, CLCD<br>010111-1, ARM data, S0<br>010010-1, ARM data, S1<br>100011-1, ARM DMA<br>000100-1, ARM instruction<br>110101-1, CoreSight debug<br>001000-1111111-1, AXI master |

|                           |                     | ,                                                                                                                                                                                 |

#### Table 2-6 32-bit AXI ID make-up

# Security configuration

Each CAI master port is assigned either a secure or non-secure attribute through a set of inputs controlled by the *TrustZone Protection Controller* (TZPC). Figure 2-1 on page 2-2 shows shaded areas in the system block diagram. These indicate ports and peripherals you can configure to be secure.

— Note —

At reset, all CAI master ports and peripherals that you can configure to be secure, under control of the TZPC, are set as secure.

The AXI infrastructure rejects non-secure, NS, transactions to secure, S, ports or peripheral, and returns a DECERR response. Writes fail, but the write burst must complete before the AXI infrastructure returns a DECERR response. Reads also fail in a similar way, with a zero value returned and a DECERR response. The AXI infrastructure responds after the first read, when the master aborts the rest of the burst.

You can configure the off-chip AXI master port to be either fully secure or non-secure. Four security configuration bits, **DECPROT**, from the TZPC, are exported off-chip as sideband signals to the AXI Master port **TZPROTMAXI[3:0]**. These are useful to AXI peripheral developers,. These enable you to construct off-chip, either a single secure peripheral or an additional CAI matrix, with up to four separate secure regions.

Security for the AXI Slave port is configurable under control of the TZPC as a gating function of secure transactions. Secure transactions can be gated from entering the AXI infrastructure.

Although the CLCDC has no security awareness, as part of the AHB to AXI conversion, you can configure transactions as secure under control of the TZPC. You can also configure the CLCDC configuration port to be secure to complete the TrustZone protection of the peripheral.

You can configure the DMC and SMC memory space to be either secure or non-secure in 64MB regions under control of the TZPC. Each of the eight SMC chip select regions is 64MB. They are potentially either a half or a full DMC chip select region. You can also configure the DMC and SMC configuration ports to be secure to complete the TrustZone protection of the peripherals.

# AXI off-chip slave interface

A 64-bit AXI slave port is implemented that enables off-chip masters to access the on-chip peripherals, memory controllers and the AXI master port. It has an interleaved write depth of one.

The interface is synchronous. It supports all integer clocking ratios from 1:1 to 1:8 between the external clock and SoC AXI clock.

The AXI off-chip slave port operates synchronously with **PLLREFCLK**, the main PLL input clock. This synchronicity is achieved by de-skewing the AXI SoC clock to **PLLREFCLK**, the board-level clock.

Feedback for the de-skew PLL is taken from this off-chip interface.

Maximum flexibility for TrustZone support is provided because the AXI slave port **AxPROT[1]** signals are input to the SoC. You can override these signals to gate out secure transactions under control of the TZPC.

The ARM1176JZF Development Chip Electrical Specification describes the interface port signal list.

# AXI off-chip master interface

A 64-bit AXI master port is implemented, that enables access to off-chip slaves from on-chip masters and the AXI slave port. It has an interleaved write depth of one. The interface is synchronous and supports all integer clocking ratios of 1:1 to 1:8 between the external clock and the SoC AXI clock.

—— Note ———

These ratios are independent of those set for the AXI slave port. The AXI off-chip Master port operates synchronously with **PLLREFCLK**, the main PLL input clock. This is achieved by de-skewing the AXI SoC clock to **PLLREFCLK**, the board-level clock.

A clock is exported at the frequency of operation of this port. You can configure the master port to be secure, under control of the TZPC, enabling development of secure peripherals. Alternatively, you can configure the port to be non-secure and configure the master ports of an external extended sub-system independently to be secure or non-secure. To facilitate this, four **DECPROT** signals are output from the TZPC as side-band signals to the AXI master port.

# 2.1.6 Clocking

The ARM1176JZF core, L2CC, and ETM11 operate at a variable frequency, under control of the IEM control system, up to a target frequency of 332MHz. The processor subsystem operates synchronously and asynchronously to the AXI infrastructure.

Synchronous operation, relating to an IEM performance target of 100%, is supported with core:AXI clock ratios of 2:1 and 4:1 through a static configuration at reset. This uses balanced clocks and a common enable.

The target clock frequencies for the system configuration are:

- IEM subsystem at 332MHz

- AXI clock at 166MHz

- PCLK at 83MHz.

Th clocking strategy includes components that operate at different clock frequencies:

## **Operating at 166MHz**

AXI infrastructure and bus masters, excluding the processor subsystem

- dynamic and static memory controllers, on-chip RAMs

- AMBA Trace Bus (ATB) for CoreSight.

## **Operating at 83MHz**

• APB peripherals, including the DMC configuration port.

You can configure the SMC external memory clock to operate at ACLK, ACLK÷2 or ACLK÷3, as part of the SoC static configuration at reset. SyncFlash requirements are up to 54MHz. The DMC external clock operates at 166MHz, synchronously to ACLK.

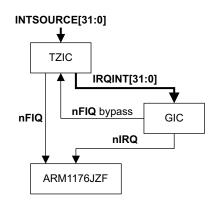

## 2.1.7 Interrupt logic

In the development chip, secure interrupt sources are routed to the **nFIQ** input on the core. Non-secure sources are routed to the **nIRQ** input on the core. A TZIC is implemented to enable and control routing to the TZIC or non-secure-IC logic as appropriate for the application.

All interrupt sources, on-chip and off-chip, are routed to the TZIC. This enables a dynamic interrupt configuration to be defined as part of the secure boot process. It is the responsibility of the end user to ensure that a secure interrupt is generated only by a securely decoded peripheral.

## Secure interrupt controller

The task of the TZIC is to create the secure interrupt **nFIQ** from the raw interrupt sources. It must also stop the sources chosen for the **nFIQ** from propagating to the non-secure interrupt controller. This creates a secure interrupt that cannot be controlled or influenced from the non-secure side of a TrustZone system. To the non-secure side, this is a non-maskable interrupt.

Although you should configure the TZIC as secure in a TrustZone aware system, you can configure it as non-secure.

## Secure interrupt flow

The following flow shows how the TZIC uses interrupts to force the operating system to enter secure state:

- 1. A TZIC selected interrupt occurs and **nFIQ** is asserted.

- 2. The ARM core branches to the **FIQ** interrupt vector.

- 3. The ARM core switches into monitor mode and stacks the current program status.

- 4. The **FIQ** handler switches the operating system into secure state.

- 5. The interrupt service routine executes in secure state.

- 6. The requesting interrupt in the peripheral is cleared.

7. The system returns to non-secure state and re-enables interrupts.

# Non-secure interrupt controller

The non-secure interrupt controller creates the non-secure interrupt **nIRQ** from the interrupt sources that the TZIC enables. The non-secure interrupt controller implemented in the development chip is the GIC. This resides in non-secure memory space and provides user mode interrupt control. Because of the core architecture, the **nIRQ** does not provide a path into the secure side of a TrustZone system.

You can completely bypass the TZIC. this enables the GIC to operate as a non-secure interrupt controller with control of **nIRQ** and **nFIQ**. For this configuration, **nFIQ** from the GIC is fed to the TZIC, enabling a bypass to the core.

## Non-secure interrupt flow

The following is the flow for a non-secure interrupt:

- 1. A GIC selected interrupt occurs and **nIRQ** is asserted.

- 2. The ARM core branches to the FRQ interrupt vector.

- 3. The Interrupt Service Routine executes in non-secure state.

- 4. The requesting interrupt in the peripheral is cleared.

- 5. The system re-enables interrupts.

Figure 2-5 shows the structure for secure and non-secure interrupts.

## Figure 2-5 Secure and non-secure interrupt structure

# 2.1.8 Interrupt sources

Table 2-7 lists the interrupt sources implemented in the chip. **EXTINTSOURCE[8:0]** enable end-user developmen. They are primary inputs to the SoC. These inputs are synchronized to **ACLK** using a two-stage synchronizer. Similarly, the L2CC combined interrupt and the four interrupts from the ARM1176JZF Development Chip are also synchronized to **ACLK**.

The GIC sees these inputs as interrupt sources 32-63, but the TZIC sees them as 0-31 as Table 2-7 shows.

|                  | •          |             |

|------------------|------------|-------------|

| Interrupt source | GIC source | TZIC source |

| EXTINTSOURCE[8]  | 63         | 31          |

| EXTINTSOURCE[7]  | 62         | 30          |

| EXTINTSOURCE[6]  | 61         | 29          |

| EXTINTSOURCE[5]  | 60         | 28          |

| EXTINTSOURCE[4]  | 59         | 27          |

| EXTINTSOURCE[3]  | 58         | 26          |

| EXTINTSOURCE[2]  | 57         | 25          |

| EXTINTSOURCE[1]  | 56         | 24          |

| EXTINTSOURCE[0]  | 55         | 23          |

| CS_IRQ           | 54         | 22          |

| UART_3           | 53         | 21          |

| UART_2           | 52         | 20          |

| UART_1           | 51         | 19          |

| UART_0           | 50         | 18          |

| SSP              | 49         | 17          |

| GPIO             | 48         | 16          |

| CLCDC            | 47         | 15          |

| RTC              | 46         | 14          |

| L2CC             | 45         | 13          |

|                  |            |             |

#### Table 2-7 Interrupt source allocation

| Interrupt source        | GIC source | TZIC source |

|-------------------------|------------|-------------|

| IEC                     | 44         | 12          |

| APC                     | 43         | 11          |

| Timers_2                | 42         | 10          |

| Timers_1                | 41         | 9           |

| Timers_0                | 40         | 8           |

| Core PMU IRQ            | 39         | 7           |

| Core Ext. Error DMA IRQ | 38         | 6           |

| Core secure DMA IRQ     | 37         | 5           |

| Core DMA IRQ            | 36         | 4           |

| Comms Tx                | 35         | 3           |

| Comms Rx                | 34         | 2           |

| Software interrupt      | 33         | 1           |

| Watchdog                | 32         | 0           |

## Table 2-7 Interrupt source allocation (continued)

## 2.1.9 On-chip RAM

Two 64-bit wide on-chip RAMs are implemented. Both feature a write depth of one, no outstanding addresses, and a single wait state for reads.

One 16KB RAM is implemented for secure boot ROM emulation. You can configure it to be fully secure or non-secure under control of the TZPC. The RAM control inputs are qualified with SoC power-on-reset to prevent corruption during reset sequences.

At reset, the RAM defaults to secure. A second 512KB RAM is implemented for general-purpose application use. This has a secure wrapper for TrustZone support enabling the RAM to be partitioned between secure and non-secure regions under control of the TZPC. You can size the secure partition in 4KB increments, from the RAM base address, up to the maximum of 512KB. A non-secure access to the secure region returns a DECERR. At reset, the RAM defaults to being a single, fully secure region.

## 2.1.10 Exclusive access

Exclusive access monitoring is provided within the DMC and is added in front of PL093 using an AHB Exclusive Access Monitor.

The Dynamic Memory Controller, PL340, keeps track of up to four outstanding exclusive accesses. These are not programmed, but stored on a rolling basis.

The Static Memory Controller, PL093, has two exclusive accesses tracked. You can configure the master IDs at run time from registers within the system controller.

—— Note ———

There is no exclusive access monitoring provision for either of the two on-chip RAMs.

## 2.1.11 External static memory control

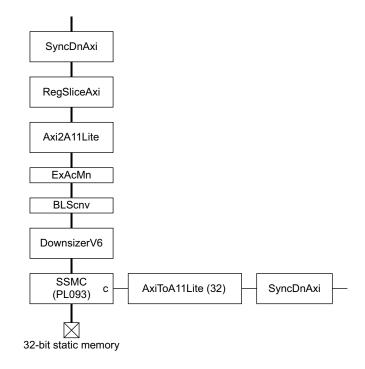

This memory is implemented to support eight chip selects of 64MB each with 32-bit data.

The SMC is clocked at 1:1 or 1:2 with ACLK, ACLKSMC, using a SyncDnAxi bridge to provide the optimal external clock frequency for synchronous devices of up to 54MHz.

The external synchronous memory clock, **SMMEMCLK** can run at 1:1, 1:2 or 1:3 with **ACLKSMC**. Both **ACLKSMC** and **SMMEMCLK** clock ratios are configured by static configuration. Figure 2-6 on page 2-21 shows the AXI to AHB logic, and the clocking conversion logic.

Figure 2-6 SMC AXI interface logic

## 2.1.12 External dynamic memory control

The *Dynamic Memory Controller* (DMC), PrimeCell PL340, is implemented with a 32-bit Mobile DDR interface. It operates at 1.8V LVCMOS thresholds and a target clock rate of 166MHz. The standard for 1.8V Mobile DDR is 1.8V LVCMOS, rather than SSTL\_18.

The clock output provided on PL340 is replicated to create an inverted clock output to support Mobile DDR,. These two stages form a differential clock output that is closely skew controlled. The pad interface is clocked synchronously with **ACLK** to minimize latency and reduce the clocking complexity within the SoC.

The PL340 enables you to configure the base and range addresses of each chip select. Although the ARM1176JZF SoC implements four chip selects, fewer can be used to satisfy the maximum capacitive loading of any DDR input or output of 10pF.

# Options

The following device configurations are supported:

## **Option 1**

- four 512Mbit devices making 256MByte in total

- connected as two chip selects, each with two chips of  $32M \downarrow 16$ .

## Option 2

- four 256Mbit devices making 128MByte total

- connected as two chip selects, each with two chips of  $16M \rfloor 16$ .

## **Option 3**

- two 512Mbit devices making 128MByte total

- connected as one chip select, with two chips of  $32M \downarrow 16$ .

# **DQS** pull-downs

The DMC uses four bi-directional data qualifier strobes, one per byte lane. These require pull-downs for functionality.

\_\_\_\_\_Note \_\_\_\_\_

You must provide these pull-downs on the PCB, because they are not implemented in the pads.

## **DLL control**

To capture read data correctly, a master-slave DLL combination adjusts DQS strobe timing for each byte lane. There is one slave per byte lane strobe. The DLL applies a nominal cycle delay to each DQS input to the SoC.

—— Note ———

DQS going out of the SoC for writes is not manipulated.

The master DLL outputs a raw 7-bit delay code, updated every 32 **ACLK** cycles. It tracks voltage and temperature variations. Although this code is applied to the four slaves, each byte lane code is manipulated individually using saturating adders. These adders are user-configurable.

— Note —

The saturating adder functionality ensures a value higher than 7'7F saturates at 7'7F, and a value less than 7'00 saturates at 7'00.

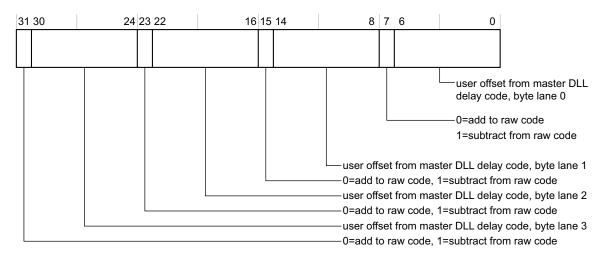

To create this offset from the master DLL code, the user\_config Register in PL340 is extended from eight bits to 32 bits. Table 2-8 shows the user\_config Register functionality. No offset is applied by default. Figure 2-7 shows the bit assignment for this register.

## Figure 2-7 user\_config Register bit assignment

Table 2-8 lists the user\_config Register functionality in the PL340.

| Bits    | Reset    | Function                                            |

|---------|----------|-----------------------------------------------------|

| [31]    | 0        | 0 = add to raw code<br>1 = subtract from raw code.  |

| [30:24] | 000_0000 | User offset from master DLL delay code, byte lane 3 |

| [23]    | 0        | 0 = add to raw code<br>1 = subtract from raw code.  |

| [22:16] | 000_0000 | User offset from master DLL delay code, byte lane 2 |

| [15]    | 0        | 0 = add to raw code<br>1 = subtract from raw code.  |

## Table 2-8 user\_config Register functionality in PL340

| Bits   | Reset    | Function                                            |

|--------|----------|-----------------------------------------------------|

| [14:8] | 000_0000 | User offset from master DLL delay code, byte lane 1 |

| [7]    | 0        | 0 = add to raw code<br>1 = subtract from raw code.  |

| [6:0]  | 000_0000 | user offset from master DLL delay code, byte lane 0 |

#### Table 2-8 user\_config Register functionality in PL340 (continued)

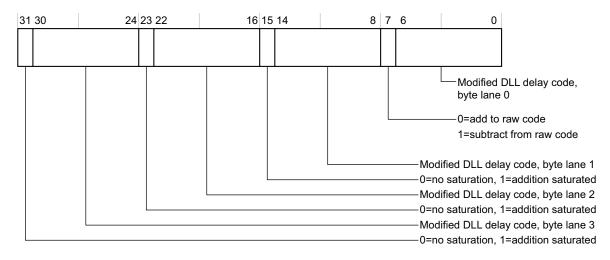

You can read back the modified codes using the user\_status Register in PL340. It has been extended from eight bits to 32 bits. Table 2-9 lists the reset and functions of the bits. Figure 2-8 shows the bit assignment for this register.

#### Figure 2-8 user\_status Register bit assignment

Table 2-9 lists the bit assignment for this register.

#### Table 2-9 user\_status Register functionality in PL340

| Bits    | Reset       | Function                                     |

|---------|-------------|----------------------------------------------|

| [31]    | PVT defined | 0 = no saturation<br>1 = addition saturated. |

| [30:24] |             | Modified DLL delay code, byte lane 3         |

| [23]    | PVT defined | 0 = no saturation<br>1 = addition saturated. |

| Bits    | Reset       | Function                                     |

|---------|-------------|----------------------------------------------|

| [22:16] |             | Modified DLL delay code, byte lane 2         |

| [15]    | PVT defined | 0 = no saturation<br>1 = addition saturated. |

| [14:8]  |             | Modified DLL delay code, byte lane 1         |

| [7]     | PVT defined | 0 = no saturation<br>1 = addition saturated. |

| [6:0]   |             | Modified DLL delay code, byte lane 0         |

Table 2-9 user\_status Register functionality in PL340 (continued)

The slave DLLs are updated with the most recent delay code. This is ensured by the control logic implementation:

• A self-loading counter, loaded with an 8-bit value from the system controller periodically requests a DLL update. The counter runs on **mclk**, with a clock enable of **mclk**÷32, that the Master DLL provides.

The count increment is 192ns at 166MHz.

• The default reset value for this counter is  $0 \rfloor 34$ , 54d. This provides a delay of approximately 10µs between DLL updates.

The range of update period is between 192ns and 48µs with a 166MHz clock.

- DLL updates cannot be disabled.

- During normal operation of the memory controller, a dummy EBI arbiter is implemented. This grants the DMC ownership of the bus by default. A DLL update request forces **ebibackoff** HIGH. This in turn forces the DMC to relinquish control of the bus at the end of the current transaction.

Control logic responds to this bus release, and updates the slave DLLs with a low going pulse on **ASETB**. This is safe because there is no DQS activity either at this time or outstanding.

The update process removes bus ownership from the DMC for worst case, three **mclk** cycles.

• The DLL master and slave cells are powered and clocked continuously in the chip to enhance implementation. Although you can gate the clock and remove power to these devices during prolonged periods of inactivity, this increases the DLL train complexity and delays update sequencing.

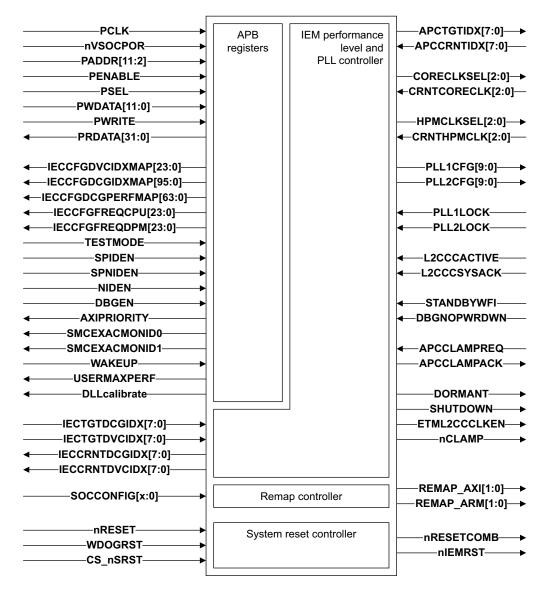

# 2.2 System controller

The system controller is an APB memory-mapped peripheral that incorporates system control and status registers. It enables:

- software to control the IEC configuration busses

- visibility of SoC-level configuration capture

- PLL configuration settings

- IEM mode control.

The system controller consists of:

- the APB subsystem

- the IEM performance level controller

- the PLL controller

- the remap controller

- the system reset controller.

Figure 2-9 on page 2-27 shows a top-level block overview of the system controller .

## Figure 2-9 System controller top-level

This section contains the following subsections:

- Intelligent Energy Management (IEM) on page 2-8

- *Power modes* on page 2-29

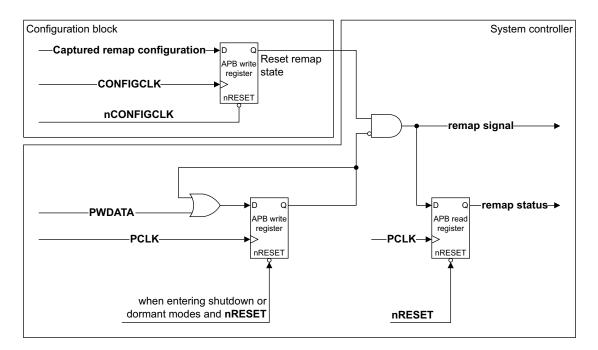

- *Remap controller* on page 2-36

- *System reset controller* on page 2-37.

# 2.2.1 Intelligent Energy Management (IEM)

This section describes the IEM and contains the following subsection:

Performance level and PLL controller.

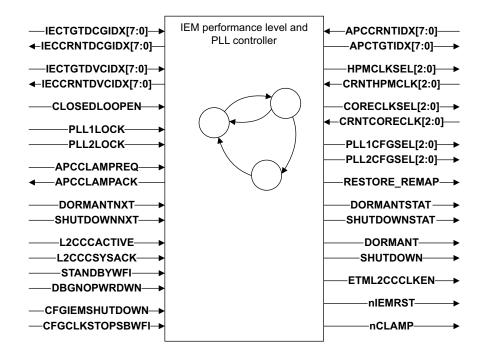

# Performance level and PLL controller

The IEM performance level and PLL controller is responsible for:

- receiving performance requests from the IEC

- sending and monitoring performance requests to the APC1 and DCG

- configuring the PLLs

- instructing the clock selection block concerning which PLL to select and when.

This block also controls the safe entry and exit from low power modes. This includes StandbyWFI, shutdown and dormant modes.

The IEM PLL controller consists of the performance level controller state machine and PLL configuration select blocks. Figure 2-10 shows an overview of the IEM performance level and PLL controller.

Figure 2-10 IEM performance level and PLL controller

## 2.2.2 Power modes

This section describes the power modes and contains the following subsections:

- Run mode

- *StandbyWFI mode* on page 2-34

- Dormant and shutdown modes on page 2-35

- *IEM subsystem permanent shutdown mode* on page 2-35

- *Wake-up sources* on page 2-35.

# Run mode

This is the normal mode after reset. IEM software only operates in this mode.

— Note — —

- After reset, the AXI slices operate asynchronously and the IEC does not generate an **IECSYNCMODEREQ** until configured.

- Additionally, after reset, the IEC defaults to requesting a 100% performance target. In Run mode, a performance level of 0% is never selected by IEM software because 1% is the minimum demand the IEM software can set.

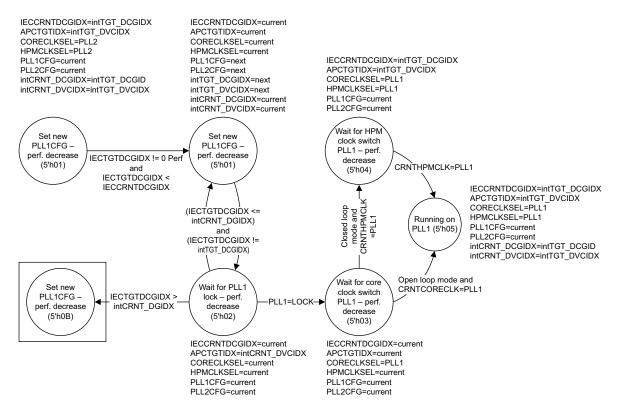

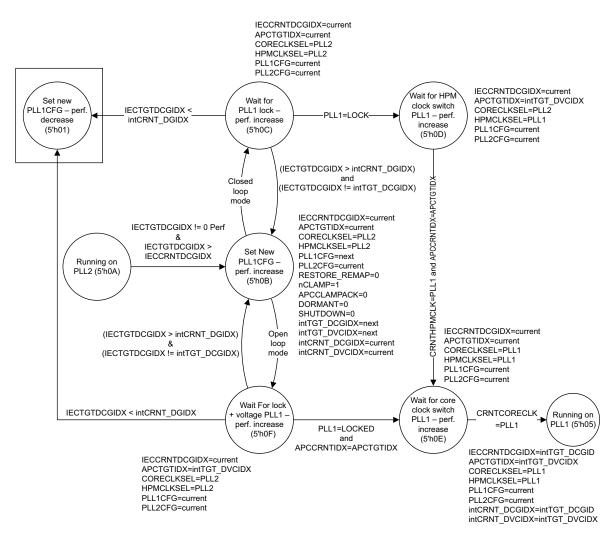

The Run Mode Performance Level Controller State Machine is shown in Figure 2-11 on page 2-30 through Figure 2-15 on page 2-34. It receives performance level requests from the IEC and ensures safe movement between performance levels. The state machine supports both closed and open loop modes.

The state machine ensures that when moving between performance levels, the required PLL is locked, and the IEM subsystem voltage level is adequate.

— Note —

In closed loop mode, the state machine also controls switching of the HPM clock.

New performance levels issued by the IEC can override current performance targets only when the state machine is in one of the 'PLL Wait For Lock' states.

An exit to 'Max Perf' state is implicitly applied for all of the following states:

- PLL wait for lock

- running on PLL

- dormant

- shutdown.

This state machine controls IEM through all active performance levels. If 0% performance is selected, the system either enters StandbyWFI, Shutdown or Dormant mode depending on system settings. For more information on these modes, see *Controlling the power modes* on page 3-20.

— Note — —

For ease of illustration, the state machine is divided into six segments. States enclosed within rectangles represent those that cross between diagrams.

Figure 2-11 shows the process of switching to a lower performance on PLL1 from running on PLL2.

\_\_\_\_ Note \_\_\_\_\_

When in open loop mode, **HPMCLKSEL** always drives 3'b000 to disable the HPM clock.

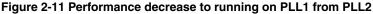

# Figure 2-12 shows the process of switching to a lower performance on PLL2 from running on PLL1.

## Figure 2-12 Performance decrease to running on PLL2 from PLL1

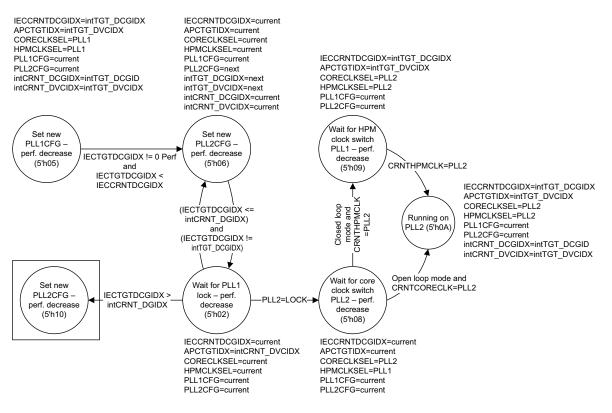

Figure 2-13 on page 2-32 shows the process of switching to a higher performance on PLL2 from running on PLL1.

Figure 2-13 Performance increase to running on PLL2 from PLL1

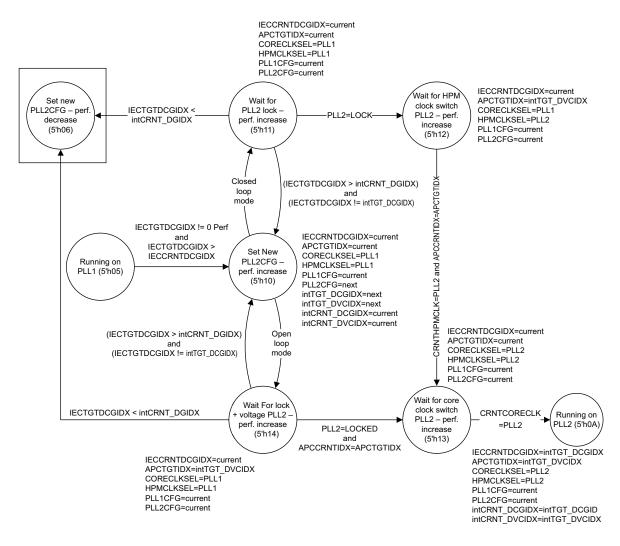

Figure 2-14 on page 2-33 shows the process of switching to a higher performance on PLL1 from running on PLL2.

## Figure 2-14 Performance increase to running on PLL1 from PLL2

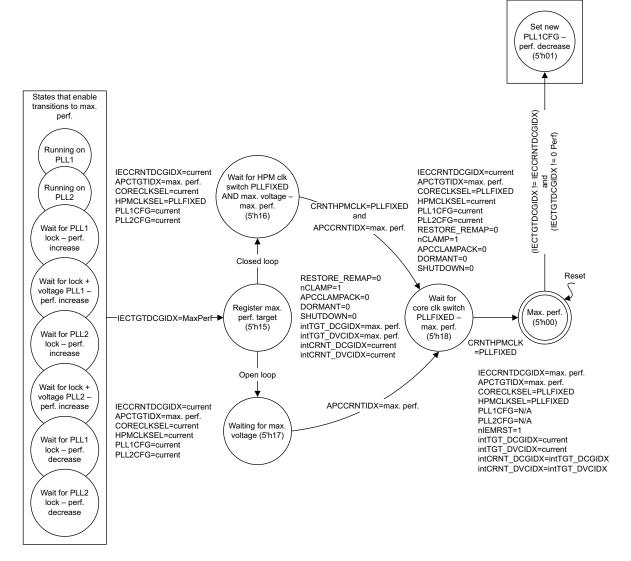

Figure 2-14 shows a transition to maximum performance. When the IEC requests maximum performance, new performance targets are not considered until maximum performance is reached.

## Figure 2-15 Increase to maximum performance

## StandbyWFI mode

StandbyWFI mode is entered whenever the IEC selects 0% performance, and neither **SHUTDOWNNXT** nor **DORMANTNXT** flags are set.

When entering StandbyWFI mode, no new voltage requests are made to the APC. Voltage is held at the current level prior to requesting 0% performance.