# AMBA Color LCD Controller Data Sheet

Copyright © 1997, 1998 ARM Limited. All rights reserved. ARM DDI 0121D

## AMBA Color LCD Controller Data Sheet

Copyright © 1997, 1998 ARM Limited. All rights reserved.

#### **Release Information**

The following changes have been made to this document.

**Change History**

| Date           | Issue | Confidentiality  | Change                                      |

|----------------|-------|------------------|---------------------------------------------|

| August 1997    | А     | Non Confidential | First issue                                 |

| September 1997 | В     | Non Confidential | Corrections to equations on pages 19 and 35 |

| December 1997  | С     | Non Confidential | Minor amendments                            |

| June 1998      | D     | Non Confidential | Minor amendments                            |

#### **Proprietary Notice**

ARM and the ARM Powered logo are trademarks of Advanced RISC Machines Ltd.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties or merchantability, or fitness for purpose, are excluded. This document is intended only to assist the reader in the use of the product. ARM Ltd shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

# Contents AMBA Color LCD Controller Data Sheet

# Chapter 1

## AMBA Color LCD Controller

| 1.1  | Module overview                                  | 1-3  |

|------|--------------------------------------------------|------|

| 1.2  | Display Specifications                           | 1-8  |

| 1.3  | AMBA Signal Descriptions                         | 1-9  |

| 1.4  | ASB Bus Master                                   | 1-10 |

| 1.5  | LCD Controller Operation                         | 1-17 |

| 1.6  | LCD Controller Register Definitions              | 1-28 |

| 1.7  | LCD Control Register                             | 1-29 |

| 1.8  | LCD Timing 0 Register                            | 1-38 |

| 1.9  | LCD Timing 1 Register                            | 1-41 |

| 1.10 | LCD Timing 2 Register                            | 1-46 |

| 1.11 | LCD Controller DMA Registers                     | 1-51 |

| 1.12 | DMA Channel 1 Base Address Register              | 1-52 |

| 1.13 | DMA Channel 1 Current Address Register           | 1-54 |

| 1.14 | DMA Channel 2 Base and Current Address Registers | 1-55 |

| 1.15 | LCD Controller Status Register                   | 1-57 |

| 1.16 | Gray Scaler Test Read Frame Phase Register       | 1-61 |

| 1.17 | Gray Scaler Test Read Row Phase Register         | 1-62 |

| 1.18 | Gray Scaler Test Read Column Phase Register      | 1-63 |

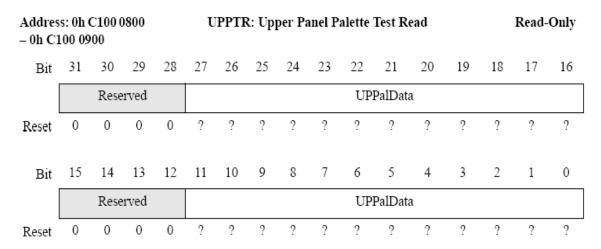

| 1.19 | Upper Panel Palette Test Read                    | 1-64 |

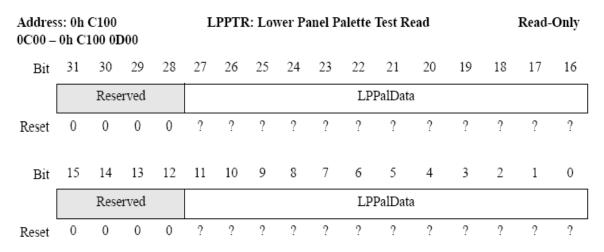

| 1.20 | Lower Panel Palette Test Read                    | 1-65 |

| 1.21 | Gray Scaler Test Write                           |      |

| 1.22 | LCD Controller Register Locations                | 1-68 |

Contents

# Chapter 1 AMBA Color LCD Controller

- *Module overview* on page 1-3

- Display Specifications on page 1-8

- AMBA Signal Descriptions on page 1-9

- ASB Bus Master on page 1-10LCD Controller Operation on page 1-17

- *LCD Controller Operation* on page 1-17

- LCD Controller Register Definitions on page 1-28

- LCD Control Register on page 1-29

- LCD Timing 0 Register on page 1-38

- LCD Timing 1 Register on page 1-41

- LCD Timing 2 Register on page 1-46

- LCD Controller DMA Registers on page 1-51

- DMA Channel 1 Base Address Register on page 1-52

- DMA Channel 1 Current Address Register on page 1-54

- DMA Channel 2 Base and Current Address Registers on page 1-55

- LCD Controller Status Register on page 1-57

- Gray Scaler Test Read Frame Phase Register on page 1-61

- *Gray Scaler Test Read Row Phase Register* on page 1-62

- Gray Scaler Test Read Column Phase Register on page 1-63

- Upper Panel Palette Test Read on page 1-64

- Lower Panel Palette Test Read on page 1-65

- Gray Scaler Test Write on page 1-66

- LCD Controller Register Locations on page 1-68

## 1.1 Module overview

The LCD controller provides all the necessary control signals to interface directly to an ARM AMBA bus as a bus master controller. The LCD controller can operate in single-panel or dual-panel modes when connected to the associated multiplexed LCD. The block is designed to work with a separate RAM block to provide data to the FIFO at the front end of the LCD controller data path, at a rate sufficient to support the chosen display mode and resolution.

The panel size is programmable, and can be any width (line length) from 16 to 1024 pixels in 16-pixel increments. The number of lines is set by programming the total number of pixels in the LCD. The total video frame size is programmable up to 1024x1024; single- or dual-panel display mode is also supported.

The screen is intended to be mapped to the video buffer as one contiguous block where each horizontal line of pixels is mapped to a set of consecutive bytes of words in the video memory. The pixels stored in memory can be programmed and arranged in a little or big endian manner.

Assuming a bus clock frequency of 30MHz, the maximum screen resolution for this bandwidth would be 640x480 pixels. To display a resolution of 800x600 pixels, the bus clock frequency would have to be 50MHz.

The principal features of the LCD controller are:

- encoded pixel data is stored in external memory in a frame buffer in 4-, 8- or 16-bit increments, and is loaded into a four-entry FIFO (32 bits per entry) and holding latch on a demand basis using the LCD's own dedicated dual-channel DMA controller

- programmable pixel display modes

- programmable display size

- 16 grayscale levels

- palette allowing full logical-to-physical address mapping

- programmable pixel rate

- four types of displays are supported—passive and active color, and passive and active monochrome

- in passive STN mode a total of 3375 possible colors is available, allowing any 256 colors to be displayed in each frame, as well as 15 grayscale levels for monochrome screens

- any screen size up to 1024x1024 (assuming big enough bandwidth) is supported, as well as single- or dual-panel display mode

- frame, line and pixel clocks

- AC-bias drive signal

- AMBA compatible

- 4, 8 and 16 bit-per-pixel display modes

- patented dithering algorithm

Frame buffer data contains encoded pixel values: these are used by the LCD controller as pointers to index into a 256-entry by 12-bit wide palette. Monochrome palette entries are 4bits wide, and color are 12 bits wide. Encoded pixel data from the frame buffer which is 4 bits wide addresses the first16 locations of the palette, and 8-bit pixel data accesses any of the 256 entries within the palette. When passive color 12-bit pixel mode is enabled, the color pixel values bypass the palette and are fed directly to the LCD's dither logic. When active color 16-bit pixel mode is enabled, the pixel value not only bypasses the palette but also the dither logic, and is sent directly to the LCD's data pins.

Once the 4- or 8-bit encoded pixel value is used to select a palette entry, the value programmed within the entry is transferred to the dither logic; this uses a patented space or time-based dithering algorithm to produce the pixel data that is output to the screen. Dithering causes individual pixels to be turned off and on in each frame at varying rates to produce the 15 levels of gray for monochrome screens, and 15 levels each for the red, green and blue pixel components for color screens: this provides a total of 3375 colors, 256 of which are available in each frame. The data output from the dither logic is placed in a FIFO before it is placed on the LCD's pins and is driven to the display using the pixel clock.

Depending on the type of panel used, the LCD controller is programmed to use either 4-, 8- or 16-pixel data output pins. Single-panel monochrome displays use 4- or 8-bit data registers to output four or eight pixels respectively to each pixel clock, and single-panel color displays use eight pins to output 22/3 pixels to each pixel clock (8 pins / 3 colors/pixel = 22/3 pixels per clock). The LCD controller also supports dual-panel mode, which causes the LCD controller's data lines to be split into two groups: one to drive the top half, and one to drive the bottom half of the screen. For dual-panel displays, the number of pixel data output pins are doubled, allowing twice as many pixels to be output from each pixel clock to the two halves of the screen.

In active (TFT) display mode, the LCD can be used with an external palette and DAC to drive a video monitor. The LCD's line clock pin functions as a horizontal sync (HSYNC) signal and the frame clock pin functions as a vertical sync (VSYNC) signal.

In TFT mode, the LCD's dither logic is bypassed, sending selected palette entries directly to the LCD's data output pins. Additionally, 16-bit pixels can be used, which bypass both the palette and the dither logic.

Details relating to the LCD controller's signals are shown in Table 1-1 and Table 1-2 on page 1-6.

#### Table 1-1 AMBA signal descriptions

| Name       | Туре  | Source/<br>Destination      | Description                                                                                                                                                                                                                                                                                                                                                       |  |

|------------|-------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BnRES      | In    | Reset Controller            | The bus reset signal is active LOW and is used to reset the system and the bus.                                                                                                                                                                                                                                                                                   |  |

| BA[31:0]   | InOut | Current Master/LCD          | System address bus. The addresses become valid before the transfer to which they refer and remain valid until the last phase 2 of the transfer.                                                                                                                                                                                                                   |  |

| BCLK       | In    | AMBA Bus                    | The ASB clock, timing and all bus transfers. It has two distinct phases: phase 1 in which BCLK is LOW and phase 2 in which BCLK is HIGH.                                                                                                                                                                                                                          |  |

| BD[31:0]   | InOut | Current Master,<br>AMBA Bus | Bi-directional system data bus. The data bus is driven by the current bus master during write transfers and by this block during register read transfers.                                                                                                                                                                                                         |  |

| BERROR     | In    | AMBA Bus                    | LCD slave signalling that a bus error has occurred.                                                                                                                                                                                                                                                                                                               |  |

| BLAST      | In    | AMBA Bus                    | This signal is driven by the selected bus slave to indicate if the current transfer should be the last of a burst sequence. When <b>BLAST</b> is HIGH, the decoder must allow sufficient time for address decoding. When <b>BLAST</b> is LOW, the next transfer may continue a burst sequence. When no slave is selected, this signal is driven by the bus decode |  |

| BSIZE[1:0] | Out   | Current Master              | These signals indicate the size of the transfer, which may be byte,<br>halfword or word. These signals have the same timing as the system<br>address bus.                                                                                                                                                                                                         |  |

| BWAIT      | In    | Current Master              | Wait slave response signal. Driven in phase 1 when the DRAM controller is selected. Asserted while the DRAM transaction is incomplete.                                                                                                                                                                                                                            |  |

| BWRITE     | InOut | Current Master              | When HIGH this signal indicates a write transfer, and when LOW a read transfer. This signal has the same timing as the address bus.                                                                                                                                                                                                                               |  |

| BTRAN[1:0] | Out   | Current Master              | These signals are used to determine sequential and non-sequential accesses for RAM burst mode access control.                                                                                                                                                                                                                                                     |  |

| BPROT[1:0] | Out   | Current Master              | These signals indicate if the transfer is an opcode fetch of data access.<br>The transfer will always be a supervisor mode.                                                                                                                                                                                                                                       |  |

| Name      | Туре | Source/<br>Destination | Description                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UPLcdData | Out  | DMA                    | Register used to store either four or eight data values at a time to the LCD display. For monochrome displays, each bit value represents a pixel; for passive color displays, groupings of three bit values represent one pixel (red, green and blue data values). UPLcdData[3:0] is used for single-panel monochrome displays; UPLcdData is used for dual-panel monochrome, as well as singlepanel color displays and active color modes. |

| LPLcdData | Out  | DMA                    | When dual-panel color or TFT operation is programmed, LPLcdData is used as the additional, required LCD data register to output pixel data to the screen.                                                                                                                                                                                                                                                                                  |

| LcdCP     | Out  | LCD                    | Pixel clock used by the LCD display to clock the pixel data into the line<br>shift register. In passive mode, pixel clock only transitions which valid<br>data is available on the data lines. In active mode the pixel clock<br>transitions continuously and the AC-bias pin is used as an output enable<br>to signal when data is available on the LCD's pins.                                                                           |

| LcdLP     | Out  | LCD                    | Line clock used by the LCD display to signal the end of a line of pixels that transfers line data from the shift register to the screen, and to increment the line pointer(s). Also used by TFT displays as the horizontal synchronization signal.                                                                                                                                                                                         |

| LcdFP     | Out  | LCD                    | Frame clock used by the LCD displays to signal the start of a new frame of pixels. Also used by TFT displays as the vertical synchronization signal.                                                                                                                                                                                                                                                                                       |

| LcdAC     | Out  | LCD                    | AC-bias used to signal the LCD display to switch the polarity of the power supplies to the row and column axis of the screen to counteract DC offset. Used in TFT mode as the output enable to signal when data should be latched from the data pins using the pixel clock.                                                                                                                                                                |

#### Table 1-2 LCD controller panel signal descriptions

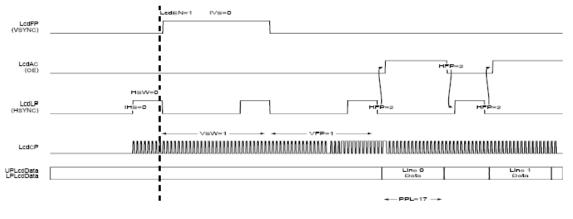

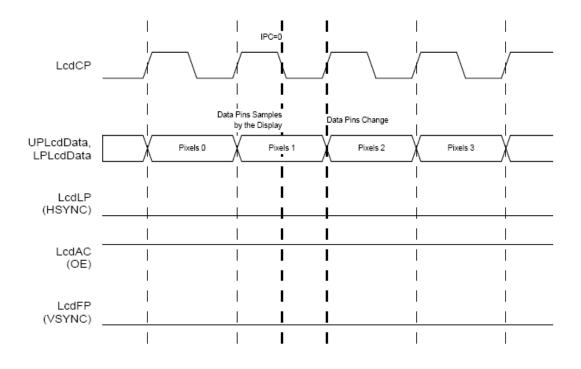

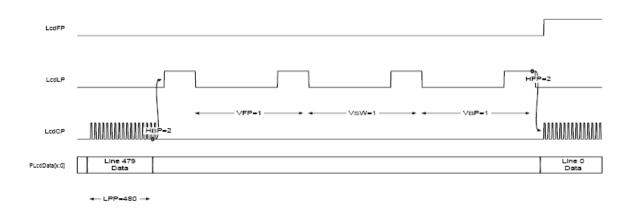

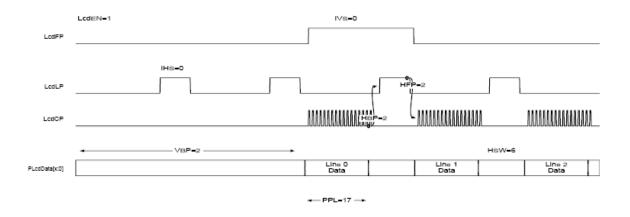

The pixel clock frequency should be derived from the output of the on-chip PLL (BCLK) and is programmable from BCLK/2 to BCLK/257. Each time new data is supplied to the LCD data pins, the pixel clock is toggled to latch the data into the LCD display's serial shifter. The line clock toggles after all pixels in a line have been transmitted to the LCD driver, and a programmable number of pixel clock wait states have elapsed both at the beginning and end of each line. In passive mode, the frame clock toggles during the first line of the screen, and the beginning and end of each frame is separated by a programmable number of line clock wait states (Horizontal Front Porch, HFP and Horizontal Back Porch, HBP should be programmed to zero in passive mode).

In active mode, the frame clock is asserted at the end of a frame after a programmable number of line clock wait states occur. In passive display mode, the pixel clock does not transition during wait state insertion or when the line clock is asserted. Finally, the AC-bias (LcdAC) can be configured to transition each time a programmable number of line clocks occurs.

# 1.2 Display Specifications

The following information shows the number of palette entries and thus the number of possible screen colors per frame that can be displayed in each mode with the corresponding number of bits-per-pixel (BPP).

Mono passive: 4 BPP only:

• 16 palette entries selecting one of 15 grayscale.

\_\_\_\_\_Note \_\_\_\_\_

8 BPP would work, but is not practicable as there are only 15 physical grayscales.

Color passive: 4 BPP, 8 BPP, 12 BPP "true-color"

- 4 BPP: 16 palette entries from 3375 possible colors

- 8 BPP: 256 palette entries from 3375 possible colors

- 12 BPP: 3375 possible on-screen colors

TFT: 4bpp, 8bpp, 16bpp

- 4 BPP: 16 palette entries selecting from 4096 colors

- 8 BPP: 256 palette entries selecting from 4096 colors

- 16 BPP: Maximum 64K colors, depending on LCD panel

Palette entries are 16 bits wide (2 bytes) and 4 BPP, so require 32 bytes of storage. 8 BPP modes require 256 bytes. 12 or 16 BPP modes do not use palette data but need the bits per- pixel information to be loaded, so these modes uses 32 byte similar to that of the 4 BPP modes.

Mono passive modes supports two different interfaces: 4 bits per panel and 8 bits per panel. Both Mono and color passive modes can operate in single- or dual-panel modes. All modes (color/mono, 4, 8, 12 or 16 bits-per-pixel, 4- or 8-bit mono, single- or dual-panel) operate independently of each other.

Vertical Back Porch (VBP) and Vertical Front Porch (VFP) must be zero on passive screen. The vertical synchronization signal (VSync) width must be programmed to be as small as possible on passive screen modes, but long enough to load the palette without stealing all the memory bandwidth from the CPU.

Pixels-per-line (PPL) must be in multiples of 16. Most LCD panels ignore data at the end of the line that is not needed—that is, they ignore data at the right hand side of the screen.

# 1.3 AMBA Signal Descriptions

This section provides detailed information on the relevant AMBA signals, including their intended use and phase-accurate timing requirements.

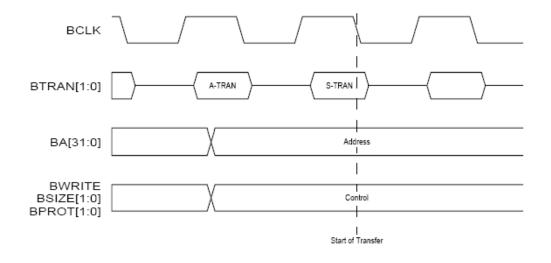

### 1.3.1 Address and Control Signal Timing

The address and control information is generated by the bus master from the rising-edge of BCLK. The timing of the address and control information, however, is considered separately for Non-sequential and Sequential transfer types. This is because a bus master will typically have significantly different timing parameters in each case.

It is a common characteristic that bus masters will have fast address and control output valid timings for Sequential transfers, as shown in Figure 1-1. This is because a bus master is usually able to generate a sequential address well before the start of the transfer, and therefore the output valid time from the bus master is mainly dependent on the time required to drive the new value onto the bus.

Figure 1-1 Address and control output timings

## 1.4 ASB Bus Master

This section provides detailed information on the relevant AMBA signals, including their intended use and phase-accurate timing requirements.

#### 1.4.1 Bus Master Interface Description

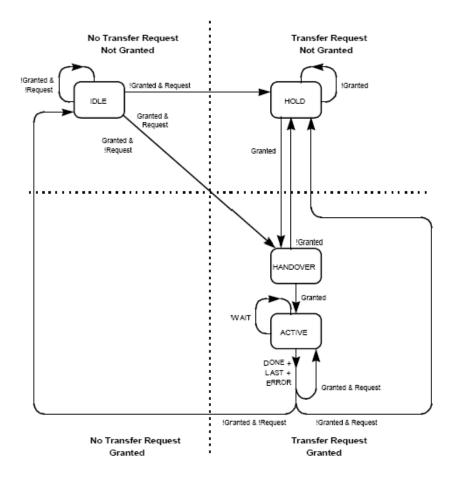

The main bus interface state machine is falling-edge triggered and contains six states. The entire state diagram, as shown in Figure 1-3 on page 1-11, is quite complex but can be considered in four quadrants.

| No Transfer Request                     | Transfer Request                                       |

|-----------------------------------------|--------------------------------------------------------|

| Not Granted                             | Not Granted                                            |

| No Transfer Request<br>Transfer Granted | Transfer Request<br>Granted<br>(Retract not supported) |

#### Figure 1-2 Quadrants

The Transfer Request, Granted quadrant contains two states, which handle handover bus turnaround (the retract operation is not supported).

The two signals internal bus master signals Granted and Request control the majority of the transitions around the state diagram. Granted is generated from the simpler state machine and Request is generated directly by the bus master. Request is asserted HIGH when the bus master requires a transfer on the bus, and is LOW when the bus master does not need access to the bus.

The only time when a transition around the state diagram is not controlled by Granted and Request is when the bus master is in the ACTIVE state. In this state, the transition to the next state is determined by the transfer response that is received. WAIT, DONE, LAST and ERROR shown in Figure 1-3 on page 1-11 correspond to the encodings of the transfer response signals.

Figure 1-3 Bus master main state machine

The state diagram assumes that, once the LCD controller has made a request for a transfer as indicated by Request, then the LCD controller de-assert Request and assert BLOK for the remainder of the time Granted is required.

As the main bus master state machine is operating from the falling-edge of the clock, it is necessary to use latched versions of the transfer response signals BWAIT, BERROR and BLAST to control the exit from the ACTIVE state. The reset conditions are not shown on the state diagram, as the main bus master state machine has a complex reset

- Note

term. BUSIDLE state is not supported as the LCD controller should not be default bus master. If AGNT is not asserted during reset then the bus master enters the IDLE state. Table 1-3 indicates the actions that must occur in each state.

| Name     | Description                                     | Action                                                   |  |  |

|----------|-------------------------------------------------|----------------------------------------------------------|--|--|

| IDLE     | The master does not require the bus and is not  | Internal BTRAN is Address-only                           |  |  |

|          | granted.                                        | Master clock is enabled                                  |  |  |

|          |                                                 | Master address bus is tri-state                          |  |  |

|          |                                                 | Master data bus is tri-state                             |  |  |

| BUSIDLE  | The master does not require the bus, but has    | Internal BTRAN as indicated by master                    |  |  |

|          | been granted anyway.                            | Master clock is enabled                                  |  |  |

|          |                                                 | Master address bus enable is generated from the          |  |  |

|          |                                                 | Granted signal                                           |  |  |

|          |                                                 | Master data bus is tri-state                             |  |  |

| HOLD     | The master requires the bus, but has not been   | Internal BTRAN is Address-only                           |  |  |

|          | granted.                                        | Master clock is disabled                                 |  |  |

|          |                                                 | Master address bus is tri-state                          |  |  |

|          |                                                 | Master data bus is tri-state                             |  |  |

| HANDOVER | This state provides bus turnaround when         | Internal BTRAN is Sequential                             |  |  |

|          | changing between different bus masters.         | Master clock is disabled                                 |  |  |

|          |                                                 | Master address bus enable is generated from              |  |  |

|          |                                                 | Granted signal                                           |  |  |

|          |                                                 | Master data bus is tri-state                             |  |  |

| ACTIVE   | Active state when data transfers occur.         | Internal BTRAN as indicated by master                    |  |  |

|          | Exiting this state is dependent on the transfer | Master clock enable is derived from BWAIT                |  |  |

|          | response.                                       | Master address bus enable is generated from              |  |  |

|          |                                                 | Granted signal                                           |  |  |

|          |                                                 | Master data bus enable is enabled if a write transaction |  |  |

#### **Table 1-3 State actions**

BTRAN[1:0] tri-state drivers are enabled when AGNT and BCLK are both HIGH. Master Address Bus Enable is used to control the tri-state enable of BA[31:0], BWRITE, BSIZE[1:0], BPROT[1:0] and BLOK. Master Data Bus Enable is used to control the tri-state enable of BD[31:0].

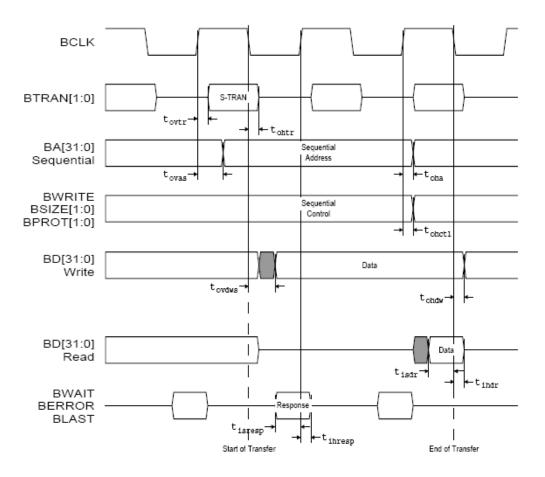

## 1.4.2 Bus Master Timing Diagrams

The following diagrams show the timing parameters related to an ASB bus master operating in an AMBA system. Figure 1-4 shows the parameters related to Sequential transfers; Figure 1-5 on page 1-14 shows the reset signal and arbitration timing.

## Figure 1-4 ASB bus master sequential transfer

A sequential transfer has different timing parameters for the address and control signal valid times. In a typical bus master, the output valid times for sequential transfers will be far better than for Non-sequential transfers. The output hold times for address, control and data are identical and independent of the transfer type. The other difference between the Sequential and Non-sequential transfers is that during a Sequential transfer the data may be driven during the first phase of the transfer and hence the data valid parameter is specified from the falling-edge of BCLK.

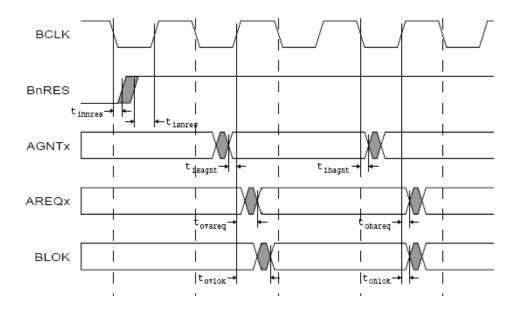

#### Figure 1-5 ASB bus master arbitration and reset signal

The BnRES signal may be asserted asynchronously and so there is no setup and hold parameter relating to the assertion of the signal. The AREQ signal, which is an output from the bus master, changes during the HIGH clock phase and the AGNT signal, which is returned from the arbiter changes during the LOW clock phase. BLOK should be driven low when the LCD is bus master.

— Note —

The LCD controller should have the highest (but not default) bus master priority.

## 1.4.3 Timing Parameters

The timing parameters related to an ASB bus master operating in an AMBA system are also shown in textual form in the following two tables: Table 1-4 details the input signals; Table 1-5 details the output signals. Bi-directional signals can be found in both tables.

| Parameter | Description                                          |

|-----------|------------------------------------------------------|

| Tclkl     | BCLK LOW time                                        |

| Tclkh     | BCLK HIGH time                                       |

| Tisnres   | BnRes de-asserted setup to rising BCLK               |

| Tihnres   | BnRes de-asserted hold after falling BCLK            |

| Tisresp   | BWAIT, BERROR and BLAST setup to rising BCLK         |

| Tihresp   | BWAIT, BERROR and BLAST hold after rising BCLK       |

| Tisdr     | For read transfers, BD[31:0] setup to falling BCLK   |

| Tihdr     | For read transfers, BD[31:0] hold after falling BCLK |

| Tisagnt   | AGNT setup to rising BCLK                            |

| Tihagnt   | AGNT hold after falling BCLK                         |

#### Table 1-4 Bus master input timing parameters

#### Table 1-5 Bus master output timing parameters

| Parameter | Description                                                                                |

|-----------|--------------------------------------------------------------------------------------------|

| Tovtr     | BTRAN valid after rising BCLK                                                              |

| Tohtr     | BTRAN hold after falling BCLK                                                              |

| Tovan     | For Non-sequential transfers, BA[31:0] valid after rising BCLK                             |

| Tovas     | For Sequential transfers, BA[31:0] valid after rising BCLK                                 |

| Tovaa     | For Address-only transfers, BA[31:0] valid after falling BCLK                              |

| Toha      | BA[31:0] hold after rising BCLK                                                            |

| Tovctln   | For Non-sequential transfers,<br>BWRITE, BSIZE[1:0] and BPROT[1:0] valid after rising BCLK |

| Parameter | Description                                                                               |

|-----------|-------------------------------------------------------------------------------------------|

| Tovctla   | For Address-only transfers,<br>BWRITE, BSIZE[1:0] and BPROT[1:0] valid after falling BCLK |

| Tohctl    | BWRITE, BSIZE[1:0] and BPROT[1:0] hold after rising BCLK                                  |

| Tovdwn    | For Non-sequential write transfers, BD[31:0] valid after rising BCLK                      |

| Tovdwn    | For Sequential write transfers, BD[31:0] valid after falling BCLK                         |

| Tohdw     | For write transfers, BD[31:0] hold after BCLK                                             |

| Tovlok    | BLOK valid after rising BCLK                                                              |

| Tohlok    | BLOK hold after rising BCLK                                                               |

| Tovareq   | AREQ valid after rising BCLK                                                              |

| Tohareq   | AREQ hold after rising BCLK                                                               |

## Table 1-5 Bus master output timing parameters (continued)

# 1.5 LCD Controller Operation

The LCD controller supports a variety of user-programmable options, including display type and size, frame buffer pixel size and output data width. Although all programmable combinations are possible, the selection of displays available within the market dictate which combinations of these programmable options are practical. In addition, the type of external memory system implemented by the user limits the bandwidth of the LCD's DMA controller, which in turn limits the size and type of screen which can be controlled.

The following sections describe individual functional blocks within the LCD controller, the frame buffer and palette memory organization, and the LCD's DMA controller. The sections are arranged in order of data flow, starting with the off-chip frame buffer and ending with the pins that interface to the LCD display.

## 1.5.1 DMA to Memory (AMBA) Interface

Palette RAM data and encoded pixel data is stored in off-chip memory (usually DRAM) in an area called the frame buffer. This data is transferred to the LCD controller's 4-entry, 32- bit wide input FIFO and holding latch on a demand basis using the LCD controller's dedicated DMA controller. The LCD controller has been placed on the ARM system bus (ASB) as a bus master rather than the ARM peripheral bus (APB) where all other peripherals are located, because it is a higher-speed synchronous bus that is able to maintain the data rate required for demanding displays such as dual-panel color. The LCD's DMA contains two channels that transfer data from external memory to the input FIFO for LCD control mode. One channel is used for single-panel displays and two are used for dual-panel displays.

The LCD controller issues a service request to the DMA after it has been initialized and enabled. The DMA automatically performs four-word transfers, filling all but one entry of the FIFO. Values are taken from the bottom of the FIFO one entry at a time, and each 32-bit value is unpacked into individual pixel encodings that are 4, 8, 12 or 16 bits each. When enough entries are read from the FIFO, a service request is issued to the DMA.

## 1.5.2 Frame Buffer

The frame buffer is an area within off-chip memory that is used to supply enough encoded pixel values to fill the entire screen one or more times. At the start or lowest order address of the LCD controller's frame buffer is a 32-byte buffer for 4- and 12-bit mode operation (512-byte buffer for all other modes of operation), used to store the look-up palette data for each frame. A 32-byte buffer is used to load the top 16 entries of the palette for 4, 12 and 16 bits-per-pixel encodings, and a 512-byte buffer is used to load the entire 256-entry palette for 8 bits-per-pixel encodings. Note that the palette is

not used for 12 or 16 bits-per pixel encodings. The 32 bytes at the top of the frame buffer, however, must be zero-filled even though the data is not used. This is due to the fact that the bits-per-pixel must be loaded regardless of operation.

Each time a new frame is fetched from the frame buffer, the LCD controller's palette is first loaded with data contained within the palette buffer. Each of the 256 palette entries is stored in adjacent half-words. Figure 1-6 on page 1-19 show the palette entry organization for both little and big endian memory organization. The user may select how the LCD views the ordering of frame buffer palette/pixel entries by programming the Lcd Big Endian (LcdBE) bit in LCD control register (LcdControl). In little endian mode, palette entries are ordered starting with the least significant half-word followed by the most significant. In big endian mode, palette entries are arranged in an order starting with the most significant half-word followed by the least significant. Note that the ordering of the 4-bit R, G, B and mono pixel data (and the BPP field) does not change between little and big endian modes: only the relative positioning of the individual 16-bit palette entries changes.

|       |     |      |    |    |    |        | narvi | uuai r | alette | LIIII | Ý     |   |      |       |       |   |

|-------|-----|------|----|----|----|--------|-------|--------|--------|-------|-------|---|------|-------|-------|---|

| Bit   | 15  | 14   | 13 | 12 | 11 | 10     | 9     | 8      | 7      | б     | 5     | 4 | 3    | 2     | 1     | 0 |

| Color | Un  | ised | BP | P* |    | Red    | (R)   |        |        | Gree  | n (G) |   |      | Blue  | e (B) |   |

| Bit   | 15  | 14   | 13 | 12 | 11 | 10     | 9     | 8      | 7      | б     | 5     | 4 | 3    | 2     | 1     | 0 |

| Mono  | Unı | ised | BP | P* |    | Unused |       |        |        |       |       |   | Mone | o (M) |       |   |

#### Individual Palette Entry

Note: bits-per-pixel (BPP) is only contained within the first palette entry (palette entry 0).

256 Entry Palette Buffer (Little Endian)

| Bit 3      | 31 16           | 15 0            |

|------------|-----------------|-----------------|

| Base + 0x0 | Palette Entry 1 | Palette Entry 0 |

| Base + 0x4 | Palette Entry 3 | Palette Entry 2 |

| Base + 0x20  | Palette Entry 31                                                                 | Palette Entry 30 |  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------|------------------|--|--|--|--|--|

| Base + 0x24  | Palette Entry 33                                                                 | Palette Entry 32 |  |  |  |  |  |

|              | Note: Entries 16 through to 255 do not exist<br>for 4, 12 and 16 bit/pixel modes |                  |  |  |  |  |  |

| Base + 0x1FC | Palette Entry 255 Palette Entry 254                                              |                  |  |  |  |  |  |

| Base + 0x200 | Start of Pixel Data                                                              |                  |  |  |  |  |  |

Figure 1-5: Palette Entry/Buffer Format (Little Endian)

#### 256 Entry Palette Buffer (Big Endian)

| Bit      | 31 16           | 15 0            |

|----------|-----------------|-----------------|

| Base + 0 | Palette Entry 0 | Palette Entry 1 |

| Base + 4 | Palette Entry 2 | Palette Entry 3 |

#### Figure 1-6 Palette Entry/Buffer Format (Big Endian and Little Endian)

The first palette entry (Palette Entry 0) also contains an extra field that is used to configure synchronously the LCD controller at the beginning of each frame. Bits 12 and 13 of the first palette entry contain a field that is used to select the number of bits-per-pixel that is to be used in the following frame and the number of entries that are used in the palette RAM. The bits-per-pixel (BPP) bit-field is decoded by the LCD to correctly unpack pixel data into nibbles, bytes, 12-bit values or half-words, and decoded by the palette to tell it how many address bits are contained in the pixel data it is supplied, configuring the palette size to 16 or 256 entries. Note that 12- and 16-bit pixel mode bypasses the LCD palette and supplies 12-bit values directly to the dither logic when passive mode is enabled, or 16-bit values directly to the output FIFOs when active mode is enabled. Table 1-6 shows the encoding of the BPP bit-field (in little endian mode).

| Table 1-6 Bits-per-pixe | I encoding for | palette entry 0 buffer |

|-------------------------|----------------|------------------------|

|-------------------------|----------------|------------------------|

| Bit   | Name | Description                                                                                          |

|-------|------|------------------------------------------------------------------------------------------------------|

| 13-12 | BPP  | bits-per-pixel                                                                                       |

|       |      | 00 - 4 bits-per-pixel                                                                                |

|       |      | 01 - 8 bits-per-pixel                                                                                |

|       |      | 1x - 12 bits-per-pixel in passive mode (LcdTFT=0), 16 bits-per-pixel in active mode (LcdTFT=1).      |

|       |      | Note: Two 4-bit pixels are packed into each byte, and 12-bit pixels are right-justified on half-word |

|       |      | boundaries (in the same format as palette entry).                                                    |

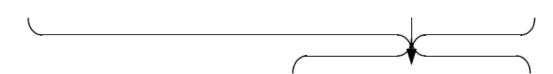

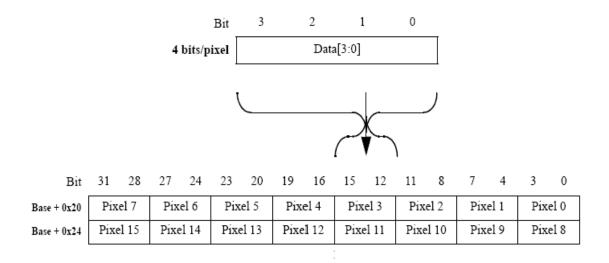

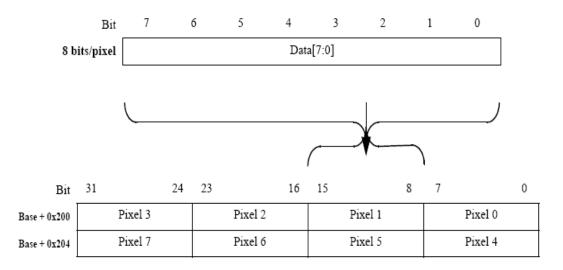

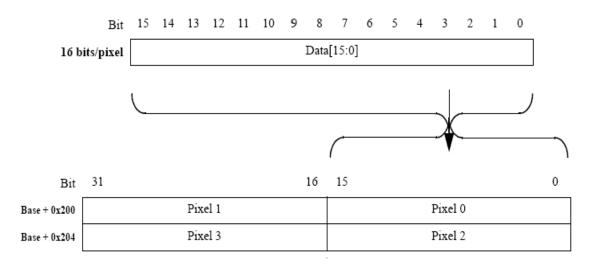

Following the palette buffer is the pixel data buffer that contains one encoded pixel value for each of the pixels present on the display. The number of pixel data values depends on the size of the screen (ie. 1024 x 768 = 786 432 encoded pixel values). Again, each pixel data value can be 4, 8 or 16 bits wide. Figures from Figure 1-7 on page 1-21 through to Figure 1-10 on page 1-22 show the memory organization (little endian mode) within the frame buffer for each size pixel encoding. Note that for 4-bit encodings, two pixels are placed into each byte, and for 12-bit encodings the value is right-justified within a half-word. These figures show the encoded pixel organization for little endian memory organization. Again, the user may select how the LCD views the ordering of frame buffer pixel entries by programming the Lcd Big Endian (LcdBE) bit in LCD control register. In big endian mode, pixel entries are arranged in an order starting with the most significant nibble, byte, or half-word and ending with the least significant.

#### Figure 1-7 4bpp data memory organization (Little Endian)

Figure 1-8 8bpp data memory organization (Little Endian)

Figure 1-9 12bpp data memory organization (STN Mode Only) - Little Endian

#### Figure 1-10 16bpp data memory organization (TFT Mode Only) - Little Endian

In dual-panel mode, pixels are presented to two halves of the screen at the same time (upper and lower). A second DMA channel and input FIFO exists to support dual-panel operation. The DMA channels alternate service requests when filling the two input FIFOs. The palette buffer is implemented in DMA channel 1 but not channel 2, so the base address points to the top of the encoded pixel values for channel 2. The DMA

controller contains a base and current address pointer register. The end address is calculated automatically by the LCD using display information such as pixels-per-line, lines per frame, single-/dualpanel mode, color/monochrome mode, and bits-per-pixel that are programmed by the user.

The LCD's DMA may overshoot the end of the frame buffer by one burst cycle (4 word read). The LCD's DMA reads these extra values but they are flushed from the input FIFO each time the frame clock is pulsed. The user must ensure that the four words immediately following the end of the frame buffer reside in legal memory space (ie. that do not cause a bus error if read). Since the LCD does not alter this memory (only reads are performed), these locations can be used for data storage unrelated to the LCD.

The equations below are used to calculate the total frame buffer size (in bytes) that should be programmed in the DMA, based on varying pixel size encodings and screen sizes. Note that for dual-panel mode the frame buffer size is equally distributed between the two DMA channels, and the DMA channel 2's buffer is either 32 or 512 bytes smaller (no palette buffer).

For 4 bits/pixel: FrameBufferSize =

$$32 + 16 + \left(\frac{\text{Lines} \times \text{Columns}}{2}\right)$$

For 8 bits/pixel: FrameBufferSize = 512 + 16 + (Lines × Columns)

For 12/16 bits/pixel: FrameBufferSize = 32 + 16 + 2(Lines × Columns)

#### Figure 1-11 Equations

#### 1.5.3 Input FIFO

Data from the LCD's DMA is directed either to the palette or the input FIFO. The direction of data flow is switched whenever the LCD controller is first enabled by each frame pulse. After the LCD controller is configured and enabled, the first 32 or 512 bytes supplied by the DMA is sent to the palette. All subsequent encoded pixel data is sent to the FIFO. For passive mode displays the frame clock is pulsed at the beginning of the frame. This signal is also used to change the direction of DMA input data from the FIFO back to the palette. A modulus of 8 or 128 is used to count during loading of the palette RAM, depending on the pixel bit size shown above. A 7-bit counter is loaded

each time a frame clock pulse occurs or the LCD is enabled. The counter is decremented each time a word is stored to the palette (that is, two palette entries). When the counter wraps around to zero, the data input from the DMA is switched back to the FIFO.

The LCD controller contains a 4-entry by 32-bit wide input FIFO and holding latch that is used to store encoded pixels fetched from the frame buffer. The FIFO signals a service request to the DMA whenever four entries of the FIFO are read. In turn, the DMA automatically fills the FIFO with a four-word blast.

Pixel data from the frame buffer remains packed within individual 32-bit words when it is loaded into the FIFO. The LCD controller's port size is 32 bits wide to accommodate the heavy data flow from the frame buffer. Depending on the number of bits-per-pixel, as words are taken from the bottom of the FIFO they are unpacked and supplied to the look-up palette in either nibbles (4 bits/pixel) or bytes (8 bits/pixel), to the dither logic (12 bits/pixel), or directly to the pins in half-words (16 bits/pixel). When four entries are read, a service request is issued to the DMA.

#### 1.5.4 Look Up Palette

The encoded pixel data from the input FIFO is used as an address to index and select individual palette locations. 4-bit pixels address 16 locations, and 8-bit pixels select any of the 256 palette entries. Note that the user may program 1, 2 and 3 bits-per-pixel as well by zeroing-out the upper 3, 2 or 1 bits or each encoded pixel value in the frame buffer and within the LCD controller's input FIFO.

Once a palette entry is selected by the encoded pixel value, the contents of the entry are sent to the color/grayscale space/time base dither circuit. In color mode, the value within the palette is made up of three 4-bit fields, one for each color component: red, green and blue. In monochrome mode, only one 4-bit value is present. For both modes, the 4-bit values represent 1 of 15 intensity levels. For color operation, an individual frame is limited to a selection of 256 colors (the number of palette entries). The LCD controller, however, is capable of generating a total of 3375 colors (15 levels per color x 3 colors). When 12 or 16 bit-per-pixel mode is enabled, the palette is bypassed. For passive displays, 12-bit pixels are sent directly to the dither logic, and 16-bit pixels are sent to the output FIFO to be driven directly to the LCD's data pins.

#### 1.5.5 Color/grayscale Dithering

Entries selected from the look-up palette are sent to the color/grayscale space/timebase dither generator. Each 4-bit value is used to select one of 15 intensity levels. Note that two of the 16 dither values are identical (most intense). The gray/color intensity is controlled by turning individual pixels on and off at varying periodic rates. More intense grays/colors are produced by making the average time that the pixel is off longer than the average time that it is on. The dither generator also uses the intensity of adjacent

pixels in its calculations to give the screen image a smooth appearance. The proprietary dither algorithm is optimized to provide a range of intensity values that match the eye's visual perception of color/gray gradations. In color mode, three separate dither blocks are used to process the three color components: red, green and blue.

The duty cycle and resultant intensity level for all 15 color/grayscale levels is summarized in Table 1-7.

| Dither Value<br>(4-bit value from palette) | Intensity<br>(0% is white) | Modulation Rate<br>(ratio of ON to ON+OFF pixels) |

|--------------------------------------------|----------------------------|---------------------------------------------------|

| 0000                                       | 0.0%                       | 0                                                 |

| 0001                                       | 11.1%                      | 1/9                                               |

| 0010                                       | 20.0%                      | 1/5                                               |

| 0011                                       | 26.7%                      | 4/15                                              |

| 0100                                       | 33.3%                      | 3/9                                               |

| 0101                                       | 40.0%                      | 2/5                                               |

| 0110                                       | 44.4%                      | 4/9                                               |

| 0111                                       | 50.0%                      | 1/2                                               |

| 1000                                       | 55.6%                      | 5/9                                               |

| 1001                                       | 60.0%                      | 3/5                                               |

| 1010                                       | 66.6%                      | 6/9                                               |

| 1011                                       | 73.3%                      | 11/15                                             |

| 1100                                       | 80.0%                      | 4/5                                               |

| 1101                                       | 88.9%                      | 8/9                                               |

| 1110                                       | 100.0%                     | 1                                                 |

| 1111                                       | 100.0%                     | 1                                                 |

Table 1-7 Color/grayscale intensities and modulation rates

## 1.5.6 Output FIFO

The LCD controller contains a 19-entry by 16-bit wide output FIFO that is used to store pixel pin data before it is driven out to the pins. Each time a modulated pixel value is output from the dither generator it is placed into a serial shifter. The size of the shifter

is controlled by programming the color/monochrome select and Lcd Dual Panel bits in the LCD's control registers. The shifter can be configured to be 4, 8 or 16 bits wide. Single-panel monochrome screens use either four or eight data lines, single-panel color and dual-panel monochrome screens use eight data pins, and dual-panel color and active screens use 16 data pins. Once the correct number of pixels have been placed within the shifter (4-, 8- or 16-pixel values), the value is transferred to the top of the output FIFO. The value is then transferred down until it reaches the last empty location within the FIFO. As values reach the bottom of the FIFO, they are driven out one by one onto the LCD's data pins on the edge selected by the Invert Pixel Clock (IPC) bit.

## 1.5.7 LCD controller Pins

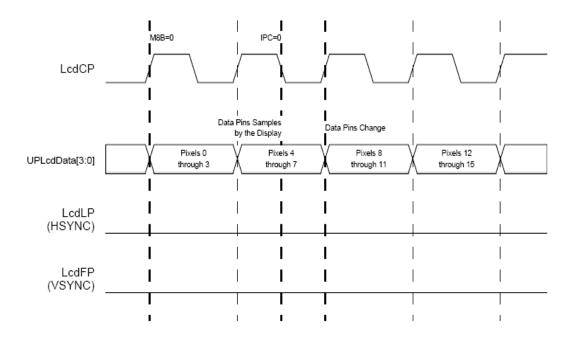

For dual-panel mode, the pixels for the upper half of the screen are loaded to the least significant half of the LCD's output FIFO shifter, and the pixels for the lower half are loaded to the most significant half of the shifter. When the shifter is filled, the value is driven to the LCD controller data bus pins (**UpLcdData[3:0]** for a 4-bit wide bus, to the **UPLcdData** for an 8-bit wide bus, and to the **UPLcdData** and **LPLcdData** for a 16-bit wide bus); in addition, the pixel clock pin (**LcdCP**) is toggled.

When an entire line of pixels has been output to the LCD screen, the line clock pin (LcdLP) is toggled. In the same manner, if the controller is in passive mode and when the start of the first line of a new frame of pixels has been output to the LCD controller screen, the frame clock pin (LcdFP) is toggled. To prevent a DC charge from building within the screen's pixels, the display's power and ground supplies are periodically switched. The LCD controller signals the display to switch the polarity by toggling the AC-bias pin (LcdAC). The user can control the frequency of the bias pin by programming the number of line clock transitions between each toggle.

When active display mode is enabled, the timing of the pixel, line and frame clocks as well as the AC-bias pin change. The pixel clock transitions continuously in this mode as long as the LCD is enabled. The AC-bias pin functions as an output enable. When it is asserted, the display latches data from the LCD's pins using the pixel clock. The line clock pin is used as the horizontal synchronization signal (HSYNC), and the frame clock used as the vertical synchronization signal (VSYNC). See Figure 1-12 on page 1-27.

Figure 1-12 Active mode timing

The timing of the line and frame clock pins is programmable to support both passive and active mode. Programming options include:

- delay insertion both at the beginning and end of each line and frame

- pixel clock, line clock, frame clock and AC-bias signal polarity

- line and frame clock pulse width.

# 1.6 LCD Controller Register Definitions

The LCD controller contains four control registers, four DMA address registers and one status register. The control registers contain bit-fields to enable and disable the LCD controller to define:

- the height and width of the screen being controlled

- single- or dual-panel display mode

- color or monochrome mode

- passive or active display

- polarity of the control lines

- pulse width of the line and frame clocks

- the pixel clock and AC-bias frequency

- the number of delays to insert before/after each line and after each frame.

An additional control field exists to tune the DMA's performance, based on the type of memory system in which the LCD controller is used. This field controls the placement of a minimum delay between each LCD palette request to ensure enough bus bandwidth is given to other ARM systems' bus masters for access. This field is only used for palette load.

The DMA address registers are used to define the base address of the off-chip frame buffer as well as to which address the DMA is currently pointing. Both of these registers exist for DMA channel 1 and 2.

The status registers contain bits that signal:

- FIFO underrun error

- DMA bus errors

- when the DMA base address can be re-programmed

- when the last active frame has completed after the LCD is disabled

Each of these hardware-detected events signal an interrupt request to the interrupt controller.

# 1.7 LCD Control Register

LCD control register (LcdControl) contains seven bit-fields that are used to control various functions within the LCD controller.

## 1.7.1 LCD Enable (LcdEn)

The LCD enable (LcdEn) bit is used to enable and disable all LCD controller operation. When LcdEn=0 the LCD controller is disabled. When LcdEn=1, the LCD controller is enabled.

— Note — \_\_\_\_

All other control registers should be initialized before setting LcdEn.

The user may program LcdControl last, and configure all eight bit-fields at the same time via a word write to the register. If the user clears LcdEn while the LCD controller is enabled, it is permitted to complete transmission of the current frame before being disabled. Completion of the current frame is signalled by the DMA when it sets the Frame Done (Done) within the LCD status register, which generates an interrupt request.

## 1.7.2 LCD Monochrome (LcdBW)

The color/monochrome select (LcdBW) bit is used to determine whether the LCD controller operates in color or monochrome mode. When LcdBW=0:

- color mode is selected

- palette entries are 12 bits wide (4 bits per color)

- 8-bit data register (UPLcdData) is enabled for single-panel mode, and 16-bit for dual-panel mode (LPLcdData register is used as the extra 8 bits)

- all three dither blocks are used, one each for the red, green and blue pixel components

When LcdBW=1:

- monochrome mode is selected

- monochrome mode is selected

- 4 or 8 data lines are enabled for single-panel mode, and 8 pins for dual-panel mode

The LCD Dual Panel(LcdDP) bit is used to select the type of display control that is implemented by the LCD screen. When LcdDP=0, single-panel operation is selected (pixels presented to screen one line at a time); when LcdDP=1, dual-panel operation is selected (pixels presented to screen two lines at a time). Single-panel LCD drivers have one line/row shifter and driver for pixels and one line pointer, while dual-panel LCD controller drivers have two line/row shifters (one for the top half of the screen, one for the bottom) and two line pointers. When dual-panel mode is programmed, both of the LCD controller's DMA channels are used. DMA channel 1 is used to load the palette RAM from the frame buffer and to drive the upper half of the display; DMA channel 2 drives the lower half. The two channels alternate when fetching data for both halves of the screen, placing encoded pixel values within the two separate input FIFOs. When dual-panel operation is enabled, the LCD controller doubles its pin use: for monochrome screens, 8 pins are used and for color screens, 16 pins are used. Table 1-8 shows which set of LCD data pins (and LPLcdData pins) are used for each mode of operation, and Table 1-11: LCD Timing 1 Register (LcdTiming1) on page 1-35 shows the ordering of pixels delivered to a screen, again for each mode of operation.

| Color/Mono | Single-/Dual-panel | Passive/Active panel | Screen portion | Pins                             |

|------------|--------------------|----------------------|----------------|----------------------------------|

| Mono       | Single             | Passive              | Whole          | UPLcdData[3:0]                   |

| Mono       | Single             | Passive              | Whole          | UPLcdData[7:0]                   |

| Mono       | Dual               | Passive              | Top Bottom     | UPLcdData[3:0]<br>UPLcdData[7:4] |

| Color      | Single             | Passive              | Whole          | UPLcdData                        |

| Color      | Dual               | Passive              | Top Bottom     | UPLcdData[7:0]<br>LPLcdData[7:0] |

| Color      | Single             | Active               | Whole          | UPLcdData[7:0]<br>LPLcdData[7:0] |

Table 1-8 LCD controller data pin utilization

## 1.7.3 LCD Done Mask (DoneMask)

The LCD Done Mask (DoneMask) bit masks the Frame Done (Done) bit of the LCD Status Register. When DoneMask = 0, the Frame Done (Done) bit of the LCD Status Register is masked. When DoneMask = 1, the Frame Done (Done) bit of the LCD Status Register is not masked.

#### 1.7.4 LCD Next Mask (Next Mask)

The LCD Next Mask (NextMask) bit masks the Next Frame (Next) bit of the LCD Status Register. When NextMask = 0, the Next Frame (Next) bit of the LCD Status Register is masked. When NextMask = 1, the Next Frame (Next) bit of the LCD Status Register is not masked.

### 1.7.5 LCD Error Mask (Error Mask)

The LCD Error Mask (ErrorMask) bit masks the Bus Error Status (BER) bit of the LCD Status Register. When ErrorMask = 0, the Bus Error Status (BER) bit of the LCD Status Register is masked. When ErrorMask = 1, the Bus Error Status (BER) bit of the LCD Status Register is not masked.

## 1.7.6 LCD TFT (LcdTFT)

The LCD TFT (LcdTFT) bit selects whether the LCD controller operates in passive (STN) or active (TFT) display control mode. When LcdTFT=0 : passive or STN mode is selected; all LCD data flow operates normally (including the use of the LCD's dither logic); and all LCD controller pin timing operates as described in 1.5.7 LCD controller Pins on page 1-21. When LcdTFT=1, active or TFT mode is selected. Video data is transferred via the DMA from off-chip memory to the input FIFO, is unpacked and used to select an entry from the palette (for 4 and 8 bits-per-pixel modes), just as for passive mode. See Figure 1-13 on page 1-32.

The value read from the palette, however, bypasses the LCD's dither logic and is sent directly to the output FIFO to be output on the LCD's data pins. In TFT mode, the pixel size within the frame buffer is increased to 16 bits when 12- or 16-bit pixel encoding mode is enabled (BPP=11). Thus two 16-bit values are packed into each word in the frame buffer. See Figure 1-14 on page 1-33.

### Figure 1-14 Active mode pixel clock and data pin timing

The size of the pixel encoding is increased in TFT mode because the LCD's dither logic is bypassed (which only supports 3-bit RGB dithering). Increasing the size of the pixel representation allows a total of 64K colors to be addressed using an off-chip palette that is used in conjunction with the LCD controller.

## 1.7.7 LCD Big Endian (LcdBE)

The LCD Big Endian (LcdBE) bit selects whether the LCD controller views external memory organization or the frame buffer as big or little endian. When LcdBE=0, little endian mode is selected, and pixel data is organized within the off-chip frame buffer. This is shown between Figure 1-7 on page 1-21 and Figure 1-10 on page 1-22. Pixels are packed into words starting with the least significant nibble, byte or half-word. When LcdBE=1, big endian mode is selected and pixel data is organized in memory in individual words starting with the most significant nibble, byte or half-word. The big/little endian select bit also effects the ordering of palette buffer entries in the external

frame buffer. When LcdBE=0, half-word palette entries are packed into words starting with the least significant half-word. When LcdBE=1, palette entries are packed into half-words starting with the most significant half-word.

—— Note ———

The LcdBE does not affect the ordering of the 4-bit red/green/blue bit-fields, the 4-bit mono field within each 16-bit palette entry or the 2 bit-per-pixel (BPP) field contained with palette entry 0.

### 1.7.8 Mono 8 Bit Mode (M8B)

The Mono 8 Bit Mode (M8B) mode bit selects whether 4 or 8 bits are used to output pixel data to the LCD screen in single-panel or dual-panel monochrome mode.

When M8B=0, UPLcdData[3:0] is used to output four pixel values to the upper panel each pixel clock transition and UPLcdData[7:4] are used to output four pixel values to the lower panel of each pixel clock transition.

When M8B=1, UPLcdData[7:0] is used to output eight pixel values to the upper panel of each pixel clock, and LPLcdData[7:0] is used to output eight pixel values to the lower panel of each pixel clock.

—— Note ———

M8B does not affect any of the color modes.

### 1.7.9 1.7.10 FIFO DMA Request Delay (FDD)

The 8-bit FIFO DMA request delay (FDD) field is used to select the minimum number of memory controller clock cycles (half the frequency of the CPU clock) to wait between the servicing of each DMA request issued by the input FIFO. After a DMA request has completed, the value contained within FDD is loaded to a down counter that disables the input FIFO from issuing another DMA request until the counter decrements to zero. This counter ensures that the LCD's DMA does not fully consume the bandwidth of the AMBA bus. Once the counter reaches zero, any pending or future DMA requests by the FIFO cause the DMA to arbitrate for the ARM system bus (ASB). Once the DMA burst cycle has completed, the process re-starts and the value in FDD is loaded to the counter to create another delay period: this disables the FIFO from issuing a DMA request. FDD can be programmed with a value that causes the FIFO to wait from 0–255 memory clock cycles after the completion of one DMA request and before the start of the next request. When FDD=0h00, the FIFO DMA request delay function is disabled. This function is only used for palette loading.

Table 1-9 on page 1-36 shows the location of all seven bit-fields located in LCD control register (LcdControl). LcdEn is the only control bit that is reset to a known state, ensuring that the LCD is disabled after a reset of the LCD controller. The user must program all other control bit-fields before setting LcdEn=1 (a half-word or word write can be used to configure the whole register while setting LcdEn), and must also disable the LCD controller when changing the state of any control bit within the LCD controller.

\_\_\_\_\_ Note \_\_\_\_\_

Writes to reserved bits are ignored, and reads return zeros.

| Addres | ss: Oh | C100     | 0000 |    |      | ]    | LcdCont | rol: LCI |        |          |            | /Write    |           |       |       |       |  |  |

|--------|--------|----------|------|----|------|------|---------|----------|--------|----------|------------|-----------|-----------|-------|-------|-------|--|--|

| Bit    | 31     | 30       | 29   | 28 | 27   | 26   | 25      | 24       | 23     | 22       | 21         | 20        | 19        | 18    | 17    | 16    |  |  |

|        |        | Reserved |      |    |      |      |         |          |        |          |            |           |           | FDD   |       |       |  |  |

| Reset  | 0      | 0        | 0    | 0  | 0    | 0    | 0       | 0        | 0      | 0        | 0          | 0         | 0         | 0     | 0     | 0     |  |  |

| Bit    | 15     | 14       | 13   | 12 | 11   | 10   | 9       | 8        | 7      | б        | 5          | 4         | 3         | 2     | 1     | 0     |  |  |

|        |        | FI       | DD   |    | Rese | rved | M8B     | LcdBE    | LcdTFT | Reserved | Error Mask | Next Mask | Done Mask | LcdDP | LcdBW | LcdEn |  |  |

| Reset  | 0      | 0        | 0    | 0  | 0    | 0    | 0       | 0        | 0      | 0        | 0          | 0         | 0         | 0     | 0     | 0     |  |  |

## Figure 1-15 LCD control register LcdControl

Table 1-9 LCD control register LcdControl

| Bit | Name     | Description                                                                          |

|-----|----------|--------------------------------------------------------------------------------------|

| 0   | LcdEn    | LCD Controller Enable                                                                |

|     |          | 0 - LCD controller disabled                                                          |

|     |          | 1 - LCD controller enabled                                                           |

| 1   | LcdBW    | LCD Monochrome                                                                       |

|     |          | 0 - Color operation enabled                                                          |

|     |          | 1 - Monochrome operation enabled                                                     |

| 2   | LcdDP    | LCD Dual-Panel                                                                       |

|     |          | 0 - Single-panel display enabled, UPLcdData[3:0] used for monochrome, UPLcdData[7:0] |

|     |          | used for color                                                                       |

|     |          | 1 - Dual-panel display enabled, UPLcdData used for monochrome, UPLcdData and         |

|     |          | LPLcdData used for color                                                             |

| 3   | DoneMask | Done Mask                                                                            |

|     |          | 0 - Mask out the Frame Done (Done) Interrupt.                                        |

|     |          | 1 - Mask not active.                                                                 |

| 4   | NextMask | Next Mask                                                                            |

|     |          | 0 - Mask out the Next Frame (Next) Interrupt.                                        |

|     |          | 1 - Mask not active                                                                  |

| Bit   | Name      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5     | ErrorMask | Error Mask<br>0 - Mask out the Bus Error Status (BER) Interrupt<br>1 - Mask not active.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7     | LcdTFT    | LCD TFT<br>0 - Passive or STN display operation enabled, dither logic is enabled<br>1 - Active or TFT display operation enabled, external palette and DAC required, dither logic<br>bypassed, pin timing changes to support continuous pixel clock, output enable, VSYNC,<br>HSYNC signals                                                                                                                                                                                                                                                           |

| 8     | LcdBE     | <ul> <li>Lcd Big Endian</li> <li>0 - Little endian operation is selected, frame/pin buffer data is arranged into individual words of memory starting with the least significant nibble, byte or half-word</li> <li>1 - Big endian operation is selected, frame/pin buffer data is arranged into individual words of memory starting with the most significant nibble, byte or half-word</li> </ul>                                                                                                                                                   |

| 9     | M8B       | Mono 8 Bit Mode<br>0 - UPLcdData[3:0] is used to output four pixel values to the upper panel each pixel clock<br>transition and UPLcdData[7:4] are used to output four pixel values to the lower panel of<br>each pixel clock transition.<br>1 - UPLcdData[7:0] is used to output eight pixel values to the upper panel of each pixel<br>clock, and LPLcdData[7:0] is used to output eight pixel values to the lower panel of each<br>pixel clock<br><u>Note</u><br>This bit is ignored in all other modes of operation except for single panel mode |

| 11-10 | -         | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 19-12 | FDD       | FIFO DMA Request Delay<br>Encoded value (0—255) used to specify the number of memory controller clocks. The input<br>FIFO DMA request should be disabled. The clock count starts after the last write of each<br>burst cycle. While the counter is decrementing, all DMA requests from the input FIFO are<br>masked. When the counter reaches zero, any pending or subsequent DMA requests are<br>allowed to generate a four-word burst. Programming FDD=0h00 disables this function.                                                                |

| 31-16 |           | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

## Table 1-9 LCD control register LcdControl (continued)

# 1.8 LCD Timing 0 Register

LCD Timing 0 Register (LcdTiming0) contains four bit-fields that are used as modulus values for a collection of down counters, each of which performs a different function to control the timing of several of the LCD's pins.

## 1.8.1 Pixels-per-line (PPL)

The pixels-per-line (PPL) bit-field is used to specify the number of pixels in each line or row on the screen. PPL is a 10-bit value that represents between 1-1024 pixels-per-line. PPL is used to count the correct number of pixel clocks that must occur before the line clock can be pulsed. (The bottom 4 bits of this register are not used).

## 1.8.2 Horizontal Sync Pulse Width (HSW)

The 6-bit horizontal sync pulse width (HSW) field is used to specify the pulse width of the line clock in passive mode, or horizontal synchronization pulse in active mode. **LcdLP** is asserted each time a line or row of pixels is output to the display and a programmable number of pixel clock delays have elapsed. When line clock is asserted, the value in HSW is transferred to a 6-bit down counter that uses the programmed pixel clock frequency to decrement. When the counter reaches zero, the line clock is negated. HSW can be programmed to generate a line clock pulse width ranging from 0–63 pixel clock periods (program to value required minus one).

— Note –

The pixel clock does not transition during the line clock pulse in passive display mode, but transitions in active display mode. Also, the polarity (active and inactive state) of the line clock is programmed using the Invert Hsync (IHS) bit in LcdTiming2.

### 1.8.3 Horizontal Front Porch (HFP)

The 8-bit Horizontal Front Porch (HFP) field is used to specify the number of dummy pixel clocks to insert at the end of each line or row of pixels before pulsing the line clock pin. Once a complete line of pixels is transmitted to the LCD driver, the value in HFP is used to count the number of pixel clocks to wait before pulsing the line clock. HFP generates a wait period ranging from 0–255 pixel clock cycles (program to value required minus one).

— Note –