# AMBA<sup>®</sup> Level 2 Cache Controller (L2C-310)

Revision: r3p0

**Technical Reference Manual**

#### AMBA Level 2 Cache Controller (L2C-310)

#### **Technical Reference Manual**

Copyright © 2007-2009 ARM. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

#### Change history

| Date             | Issue | Confidentiality                      | Change                 |

|------------------|-------|--------------------------------------|------------------------|

| 30 November 2007 | A     | Non-Confidential                     | First release for r0p0 |

| 04 April 2008    | В     | Non-Confidential                     | First release for r1p0 |

| 19 December 2008 | С     | Non-Confidential Unrestricted Access | First release for r2p0 |

| 02 October 2009  | D     | Non-Confidential Unrestricted Access | First release for r3p0 |

#### **Proprietary Notice**

Words and logos marked with  $^*$  or  $^{\text{m}}$  are registered trademarks or trademarks of ARM $^*$  in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

Unrestricted Access is an ARM internal classification.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

### Contents

# AMBA Level 2 Cache Controller (L2C-310) Technical Reference Manual

|            | Pref  | ace                                               |      |

|------------|-------|---------------------------------------------------|------|

|            |       | About this book                                   | xi   |

|            |       | Feedback                                          |      |

| Chapter 1  | Intro | oduction                                          |      |

| -          | 1.1   | About the AMBA Level 2 Cache Controller (L2C-310) | 1-2  |

|            | 1.2   | Typical system configuration                      |      |

|            | 1.3   | Product revisions                                 |      |

| Chapter 2  | Fund  | ctional Overview                                  |      |

| •          | 2.1   | Cache configurability                             | 2-2  |

|            | 2.2   | AXI master and slave interfaces                   |      |

|            | 2.3   | Cache operation                                   | 2-12 |

|            | 2.4   | RAM interfaces                                    |      |

|            | 2.5   | Implementation details                            |      |

|            | 2.6   | Power modes                                       |      |

| Chapter 3  | Prog  | grammers Model                                    |      |

| -          | 3.1   | About this programmers model                      | 3-2  |

|            | 3.2   | Register summary                                  |      |

|            | 3.3   | Register descriptions                             |      |

| Appendix A | Sian  | nal Descriptions                                  |      |

|            | A.1   | Clock and reset                                   | A-2  |

|            | A.2   | Configuration                                     |      |

|            | A.3   | Slave and master ports                            |      |

|            |       | <del> </del>                                      |      |

| C.2<br>C.3<br>C.4<br>C.5<br>C.6<br>C.7 | Single read miss transaction Single non-cacheable read transaction Outstanding read hit transactions Hit under miss read transactions Single bufferable write transaction Single non-bufferable write transaction |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C.2<br>C.3<br>C.4<br>C.5<br>C.6        | Single read miss transaction Single non-cacheable read transaction Outstanding read hit transactions Hit under miss read transactions Single bufferable write transaction                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| C.2<br>C.3<br>C.4<br>C.5               | Single read miss transaction Single non-cacheable read transaction Outstanding read hit transactions Hit under miss read transactions                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| C.2<br>C.3<br>C.4                      | Single read miss transaction Single non-cacheable read transaction Outstanding read hit transactions                                                                                                              | C-3<br>C-4<br>C-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| C.2<br>C.3                             | Single read miss transaction                                                                                                                                                                                      | C-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| C.2                                    | Single read miss transaction                                                                                                                                                                                      | C-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                        |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| C.1                                    |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                        | Single read hit transaction                                                                                                                                                                                       | C-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Timir                                  | ng Diagrams                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| B.9                                    | MBIST interface input and output signal timing parameters                                                                                                                                                         | B-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| B.8                                    | Cache interrupt ports signal timing parameters                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| B.7                                    | Event monitor input and output signal timing parameters                                                                                                                                                           | B-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| B.6                                    | RAMs signal timing parameters                                                                                                                                                                                     | B-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| B.5                                    | Master port 1 input and output signal timing parameters                                                                                                                                                           | B-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| B.4                                    | Master port 0 input and output signal timing parameters                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| B.3                                    |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| B.2                                    |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| B.1                                    | Reset and configuration signal timing parameters                                                                                                                                                                  | B-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AC F                                   | Parameters                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A.7                                    | MBIST interface                                                                                                                                                                                                   | A-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                        | •                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A.5                                    | <u> </u>                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A.4                                    | RAM interface                                                                                                                                                                                                     | A-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                        | A.5<br>A.6<br>A.7<br>AC F<br>B.1<br>B.2<br>B.3<br>B.4<br>B.5<br>B.6<br>B.7<br>B.8<br>B.9                                                                                                                          | A.5 Cache event monitoring A.6 Cache interrupt A.7 MBIST interface  AC Parameters B.1 Reset and configuration signal timing parameters B.2 Slave port 0 input and output signal timing parameters B.3 Slave port 1 input and output signal timing parameters B.4 Master port 0 input and output signal timing parameters B.5 Master port 1 input and output signal timing parameters B.6 RAMs signal timing parameters B.7 Event monitor input and output signal timing parameters B.8 Cache interrupt ports signal timing parameters B.9 MBIST interface input and output signal timing parameters  Timing Diagrams |

### **List of Tables**

# AMBA Level 2 Cache Controller (L2C-310) Technical Reference Manual

|            | Change history                                                       | i                |

|------------|----------------------------------------------------------------------|------------------|

| Table 1-1  | Typical memory sizes and access times                                |                  |

| Table 1-2  | RTL options                                                          | 1-4              |

| Table 1-3  | Master port transactions for a two master port system                | 1-6              |

| Table 2-1  | Cache controller cache configurability                               | 2-2              |

| Table 2-2  | AXI master interface attributes                                      | 2-3              |

| Table 2-3  | AXI slave interface attributes                                       | 2-4              |

| Table 2-4  | Master port ID values for writes                                     | 2-8              |

| Table 2-5  | Master port ID values for reads                                      |                  |

| Table 2-6  | Exported master ports AXI control signals                            | 2-9              |

| Table 2-7  | Non-cacheable and non-bufferable AXI transactions                    | 2-12             |

| Table 2-8  | Bufferable only AXI transactions                                     |                  |

| Table 2-9  | Cacheable but do not allocate AXI transactions                       | 2-12             |

| Table 2-10 | Cacheable write-through, allocate on read AXI transactions           | 2-12             |

| Table 2-11 | Cacheable write-back, allocate on read AXI transactions              | 2-13             |

| Table 2-12 | Cacheable write-through, allocate on write AXI transactions          | 2-13             |

| Table 2-13 | Cacheable write-back, allocate on write AXI transactions             |                  |

| Table 2-14 | Cacheable write-through, allocate on read and write AXI transactions | 2-14             |

| Table 2-15 | Cacheable write-back, allocate on read and write AXI transactions    | 2-14             |

| Table 2-16 | AWCACHE and ARCACHE definitions                                      | 2-1              |

| Table 2-17 | MP4 system lockdown register definitions                             | 2-2              |

| Table 2-18 | MPI plus APC system lockdown register definitions.                   | 2-22             |

| Table 2-19 | Data RAM bank identification                                         | 2-2              |

| Table 2-20 | RAM clock enables                                                    | 2-3 <sup>-</sup> |

| Table 2-21 | L2C-310 master port behavior                                         | 2-39             |

| Table 2-22 | Error responses for all combinations of L3 access                    | 2-40             |

| Table 2-23 | Event pins                                                           | 2-4 <sup>2</sup> |

| Table 2-24 | Interrupts                                                              | 2-42 |

|------------|-------------------------------------------------------------------------|------|

| Table 2-25 | Cacheable read requests on AXI slave ports                              |      |

| Table 2-26 | Write-through/write-back write access from store buffer                 |      |

| Table 2-27 | AXI M0 and AXI M1 masters or store buffer allocation requests           |      |

| Table 2-28 | Clean maintenance operation cases                                       |      |

| Table 2-29 | Invalidate maintenance operation cases                                  |      |

| Table 2-30 | Clean and Invalidate maintenance operation cases                        |      |

| Table 3-1  | Cache controller register map                                           |      |

| Table 3-2  | Summary of cache controller registers                                   |      |

| Table 3-3  | reg0_cache_id Register bit assignments                                  |      |

| Table 3-4  | reg0_cache_type Register bit assignments                                |      |

| Table 3-5  | reg1 control Register bit assignments                                   |      |

| Table 3-6  | reg1_aux_control Register bit assignments                               |      |

| Table 3-7  | reg1_tag_ram_control and reg1_data_ram_control Register bit assignments |      |

| Table 3-7  | reg2_ev_counter_ctrl Register bit assignments                           |      |

|            | reg2_ev_counter0_cfg and reg2_ev_counter1_cfg Register bit assignments  |      |

| Table 3-9  |                                                                         |      |

| Table 3-10 | reg2_ev_counter0 and reg2_ev_counter1 Register bit assignments          |      |

| Table 3-11 | reg2_int_mask Register bit assignments                                  |      |

| Table 3-12 | Masked Interrupt Status Register bit assignments                        |      |

| Table 3-13 | reg2_int_raw_status Register bit assignments                            |      |

| Table 3-14 | reg2_int_clear Register bit assignments                                 |      |

| Table 3-15 | Maintenance operations                                                  |      |

| Table 3-16 | Cache maintenance operations                                            |      |

| Table 3-17 | Cache lockdown                                                          |      |

| Table 3-18 | Lockdown by Line Enable Register bit assignments                        |      |

| Table 3-19 | Unlock All Lines Register bit assignments                               |      |

| Table 3-20 | Data Lockdown 0 Register, offset 0x900                                  |      |

| Table 3-21 | Instruction Lockdown 0 Register, offset 0x904                           |      |

| Table 3-22 | Data Lockdown 1 Register, offset 0x908                                  |      |

| Table 3-23 | Instruction Lockdown 1 Register, offset 0x90C                           |      |

| Table 3-24 | Data Lockdown 2 Register, offset 0x910                                  |      |

| Table 3-25 | Instruction Lockdown 2 Register, offset 0x914                           |      |

| Table 3-26 | Data Lockdown 3 Register, offset 0x918                                  | 3-29 |

| Table 3-27 | Instruction Lockdown 3 Register, offset 0x91C                           | 3-29 |

| Table 3-28 | Data Lockdown 4 Register, offset 0x920                                  | 3-29 |

| Table 3-29 | Instruction Lockdown 4 Register, offset 0x924                           | 3-30 |

| Table 3-30 | Data Lockdown 5 Register, offset 0x928                                  |      |

| Table 3-31 | Instruction Lockdown 5 Register, offset 0x92C                           | 3-30 |

| Table 3-32 | Data Lockdown 6 Register, offset 0x930                                  | 3-30 |

| Table 3-33 | Instruction Lockdown 6 Register, offset 0x934                           | 3-30 |

| Table 3-34 | Data Lockdown 7 Register, offset 0x938                                  | 3-30 |

| Table 3-35 | Instruction Lockdown 7 Register, offset 0x93C                           | 3-30 |

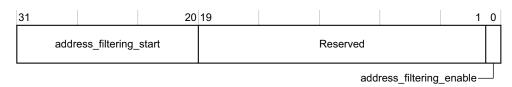

| Table 3-36 | Address Filtering Start Register bit assignments                        |      |

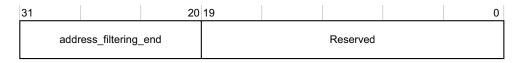

| Table 3-37 | Address Filtering End Register bit assignments                          |      |

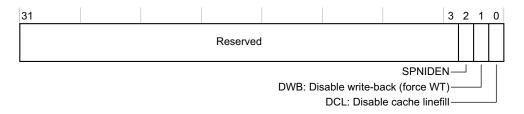

| Table 3-38 | Debug Control Register bit assignments                                  |      |

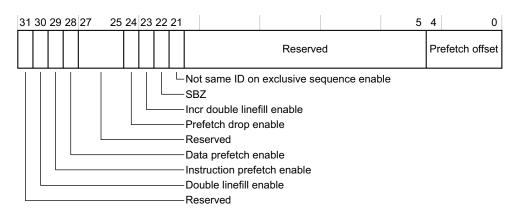

| Table 3-39 | Prefetch Control Register bit assignments                               |      |

| Table 3-40 | pwr_ctrl Register bit assignments                                       |      |

| Table A-1  | Clock and reset signals                                                 |      |

| Table A-2  | Configuration signals                                                   |      |

| Table A-3  | Slave port 0 signals                                                    |      |

| Table A-4  | Slave port 1 signals                                                    |      |

| Table A-5  | Master port 0 signals                                                   |      |

| Table A-5  | Master port 1 signals                                                   |      |

| Table A-6  | Data RAM interface signals                                              |      |

| Table A-7  | Tag RAM interface                                                       |      |

| Table A-6  |                                                                         |      |

|            | Cache interrupt signals                                                 |      |

| Table A-10 | Cache interrupt signals                                                 |      |

| Table A-11 | MBIST interface signals                                                 |      |

| Table B-1  | Reset and configuration                                                 |      |

| Table B-2  | Slave port 0 inputs and outputs                                         | B-3  |

| Table B-3  | Slave port 1 inputs and outputs           | B-5  |

|------------|-------------------------------------------|------|

| Table B-4  | Master port 0 inputs and outputs          | B-7  |

| Table B-5  | Master port 1 inputs and outputs          |      |

| Table B-6  | Data RAM inputs and outputs               |      |

| Table B-7  | Tag RAM inputs and outputs                | B-12 |

| Table B-8  | Event monitor inputs and outputs          | B-13 |

| Table B-9  | Cache interrupt ports                     | B-14 |

| Table B-10 | MBIST interface signal inputs and outputs | B-15 |

| Table D-1  | Differences between issue C and issue D   |      |

### List of Figures

# AMBA Level 2 Cache Controller (L2C-310) Technical Reference Manual

|             | Key to timing diagram conventions                                                              | xii     |

|-------------|------------------------------------------------------------------------------------------------|---------|

| Figure 1-1  | Top-level diagram                                                                              | 1-2     |

| Figure 1-2  | Example cache controller interfaced to an ARM processor                                        | 1-6     |

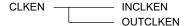

| Figure 2-1  | CLKEN used to drive cache controller inputs in case of integer clock ratio                     | 2-5     |

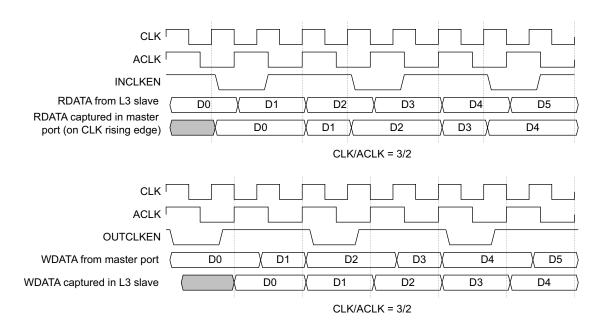

| Figure 2-2  | Clock enable usage model for 1.5:1 clock ratio in master port                                  |         |

| Figure 2-3  | Clock enable usage model for 2.5:1 clock ratio in master port                                  | 2-6     |

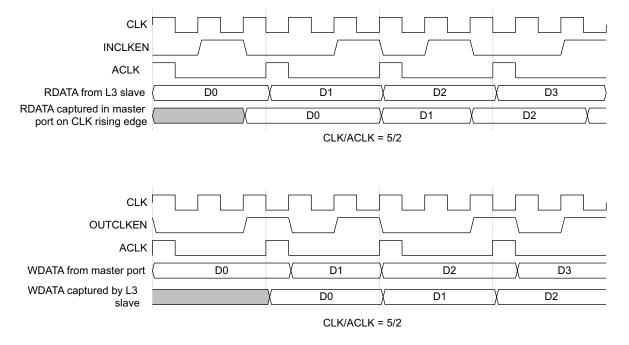

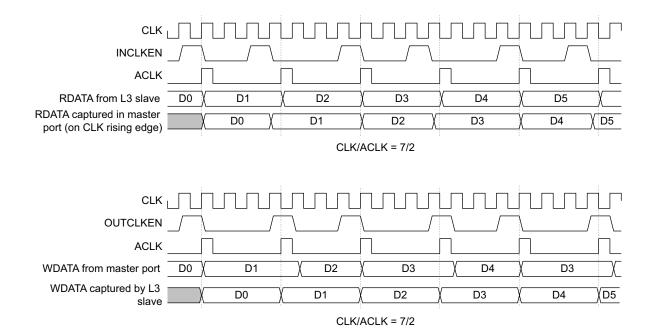

| Figure 2-4  | Clock enable usage model for 3.5:1 clock ratio in master port                                  | 2-7     |

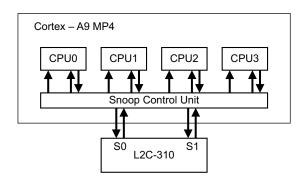

| Figure 2-5  | Driven by cortex a9 cluster with 4 CPUs                                                        | 2-20    |

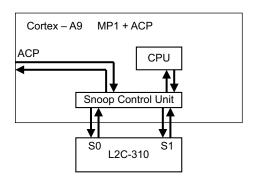

| Figure 2-6  | Driven by cortex a9 cluster with 1 CPU and ACP                                                 | 2-21    |

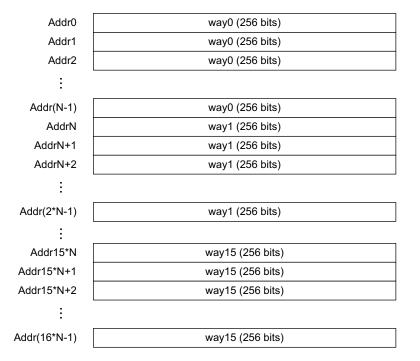

| Figure 2-7  | No multi banking                                                                               | 2-23    |

| Figure 2-8  | Multi banking                                                                                  | 2-23    |

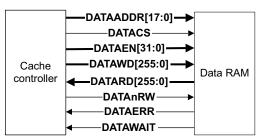

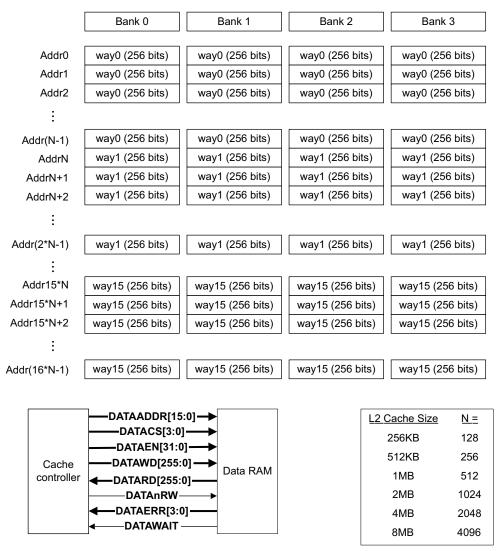

| Figure 2-9  | Data RAM organization for 16 ways                                                              | 2-24    |

| Figure 2-10 | Data RAM with banking and 16 ways                                                              | 2-26    |

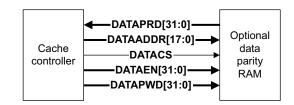

| Figure 2-11 | Data parity RAM without banking organization                                                   | 2-26    |

| Figure 2-12 | Data parity RAM with banking organization                                                      | 2-27    |

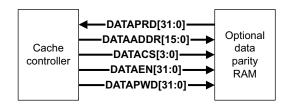

| Figure 2-13 | Tag RAM organization for a 16-way 256KB L2 cache, with parity, with lockdown by line           | 2-28    |

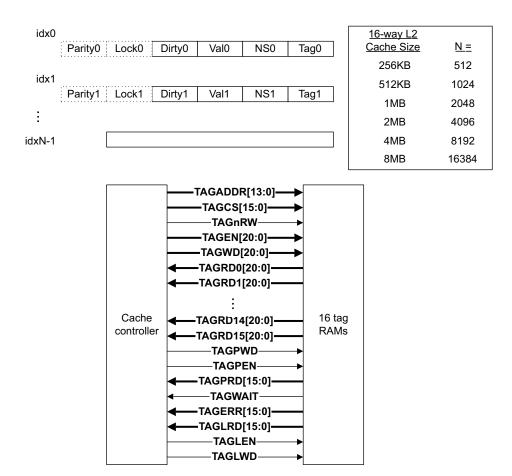

| Figure 2-14 | Data RAM address bus format for 16 ways without banking                                        | 2-29    |

| Figure 2-15 | Data RAM address bus format for 16 ways with banking                                           | 2-29    |

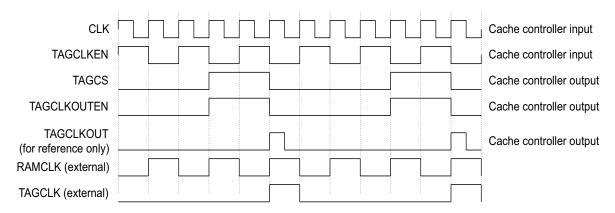

| Figure 2-16 | Tag RAM running at slower frequency                                                            |         |

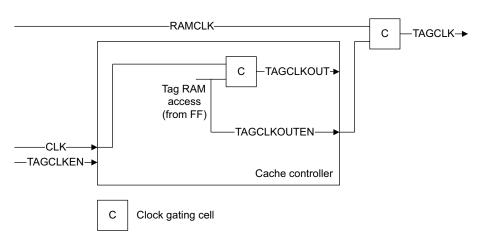

| Figure 2-17 | Tag RAM clock gating                                                                           | 2-32    |

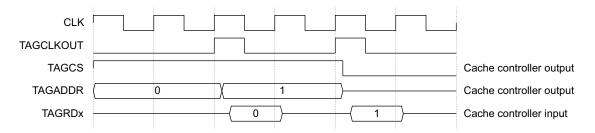

| Figure 2-18 | Tag RAM setup latency                                                                          | 2-33    |

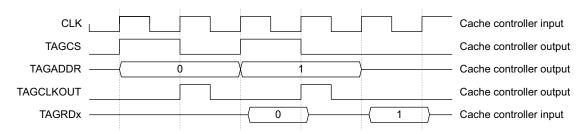

| Figure 2-19 | Tag RAM read access latency                                                                    | 2-33    |

| Figure 2-20 | Tag RAM write access latency                                                                   | 2-33    |

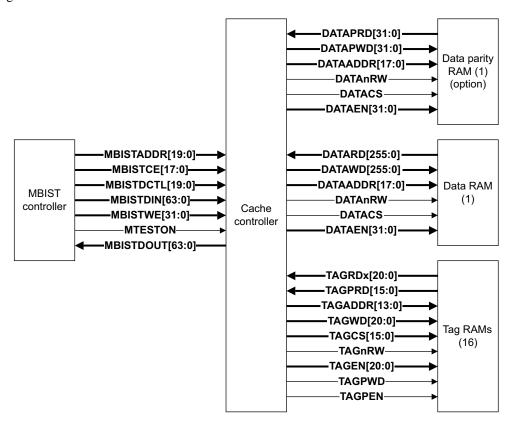

| Figure 2-21 | MBIST interface for 16-way implementation, with parity, without lockdown by line, without 2-34 | banking |

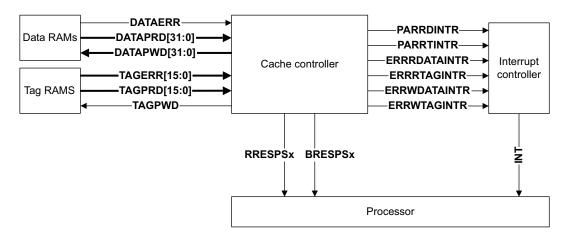

| Figure 2-22 | Parity and RAM error support for a 16-way implementation without banking                       | 2-43    |

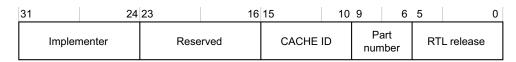

| Figure 3-1  | reg0_cache_id Register bit assignments                                                         | 3-7     |

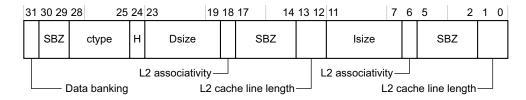

| Figure 3-2  | reg0_cache_type Register bit assignments                                | 3-8  |

|-------------|-------------------------------------------------------------------------|------|

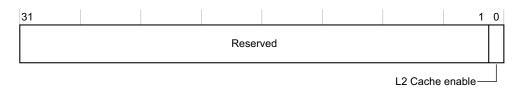

| Figure 3-3  | reg1_control Register bit assignments                                   |      |

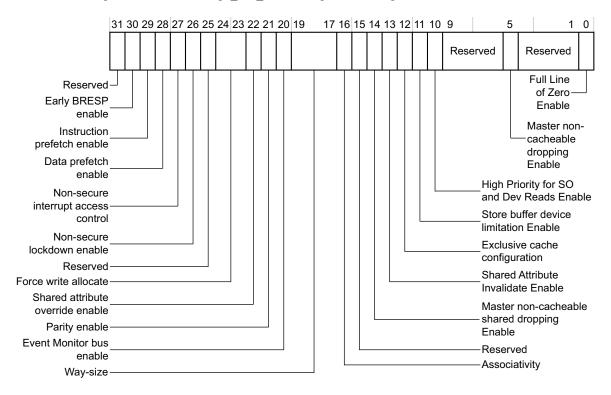

| Figure 3-4  | reg1_aux_control Register bit assignments                               | 3-10 |

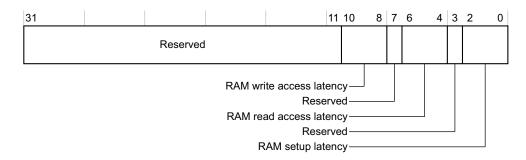

| Figure 3-5  | reg1_tag_ram_control and reg1_data_ram_control Register bit assignments | 3-13 |

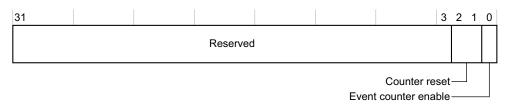

| Figure 3-6  | reg2_ev_counter_ctrl Register bit assignments                           | 3-14 |

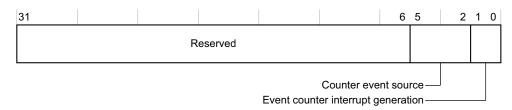

| Figure 3-7  | reg2_ev_counter0_cfg and reg2_ev_counter1_cfg Register bit assignments  | 3-15 |

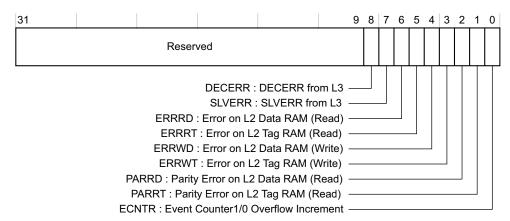

| Figure 3-8  | Interrupt Register bit assignments                                      |      |

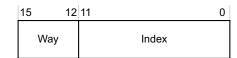

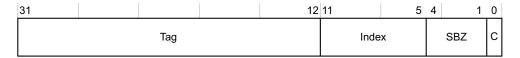

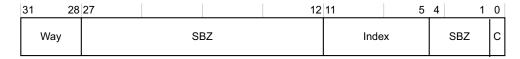

| Figure 3-9  | Physical address format                                                 | 3-22 |

| Figure 3-10 | Index or way format                                                     | 3-22 |

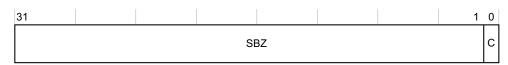

| Figure 3-11 | Cache sync format                                                       | 3-22 |

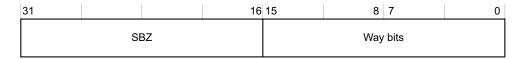

| Figure 3-12 | Way format                                                              | 3-23 |

| Figure 3-13 | Address Filtering Start Register bit assignments                        | 3-31 |

| Figure 3-14 | Address Filtering End Register bit assignments                          | 3-32 |

| Figure 3-15 | Debug Control Register bit assignments                                  | 3-33 |

| Figure 3-16 | Prefetch Control Register bit assignments                               | 3-34 |

| Figure 3-17 | pwr_ctrl Register bit assignments                                       | 3-35 |

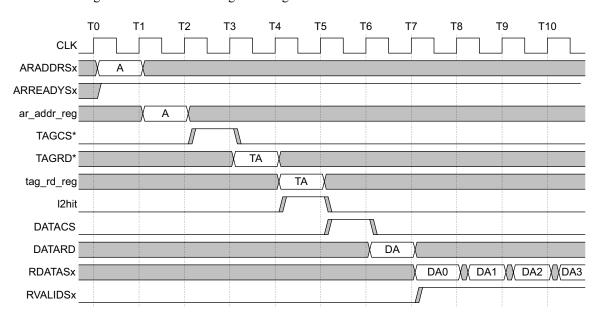

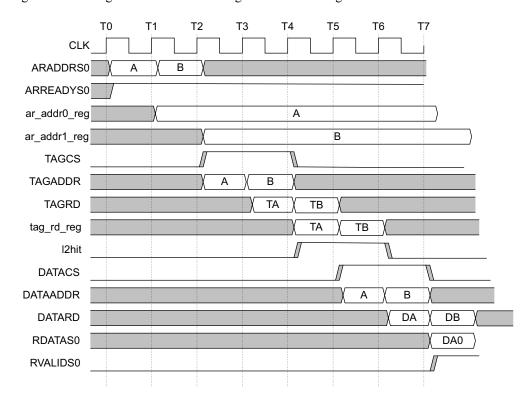

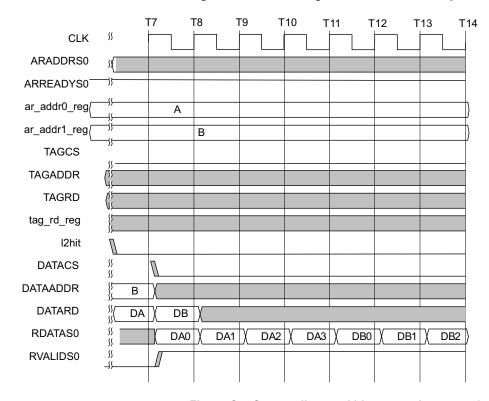

| Figure C-1  | Single read hit transaction                                             | C-2  |

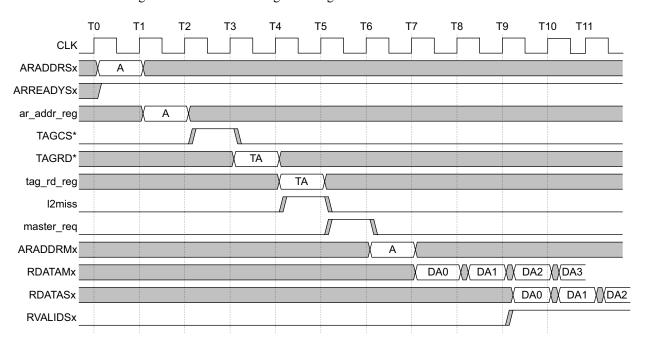

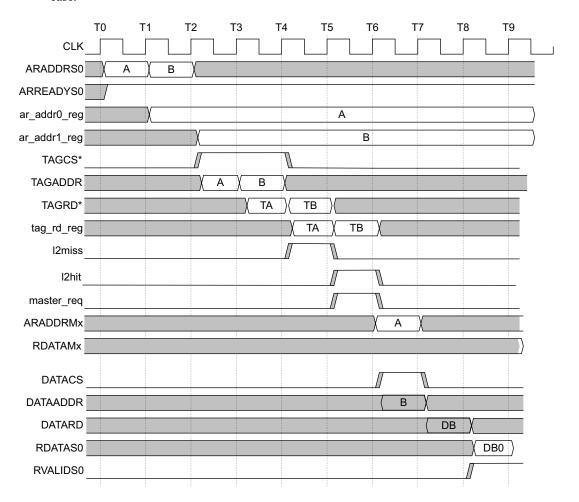

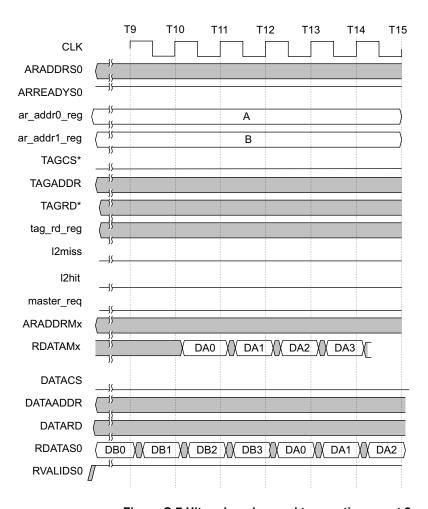

| Figure C-2  | Single read miss transaction                                            | C-3  |

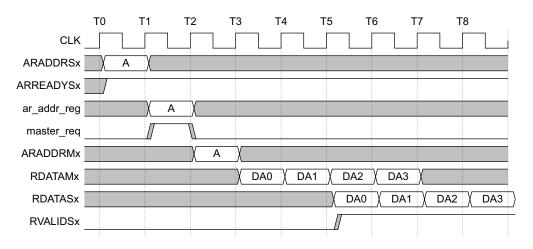

| Figure C-3  | Single non-cacheable read transaction                                   | C-4  |

| Figure C-4  | Outstanding read hit transactions, part 1                               | C-5  |

| Figure C-5  | Outstanding read hit transactions, part 2                               | C-5  |

| Figure C-6  | Hit under miss read transactions, part 1                                | C-6  |

| Figure C-7  | Hit under miss read transactions, part 2                                | C-7  |

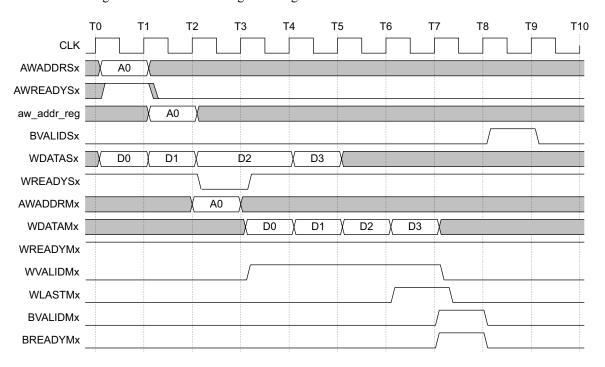

| Figure C-8  | Single bufferable write transaction                                     | C-8  |

| Figure C-9  | Single non-bufferable write transaction                                 | C-9  |

### **Preface**

This preface introduces the *AMBA Level 2 Cache Controller (L2C-310) Technical Reference Manual*. It contains the following sections:

- About this book on page xi

- Feedback on page xiv.

#### About this book

This book is for the AMBA Level 2 Cache Controller (L2C-310).

#### **Product revision status**

The rnpn identifier indicates the revision status of the product described in this book, where:

**rn** Identifies the major revision of the product.

**pn** Identifies the minor revision or modification status of the product.

#### Intended audience

This book is written for hardware and software engineers implementing the AMBA Level 2 Cache Controller into ASIC designs. It provides information to enable designers to integrate the device into a target system as quickly as possible.

#### Using this book

This book is organized into the following chapters:

#### Chapter 1 Introduction

Read this for an introduction to the cache controller.

#### Chapter 2 Functional Overview

Read this for a description of a functional overview and the functional operation of the cache controller.

#### Chapter 3 Programmers Model

Read this for a description of the cache controller registers for programming details.

#### Appendix A Signal Descriptions

Read this for a description of the signals used in the cache controller.

#### Appendix B AC Parameters

Read this for a description of the AC signal timing parameters

#### Appendix C Timing Diagrams

Read this for a description of cache controller timing diagrams.

#### Appendix D Revisions

Read this for a description of the technical changes between released issues of this book.

#### Glossary

Read this for definitions of terms used in this manual.

#### Conventions

Conventions that this book can use are described in:

- Typographical on page xii

- Timing diagrams on page xii

- Signals on page xii.

#### **Typographical**

The typographical conventions are:

*italic* Highlights important notes, introduces special terminology, denotes

internal cross-references, and citations.

bold Highlights interface elements, such as menu names. Denotes signal

names. Also used for terms in descriptive lists, where appropriate.

monospace Denotes text that you can enter at the keyboard, such as commands, file

and program names, and source code.

monospace Denotes a permitted abbreviation for a command or option. You can enter

the underlined text instead of the full command or option name.

monospace italic Denotes arguments to monospace text where the argument is to be

replaced by a specific value.

monospace bold Denotes language keywords when used outside example code.

< and > Enclose replaceable terms for assembler syntax where they appear in code

or code fragments. For example:

MRC p15, 0 <Rd>, <CRn>, <CRm>, <Opcode\_2>

#### **Timing diagrams**

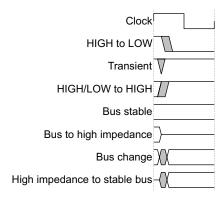

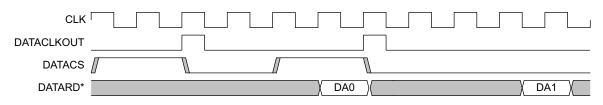

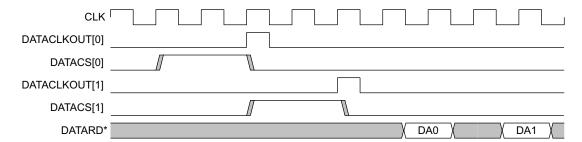

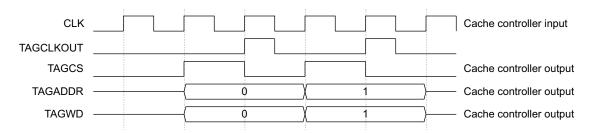

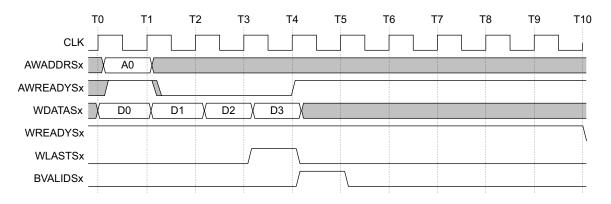

The figure named *Key to timing diagram conventions* explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

Key to timing diagram conventions

#### **Signals**

The signal conventions are:

**Signal level** The level of an asserted signal depends on whether the signal is

active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals

- LOW for active-LOW signals.

**Lower-case n** At the start or end of a signal name denotes an active-LOW signal.

#### **Additional reading**

This section lists publications by ARM and by third parties.

See Infocenter, http://infocenter.arm.com, for access to ARM documentation.

#### **ARM** publications

This book contains information that is specific to this product. See the following documents for other relevant information:

- AMBA AXI Protocol Specification (ARM IHI 0022)

- ARM Architecture Reference Manual ARM v7-A and ARM v7-R (ARM DDI 0406)

- AMBA Level 2 MBIST Controller (L2C-310) Technical Reference Manual (ARM DDI 0402)

- AMBA Level 2 Cache Controller (L2C-310) Implementation Guide (ARM DII 0045)

- *Cortex*<sup>™</sup>-*A9 Technical Reference Manual* (ARM DDI 0388)

- Cortex<sup>™</sup>-A9 MPCore Technical Reference Manual (ARM DDI 0407).

#### **Feedback**

ARM welcomes feedback on this product and its documentation.

#### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

#### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- the title

- the number, ARM DDI 0246D

- the page numbers to which your comments apply

- a concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

#### **Customer support**

Customers with active support contracts can obtain support for ARM Physical Intellectual Property products by going to DesignStart, http://access.arm.com and clicking on the **Login** link on the left side of the web page to obtain prompt attention to issues and questions.

See Support Programs, http://www.arm.com/products/physicalip/support for information about support contract options.

If you cannot contact ARM through the web support channel then send an e-mail to support-pipd@arm.com.

## Chapter 1 **Introduction**

This chapter introduces the AMBA Level 2 Cache Controller (L2C-310) and its features. It contains the following sections:

- About the AMBA Level 2 Cache Controller (L2C-310) on page 1-2

- Typical system configuration on page 1-6

- Product revisions on page 1-8.

#### 1.1 About the AMBA Level 2 Cache Controller (L2C-310)

The addition of an on-chip secondary cache, also referred to as a Level 2 or L2 cache, is a recognized method of improving the performance of ARM-based systems when significant memory traffic is generated by the processor. By definition a secondary cache assumes the presence of a Level 1 or primary cache, closely coupled or internal to the processor.

Memory access is fastest to L1 cache, followed closely by L2 cache. Memory access is typically significantly slower with L3 main memory. Table 1-1 shows typical sizes and access times for different types of memory.

| Memory type                   | Typical size | Typical access time |

|-------------------------------|--------------|---------------------|

| Processor registers           | 128B         | 1 cycle             |

| On-chip L1 cache              | 32KB         | 1-2 cycles          |

| On-chip L2 cache              | 256KB        | 8 cycles            |

| Main memory, L3, dynamic RAM  | MB or GBa    | 30-100 cycles       |

| Back-up memory, hard disk, L4 | MB or GB     | > 500 cycles        |

Table 1-1 Typical memory sizes and access times

The cache controller features:

- TrustZone architecture for enhanced OS security.

- Slave and master AMBA AXI interfaces designed for high performance systems.

The cache controller is a unified, physically addressed, physically tagged cache with up to 16 ways. You can lock the replacement algorithm on a way basis, enabling the associativity to be reduced from 16-way down to 1-way (direct mapped).

The cache controller does not have snooping hardware to maintain coherency between caches, so you must maintain coherency by software.

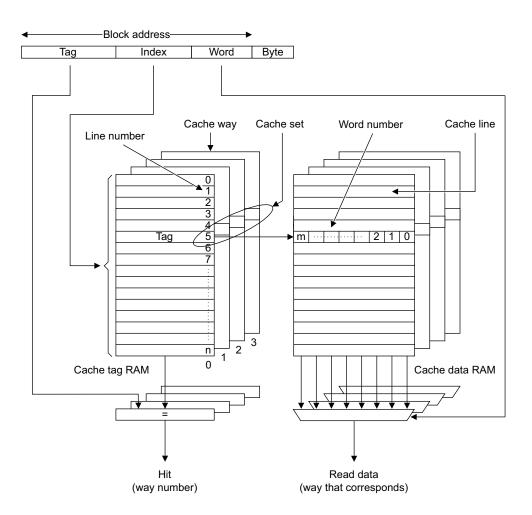

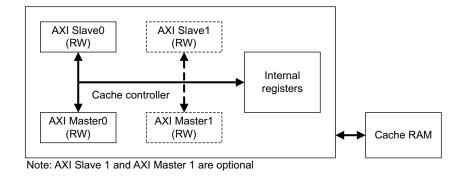

Figure 1-1 shows a top level diagram of the cache controller.

Figure 1-1 Top-level diagram

#### 1.1.1 Features

The cache controller has the following features:

Physically addressed and physically tagged.

a. Size limited by the processor core addressing, for example a 32-bit processor without memory management can directly address 4GB of memory.

| • | Lockdown format C supported, for data and instructions. |

|---|---------------------------------------------------------|

|   | Note                                                    |

|   | Lockdown format C is also known as way locking.         |

- Lockdown by line supported.

- Lockdown by master ID supported.

- L2 cache available size can be 16KB to 8MB, depending on configuration and the use of the lockdown registers.

- Direct mapped to 16-way associativity, depending on the configuration and the use of lockdown registers. The associativity is RTL configurable as 8 or 16.

- Fixed line length of 32 bytes, eight words or 256 bits.

- Interface to data RAM is byte writable.

- Banking on data RAM supported.

- Supports all of the AXI cache modes:

- write-through and write-back

- read allocate, write allocate, read and write allocate.

- Force write allocate option to always have cacheable writes allocated to L2 cache, for processors not supporting this mode.

- Normal memory non-cacheable shared reads are treated as cacheable non-allocatable.

Normal memory non-cacheable shared writes are treated as cacheable write-through no write-allocate. There is an option, Shared Override, to override this behavior. For information on the Shared attribute see *Shareable attribute* on page 2-16.

- TrustZone support, with the following features:

- Non-Secure (NS) tag bit added in tag RAM and used for lookup in the same way as an address bit. The NS-tag bit is added in all buffers.

- NS bit in Tag RAM used to determine security level of evictions to L3.

- Restrictions for NS accesses for control, configuration, and maintenance registers to restrict access to secure data.

- Critical word first linefill supported.

- Pseudo-Random, or round-robin victim selection policy. You can make this deterministic with use of lockdown registers.

- Four 256-bit *Line Fill Buffers* (LFBs), shared by the master ports. These buffers capture linefill data from main memory, waiting for a complete line before writing to L2 cache memory.

- Two 256-bit *Line Read Buffers* (LRBs) for each slave port. These buffers hold a line from the L2 memory for a cache hit.

- Three 256-bit Eviction Buffers (EBs). These buffers hold evicted lines from the L2 cache, to be written back to main memory.

- Three 256-bit *Store Buffers* (STBs). These buffers hold bufferable writes before their draining to main memory, or the L2 cache. They enable multiple writes to the same line to be merged.

- Supports outstanding accesses on slave and master ports.

- Option to select one or two master ports.

- Option to select one or two slave ports. If only one slave is supported, only one master is configured.

- Software option to enable exclusive cache configuration, see Cache operation on page 2-12 for more information.

- Prefetching capability. See Auxiliary Control Register on page 3-10 for more information.

- Support for integer, 1:1, 2:1, and half-integer, 1.5:1, 2.5:1, clock ratios controlled by clock enable inputs on slave and master ports.

- Wait, latency, clock enable, parity, and error support at the RAM interfaces.

- MBIST support.

- L2 cache event monitoring. Event signals are exported if you want to use these in conjunction with an event monitoring block. Event monitoring is also offered in the cache controller with two programmable 32-bit counters. Secure event and performance signals are only available when the signal on the **SPNIDEN** pin is configured HIGH.

- Configuration registers accessible using address decoding in the slave ports.

- Address filtering in the master ports enabling redirection of a certain address range to one

master port while all other addresses are redirected to the other one.

A number of RTL options enable you to implement the RTL with different features present or absent, as shown in Table 1-2.

Table 1-2 RTL options

| Feature                | RTL option                                                                                                               |

|------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 16-way associativity   | pl310_16_WAYS                                                                                                            |

| Data RAM banking       | pl310_DATA_BANKING                                                                                                       |

| Number of slave ports  | pl310_S1                                                                                                                 |

| Number of master ports | pl310_M1, requires pl310_S1                                                                                              |

| Parity                 | pl310_PARITY                                                                                                             |

| Address filtering      | pl310_ADDRESS_FILTERING, requires pl310_M1                                                                               |

| Lockdown by master     | pl310_LOCKDOWN_BY_MASTER                                                                                                 |

| Lockdown by line       | pl310_LOCKDOWN_BY_LINE                                                                                                   |

| Speculative read logic | pl310_SPECULATIVE_READ                                                                                                   |

| Slave AXI ID width     | pl310_AXI_ID_MAX                                                                                                         |

| RAM latencies          | p1310_TAG_SETUP_LAT p1310_TAG_READ_LAT p1310_TAG_WRITE_LAT p1310_DATA_SETUP_LAT p1310_DATA_READ_LAT p1310_DATA_WRITE_LAT |

Cache configurability on page 2-2 shows how you can use these RTL options to configure the cache controller.

| Note                                                                    |             |

|-------------------------------------------------------------------------|-------------|

| Before synthesis you must define these options in the p1310_defs.v $Ve$ | erilog file |

The cache controller is configured using memory-mapped registers, rather than using CP15 instructions. See Chapter 3 *Programmers Model* for more information.

The cache controller is designed to work with 64-bit AXI masters. No particular primary cache architecture is assumed.

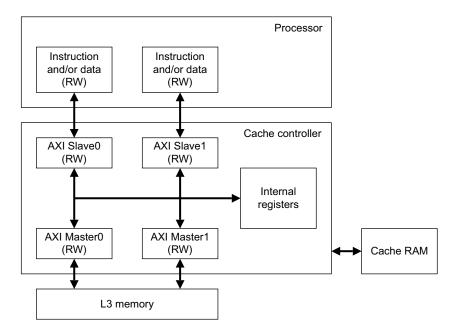

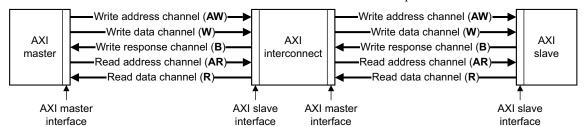

#### 1.2 Typical system configuration

The cache controller works efficiently with ARM processors that implement AXI interfaces. It directly interfaces on the data and instruction interface. The internal pipelining of the cache controller is optimized to enable the processors to operate at the same clock frequency.

The cache controller supports:

- One or two read/write 64-bit slave ports for interfacing with data and instruction interfaces.

- One or two read/write 64-bit master ports for interfacing with L3 memory system.

Figure 1-2 shows an example of a cache controller with two slave ports and two master ports interfaced to an ARM processor.

Figure 1-2 Example cache controller interfaced to an ARM processor

You can configure the cache controller to use one or two master ports. Table 1-3 shows what each master port is used for.

Table 1-3 Master port transactions for a two master port system

| Master port 0                    | Master port 1                    |

|----------------------------------|----------------------------------|

| Non-cacheable reads from S0      | Non-cacheable reads from S1      |

| Linefills from S0 or S1          | Linefills from S0 or S1          |

| Write allocations reads from STB | Write allocations reads from STB |

| Non-bufferable writes from S0    | Non-bufferable writes from S1    |

| Bufferable writes from STB       | Bufferable writes from STB       |

| Evictions from EB                | Evictions from EB                |

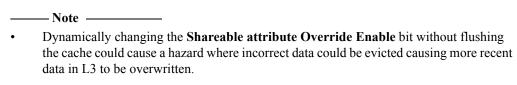

#### - Note -

- Table 1-3 does not take address filtering into account. If address filtering is implemented and enabled:

- master port 1 deals with all transactions from S0, S1, STB, and EB targeting the defined address range

- master port 0 deals with all other transactions.

- In a one master port system, master port 1 is not implemented. All master port 0 transactions apply to both **S0** and **S1**.

#### 1.3 Product revisions

This section summarizes the differences in functionality between the releases of the cache controller:

**r0p0-r1p0** The main differences between these versions are:

- new RAM latency scheme introduced and new configuration registers to support this scheme

- new RAM clocking scheme introduced enabling RAMs to be run at a lower frequency to the cache controller

- AXI slave and master interface attributes changed

- device writes can go into store buffer

- additional ARUSERSx and AWUSERSx signals.

**r1p0-r2p0** The main differences between these versions are:

- new behavior linked to the Shared attribute

- new configuration for supporting full address hazard checking

- performance improvements linked to the Cortex-A9 processor

- new AXI ID dedicated to Device writes from store buffer.

**r2p0-r3p0** The main differences between these versions are:

- new data RAM banking feature

- new speculative read optimization with Cortex-A9 MPCore processor

- new low-power modes

- new AXI ID encodings on master interfaces

- support for 64-byte linefills issued to L3.

## Chapter 2 **Functional Overview**

This chapter describes the cache controller and its features. It contains the following sections:

- *Cache configurability* on page 2-2

- AXI master and slave interfaces on page 2-3

- *Cache operation* on page 2-12

- *RAM interfaces* on page 2-23

- *Implementation details* on page 2-35

- *Power modes* on page 2-46.

#### 2.1 Cache configurability

Table 2-1 shows how you can configure the cache controller.

Table 2-1 Cache controller cache configurability

| Feature                     | Enabled by                                       | Range of options                            | Default<br>value | Default option                                           |

|-----------------------------|--------------------------------------------------|---------------------------------------------|------------------|----------------------------------------------------------|

| Cache way size              | Register or WAYSIZE[2:0] input                   | 16KB, 32KB,<br>64KB, 128KB,<br>256KB, 512KB | 001              | 16KB                                                     |

| Number of cache ways        | Register or ASSOCIATIVITY input                  | 8, 16a                                      | 0                | 8 ways                                                   |

| RAM latencies               | Register or verilog `define                      | 1, 2, 3, 4, 5, 6, 7, 8                      | 111              | 8 cycles of latency                                      |

| Data RAM banking            | Verilog `define pl310_DATA_BANKING               | Commented or uncommented                    | Commented        | No data RAM banking                                      |

| Slave port 1 present        | Verilog `define pl310_S1                         | Commented or uncommented                    | Commented        | No slave port 1                                          |

| Master port 1 present       | Verilog `define pl310_M1                         | Commented or uncommented                    | Commented        | No master port 1                                         |

| Parity logic                | Verilog `define pl310_PARITY                     | Commented or uncommented                    | Commented        | No parity logic                                          |

| Lockdown by master          | Verilog `define pl310_LOCKDOWN_BY_MASTER         | Commented or uncommented                    | Commented        | No lockdown by master                                    |

| Lockdown by line            | Verilog `define pl310_LOCKDOWN_BY_LINE           | Commented or uncommented                    | Commented        | No lockdown by line                                      |

| AXI ID width on slave ports | Verilog `define pl310_AXI_ID_MAX <value></value> | >=2                                         | 5                | 6 AXI ID bits on slave<br>ports and 8 on master<br>ports |

| Address filtering           | Verilog `define pl310_ADDRESS_FILTERING          | Commented or uncommented                    | Commented        | No address filtering logic                               |

| Speculative read            | Verilog `define pl310_SPECULATIVE_READ           | Commented or uncommented                    | Commented        | No logic for supporting speculative read                 |

a. 16-way associativity must be enabled using the p1310\_16\_WAYS verilog `define.

If you configure a single slave port, **AXI S0**, you must only configure a single master port, **AXI M0**. If you configure address filtering, you must configure master port **AXI M1**.

#### 2.2 AXI master and slave interfaces

This section describes:

- AXI master and slave interface attributes

- Clock enable usage model in the cache controller AXI interfaces on page 2-5

- *Master and slave port IDs* on page 2-7

- Exported AXI control on page 2-9

- AXI locked and exclusive accesses on page 2-10.

The cache controller reaches optimal performance when it receives AXI transactions that target full cache lines. That is, when all of the following conditions are met:

- AxLENS0/1 = 0x3

- AxSIZES0/1 = 0x3

- one of the following conditions is true:

- AxBURSTS0/1 = 0x1 and AxADDRS0/1[4:3] = 0x0

- AxBURSTS0/1 = 0x2.

You can obtain optimal performance by using different AXI IDs for outstanding read transactions sent to the L2C-310 slave interfaces.

#### 2.2.1 AXI master and slave interface attributes

Table 2-2 shows the AXI master interface attributes. The attribute values in Table 2-2 are maximum values. They might not be reached in all systems.

Table 2-2 AXI master interface attributes

| Configuration    | Attribute                   | Value                                                                                                                                          |  |

|------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Two master ports | Write issuing capability    | <ul><li>12, consisting of:</li><li>6 evictions</li><li>6 writes from store buffer.</li></ul>                                                   |  |

|                  | Read issuing capability     | <ul> <li>11, consisting of:</li> <li>8, 4 per master port, prefetches or reads from slave ports</li> <li>3 reads from store buffer.</li> </ul> |  |

|                  | Combined issuing capability | 23                                                                                                                                             |  |

|                  | Write interleave capability | 2, 1 per master port                                                                                                                           |  |

|                  | Write ID width              | Defined by Write ID width on slave ports.                                                                                                      |  |

|                  | Read ID width               | Defined by Read ID width on slave ports.                                                                                                       |  |

Table 2-2 AXI master interface attributes (continued)

| Configuration   | Attribute                   | Value                                                                                                                                 |

|-----------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| One master port | Write issuing capability    | <ul><li>12, consisting of:</li><li>6 evictions</li><li>6 writes from store buffer.</li></ul>                                          |

|                 | Read issuing capability     | <ul> <li>7, consisting of:</li> <li>4 prefetches or reads from one or more slave ports</li> <li>3 reads from store buffer.</li> </ul> |

|                 | Combined issuing capability | 19                                                                                                                                    |

|                 | Write interleave capability | 1                                                                                                                                     |

|                 | Write ID width              | Defined by Write ID width on slave ports.                                                                                             |

|                 | Read ID width               | Defined by Read ID width on slave ports.                                                                                              |

Table 2-3 shows the AXI slave interface attributes. The attribute values in Table 2-3 are maximum values. They might not be reached in all systems.

Table 2-3 AXI slave interface attributes

| Configuration                               | Attribute                      | Value                                                                                                                                          |

|---------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Two slave ports                             | Write acceptance capability    | 6, 3 per slave port                                                                                                                            |

| and two master ports <sup>a</sup>           | Read acceptance capability     | <ul> <li>16, 8 per slave port</li> <li>24, 12 per slave port, for sequential accesses, when you enable the double linefill feature.</li> </ul> |

|                                             | Combined acceptance capability | <ul> <li>22</li> <li>enable the double linefill feature to increase this value.</li> </ul>                                                     |

|                                             | Write interleave depth         | 2, 1 per slave port                                                                                                                            |

|                                             | Read data reorder depth        | 16                                                                                                                                             |

|                                             | Write ID width                 | Parameterizable, defined by pl310_AXI_ID_MAX, default is 6                                                                                     |

|                                             | Read ID width                  | Parameterizable, defined by pl310_AXI_ID_MAX, default is 6                                                                                     |

| Two slave ports Write acceptance capability |                                | 6, 3 per slave port                                                                                                                            |

| and one master port                         | Read acceptance capability     | <ul> <li>12, 6 per slave port</li> <li>16, 8 per slave port, for sequential accesses, when you enable the double linefill feature.</li> </ul>  |

|                                             | Combined acceptance capability | <ul> <li>18</li> <li>enable the double linefill feature to increase this value.</li> </ul>                                                     |

|                                             | Write interleave depth         | 2, 1 per slave port                                                                                                                            |

|                                             | Read data reorder depth        | 12                                                                                                                                             |

|                                             | Write ID width                 | Parameterizable, defined by pl310_AXI_ID_MAX, default is 6                                                                                     |

|                                             | Read ID width                  | Parameterizable, defined by pl310_AXI_ID_MAX, default is 6                                                                                     |

Table 2-3 AXI slave interface attributes (continued)

| Configuration                      | Attribute                      | Value                                                                                                                   |

|------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| One slave port and one master port | Write acceptance capability    | 3                                                                                                                       |

|                                    | Read acceptance capability     | <ul> <li>8</li> <li>enable the double linefill feature to increase this value to 12 for sequential accesses.</li> </ul> |

|                                    | Combined acceptance capability | <ul> <li>11</li> <li>enable the double linefill feature to increase this value.</li> </ul>                              |

|                                    | Write interleave depth         | 1                                                                                                                       |

|                                    | Read data reorder depth        | 8                                                                                                                       |

|                                    | Write ID width                 | Parameterizable, defined by p1310_AXI_ID_MAX, default is 6                                                              |

|                                    | Read ID width                  | Parameterizable, defined by p1310_AXI_ID_MAX, default is 6                                                              |

a. These values ignore address filtering. If you implement address filtering, the values might be reduced to values close to those in the *Two slave ports and one master port* section of the table.

#### 2.2.2 Clock enable usage model in the cache controller AXI interfaces

The cache controller receives one clock, **CLK**. The AXI slave and master ports receive clock enable pins that enable you to define different clock ratios from **CLK**. The ratios can be integer or half-integer, 1.5:1, 2.5:1, and 3.5:1. Each master and slave receives one clock enable for its AXI inputs and one for its AXI outputs.

For integer clock ratios, the clock enable **CLKEN** of the system must be used to drive both cache controller inputs, **INCLKEN** and **OUTCLKEN**, as Figure 2-1 shows.

Figure 2-1 CLKEN used to drive cache controller inputs in case of integer clock ratio

Figure 2-2 on page 2-6 shows how the different clock enable signals can be generated to support half integer clock ratios. In the figure, **ACLK** is the clock of the L3 AXI system.

Figure 2-2 Clock enable usage model for 1.5:1 clock ratio in master port

Figure 2-3 shows how the different clock enable signals can be generated to support half integer clock ratios. In Figure 2-3, **ACLK** is the clock of the L3 AXI system.

Figure 2-3 Clock enable usage model for 2.5:1 clock ratio in master port

Figure 2-4 Clock enable usage model for 3.5:1 clock ratio in master port

See Table A-1 on page A-2 for a description of the clock enables. These clock enables enable the cache controller to communicate with AXI components that run at slower frequencies.

In each of these AXI interfaces, the clock enable is used as follows:

- Inputs are sampled on rising edges of **CLK** only when **INCLKEN** is HIGH.

- Outputs are updated on rising edges of **CLK** only when **OUTCLKEN** is HIGH.

#### 2.2.3 Master and slave port IDs

The AXI ID width on the slave and master ports depends on the value of parameter pl310\_AXI\_ID\_MAX that has a default value of 5. The AXI ID width is [`pl310\_AXI\_ID\_MAX:0] on the slave ports and [`pl310\_AXI\_ID\_MAX+2:0] on the master ports. This section assumes that the default value for pl310\_AXI\_ID\_MAX is 5.

The number of bits for master and slave port IDs are as follows:

- Slave S0: 6 bits [5:0], signals AWIDS0, ARIDS0, WIDS0, BIDS0, and RIDS0

- Slave S1: 6 bits [5:0], signals AWIDS1, ARIDS1, WIDS1, BIDS1, and RIDS1

- Master M0: 8 bits [7:0], signals AWIDM0, ARIDM0, WIDM0, BIDM0, and RIDM0

- Master M1: 8 bits [7:0], signals AWIDM1, ARIDM1, WIDM1, BIDM1, and RIDM1.

Table 2-4 shows the format of the identifications that are exported on the master ports for writes.

Table 2-4 Master port ID values for writes

| Master ID buses      | Access types                      | ID value, Verilog                                |

|----------------------|-----------------------------------|--------------------------------------------------|

| AWIDMx, WIDMx, BIDMx | Non-bufferable write from slave 0 | {AWIDS0, 00}                                     |

|                      | Non-bufferable write from slave 1 | {AWIDS1, 10}                                     |

|                      | Eviction from slot 0              | {{`pl310_AXI_ID_MAX-1{0}}, 0011}                 |

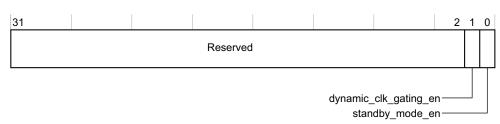

|                      | Eviction from slot 1              | {{`p1310_AXI_ID_MAX-1{0}}, 0111}                 |