Revision: r3p2

**Technical Reference Manual**

Copyright © 2006-2010 ARM Limited. All rights reserved. ARM DDI 0344K (ID060510)

# Cortex-A8 Technical Reference Manual

Copyright © 2006-2010 ARM Limited. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

|                  |       |                                      | onange mistory          |

|------------------|-------|--------------------------------------|-------------------------|

| Date             | Issue | Confidentiality                      | Change                  |

| 18 July 2006     | А     | Confidential                         | First release for r1p0  |

| 13 December 2006 | В     | Non-Confidential                     | First release for r1p1  |

| 13 July 2007     | С     | Non-Confidential                     | First release for r2p0  |

| 16 November 2007 | D     | Non-Confidential                     | First release for r2p1  |

| 14 March 2008    | Е     | Non-Confidential                     | First release for r2p2  |

| 06 October 2008  | F     | Non-Confidential                     | First release for r2p3  |

| 24 October 2008  | G     | Non-Confidential Restricted Access   | First release for r3p0  |

| 03 December 2008 | Н     | Non-Confidential Unrestricted Access | Second release for r3p0 |

| 30 January 2009  | Ι     | Non-Confidential Unrestricted Access | First release for r3p1  |

| 15 May 2009      | J     | Non-Confidential Unrestricted Access | First release for r3p2  |

| 07 May 2010      | K     | Non-Confidential Unrestricted Access | Second release for r3p2 |

#### **Proprietary Notice**

Words and logos marked with <sup>®</sup> or <sup>™</sup> are registered trademarks or trademarks owned by ARM Limited, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Some material in this document is based on ANSI/IEEE Std 754-1985, IEEE Standard for Binary Floating-Point Arithmetic and on IEEE Std. 1500-2005, IEEE Standard Testability Method for Embedded Core-based Integrated Circuits. The IEEE disclaims any responsibility or liability resulting from the placement and use in the described manner.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

Change history

#### Web Address

http://www.arm.com

# Contents Cortex-A8 Technical Reference Manual

| Preface  |

|----------|

| 1 101400 |

| About this manual                      | xxi      |  |

|----------------------------------------|----------|--|

| Feedback                               | xxv      |  |

| roduction                              |          |  |

| About the processor                    | 1-2      |  |

| ARMv7-A architecture                   | 1-3      |  |

| Components of the processor            | 1-4      |  |

| External interfaces of the processor   | 1-7      |  |

| Debug                                  | 1-8      |  |

| Power management                       | 1-9      |  |

| Configurable options                   | 1-10     |  |

| Product documentation and architecture | 1-11     |  |

| Product revisions                      | 1-13     |  |

| Programmers Model                      |          |  |

| •                                      |          |  |

| Thumb-2 instruction set                |          |  |

| ThumbEE instruction set                |          |  |

| Jazelle Extension                      | 2-7      |  |

| Security Extensions architecture       |          |  |

|                                        |          |  |

| VFPv3 architecture                     |          |  |

| Processor operating states             | 2-13     |  |

|                                        |          |  |

|                                        |          |  |

| Data types                             |          |  |

| Data types                             | 2-15     |  |

| Data types                             |          |  |

|                                        | Feedback |  |

#### Contents

|           | 2.14       | The program status registers                                         |            |

|-----------|------------|----------------------------------------------------------------------|------------|

|           | 2.15       | Exceptions                                                           |            |

|           | 2.16       | Software consideration for Security Extensions                       |            |

|           | 2.17       | Hardware consideration for Security Extensions                       |            |

|           | 2.18       | Control coprocessor                                                  | 2-38       |

| Chapter 3 | Syst       | em Control Coprocessor                                               |            |

|           | 3.1        | About the system control coprocessor                                 | 3-2        |

|           | 3.2        | System control coprocessor registers                                 | 3-7        |

| Chapter 4 | Unal       | igned Data and Mixed-endian Data Support                             |            |

| •         | 4.1        | About unaligned and mixed-endian data                                | 4-2        |

|           | 4.2        | Unaligned data access support                                        | 4-3        |

|           | 4.3        | Mixed-endian access support                                          | 4-5        |

| Chapter 5 | Proq       | ram Flow Prediction                                                  |            |

| •         | 5.1        | About program flow prediction                                        | 5-2        |

|           | 5.2        | Predicted instructions                                               |            |

|           | 5.3        | Nonpredicted instructions                                            |            |

|           | 5.4        | Guidelines for optimal performance                                   |            |

|           | 5.5        | Enabling program flow prediction                                     |            |

|           | 5.6        | Operating system and predictor context                               |            |

| Chapter 6 | Mom        | ory Management Unit                                                  |            |

| Chapter 0 |            |                                                                      | <b>C</b> O |

|           | 6.1        | About the MMU                                                        |            |

|           | 6.2        | Memory access sequence                                               |            |

|           | 6.3        | 16MB supersection support                                            |            |

|           | 6.4        | MMU interaction with memory system                                   |            |

|           | 6.5        | External aborts                                                      |            |

|           | 6.6<br>6.7 | TLB lockdown<br>MMU software-accessible registers                    |            |

|           |            |                                                                      |            |

| Chapter 7 |            | l 1 Memory System                                                    |            |

|           | 7.1        | About the L1 memory system                                           | 7-2        |

|           | 7.2        | Cache organization                                                   | 7-3        |

|           | 7.3        | Memory attributes                                                    |            |

|           | 7.4        | Cache debug                                                          | 7-7        |

|           | 7.5        | Data cache features                                                  |            |

|           | 7.6        | Instruction cache features                                           |            |

|           | 7.7        | Hardware support for virtual aliasing conditions                     | 7-10       |

|           | 7.8        | Parity detection                                                     | 7-11       |

| Chapter 8 | Leve       | l 2 Memory System                                                    |            |

|           | 8.1        | About the L2 memory system                                           | 8-2        |

|           | 8.2        | Cache organization                                                   |            |

|           | 8.3        | Enabling and disabling the L2 cache controller                       |            |

|           | 8.4        | L2 PLE                                                               |            |

|           | 8.5        | Synchronization primitives                                           |            |

|           | 8.6        | Locked access                                                        |            |

|           | 8.7        | Parity and error correction code                                     |            |

| Chapter 9 | Fyte       | rnal Memory Interface                                                |            |

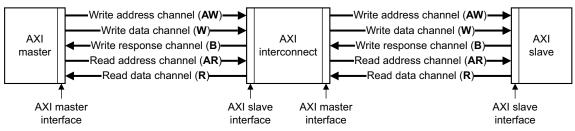

| Shupters  | 9.1        | About the external memory interface                                  | 0.2        |

|           | 9.1<br>9.2 | •                                                                    |            |

|           | 9.2<br>9.3 | AXI control signals in the processor<br>AXI instruction transactions |            |

|           | 9.3<br>9.4 | AXI instruction transactions                                         |            |

|           | 9.4        |                                                                      |            |

| Chapter 10 | Clock          | x, Reset, and Power Control                                                                 |       |

|------------|----------------|---------------------------------------------------------------------------------------------|-------|

| •          | 10.1           | Clock domains                                                                               | 10-2  |

|            | 10.2           | Reset domains                                                                               |       |

|            | 10.3           | Power control                                                                               | 10-8  |

| Chapter 11 | Desig          | In for Test                                                                                 |       |

|            | 11.1           | MBIST                                                                                       | 11-2  |

|            | 11.2           | ATPG test features                                                                          |       |

| Oberten 40 | Debu           | _                                                                                           |       |

| Chapter 12 | Debu           |                                                                                             |       |

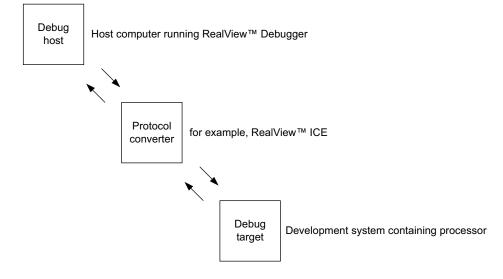

|            | 12.1           | Debug systems                                                                               |       |

|            | 12.2           | About the debug unit                                                                        |       |

|            | 12.3           | Debug register interface                                                                    |       |

|            | 12.4           | Debug register descriptions                                                                 |       |

|            | 12.5           | Management registers                                                                        |       |

|            | 12.6           | Debug events                                                                                |       |

|            | 12.7           | Debug exception                                                                             |       |

|            | 12.8           | Debug state                                                                                 |       |

|            | 12.9           | Cache debug                                                                                 |       |

|            | 12.10          | External debug interface                                                                    |       |

|            | 12.11          | Using the debug functionality                                                               |       |

|            | 12.12          | Debugging systems with energy management capabilities                                       | 12-86 |

| Chapter 13 | NEON           | and VFP Programmers Model                                                                   |       |

|            | 13.1           | About the NEON and VFP programmers model                                                    | 13-2  |

|            | 13.2           | General-purpose registers                                                                   | 13-3  |

|            | 13.3           | Short vectors                                                                               | 13-5  |

|            | 13.4           | System registers                                                                            | 13-10 |

|            | 13.5           | Modes of operation                                                                          | 13-16 |

|            | 13.6           | Compliance with the IEEE 754 standard                                                       | 13-17 |

| Chapter 14 | Embe           | dded Trace Macrocell                                                                        |       |

|            | 14.1           | About the ETM                                                                               | 14-2  |

|            | 14.2           | ETM configuration                                                                           |       |

|            | 14.3           | ETM register summary                                                                        |       |

|            | 14.4           | ETM register descriptions                                                                   |       |

|            | 14.5           | Precision of TraceEnable and ViewData                                                       |       |

|            | 14.6           | Exact match bit                                                                             |       |

|            | 14.7           | Context ID tracing                                                                          |       |

|            | 14.8           | Instrumentation instructions                                                                |       |

|            | 14.9           | Idle state control                                                                          |       |

|            | 14.10          | Interaction with the Performance Monitoring Unit                                            |       |

| Chapter 15 | Croos          | Trigger Interface                                                                           |       |

| Chapter 15 |                | s Trigger Interface                                                                         | 45.0  |

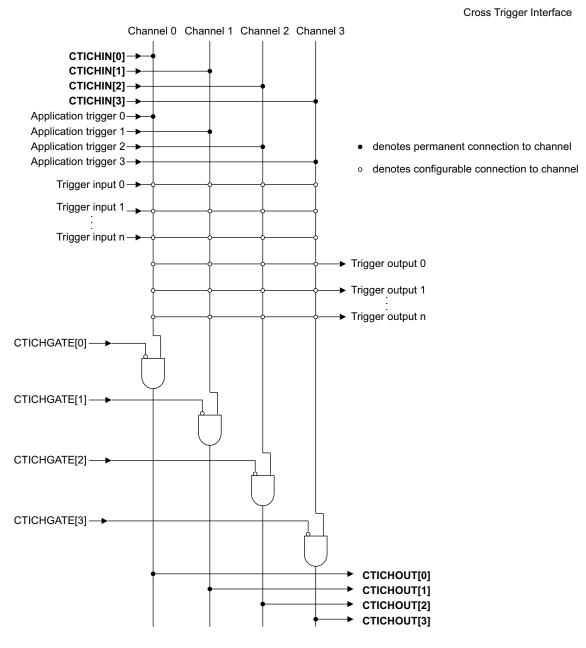

|            | 15.1           | About the CTI                                                                               |       |

|            | 15.2           | Trigger inputs and outputs                                                                  |       |

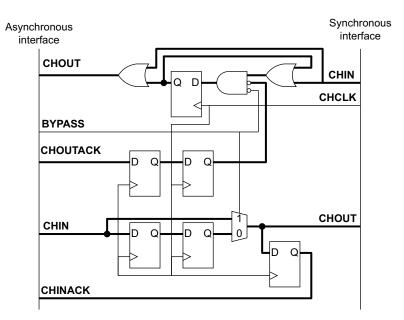

|            | 15.3           | Connecting asynchronous channel interfaces                                                  |       |

|            | 15.4           | About the CTI programmers model                                                             |       |

|            | 15.5<br>15.6   | CTI register summary                                                                        |       |

|            | 15.6           | CTI register descriptions                                                                   |       |

|            | 15.7           | CTI Integration Test Registers<br>CTI CoreSight defined registers                           |       |

| Ob         | <b>1</b> 4     |                                                                                             |       |

| Chapter 16 | Instru<br>16.1 | About instruction cycle timing                                                              | 16.0  |

|            | 16.1           | About instruction cycle timing                                                              |       |

|            | 16.2<br>16.3   | Instruction-specific scheduling for ARM instructions<br>Dual-instruction issue restrictions |       |

|            | 16.3<br>16.4   |                                                                                             |       |

|            | 16.4<br>16.5   | Other pipeline-dependent latencies                                                          |       |

|            | 10.5           | Advanced SIMD instruction scheduling                                                        | 10-17 |

|            | 16.6   | Instruction-specific scheduling for Advanced SIMD instructions |        |

|------------|--------|----------------------------------------------------------------|--------|

|            | 16.7   | VFP instructions                                               |        |

|            | 16.8   | Scheduling example                                             | 16-37  |

| Chapter 17 | AC Ch  | aracteristics                                                  |        |

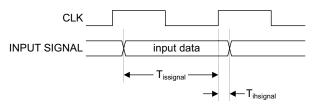

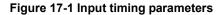

|            | 17.1   | About setup and hold times                                     | . 17-2 |

|            | 17.2   | AXI interface                                                  | . 17-4 |

|            | 17.3   | ATB and CTI interfaces                                         |        |

|            | 17.4   | APB interface and miscellaneous debug signals                  | . 17-7 |

|            | 17.5   | L1 and L2 MBIST interfaces                                     | . 17-9 |

|            | 17.6   | L2 preload interface                                           | 17-10  |

|            | 17.7   | DFT interface                                                  | 17-11  |

|            | 17.8   | Miscellaneous signals                                          | 17-12  |

| Appendix A | Signal | Descriptions                                                   |        |

|            | A.1    | AXI interface                                                  | A-2    |

|            | A.2    | ATB interface                                                  | A-3    |

|            | A.3    | MBIST and DFT interface                                        | A-4    |

|            | A.4    | Preload engine interface                                       | A-6    |

|            | A.5    | APB interface                                                  | A-7    |

|            | A.6    | Miscellaneous signals                                          | A-8    |

|            | A.7    | Miscellaneous debug signals                                    | . A-11 |

|            | A.8    | Miscellaneous ETM and CTI signals                              | . A-13 |

| Appendix B | Instru | ction Mnemonics                                                |        |

| • •        | B.1    | Advanced SIMD data-processing instructions                     | B-2    |

|            | B.2    | VFP data-processing instructions                               |        |

| Appendix C | Revisi | ons                                                            |        |

|            | Glossa | ary                                                            |        |

# List of Tables Cortex-A8 Technical Reference Manual

|            | Change history                                        | ii   |

|------------|-------------------------------------------------------|------|

| Table 1-1  | Cortex-A8 configurable options                        | 1-10 |

| Table 2-1  | ThumbEE Configuration Register bit functions          | 2-5  |

| Table 2-2  | ThumbEE HandlerBase Register bit functions            | 2-6  |

| Table 2-3  | Access to ThumbEE registers                           | 2-6  |

| Table 2-4  | Jazelle Identity Register bit functions               | 2-7  |

| Table 2-5  | Jazelle Main Configuration Register bit functions     | 2-8  |

| Table 2-6  | Jazelle OS Control Register bit functions             | 2-8  |

| Table 2-7  | Address types in the processor system                 | 2-16 |

| Table 2-8  | Mode structure                                        |      |

| Table 2-9  | Register mode identifiers                             | 2-18 |

| Table 2-10 | GE[3:0] settings                                      | 2-23 |

| Table 2-11 | PSR mode bit values                                   | 2-25 |

| Table 2-12 | Exception entry and exit                              |      |

| Table 2-13 | Exception priorities                                  | 2-33 |

| Table 3-1  | System control coprocessor register functions         |      |

| Table 3-2  | CP15 registers affected by CP15SDISABLE               | 3-5  |

| Table 3-3  | Summary of CP15 registers and operations              | 3-7  |

| Table 3-4  | Main ID Register bit functions                        |      |

| Table 3-5  | Results of access to the Main ID Register             |      |

| Table 3-6  | Cache Type Register bit functions                     | 3-20 |

| Table 3-7  | Results of access to the Cache Type Register          |      |

| Table 3-8  | Results of access to the TCM Type Register            | 3-21 |

| Table 3-9  | TLB Type Register bit functions                       |      |

| Table 3-10 | Results of access to the TLB Type Register            |      |

| Table 3-11 | Results of access to the Multiprocessor ID Register   |      |

| Table 3-12 | Processor Feature Register 0 bit functions            |      |

| Table 3-13 | Results of access to the Processor Feature Register 0 |      |

| Table 3-14 | Processor Feature Register 1 bit functions            |      |

| Table 3-15 | Results of access to Processor Feature Register 1     | 3-24 |

| Table 3-16               | Debug Feature Register 0 bit functions                                                                                      | 3-25 |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|

| Table 3-17               | Results of access to Debug Feature Register 0                                                                               |      |

| Table 3-18               | Results of access to Auxiliary Feature Register 0                                                                           |      |

| Table 3-19               | Memory Model Feature Register 0 bit functions                                                                               | 3-27 |

| Table 3-20               | Results of access to Memory Model Feature Register 0                                                                        | 3-27 |

| Table 3-21               | Memory Model Feature Register 1 bit functions                                                                               | 3-28 |

| Table 3-22               | Results of access to Memory Model Feature Register 1                                                                        |      |

| Table 3-23               | Memory Model Feature Register 2 bit functions                                                                               |      |

| Table 3-24               | Results of access to Memory Model Feature Register 2                                                                        |      |

| Table 3-25               | Memory Model Feature Register 3 bit functions                                                                               |      |

| Table 3-26               | Results of access to Memory Model Feature Register 3                                                                        |      |

| Table 3-27               | Instruction Set Attributes Register 0 bit functions                                                                         |      |

| Table 3-28               | Results of access to Instruction Set Attributes Register 0                                                                  |      |

| Table 3-29               | Instruction Set Attributes Register 1 bit functions                                                                         |      |

| Table 3-30               | Results of access to Instruction Set Attributes Register 1                                                                  |      |

| Table 3-31               | Instruction Set Attributes Register 2 bit functions                                                                         |      |

| Table 3-32               | Results of access to Instruction Set Attributes Register 2                                                                  |      |

| Table 3-33               | Instruction Set Attributes Register 3 bit functions                                                                         |      |

| Table 3-34               | Results of access to Instruction Set Attributes Register 3                                                                  |      |

| Table 3-35<br>Table 3-36 | Instruction Set Attributes Register 4 bit functions                                                                         |      |

| Table 3-36               | Results of access to Instruction Set Attributes Register 4<br>Cache Level ID Register bit functions                         |      |

| Table 3-37               | Results of access to the Cache Level ID Register                                                                            |      |

| Table 3-39               | Silicon ID Register bit functions                                                                                           |      |

| Table 3-40               | Results of access to the Silicon ID Register                                                                                |      |

| Table 3-41               | Cache Size Identification Register bit functions                                                                            |      |

| Table 3-42               | Encodings of the Cache Size Identification Register                                                                         |      |

| Table 3-43               | Results of access to the Cache Size Identification Register                                                                 |      |

| Table 3-44               | Cache Size Selection Register bit functions                                                                                 |      |

| Table 3-45               | Results of access to the Cache Size Selection Register                                                                      |      |

| Table 3-46               | Control Register bit functions                                                                                              |      |

| Table 3-47               | Results of access to the Control Register                                                                                   |      |

| Table 3-48               | Behavior of the processor when enabling caches                                                                              |      |

| Table 3-49               | Auxiliary Control Register bit functions                                                                                    |      |

| Table 3-50               | Results of access to the Auxiliary Control Register                                                                         |      |

| Table 3-51               | Coprocessor Access Control Register bit functions                                                                           |      |

| Table 3-52               | Results of access to the Coprocessor Access Control Register                                                                | 3-52 |

| Table 3-53               | Secure Configuration Register bit functions                                                                                 | 3-54 |

| Table 3-54               | Operation of the FW and FIQ bits                                                                                            | 3-54 |

| Table 3-55               | Operation of the AW and EA bits                                                                                             | 3-55 |

| Table 3-56               | Secure Debug Enable Register bit functions                                                                                  |      |

| Table 3-57               | Results of access to the Secure Debug Enable Register                                                                       |      |

| Table 3-58               | Nonsecure Access Control Register bit functions                                                                             |      |

| Table 3-59               | Results of access to the Auxiliary Control Register                                                                         |      |

| Table 3-60               | Translation Table Base Register 0 bit functions                                                                             |      |

| Table 3-61               | Results of access to the Translation Table Base Register 0                                                                  |      |

| Table 3-62               | Translation Table Base Register 1 bit functions                                                                             |      |

| Table 3-63               | Results of access to the Translation Table Base Register 1                                                                  |      |

| Table 3-64               | Translation Table Base Control Register bit functions                                                                       |      |

| Table 3-65               | Results of access to the Translation Table Base Control Register                                                            |      |

| Table 3-66               | Domain Access Control Register bit functions                                                                                |      |

| Table 3-67               | Results of access to the Domain Access Control Register                                                                     |      |

| Table 3-68               | Data Fault Status Register bit functions                                                                                    |      |

| Table 3-69               | Instruction Fault Status Register bit functions                                                                             |      |

| Table 3-70               | Results of access to the Auxiliary Fault Status Registers                                                                   |      |

| Table 3-71               | Results of access to the Data Fault Address Register                                                                        |      |

| Table 3-72<br>Table 3-73 | Results of access to the Instruction Fault Address Register<br>Register c7 cache and prefetch buffer maintenance operations |      |

| Table 3-73               | Functional bits of c7 for set and way                                                                                       |      |

| Table 3-74<br>Table 3-75 | Values of A, L, and S for L1 cache sizes                                                                                    |      |

|                          |                                                                                                                             |      |

| Table 3-76  | Values of A, L, and S for L2 cache sizes                             | 3-70  |

|-------------|----------------------------------------------------------------------|-------|

| Table 3-77  | Functional bits of c7 for MVA                                        |       |

| Table 3-78  | PA Register for successful translation bit functions                 |       |

| Table 3-79  | PA Register for unsuccessful translation bit functions               | 3-73  |

| Table 3-80  | Results of access to the data synchronization barrier operation      | 3-75  |

| Table 3-81  | Results of access to the data memory barrier operation               |       |

| Table 3-82  | Performance Monitor Control Register bit functions                   | 3-77  |

| Table 3-83  | Results of access to the Performance Monitor Control Register        | 3-78  |

| Table 3-84  | Count Enable Set Register bit functions                              | 3-78  |

| Table 3-85  | Results of access to the Count Enable Set Register                   | 3-79  |

| Table 3-86  | Count Enable Clear Register bit functions                            |       |

| Table 3-87  | Results of access to the Count Enable Clear Register                 | 3-80  |

| Table 3-88  | Overflow Flag Status Register bit functions                          | 3-81  |

| Table 3-89  | Results of access to the Overflow Flag Status Register               |       |

| Table 3-90  | Software Increment Register bit functions                            | 3-82  |

| Table 3-91  | Results of access to the Software Increment Register                 | 3-82  |

| Table 3-92  | Performance Counter Selection Register bit functions                 | 3-83  |

| Table 3-93  | Results of access to the Performance Counter Selection Register      | 3-83  |

| Table 3-94  | Results of access to the Cycle Count Register                        |       |

| Table 3-95  | Event Selection Register bit functions                               | 3-84  |

| Table 3-96  | Results of access to the Event Selection Register                    |       |

| Table 3-97  | Values for predefined events                                         | 3-85  |

| Table 3-98  | Results of access to the Performance Monitor Count Registers         | 3-88  |

| Table 3-99  | Signal settings for the Performance Monitor Count Registers          | 3-89  |

| Table 3-100 | User Enable Register bit functions                                   | 3-89  |

| Table 3-101 | Results of access to the User Enable Register                        | 3-90  |

| Table 3-102 | Interrupt Enable Set Register bit functions                          | 3-91  |

| Table 3-103 | Results of access to the Interrupt Enable Set Register               | 3-91  |

| Table 3-104 | Interrupt Enable Clear Register bit functions                        | 3-92  |

| Table 3-105 | Results of access to the Interrupt Enable Clear Register             | 3-92  |

| Table 3-106 | L2 Cache Lockdown Register bit functions                             | 3-93  |

| Table 3-107 | Results of access to the L2 Cache Lockdown Register                  | 3-94  |

| Table 3-108 | L2 Cache Auxiliary Control Register bit functions                    | 3-95  |

| Table 3-109 | Results of access to the L2 Cache Auxiliary Control Register         | 3-97  |

| Table 3-110 | TLB Lockdown Register bit functions                                  | 3-98  |

| Table 3-111 | Results of access to the TLB Lockdown Register                       | 3-99  |

| Table 3-112 | Application of remapped registers on memory access                   | 3-101 |

| Table 3-113 | Primary Region Remap Register bit functions                          | 3-101 |

| Table 3-114 | Encoding for the remapping of the primary memory type                | 3-102 |

| Table 3-115 | Normal Memory Remap Register bit functions                           | 3-102 |

| Table 3-116 | Remap encoding for inner or outer cacheable attributes               | 3-103 |

| Table 3-117 | Results of access to the memory region remap registers               | 3-104 |

| Table 3-118 | PLE Identification and Status Register bit functions                 | 3-105 |

| Table 3-119 | Opcode_2 values for PLE Identification and Status Register functions | 3-105 |

| Table 3-120 | Results of access to the PLE Identification and Status Registers     | 3-106 |

| Table 3-121 | PLE User Accessibility Register bit functions                        | 3-107 |

| Table 3-122 | Results of access to the PLE User Accessibility Register             | 3-107 |

| Table 3-123 | PLE Channel Number Register bit functions                            | 3-108 |

| Table 3-124 | Results of access to the PLE User Accessibility Register             | 3-108 |

| Table 3-125 | Results of access to the PLE enable commands                         | 3-109 |

| Table 3-126 | PLE Control Register bit functions                                   | 3-110 |

| Table 3-127 | Writing to UM bit [26]                                               |       |

| Table 3-128 | Results of access to the PLE Control Registers                       |       |

| Table 3-129 | Results of access to the PLE Internal Start Address Register         |       |

| Table 3-130 | Maximum transfer size for various L2 cache sizes                     | 3-113 |

| Table 3-131 | Results of access to the PLE Internal End Address Register           | 3-114 |

| Table 3-132 | PLE Channel Status Register bit functions                            | 3-115 |

| Table 3-133 | Results of access to the PLE Channel Status Register                 | 3-115 |

| Table 3-134 | PLE Context ID Register bit functions                                |       |

| Table 3-135 | Results of access to the PLE Context ID Register                     | 3-116 |

| T-61- 0 400                | On sum on Names and Names Dans Address Danister bit for stiens                                                                   | 0.447 |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------|

| Table 3-136                | Secure or Nonsecure Vector Base Address Register bit functions                                                                   |       |

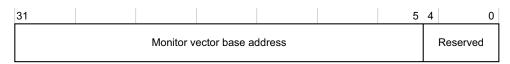

| Table 3-137<br>Table 3-138 | Results of access to the Secure or Nonsecure Vector Base Address Register<br>Monitor Vector Base Address Register bit functions  |       |

| Table 3-138                | Results of access to the Monitor Vector Base Address Register                                                                    |       |

| Table 3-140                | Interrupt Status Register bit functions                                                                                          |       |

| Table 3-141                | Results of access to the Interrupt Status Register                                                                               |       |

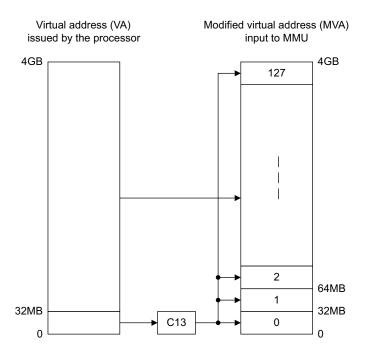

| Table 3-142                | FCSE PID Register bit functions                                                                                                  |       |

| Table 3-143                | Results of access to the FCSE PID Register                                                                                       |       |

| Table 3-144                | Context ID Register bit functions                                                                                                |       |

| Table 3-145                | Results of access to the Context ID Register                                                                                     |       |

| Table 3-146                | Results of access to the Thread and Process ID Registers                                                                         |       |

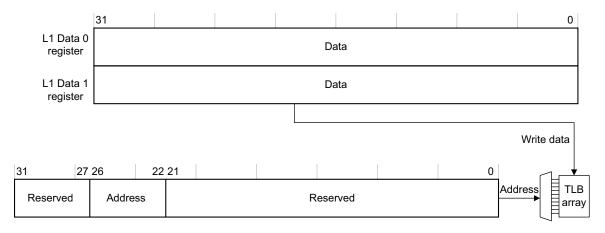

| Table 3-147                | Functional bits of I-L1 or D-L1 Data 0 Register for a TLB CAM operation                                                          |       |

| Table 3-148                | Functional bits of I-L1 or D-L1 Data 1 Register for a TLB CAM operation                                                          |       |

| Table 3-149                | Functional bits of I-L1 or D-L1 Data 0 Register for a TLB ATTR operation                                                         | 3-126 |

| Table 3-150                | Functional bits of I-L1 or D-L1 Data 0 Register for a TLB PA array operation                                                     | 3-126 |

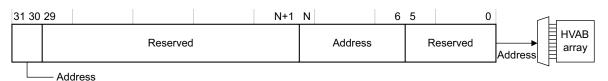

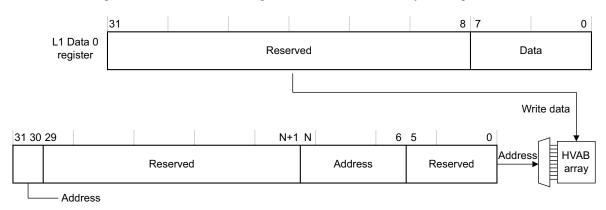

| Table 3-151                | Functional bits of I-L1 or D-L1 Data 0 Register for an HVAB array operation                                                      |       |

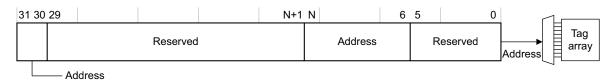

| Table 3-152                | Functional bits of I-L1 or D-L1 Data 0 Register for an L1 tag array operation                                                    |       |

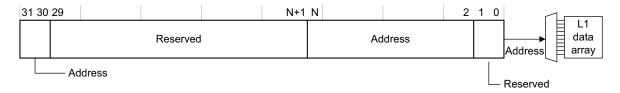

| Table 3-153                | Functional bits of I-L1 or D-L1 Data 0 Register for L1 data array operation                                                      |       |

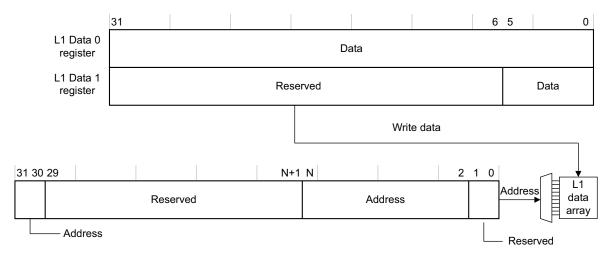

| Table 3-154                | Functional bits of I-L1 or D-L1 Data 1 Register for L1 data array operation                                                      |       |

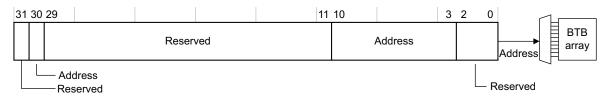

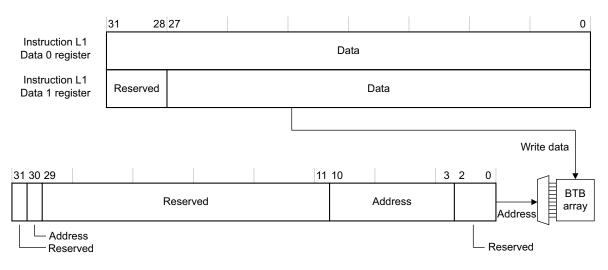

| Table 3-155                | Functional bits of I-L1 Data 0 Register for a BTB array operation                                                                |       |

| Table 3-156                | Functional bits of I-L1 Data 1 Register for a BTB array operation                                                                |       |

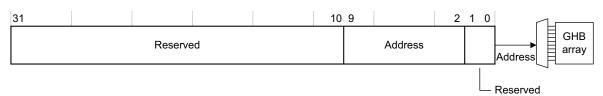

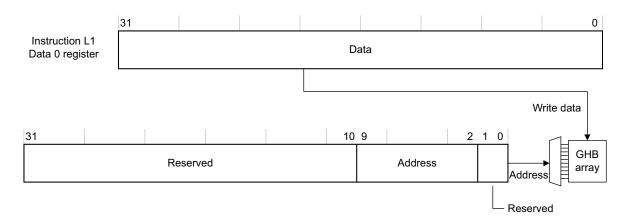

| Table 3-157                | Functional bits of I-L1 Data 0 Register for a GHB array operation                                                                |       |

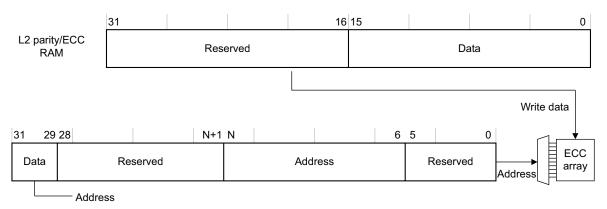

| Table 3-158                | Functional bits of L2 Data 0 Register for an L2 parity/ECC operation                                                             |       |

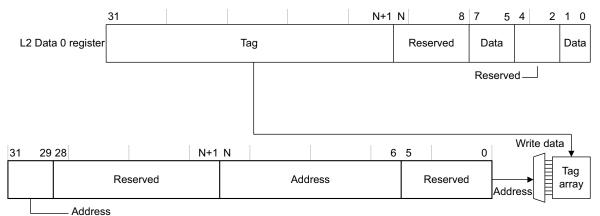

| Table 3-159                | Functional bits of L2 Data 0 Register for a tag RAM operation                                                                    |       |

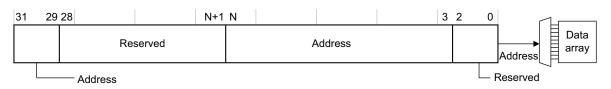

| Table 3-160<br>Table 3-161 | Functional bits of L2 Data 0 Register for a data RAM operation<br>Functional bits of L2 Data 1 Register for a data RAM operation |       |

| Table 3-161                | Functional bits of L2 Data 1 Register for a data RAM operation                                                                   |       |

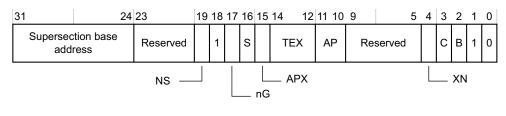

| Table 3-162                | Address field values                                                                                                             |       |

| Table 4-1                  | NEON normal memory alignment qualifiers                                                                                          |       |

| Table 6-1                  | CP15 register functions                                                                                                          |       |

| Table 7-1                  | Memory types affecting L1 and L2 cache flows                                                                                     |       |

| Table 8-1                  | L2 cache transfer policy                                                                                                         |       |

| Table 8-2                  | Cacheable and noncacheable memory region types                                                                                   |       |

| Table 9-1                  | Read address channel AXI ID                                                                                                      |       |

| Table 9-2                  | Write address channel AXI ID                                                                                                     | 9-3   |

| Table 9-3                  | AXI master interface attributes                                                                                                  | 9-4   |

| Table 9-4                  | A64n128 encoding                                                                                                                 |       |

| Table 9-5                  | AXI address channel for instruction transactions                                                                                 |       |

| Table 9-6                  | Number of transfers on AXI write channel for an eviction                                                                         |       |

| Table 9-7                  | AXI address channel for data transactions - excluding load/store multiples                                                       |       |

| Table 9-8                  | AXI address channel for data transactions for load/store multiples                                                               |       |

| Table 10-1                 | Reset inputs                                                                                                                     |       |

| Table 10-2                 | Valid power domains                                                                                                              |       |

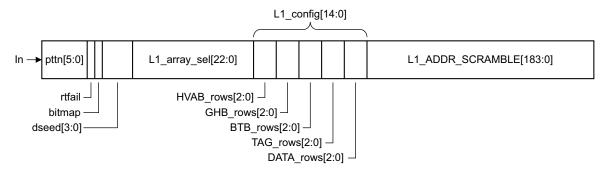

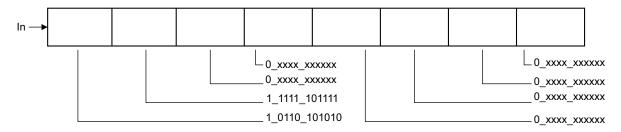

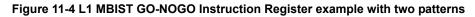

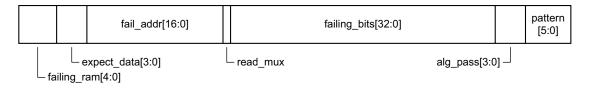

| Table 11-1<br>Table 11-2   | MBIST register summary<br>Selecting a test pattern with pttn[5:0]                                                                |       |

| Table 11-2<br>Table 11-3   | Selecting the L1 arrays to test with L1_array_sel[22:0]                                                                          |       |

| Table 11-3                 | L1_config[14:0]                                                                                                                  |       |

| Table 11-4                 | Configuring the number of L1 array rows with L1_config[14:0]                                                                     |       |

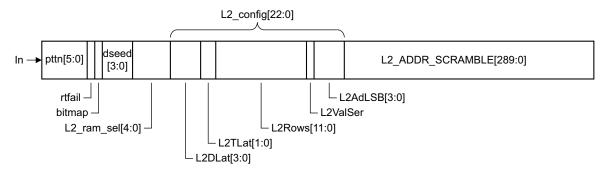

| Table 11-6                 | Selecting L2 RAMs for test with L2_ram_sel[4:0]                                                                                  |       |

| Table 11-7                 | L2_config[22:0]                                                                                                                  |       |

| Table 11-8                 | Selecting L2 data array latency with L2DLat[3:0]                                                                                 |       |

| Table 11-9                 | Selecting L2 tag array latency with L2TLat[1:0]                                                                                  |       |

| Table 11-10                | Selecting the L2 RAMs with L2Rows[11:0]                                                                                          |       |

| Table 11-11                | Configuring the number of L2 RAM rows with L2Rows[11:0]                                                                          |       |

| Table 11-12                | Valid L2 array row numbers                                                                                                       | 11-9  |

| Table 11-13                | Selecting the L2ValSer test type                                                                                                 |       |

| Table 11-14                | Selecting L2 RAMs for LSB control                                                                                                |       |

| Table 11-15                | Selecting counting sequence of L2 RAM column address LSBs                                                                        |       |

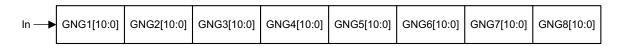

| Table 11-16                | GNG[10:0] field                                                                                                                  |       |

| Table 11-17                | L2 cache way grouping                                                                                                            | 11-13 |

|                            |                                                                                                                                  |       |

| T-61- 44 40                |                                                                                      | 11.10         |

|----------------------------|--------------------------------------------------------------------------------------|---------------|

| Table 11-18                | Identifying failing L2 bits with failing_bits[32:0]                                  |               |

| Table 11-19<br>Table 12-1  | Summary of MBIST patterns<br>Access to CP14 debug registers                          |               |

| Table 12-1                 | CP14 debug registers summary                                                         |               |

| Table 12-2                 | Debug memory-mapped registers                                                        |               |

| Table 12-3                 | Processor reset effect on debug and ETM logic                                        |               |

| Table 12-4                 | APB interface access with relation to software lock                                  | 12-0<br>12-10 |

| Table 12-6                 | Debug registers access with relation to power-down event                             |               |

| Table 12-7                 | Power management registers access with relation to power-down event                  |               |

| Table 12-8                 | ETM and CTI registers access with relation to power-down event                       |               |

| Table 12-9                 | Terms used in register descriptions                                                  |               |

| Table 12-10                | CP14 debug registers                                                                 |               |

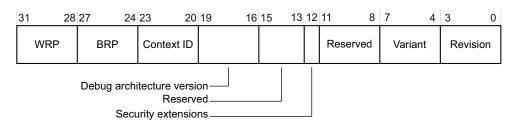

| Table 12-11                | Debug ID Register bit functions                                                      |               |

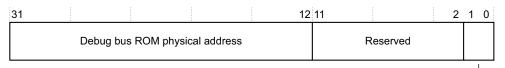

| Table 12-12                | Debug ROM Address Register bit functions                                             |               |

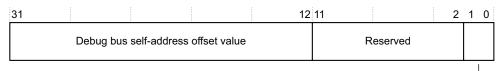

| Table 12-13                | Debug Self Address Offset Register bit functions                                     |               |

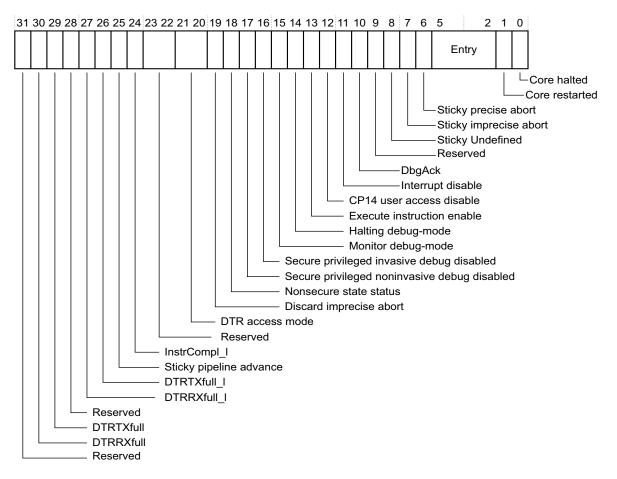

| Table 12-14                | Debug Status and Control Register bit functions                                      |               |

| Table 12-15                | Data Transfer Register bit functions                                                 |               |

| Table 12-16                | Watchpoint Fault Address Register bit functions                                      |               |

| Table 12-17                | Vector Catch Register bit functions                                                  |               |

| Table 12-18                | Event Catch Register bit functions                                                   |               |

| Table 12-19                | Debug State Cache Control Register bit functions                                     |               |

| Table 12-20                | Instruction Transfer Register bit functions                                          |               |

| Table 12-21                | Debug Run Control Register bit functions                                             |               |

| Table 12-22                | Breakpoint Value Registers bit functions                                             |               |

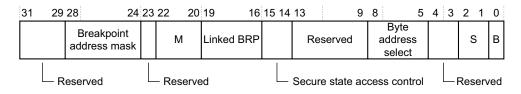

| Table 12-23                | Breakpoint Control Registers bit functions                                           |               |

| Table 12-24                | Meaning of BVR bits [22:20]                                                          |               |

| Table 12-25                | Watchpoint Value Registers bit functions                                             |               |

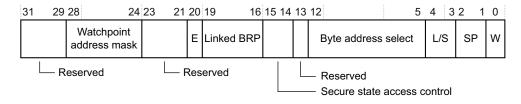

| Table 12-26                | Watchpoint Control Registers bit functions                                           |               |

| Table 12-27                | OS Lock Access Register bit functions                                                |               |

| Table 12-28                | OS Lock Status Register bit functions                                                |               |

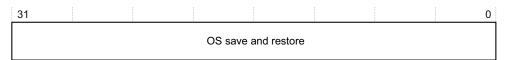

| Table 12-29                | OS Save and Restore Register bit functions                                           |               |

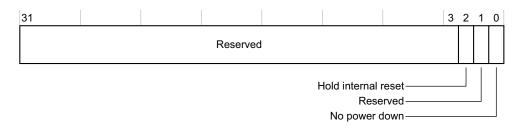

| Table 12-30                | PRCR bit functions                                                                   | 12-36         |

| Table 12-31                | PRSR bit functions                                                                   | 12-37         |

| Table 12-32                | Management registers                                                                 | 12-38         |

| Table 12-33                | Processor Identifier Registers                                                       | 12-39         |

| Table 12-34                | Integration Internal Output Control Register bit functions                           | 12-40         |

| Table 12-35                | Integration External Output Control Register bit functions                           | 12-41         |

| Table 12-36                | Integration Input Status Register bit functions                                      | 12-42         |

| Table 12-37                | Integration Mode Control Register bit functions                                      |               |

| Table 12-38                | Claim Tag Set Register bit functions                                                 |               |

| Table 12-39                | Claim Tag Clear Register bit functions                                               | 12-44         |

| Table 12-40                | Lock Access Register bit functions                                                   | 12-45         |

| Table 12-41                | Lock Status Register bit functions                                                   |               |

| Table 12-42                | Authentication Status Register bit functions                                         |               |

| Table 12-43                | Device Type Register bit functions                                                   |               |

| Table 12-44                | Peripheral Identification Registers                                                  |               |

| Table 12-45                | Fields in the Peripheral Identification Registers                                    |               |

| Table 12-46                | Peripheral ID Register 0 bit functions                                               |               |

| Table 12-47                | Peripheral ID Register 1 bit functions                                               |               |

| Table 12-48                | Peripheral ID Register 2 bit functions                                               |               |

| Table 12-49                | Peripheral ID Register 3 bit functions                                               |               |

| Table 12-50                | Peripheral ID Register 4 bit functions                                               |               |

| Table 12-51                | Component Identification Registers                                                   |               |

| Table 12-52                | Processor behavior on debug events                                                   |               |

| Table 12-53                | Values in Link Register after exceptions                                             |               |

| Table 12-54                | Read PC value after debug state entry                                                |               |

| Table 12-55                | Permitted updates to the CPSR in debug state                                         |               |

| Table 12-56                | Accesses to CP15 and CP14 registers in debug state                                   |               |

| Table 12-57<br>Table 12-58 | Authentication signal restrictions<br>Values to write to BCR for a simple breakpoint |               |

|                            | ימומפש נט איווני נט שטול וטו מ שוווטוב טובמגעטוונ                                    |               |

| Table 12 50                | Voluce to write to WCD for a simple watchnoint                                                        | 10 70 |

|----------------------------|-------------------------------------------------------------------------------------------------------|-------|

| Table 12-59<br>Table 12-60 | Values to write to WCR for a simple watchpoint<br>Example byte address masks for watchpointed objects |       |

| Table 12-00<br>Table 13-1  | Single-precision three-operand register usage                                                         |       |

| Table 13-1                 | Single-precision two-operand register usage                                                           |       |

| Table 13-3                 | Double-precision three-operand register usage                                                         |       |

| Table 13-4                 | Double-precision two-operand register usage                                                           |       |

| Table 13-5                 | NEON and VFP system registers                                                                         |       |

| Table 13-6                 | Accessing NEON and VFP system registers                                                               |       |

| Table 13-7                 | FPSID Register bit functions                                                                          |       |

| Table 13-8                 | FPSCR Register bit functions                                                                          |       |

| Table 13-9                 | Vector length and stride combinations                                                                 |       |

| Table 13-10                | Floating-Point Exception Register bit functions                                                       |       |

| Table 13-11                | MVFR0 Register bit functions                                                                          |       |

| Table 13-12                | MVFR1 Register bit functions                                                                          |       |

| Table 13-13                | Default NaN values                                                                                    |       |

| Table 13-14                | QNaN and SNaN handling                                                                                |       |

| Table 14-1                 | ETM implementation                                                                                    |       |

| Table 14-2                 | ETM register summary                                                                                  |       |

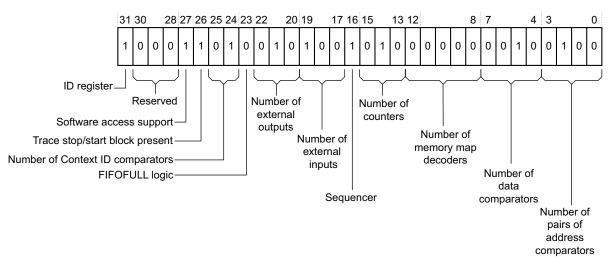

| Table 14-3                 | ID Register bit functions                                                                             |       |

| Table 14-4                 | Configuration Code Register bit functions                                                             |       |

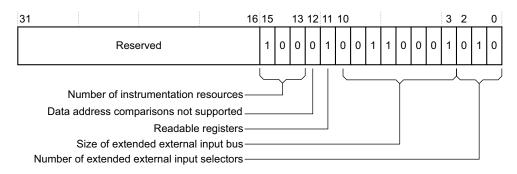

| Table 14-5                 | Configuration Code Extension Register bit functions                                                   |       |

| Table 14-6                 | Peripheral Identification Registers bit functions                                                     |       |

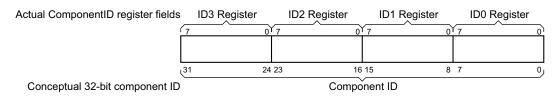

| Table 14-7                 | Component Identification Registers bit functions                                                      |       |

| Table 14-8                 | Output signals that can be controlled by the Integration Test Registers                               |       |

| Table 14-9                 | Input signals that can be read by the Integration Test Registers                                      |       |

| Table 14-10                | ITMISCOUT Register bit functions                                                                      |       |

| Table 14-11                | ITMISCIN Register bit functions                                                                       |       |

| Table 14-12                | ITTRIGGER Register bit functions                                                                      |       |

| Table 14-13                | ITATBDATA0 Register bit functions                                                                     |       |

| Table 14-14                | ITATBCTR2 Register bit functions                                                                      |       |

| Table 14-15                | ITATBCTR1 Register bit functions                                                                      |       |

| Table 14-16                | ITATBCTR0 Register bit functions                                                                      |       |

| Table 14-17                | PMU event number mappings                                                                             |       |

| Table 14-18                | PMU event cycle mappings                                                                              |       |

| Table 15-1                 | Trigger inputs                                                                                        |       |

| Table 15-2                 | Trigger outputs                                                                                       |       |

| Table 15-3                 | CTI register summary                                                                                  |       |

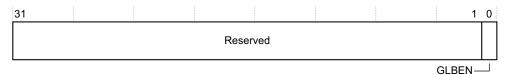

| Table 15-4                 | CTI Control Register bit functions                                                                    |       |

| Table 15-5                 | CTI Interrupt Acknowledge Register bit functions                                                      |       |

| Table 15-6                 | CTI Application Trigger Set Register bit functions                                                    |       |

| Table 15-7                 | CTI Application Trigger Clear Register bit functions                                                  |       |

| Table 15-8                 | CTI Application Pulse Register bit functions                                                          |       |

| Table 15-9                 | CTI Trigger to Channel Enable Registers bit functions                                                 |       |

| Table 15-10                | CTI Channel to Trigger Enable Registers bit functions                                                 |       |

| Table 15-11                | CTI Trigger In Status Register bit functions                                                          |       |

| Table 15-12                | CTI Trigger Out Status Register bit functions                                                         |       |

| Table 15-13                | CTI Channel In Status Register bit functions                                                          |       |

| Table 15-14                | CTI Channel Gate Register bit functions                                                               |       |

| Table 15-15                | ASIC Control Register bit functions                                                                   |       |

| Table 15-16                | CTI Channel Out Status Register bit functions                                                         |       |

| Table 15-17                | CTI Integration Test Registers                                                                        |       |

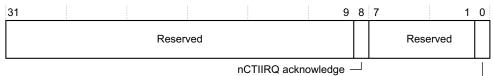

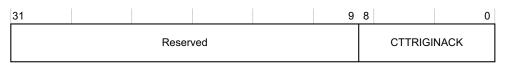

| Table 15-18                | ITTRIGINACK Register bit functions                                                                    |       |

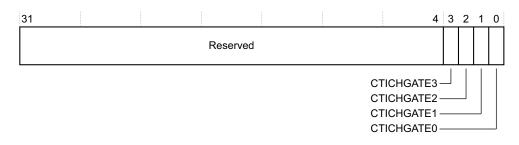

| Table 15-19                | ITCHOUT Register bit functions                                                                        |       |

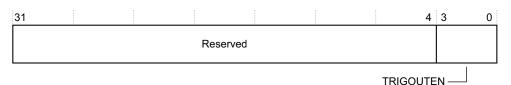

| Table 15-20                | ITTRIGOUT Register bit functions                                                                      |       |

| Table 15-21                | ITTRIGOUT connections to other integration test registers                                             |       |

| Table 15-22                | ITTRIGOUTACK Register bit functions                                                                   |       |

| Table 15-23                | ITTRIGOUTACK connections to other integration test registers                                          |       |

| Table 15-24                | ITCHIN Register bit functions                                                                         |       |

| Table 15-25                | ITTRIGIN Register bit functions                                                                       |       |

| Table 15-26                | ITTRIGIN connections to other integration test registers                                              |       |

|                            |                                                                                                       |       |

| Table 15-27 | Authentication Status Register bit functions                       |     |

|-------------|--------------------------------------------------------------------|-----|

| Table 15-28 | Device ID Register bit functions                                   |     |

| Table 15-29 | Device Type Identifier Register bit functions                      |     |

| Table 15-30 | Peripheral Identification Registers bit functions                  |     |

| Table 15-31 | Component Identification Registers bit functions                   |     |

| Table 16-1  | Data-processing instructions with a destination                    |     |

| Table 16-2  | Data-processing instructions without a destination                 |     |

| Table 16-3  | MOV and MOVN instructions                                          |     |

| Table 16-4  | Multiply instructions                                              |     |

| Table 16-5  | Parallel arithmetic instructions                                   |     |

| Table 16-6  | Extended instructions                                              |     |

| Table 16-7  | Miscellaneous data-processing instructions                         |     |

| Table 16-8  | Status register access instructions                                |     |

| Table 16-9  | Load instructions                                                  |     |

| Table 16-10 | Store instructions                                                 |     |

| Table 16-11 | Branch instructions                                                |     |

| Table 16-12 | Nonpipelined CP14 instructions                                     |     |

| Table 16-13 | Nonpipelined CP15 instructions                                     |     |

| Table 16-14 | CP15 instructions affected when ACTRL bit[20] = 0                  |     |

| Table 16-15 | Dual-issue restrictions                                            |     |

| Table 16-16 | Memory system effects on instruction timings                       |     |

| Table 16-17 | ThumbEE instructions                                               |     |

| Table 16-18 | Advanced SIMD integer ALU instructions                             |     |

| Table 16-19 | Advanced SIMD integer multiply instructions                        |     |

| Table 16-20 | Advanced SIMD integer shift instructions                           |     |

| Table 16-21 | Advanced SIMD floating-point instructions                          |     |

| Table 16-22 | Advanced SIMD byte permute instructions                            |     |

| Table 16-22 | Advanced SIMD load/store instructions                              |     |

| Table 16-23 | Advanced SIMD register transfer instructions                       |     |

| Table 16-25 | VFP Instruction cycle counts                                       |     |

| Table 17-1  | Format of timing parameter tables                                  |     |

| Table 17-2  | Timing parameters of AXI interface                                 |     |

| Table 17-2  | Timing parameters of ATB and CTI interfaces                        |     |

| Table 17-4  | Timing parameters of APB interface and miscellaneous debug signals |     |

| Table 17-5  | Timing parameters of the L1 and L2 MBIST interface                 |     |

| Table 17-5  | Timing parameters of the L2 preload interface                      |     |

| Table 17-0  | Timing parameters of the DFT interface                             |     |

| Table 17-8  | Timing parameters of miscellaneous signals                         |     |

| Table A-1   | AXI interface                                                      |     |

| Table A-2   | ATB interface                                                      |     |

| Table A-3   | MBIST interface                                                    | A-4 |

| Table A-4   | DFT and additional MBIST pin requirements                          |     |

| Table A-5   | Preload engine interface                                           |     |

| Table A-6   | APB interface                                                      |     |

| Table A-7   | Miscellaneous signals                                              |     |

| Table A-8   | Miscellaneous debug signals                                        |     |

| Table A-9   | Miscellaneous ETM and CTI signals                                  |     |

| Table B-1   | Advanced SIMD mnemonics                                            |     |

| Table B-2   | VFP data-processing mnemonics                                      |     |

| Table C-1   | Differences between issue F and issue G                            |     |

| Table C-2   | Differences between issue G and issue H                            |     |

| Table C-3   | Differences between issue H and issue I                            |     |

| Table C-4   | Differences between Issue I and Issue J                            |     |

| Table C-5   | Differences between Issue J and Issue K                            |     |

|             |                                                                    |     |

# List of Figures Cortex-A8 Technical Reference Manual

|             | Key to timing diagram conventions               | xxiii |

|-------------|-------------------------------------------------|-------|

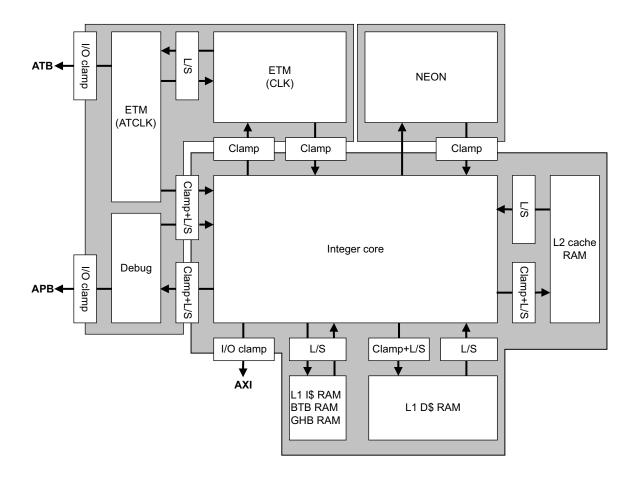

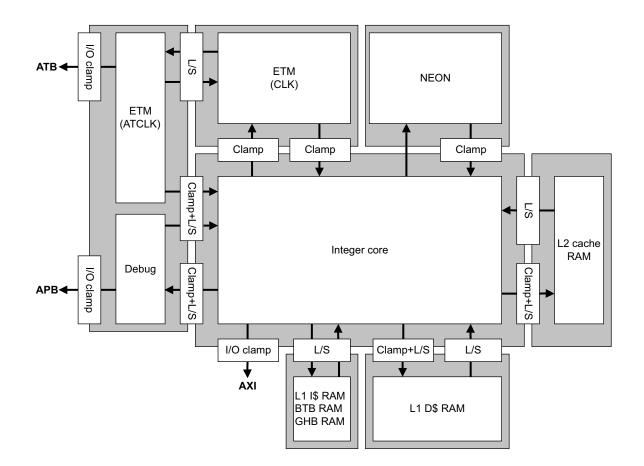

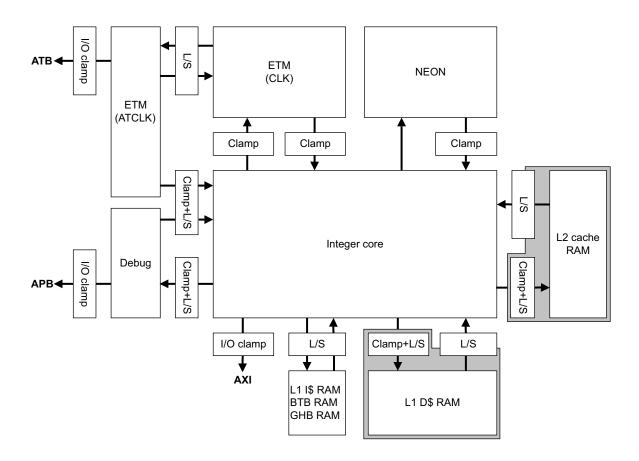

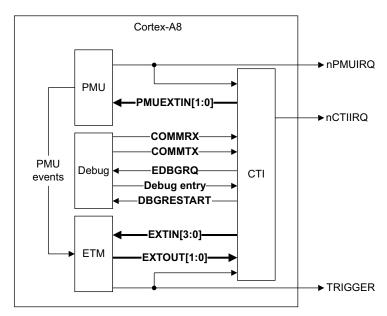

| Figure 1-1  | Cortex-A8 block diagram                         | 1-4   |

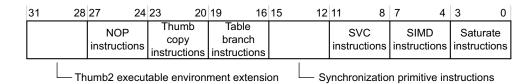

| Figure 2-1  | 32-bit ARM Thumb-2 instruction format           | 2-3   |

| Figure 2-2  | ThumbEE Configuration Register format           | 2-5   |

| Figure 2-3  | ThumbEE HandlerBase Register format             |       |

| Figure 2-4  | Jazelle Identity Register format                | 2-7   |

| Figure 2-5  | Jazelle Main Configuration Register format      |       |

| Figure 2-6  | Jazelle OS Control Register format              |       |

| Figure 2-7  | Secure and Nonsecure states                     | 2-9   |

| Figure 2-8  | Big-endian addresses of bytes within words      | 2-15  |

| Figure 2-9  | Little-endian addresses of bytes within words   |       |

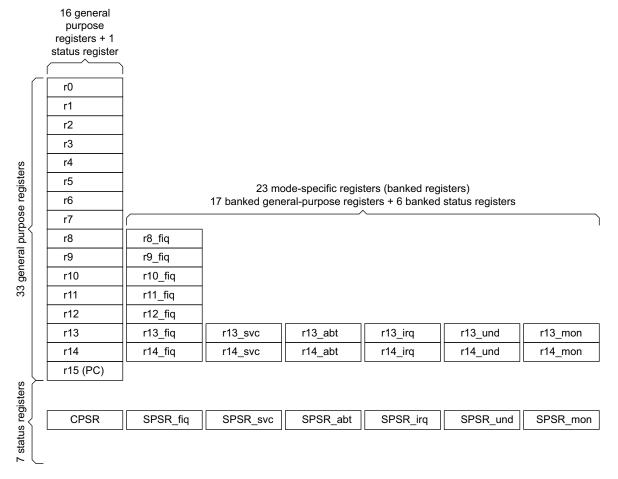

| Figure 2-10 | Register organization in ARM state              |       |

| Figure 2-11 | Processor register set showing banked registers |       |

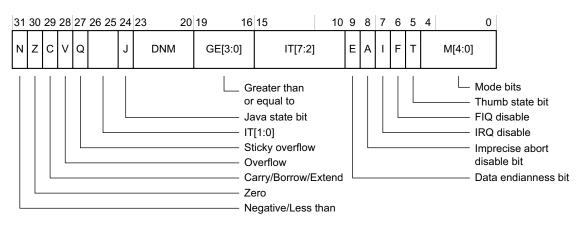

| Figure 2-12 | Program status register                         | 2-21  |

| Figure 3-1  | Main ID Register format                         |       |

| Figure 3-2  | Cache Type Register format                      |       |

| Figure 3-3  | TLB Type Register format                        |       |

| Figure 3-4  | Processor Feature Register 0 format             |       |

| Figure 3-5  | Processor Feature Register 1 format             |       |

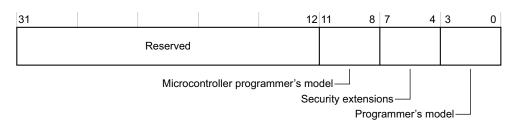

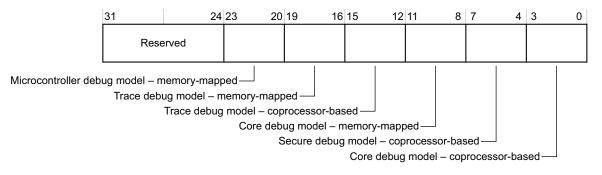

| Figure 3-6  | Debug Feature Register 0 format                 |       |

| Figure 3-7  | Memory Model Feature Register 0 format          |       |

| Figure 3-8  | Memory Model Feature Register 1 format          |       |

| Figure 3-9  | Memory Model Feature Register 2 format          |       |

| Figure 3-10 | Memory Model Feature Register 3 format          |       |

| Figure 3-11 | Instruction Set Attributes Register 0 format    |       |

| Figure 3-12 | Instruction Set Attributes Register 1 format    |       |

| Figure 3-13 | Instruction Set Attributes Register 2 format    |       |

| Figure 3-14 | Instruction Set Attributes Register 3 format    |       |

| Figure 3-15 | Instruction Set Attributes Register 4 format    |       |

| Figure 3-16 | Cache Level ID Register format                  |       |

| Figure 3-17 | Silicon ID Register format                              | 3-41  |

|-------------|---------------------------------------------------------|-------|

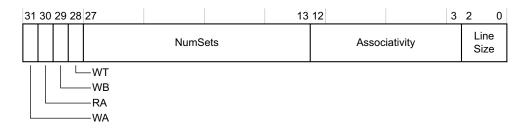

| Figure 3-18 | Cache Size Identification Register format               | 3-42  |

| Figure 3-19 | Cache Size Selection Register format                    | 3-43  |

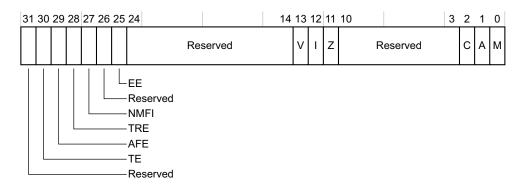

| Figure 3-20 | Control Register bit assignments                        | 3-45  |

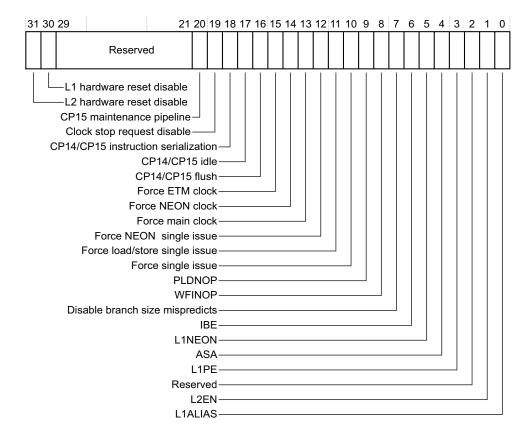

| Figure 3-21 | Auxiliary Control Register format                       | 3-48  |

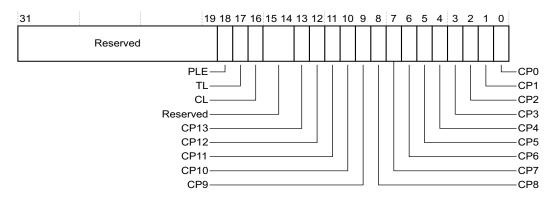

| Figure 3-22 | Coprocessor Access Control Register format              | 3-52  |

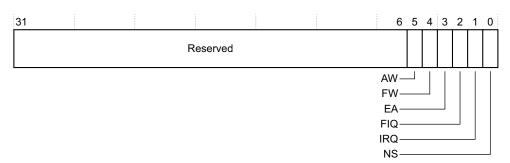

| Figure 3-23 | Secure Configuration Register format                    | 3-53  |

| Figure 3-24 | Secure Debug Enable Register format                     | 3-55  |

| Figure 3-25 | Nonsecure Access Control Register format                | 3-56  |

| Figure 3-26 | Translation Table Base Register 0 format                | 3-58  |

| Figure 3-27 | Translation Table Base Register 1 format                | 3-59  |

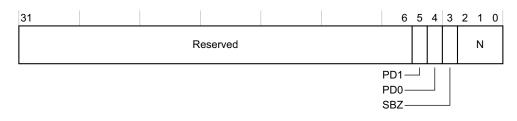

| Figure 3-28 | Translation Table Base Control Register format          | 3-61  |

| Figure 3-29 | Domain Access Control Register format                   | 3-62  |

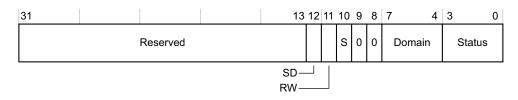

| Figure 3-30 | Data Fault Status Register format                       | 3-63  |

| Figure 3-31 | Instruction Fault Status Register format                |       |

| Figure 3-32 | c7 format for set and way                               | 3-70  |

| Figure 3-33 | c7 format for MVA                                       |       |

| Figure 3-34 | PA Register format for successful translation           |       |

| Figure 3-35 | PA Register format for unsuccessful translation         |       |

| Figure 3-36 | TLB Operations MVA and ASID format                      |       |

| Figure 3-37 | TLB Operations ASID format                              |       |

| Figure 3-38 | Performance Monitor Control Register format             | 3-77  |

| Figure 3-39 | Count Enable Set Register format                        |       |

| Figure 3-40 | Count Enable Clear Register format                      | 3-79  |

| Figure 3-41 | FLAG Register format                                    |       |

| Figure 3-42 | Software Increment Register format                      |       |