# Arm<sup>®</sup> Cortex<sup>®</sup>-M3 DesignStart<sup>™</sup> FPGA-Xilinx edition

Revision: r0p0

**User Guide**

# Arm<sup>®</sup> Cortex<sup>®</sup>-M3 DesignStart<sup>™</sup> FPGA-Xilinx edition

#### **User Guide**

Copyright © 2018 Arm Limited or its affiliates. All rights reserved.

#### **Release Information**

#### **Document History**

| Issue Date |                 | Confidentiality  | Change                  |  |

|------------|-----------------|------------------|-------------------------|--|

| 0000-00    | 29 October 2018 | Non-Confidential | First release for r0p0. |  |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. **No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.**

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with <sup>®</sup> or <sup>™</sup> are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at *http://www.arm.com/company/policies/trademarks*.

Copyright © 2018 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

#### **Product Status**

The information in this document is Final, that is for a developed product.

#### Web Address

http://www.arm.com

# Contents Arm<sup>®</sup> Cortex<sup>®</sup>-M3 DesignStart<sup>™</sup> FPGA-Xilinx edition User Guide

|           | Pref  | face                                                                         |      |

|-----------|-------|------------------------------------------------------------------------------|------|

|           |       | About this book                                                              |      |

|           |       | Feedback                                                                     |      |

| Chapter 1 | Intro | oduction                                                                     |      |

|           | 1.1   | Cortex <sup>®</sup> -M3 DesignStart <sup>™</sup> FPGA-Xilinx edition package | 1-11 |

|           | 1.2   | Directory structure                                                          | 1-12 |

|           | 1.3   | Cortex®-M3 processor integration                                             | 1-13 |

| Chapter 2 | Insta | alling the Cortex®-M3 DesignStart™ example design                            |      |

|           | 2.1   | Installing board files                                                       | 2-15 |

|           | 2.2   | Setting local drive for Windows                                              | 2-17 |

|           | 2.3   | Installing Arm IP repository                                                 | 2-18 |

|           | 2.4   | Installing Arm software repository                                           | 2-19 |

|           | 2.5   | Downloading QSPI memory models                                               | 2-21 |

|           | 2.6   | Configuring simulation in Vivado                                             | 2-23 |

| Chapter 3 | Cort  | tex®-M3 processor IP configuration                                           |      |

|           | 3.1   | Configuration tab                                                            | 3-25 |

|           | 3.2   | Debug tab                                                                    | 3-27 |

|           | 3.3   | Instruction Memory tab                                                       | 3-29 |

|           | 3.4   | Data Memory tab                                                              | 3-31 |

|           |       |                                                                              |      |

|            | 3.5  | Cortex <sup>®</sup> -M3 processor signals                                      | 3-33      |

|------------|------|--------------------------------------------------------------------------------|-----------|

| Chapter 4  | Work | king with the Cortex®-M3 DesignStart™ example design                           |           |

|            | 4.1  | Editing the A7 example design                                                  | 4-36      |

|            | 4.2  | Debug                                                                          | 4-37      |

|            | 4.3  | Memory map                                                                     | 4-38      |

|            | 4.4  | QSPI multiplexing for the V2C-DAPLink board                                    | 4-41      |

|            | 4.5  | Interrupt mapping                                                              | 4-42      |

|            | 4.6  | Constraints                                                                    | 4-43      |

|            | 4.7  | Loading the pre-built bitstream                                                | 4-44      |

|            | 4.8  | Loading the flash file                                                         | 4-45      |

|            | 4.9  | Bit file regeneration                                                          | 4-47      |

|            | 4.10 | Simulation                                                                     | 4-48      |

| Chapter 5  | V2C- | DAPLink board                                                                  |           |

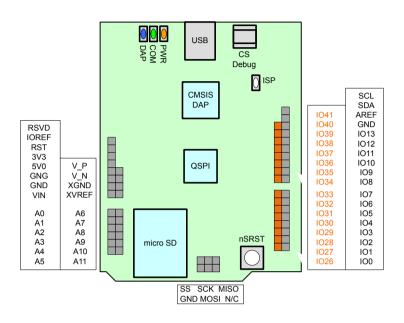

|            | 5.1  | V2C-DAPLink adaptor board features                                             | 5-50      |

|            | 5.2  | V2C-DAPLink configuration                                                      | 5-52      |

|            | 5.3  | Flash download requirements                                                    | 5-53      |

|            | 5.4  | V2C-DAPLink board layout                                                       | 5-54      |

|            | 5.5  | Conditions to enable the DAP interface                                         | 5-56      |

|            | 5.6  | DAP drivers                                                                    | 5-57      |

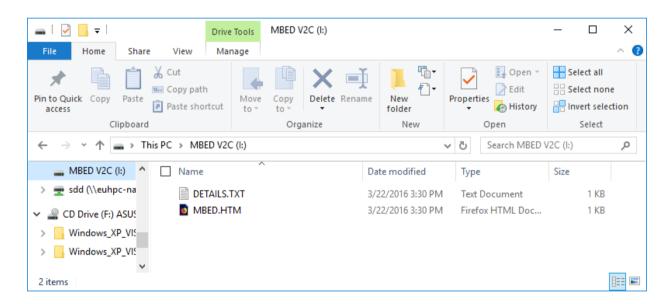

|            | 5.7  | Programming the V2C-DAPLink QSPI using drag and drop                           | 5-58      |

|            | 5.8  | Using the µVision debugger to communicate through V2C-DAPLink                  | 5-60      |

|            | 5.9  | Using the $\mu$ Vision debugger to download projects through the flash program | ming      |

|            |      | utility                                                                        | 5-62      |

|            | 5.10 | Recovering the DAP connection                                                  | 5-65      |

| Chapter 6  | Exan | nple software design                                                           |           |

|            | 6.1  | Example software design for Arty A7                                            | 6-68      |

|            | 6.2  | Example software design directory structure                                    | 6-69      |

|            | 6.3  | Example design reference files                                                 | 6-70      |

|            | 6.4  | Generating the Arty A7 board support package                                   | 6-71      |

|            | 6.5  | Building the example software design                                           | 6-77      |

|            | 6.6  | Software update flow                                                           | 6-78      |

| Appendix A | Revi | sions                                                                          |           |

|            | A.1  | Revisions                                                                      | Appx-A-81 |

# Preface

This preface introduces the Arm<sup>®</sup> Cortex<sup>®</sup>-M3 DesignStart<sup>™</sup> FPGA-Xilinx edition User Guide.

It contains the following:

- *About this book* on page 7.

- *Feedback* on page 9.

### About this book

This book describes how to use the Cortex<sup>®</sup>-M3 DesignStart<sup>™</sup> FPGA-Xilinx edition to design your system using the Cortex-M3 processor. This book also describes an example design for the Digilent Arty *Artix* 7 (A7) development board.

#### Product revision status

The *rmpn* identifier indicates the revision status of the product described in this book, for example, r1p2, where:

- rm Identifies the major revision of the product, for example, r1.

- pn Identifies the minor revision or modification status of the product, for example, p2.

#### Intended audience

The intended audience is system designers, system integrators, and verification engineers who want to implement the processor in a *Field-Programmable Gate Array* (FPGA) using the Xilinx Vivado tools.

#### Using this book

This book is organized into the following chapters:

#### **Chapter 1 Introduction**

The Cortex-M3 DesignStart<sup>™</sup> FPGA-Xilinx edition package provides an easy way to use the Cortex-M3 processor in the Xilinx Vivado design environment. The Cortex-M3 processor is intended for deeply embedded applications, usually in ASIC designs. It can be implemented in FPGA, but is not optimized for timing. The processor implements the Armv7-M architecture.

#### Chapter 2 Installing the Cortex<sup>®</sup>-M3 DesignStart<sup>™</sup> example design

This chapter describes the Cortex-M3 DesignStart example design installation process.

#### Chapter 3 Cortex®-M3 processor IP configuration

After installing the Arm *IP Integrator* (IPI) repository, you can find the Cortex-M3 processor package in the Vivado IP catalog.

#### Chapter 4 Working with the Cortex<sup>®</sup>-M3 DesignStart<sup>™</sup> example design

This chapter describes how to work with an example design targeting a low-cost evaluation board, Digilent Arty *Artix 7* (A7). This example design is provided to demonstrate the integration and software development using the Cortex-M3 processor. The example is based on the Digilent Arty A7-35T board, and uses some of the standard Xilinx peripherals to connect to some of the features on the board. The example is intended to show typical usage, rather than a completely minimal Cortex-M3 processor design.

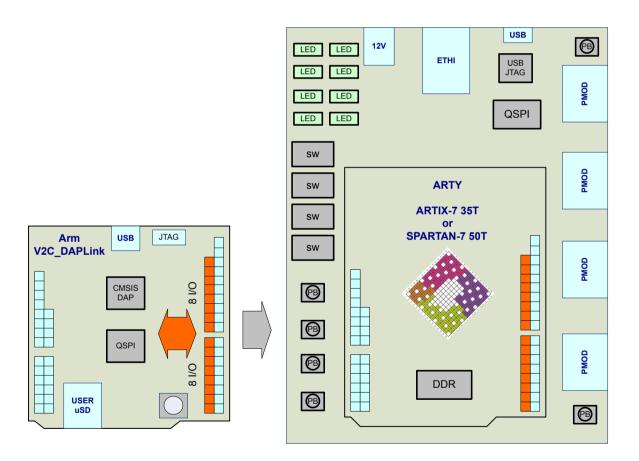

#### Chapter 5 V2C-DAPLink board

The optional V2C-DAPLink adaptor board provides a debug flow that is familiar to anyone who is used to working with Cortex-M microcontrollers. It allows Arty FPGA boards to be used with mbed OS 2 Classic. This chapter describes the optional V2C-DAPLink adaptor board and how it is used.

#### Chapter 6 Example software design

This chapter describes an example software design, and describes how to build and debug it.

#### **Appendix A Revisions**

This appendix describes the technical changes between released issues of this document.

#### Glossary

The Arm<sup>®</sup> Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

See the Arm<sup>®</sup> Glossary for more information.

#### Typographic conventions

#### italic

Introduces special terminology, denotes cross-references, and citations.

#### bold

Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.

#### monospace

Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.

#### <u>mono</u>space

Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.

#### monospace italic

Denotes arguments to monospace text where the argument is to be replaced by a specific value.

#### monospace bold

Denotes language keywords when used outside example code.

#### <and>

Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:

ADD Rd, SP, #<imm>

#### SMALL CAPITALS

Used in body text for a few terms that have specific technical meanings, that are defined in the *Arm*<sup>®</sup> *Glossary*. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE.

#### Additional reading

This book contains information that is specific to this product. See the following documents for other relevant information.

#### Arm publications

- Cortex<sup>®</sup>-M3 Technical Reference Manual (100165).

- Arm<sup>®</sup> CoreSight<sup>™</sup> SoC-400 Technical Reference Manual (DDI 0480).

The following confidential book is only available to licensees:

Cortex<sup>®</sup>-M3 Integration and Implementation Manual (DII 0240B).

#### **Other publications**

- IEEE Std 1149.1-2001, Test Access Port and Boundary-Scan Architecture (JTAG).

- ANSI/IEEE Std 754-2008, IEEE Standard for Binary Floating-Point Arithmetic.

# Feedback

#### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

#### Feedback on content

If you have comments on content then send an e-mail to *errata@arm.com*. Give:

- The title Arm Cortex-M3 DesignStart FPGA-Xilinx edition User Guide.

- The number 101483 0000 00 en.

- If applicable, the page number(s) to which your comments refer.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

\_\_\_\_\_ Note \_\_\_\_\_

Arm tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader.

# Chapter 1 Introduction

The Cortex-M3 DesignStart<sup>™</sup> FPGA-Xilinx edition package provides an easy way to use the Cortex-M3 processor in the Xilinx Vivado design environment. The Cortex-M3 processor is intended for deeply embedded applications, usually in ASIC designs. It can be implemented in FPGA, but is not optimized for timing. The processor implements the Armv7-M architecture.

This chapter describes the Cortex-M3 DesignStart FPGA-Xilinx edition features and directory structure.

It contains the following sections:

- 1.1 Cortex<sup>®</sup>-M3 DesignStart<sup>™</sup> FPGA-Xilinx edition package on page 1-11.

- *1.2 Directory structure* on page 1-12.

- 1.3 Cortex<sup>®</sup>-M3 processor integration on page 1-13.

# 1.1 Cortex<sup>®</sup>-M3 DesignStart<sup>™</sup> FPGA-Xilinx edition package

An example system design is provided to target a low-cost development platform, with example integration tests.

The Cortex-M3 DesignStart FPGA-Xilinx edition package includes:

- A Cortex-M3 processor that has:

- A *Nested Vectored Interrupt Controller* (NVIC) that supports up to 240 interrupts, each with up to 256 levels of priority that can be changed dynamically.

- Configurable endianness, only little-endian is supported in the example system.

- Configurable embedded debug support.

- Instruction Tightly Coupled Memory (ITCM), up to 1MB.

- Data Tightly Coupled Memory (DTCM), up to 1MB.

- ITCM Alias support.

- Serial Wire (SW), JTAG, or combined SWJ-DP debug port.

- Integrated AHB to AXI bridges, which allow the packaged Cortex-M3 processor to connect directly to standard Vivado components.

- Optional *Embedded Trace Macrocell* (ETM) for instruction trace, *Data Watchpoint and Trace* (DWT) and *Instrumentation Trace Macrocell* (ITM), coupled with a *Trace Port Interface Unit* (TPIU) with four pins.

- Optional V2C-DAPLink board support, which:

- Provides Cortex-M debug flow.

- V2C-DAPLink USB to the Serial Wire Debug (SWD) interface.

- V2C-DAPLink USB UART endpoint.

- Local Quad Serial Peripheral Interface (QSPI), flash for code download (8MB) independent of FPGA image.

- User accessible microSD card support.

- Pass-through connections for shield adapter boards.

- Example designs for Arty Artix 7 (A7) 35T development boards.

- Integrates the processor with standard Xilinx peripherals.

- Example software tests.

- Cortex Microcontroller Software Interface Standard (CMSIS) compatible Board Support Package (BSP) generation that is done through Xilinx Vivado Software Development Kit (SDK).

- Support for simulation and FPGA implementation. The encrypted design can be:

- Simulated in the Xilinx Vivado and Mentor QuestaSim simulators.

- Implemented for FPGA in Xilinx Vivado.

— Note —

The Cortex-M3 DesignStart FPGA-Xilinx edition package:

- Can be used with any suitable Xilinx FPGA, but the example system design only supports one specific development board. You require version 2018.2 or later of the Xilinx Vivado tool.

- Targets Windows development environment and uses Arm Keil *Microcontroller Development Kit* (MDK) for software development.

To use the example system designs, you require:

- A Digilent Arty A7 development board or a supported Xilinx FPGA.

- The board files provided by Digilent for this board or support files for any board that you use.

- Xilinx Vivado.

- Arm Keil MDK or a Cortex-M compatible toolchain.

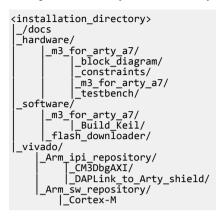

### 1.2 Directory structure

The expected directory structure after you download and unpack the Arm IP deliverables is:

The following table describes the directory structure.

#### Table 1-1 Directory structure

| File                                                  | Description                                                                                                    |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| /docs                                                 | Contains this document and example design diagram.                                                             |

| hardware/m3_for_arty_a7/block_diagram/                | Example block diagram.                                                                                         |

| hardware/m3_for_arty_a7/constraints/                  | Constraint files.                                                                                              |

| hardware/m3_for_arty_a7/m3_for_arty_a7/               | Vivado project root.                                                                                           |

| hardware/m3_for_arty_a7/testbench/                    | Simulation testbench.                                                                                          |

| software/m3_for_arty_a7/                              | Example software application.                                                                                  |

| software/m3_for_arty_a7/Build_Keil/                   | Compilation directory for example code, which compiles under MDK and uses Xilinx drivers.                      |

| software/flash_downloader/                            | Flash downloader.                                                                                              |

| vivado/Arm_ipi_repository/CM3DbgAXI/                  | Cortex-M3 processor debug and AXI interface.                                                                   |

| vivado/Arm_ipi_repository/<br>DAPLink_to_Arty_shield/ | Interface block to the Arty adaptor board.                                                                     |

| vivado/Arm_sw_repository/                             | Cortex-M3 processor software files for <i>Board Support Package</i> (BSP) and example application development. |

Before you can use the deliverables, you must configure your Vivado installation to:

• Reference the Arm IP.

– Note –

• Install the Digilent board files, if you want to use the provided example design.

If you have already installed other Arm DesignStart FPGA-Xilinx products, then these have a similar directory structure. Arm recommends that you merge the directory structure between the installs to simplify their use. At a minimum, Arm recommends that you merge the directories under /vivado so that Vivado only needs to be assigned one directory location to read Arm hardware and software repositories.

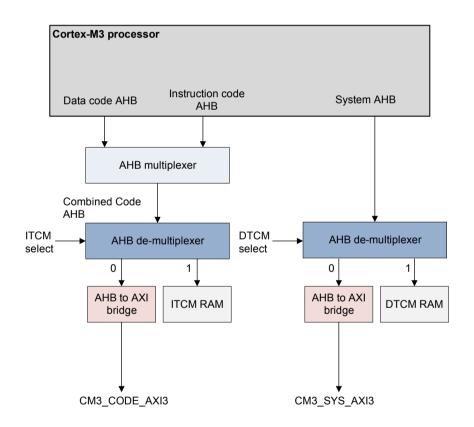

# 1.3 Cortex<sup>®</sup>-M3 processor integration

The Cortex-M3 processor which is included in the Cortex-M3 DesignStart FPGA-Xilinx edition deliverables has been pre-integrated with several components to make it easier to use in an FPGA flow.

There are two *Tightly Coupled Memory* (TCM) instances, for code and data. These are both configurable in size. The *Instruction Tightly Coupled Memory* (ITCM) can be configured at run time to be aliased to either or both of 0x00000000 and 0x10000000. The *Data Tightly Coupled Memory* (DTCM) is at a fixed location of 0x20000000.

The instruction code and data code AHB interfaces from the processor are combined internally. Any access from either of these buses which does not match an active ITCM alias is presented on the external instruction AXI interface.

The *System AHB* (S-AHB) interface from the processor is used to access the DTCM, any accesses which are not within the range of the configured DTCM size are presented on the system AXI interface.

The processor is integrated with a Serial Wire/JTAG Debug Port (SWJ-DP) to provide debug access.

The following figure shows internal memory processing of the instruction code and data code AHB interfaces.

Figure 1-1 Internal memory processing

# Chapter 2 Installing the Cortex<sup>®</sup>-M3 DesignStart<sup>™</sup> example design

This chapter describes the Cortex-M3 DesignStart example design installation process.

—— Attention —

If you only use the provided example design for software development, then you can skip 2.5 *Downloading QSPI memory models* on page 2-21 and 2.6 *Configuring simulation in Vivado* on page 2-23. You can use the steps described in 4.8 *Loading the flash file* on page 4-45 to load the FPGA image.

It contains the following sections:

- 2.1 Installing board files on page 2-15.

- 2.2 Setting local drive for Windows on page 2-17.

- 2.3 Installing Arm IP repository on page 2-18.

- 2.4 Installing Arm software repository on page 2-19.

- 2.5 Downloading OSPI memory models on page 2-21.

- 2.6 Configuring simulation in Vivado on page 2-23.

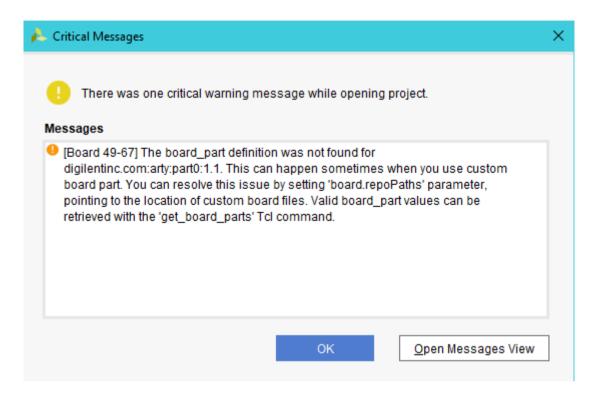

# 2.1 Installing board files

The Digilent Arty *Artix* 7 (A7) board uses a board file to enable easy connectivity from the Xilinx *IP Integrator* (IPI) tool to the board pins. To use the board file in the tool, you must copy the board file into the Vivado installation.

#### — Caution -

If you have opened the example design before the board files were installed, then Vivado has already modified the project to only target the device and not the board. In this scenario, when the example design block diagram is opened, Vivado reports errors because it does not have the board I/O connections. To resolve this, you must copy the Xilinx project file (m3\_for\_arty\_a7.xpr) again from the archive.

#### Procedure

- The board file download and installation instructions are found at <a href="https://reference.digilentinc.com/learn/software/tutorials/vivado-board-files/start">https://reference.digilentinc.com/learn/software/tutorials/vivado-board-files/start</a>. As a minimum you must install the /arty directory.

- To use the board files in a shared environment, you can add a reference to the location as part of your design. For example, if you uncompress the Digilent files to <install\_dir>/vivado/Digilent, you can use the following command in the Tcl console.

set\_param board.repoPaths ../../vivado/Digilent\_board\_files/vivado-boards-master/new/ board\_files/arty/

Alternatively, the Vivado project has the parameter board.repoPaths ready within it. Open the Vivado project, <install\_dir>/hardware/m3\_for\_arty\_a7/m3\_for\_arty\_a7/m3\_for\_arty\_a7.xpr, and uncomment the following line:

<!-- Option Name="BoardPartRepoPaths" Val="\$PPRDIR/../../vivado/Digilent\_board\_files/ vivado-boards-master/new/board\_files"/ -->

When the design is opened in Vivado and if the board files are not correctly installed, the following error message is displayed.

#### Figure 2-1 Error message

#### Next Steps

You must now proceed to 2.2 Setting local drive for Windows on page 2-17.

# 2.2 Setting local drive for Windows

Some Vivado projects can have issues with long path names to instances deep within the hierarchy because of Windows limitations on path length. This can become apparent when running simulations and other processes.

To resolve this, when running in Windows, Arm recommends that you assign a drive letter to the root of the current design. Using this method, all subsequent paths are relative to this drive letter. To map a local drive letter to the current path:

#### Prerequisites

You must complete the steps in 2.1 Installing board files on page 2-15.

#### Procedure

- 1. Open Vivado.

- 2. Open the Tcl console window.

- 3. The current directory location can be checked using the Unix command pwd.

- 4. Navigate to your <installation\_directory> folder. This is the folder where the Cortex-M3 package was installed.

- 5. To map the <installation\_directory> folder to the drive V:, type the following command in the prompt:

exec subst V: .

—— Attention —

In the exec subst V: . command, you must add a space between V: and . characters.

The package <installation\_directory> folder maps to drive V: and the rest of this book assumes that this folder maps to drive V:. If you map to a different drive, you must use the different drive in the instructions as appropriate. If the drive mapping is successful, you should have the directories V:/ hardware, V:/software, V:/vivado, and V:/docs.

#### **Next Steps**

You must now proceed to 2.3 Installing Arm IP repository on page 2-18.

# 2.3 Installing Arm IP repository

After downloading and unpacking the deliverable, the Arm *IP Integrator* (IPI) repository must be added to the list of Vivado IP repositories. This makes the processor available in any new designs.

To add Arm IPI repository to the list of Vivado IP repositories:

#### Prerequisites

You must complete the steps in:

- 2.1 Installing board files on page 2-15.

- 2.2 Setting local drive for Windows on page 2-17.

#### Procedure

- 1. Open Vivado.

- 2. From Tools  $\rightarrow$  Settings, select IP Defaults.

- 3. In the list of Default IP repository search paths, add the path to the /Arm\_ipi\_repository.

Vivado only reads the IPI repository during design creation. If the repository is updated, or an existing design must use the Cortex-M3 processor, then you must refresh the project repository. To do this, navigate to Tools  $\rightarrow$  Settings  $\rightarrow$  IP  $\rightarrow$  Repository  $\rightarrow$  Refresh all.

#### **Next Steps**

You must now proceed to 2.4 Installing Arm software repository on page 2-19.

### 2.4 Installing Arm software repository

The Arm software repository must also be added to the list of available Vivado repositories.

To add the Arm software repository to the list of Vivado software repositories:

#### Prerequisites

You must complete the steps in:

- 2.1 Installing board files on page 2-15.

- 2.2 Setting local drive for Windows on page 2-17.

- 2.3 Installing Arm IP repository on page 2-18.

#### Procedure

- 1. Open Vivado.

- 2. From File, select Launch SDK.

- Set the default *Exported location* to V:/software and the default *Workspace* to V:/software/ m3\_for\_arty\_a7/sdk\_workspace.

| 🕕 Launch SDK                                        | ×     |

|-----------------------------------------------------|-------|

| Launch software development tool.                   | 4     |

| Exported location: 🔄 V:/software                    | ~     |

| Workspace: V:/software/m3_for_arty_a7/sdk_workspace | ~     |

| ? ОК Са                                             | ancel |

#### Figure 2-2 Launch SDK

4. Vivado issues a warning regarding the exported hardware file being out of date. This is because you have not built the project. Select Yes to proceed.

| 🙏 Expor | ted hardware system out-of-date                                                                                                                                                                                                                                                                   | $\times$ |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| ?       | Exported Hardware file is out of date. Exported hardware information may be inconsistent with respect to the current state of the design. It is recommended that you re-export the design and launch SDK otherwise SDK is launched with out of date hardware system file. Do you want to proceed? |          |

#### Figure 2-3 Exported hardware system out-of-date

5. Once the SDK opens, select Xilinx → Repositories and add the path to the V:vivado/ Arm\_sw\_repository/ to the Global Repositories.

#### **Next Steps**

To use the Cortex-M3 software on existing designs, you might be required to rescan the *Software Development Kit* (SDK) repositories. In the SDK, select Xilinx  $\rightarrow$  Repositories  $\rightarrow$  Rescan Repositories.

You must now proceed to 2.5 Downloading QSPI memory models on page 2-21.

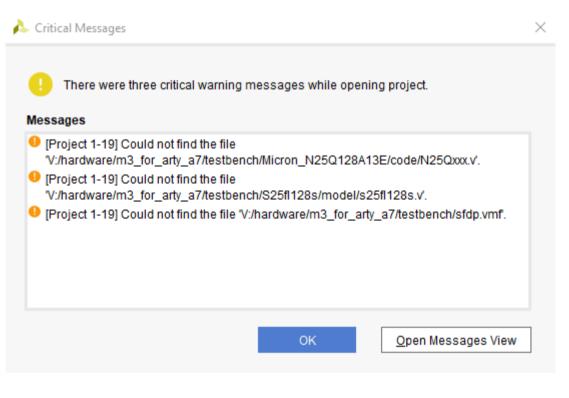

# 2.5 Downloading QSPI memory models

- Note

If you want to simulate the example design, then the testbench can also simulate the *Quad Serial Port Interface* (QSPI) devices that are fitted to the Arty *Artix* 7 (A7) baseboard (a Micron device) and the V2C-DAPLink board (a Cypress device).

#### Prerequisites

It is only necessary to download the QSPI memory models if you want to simulate the example design when you are operating on the Arty A7 board, and optionally, with the V2C-DAPLink board fitted. If you do not want to simulate the design, you can ignore this section.

#### ------ Caution ------

If you do not download the QSPI memory models, then you get warnings every time you open the Vivado project. The following figure shows these warnings. If you do not intend to simulate the QSPI models, then these warnings can be ignored.

#### Figure 2-4 Critical warning messages

You must complete the steps in:

- 2.1 Installing board files on page 2-15.

- 2.2 Setting local drive for Windows on page 2-17.

- 2.3 Installing Arm IP repository on page 2-18.

- 2.4 Installing Arm software repository on page 2-19.

#### Procedure

- To simulate the QSPI devices that are fitted, you must download the appropriate models from Micron and Cypress websites.

- When the QSPI memory models are correctly installed, you can enable using the Verilog define at the top of V:/testbench/tb\_m3\_for\_arty.v.

If the V2C-DAPLink board is fitted and QSPI device models included, then code execution is from the QSPI device on the V2C-DAPLink board.

#### **Next Steps**

You must first refer to the information in either of the following depending on the QSPI model that you choose to install:

- 2.5.1 Micron QSPI model on page 2-22.

- 2.5.2 Cypress QSPI model on page 2-22.

After you have downloaded and installed the required QSPI model, you must proceed to 2.6 Configuring simulation in Vivado on page 2-23.

#### 2.5.1 Micron QSPI model

The Micron device used on the Digilent Arty Artix 7 (A7) base board is N25Q128A13E.

A Verilog simulation model for this device is available in the Micron website.

The archive file that you must download is N25Q128A13E\_3V\_MicronXIP\_VG12.tar. When the archive is downloaded, it must be expanded to a directory named /Micron\_N25Q128A13E. This directory must be located under the V:/hardware/m3\_for\_arty\_a7/testbench directory. To enable the correct configuration of the QSPI memory, the /Micron\_N25Q128A13E/sim/sfdp.vmf file must be copied to the V:/hardware/m3\_for\_arty\_a7/testbench directory.

If you are using the Micron model, ensure to add the include directory for it to the design. This is done in the Tcl console using the following command:

```

set_property INCLUDE_DIRS [get_property DIRECTORY [current_project]]/../testbench/

Micron_N25Q128A13E [get_filesets sim_1]

```

#### 2.5.2 Cypress QSPI model

The Cypress (Spansion) QSPI device used on the V2C-DAPLink board is S25f1128S.

A Verilog simulation model for this device is available at the Cypress website.

The archive file that you must download is s25f1128s.zip. This archive is a self-installing executable. Run the executable, and extract the files to the V:/hardware/m3\_for\_arty\_a7/testbench directory. This copies the model files to a folder called /S25f1128s in this location.

# 2.6 Configuring simulation in Vivado

To configure simulations in Vivado, you must have either the Vivado or a third-party simulator installed. The paths to the simulator must be configured in Vivado.

To configure the paths to the simulator in Vivado, navigate to Tools  $\rightarrow$  Settings  $\rightarrow$  Tool Settings  $\rightarrow$  3rd Party simulators.

#### Prerequisites

- 2.1 Installing board files on page 2-15.

- 2.2 Setting local drive for Windows on page 2-17.

- 2.3 Installing Arm IP repository on page 2-18.

- 2.4 Installing Arm software repository on page 2-19.

- 2.5 Downloading QSPI memory models on page 2-21.

# Chapter 3 Cortex<sup>®</sup>-M3 processor IP configuration

After installing the Arm *IP Integrator* (IPI) repository, you can find the Cortex-M3 processor package in the Vivado IP catalog.

This package is a version of Cortex-M3 r2p1 processor with debug and two BP136 AHB to AXI bridges r0p1 pre-integrated.

See the Cortex®-M3 Technical Reference Manual for a detailed description of the processor.

This chapter describes the four Cortex-M3 processor IP configuration tabs, each with details on individual configuration categories.

—— Note

For more information about the Cortex-M3 processor configuration options, see, the *Configurable options* section in the *Cortex*<sup>®</sup>-M3 Technical Reference Manual.

It contains the following sections:

- 3.1 Configuration tab on page 3-25.

- *3.2 Debug tab* on page 3-27.

- 3.3 Instruction Memory tab on page 3-29.

- *3.4 Data Memory tab* on page 3-31.

- 3.5 Cortex<sup>®</sup>-M3 processor signals on page 3-33.

# 3.1 Configuration tab

The following figure shows the configuration tab.

| 🝌 Re-customize IP                                                                                                                                                                                                                                                              |                                                                                                                                                                            | ×     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Cortex-M3 (1.0)                                                                                                                                                                                                                                                                |                                                                                                                                                                            | 4     |

| Documentation Documentation                                                                                                                                                                                                                                                    |                                                                                                                                                                            |       |

| Show disabled ports                                                                                                                                                                                                                                                            | Component Name Cortex_M3_0                                                                                                                                                 |       |

| CMD_SYS_AXD +<br>HCLK CMD_CODE_AXD +<br>SYSRESET# SYSRESETRED<br>IRQISSO DBGRESTARTED<br>NMI LOCKUP<br>CFGTCMEN[10] HALTED<br>DBGRESET# JTAGTOP<br>EDBGRO SWDO<br>STCLK SWDOEN<br>STCLK SWDOEN<br>STCLK SWDOEN<br>STCLK TCC<br>WDTWS #TDOEN<br>WDTWS #TDOEN<br>TDI TRACEDATADJ | ConfigurationDebugInstruction MemoryData MemoryNumber of Interrupts (Auto)8[0 - 240]IRQ Priority level width33MPU PresentWIC PresentWIC Lines3[3 - 243]Bit-banding Present |       |

|                                                                                                                                                                                                                                                                                | ОК Са                                                                                                                                                                      | ancel |

#### Figure 3-1 Configuration tab

In this tab, you can select the following:

#### Number of interrupts

This indicates the number of interrupt sources the Cortex-M3 processor supports. The Cortex-M3 processor can support up to 240 interrupt sources.

The width of the signals connected to the IRQ port automatically determines the number of interrupts. This implies that you cannot set the value directly. To update the width of the IRQ port, connect the required number of signals to the IRQ port. You can then validate the block diagram. This updates the IRQ port width, and the configuration tab with the new value.

—— Note –

Increasing the number of interrupts or the number of priority levels affects the maximum synthesis frequency.

#### **IRQ** Priority level width

This determines the number of IRQ priority levels and is equal to  $2^{\text{Priority level width}}$ . The range is 3-8, with a default value of 3, that is, eight priority levels.

#### **MPU Present**

Enable the Memory Protection Unit (MPU) in the Cortex-M3 core.

#### WIC Present

Enable the Wake-up Interrupt Controller (WIC) in the Cortex-M3 core.

#### WIC Lines

Determine the number of internal priority lines used for the WIC. This value can only be changed if the WIC present is enabled.

#### Bit banding present

Enable bit-banding in the Cortex-M3 core.

For more information on these options, see the Cortex®-M3 Technical Reference Manual.

# 3.2 Debug tab

The following figure shows the Debug tab.

| 🍌 Re-customize IP                                                                                                                                                                                                                                                                                     |                                                                                                                           |                                                                                                            | ×           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------|

| Cortex-M3 (1.0)                                                                                                                                                                                                                                                                                       |                                                                                                                           |                                                                                                            | 4           |

| 🚺 Documentation 🛛 🗁 IP Location                                                                                                                                                                                                                                                                       |                                                                                                                           |                                                                                                            |             |

| Show disabled ports                                                                                                                                                                                                                                                                                   | Component Name                                                                                                            | tex_M3_0                                                                                                   |             |

|                                                                                                                                                                                                                                                                                                       | Configuration Debu                                                                                                        | Instruction Memory                                                                                         | Data Memory |

| CW3_GYG_AXIS<br>CW3_GYG_AXIS<br>*CLK CW3_CODE_AXIS<br>SYSRESETN SYSRESETRED<br>HOU<br>CRATCHENTON<br>CRATCHENTON<br>DBORESTN JTACHSW<br>DBORESTN JTACHSW<br>DBORESTN JTACHSW<br>DBORESTN JTACHSW<br>DBORESTN JTACHSW<br>DBORESTN JTACHSW<br>SWDCHTCK TDO<br>SWDDITUS NTDOEN<br>NTDOEN<br>TRACELATAIJS | <ul> <li>2 = Full debu</li> <li>3 = Full debu</li> <li>Trace Level</li> <li>0 = No trace</li> <li>1 = Standard</li> </ul> | kpoint, one watchpoint<br>g minus DWT<br>g including DWT<br>trace. ITM & DWT. No ETI<br>. ITM, DWT and ETM | Ν           |

|                                                                                                                                                                                                                                                                                                       |                                                                                                                           |                                                                                                            | OK Cancel   |

#### Figure 3-2 Configuration tab

On this tab you can select the following:

#### **Debug level**

This enables you to set the level of debug supported.

#### — Note —

If this field is set to 0=No debug, the resulting build does not support the V2C-DAPLink board and it is not possible to drag and drop software to the V2C-DAPLink board.

#### **Trace level**

This enables you to set the level of debug trace that is supported, that is, from no trace to full trace.

If the Debug level is set to 0=No debug, the Trace level is automatically set to 0. If the Debug level is set to any other value, then you must reset the Trace level to the required value.

#### **JTAG Present**

When enabled, the debug port can be accessed using the Cortex-M3 JTAG pins.

#### \_\_\_\_\_ Note --

The debug port supports Serial Wire (SW) interface by default.

For more information on these options, see the Cortex®-M3 Technical Reference Manual.

# 3.3 Instruction Memory tab

The following figure shows the Instruction Memory tab.

| 🝌 Re-customize IP                                                                                                                                                                                                                                                                                                                          |                         |                        |             | ×      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------|-------------|--------|

| Cortex-M3 (1.0)                                                                                                                                                                                                                                                                                                                            |                         |                        |             | 4      |

| 🕖 Documentation 🛛 🗁 IP Location                                                                                                                                                                                                                                                                                                            |                         |                        |             |        |

| Show disabled ports                                                                                                                                                                                                                                                                                                                        | Component Name          | Cortex_M3_0            |             |        |

|                                                                                                                                                                                                                                                                                                                                            | Configuration Del       | bug Instruction Memory | Data Memory |        |

|                                                                                                                                                                                                                                                                                                                                            | ITCM Size               | 64kB 🗸                 |             |        |

|                                                                                                                                                                                                                                                                                                                                            | ✓ Initialise ITCM       |                        |             |        |

| CV1_SYS_AXIS<br>HCLK CV1_CODE_AXIS<br>SYSRESETN SYSRESETRO<br>IRC(15:8) DBGRESTARTED<br>HVI LOCKUP<br>CROTCUEN(18) HALTED<br>DBGRESETN JTAGRSW<br>DBGRESETN JTAGRSW<br>DBGRESETN JTAGRSW<br>DBGRESETN JTAGRSW<br>DBGRESETN JTAGRSW<br>DBGRESETN JTAGRSW<br>SWOCKTCK TO<br>SWOTUS NTDOEH<br>SWOLKTCK TO<br>SWOTUS NTDOEH<br>TRACEDATA(13:8) | ITCM Initialisation fil | e bram_a7.hex 🕲        |             |        |

|                                                                                                                                                                                                                                                                                                                                            |                         |                        | ОК          | Cancel |

#### Figure 3-3 Instruction Memory tab

On this tab you can select the following:

#### **ITCM Size**

The range is 8KB to 1MB. Select the optimal size for your code base.

- —— Note ——

- Currently the flow to update a bitstream with new *Instruction Tightly Coupled Memory* (ITCM) data only supports memory sizes in the range 16KB to 128KB. If you require sizes outside that range, contact Arm for support. For more information on this flow, see *Software Update flow* on page 6-78.

#### Initialize ITCM

If you require the instruction memory to be initialized when the design is built:

- 1. Select Initialize ITCM.

- 2. Specify the filename, see the example design as a reference.

— Note —

- The filename must not have quote marks around it.

- The filename must be added to the design and marked as a memory initialization file.

- Vivado reads the memory file during synthesis. It is not possible to update the memory file and to run just implementation or generate bitstream. To incorporate software updates into an existing bit file, see *Software Update flow* on page 6-78.

ITCM aliasing is controlled at reset by the state of the **CFGITCMEN[1:0]** signal. For more information on **CFGITCMEN[1:0]**, see the The upper and lower aliases can be enabled independently, that is, either one alias, both aliases, or none of the aliases. For more information about processor memory regions, see the *Cortex*\*-*M3 Technical Reference Manual*.

To boot the processor from ITCM, you must:

- 1. Enable ITCM lower alias.

- 2. Initialize the ITCM.

If the processor does not boot from ITCM, you must provide memory at address 0x00000000 on the external AXI interface which contains the initial stack pointer and vector table.

Instruction fetch latency is lower from ITCM than from the AXI interface. If you boot from AXI memory, you can copy code to ITCM at the upper alias and then execute from there to get better performance.

# 3.4 Data Memory tab

The following figure shows the data memory tab.

| 🝌 Re-customize IP                                                                                                                                                                                                                                                                                                    |                   |           |                    |             | ×      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------|--------------------|-------------|--------|

| Cortex-M3 (1.0)                                                                                                                                                                                                                                                                                                      |                   |           |                    |             | 4      |

| Ocumentation IP Location                                                                                                                                                                                                                                                                                             |                   |           |                    |             |        |

| Show disabled ports                                                                                                                                                                                                                                                                                                  | Component Name    | e Cortex  | (_M3_0             |             |        |

|                                                                                                                                                                                                                                                                                                                      | Configuration     | Debug     | Instruction Memory | Data Memory |        |

|                                                                                                                                                                                                                                                                                                                      | DTCM Size         |           | 64kB v             |             |        |

|                                                                                                                                                                                                                                                                                                                      | Initialise DT     | СМ        |                    |             |        |

| CW1_SYS_AXI3 +<br>*CLK CW1_CODE_AXI3 +<br>SYSRESETN SYSRESETRED<br>IRC(154) DBORESTARTED<br>WW1 LOCKUP<br>CROTCMEN[10] *ALTED<br>DBORESETN JTAGHSW<br>DBORESTART JTAGHSW<br>DBORESTART JTAGHSW<br>SWCLATCK SWDOEN<br>SWCLATCK TDO<br>SWDUWS PTODEN<br>WDUWS PTODEN<br>TRIST TRICENA<br>TOI TRICECK<br>TRACEDATA(150) | DTCM Initialisati | on File [ |                    |             |        |

|                                                                                                                                                                                                                                                                                                                      |                   |           |                    | ОК          | Cancel |

#### Figure 3-4 Data Memory tab

### DTCM size

The range is 2KB to 1MB. Select the optimal size for your code base.

#### Initialize DTCM

If you require the data memory to be initialized when the design is built:

- 1. Select Initialize DTCM checkbox.

- 2. Specify the filename, see the example design as a reference.

— Note –

- The filename must not have quote marks around it.

- The filename must be added to the design and marked as a memory initialization file.

- Vivado reads the memory file during synthesis. It is not possible to update the memory file and to run just implementation or generate bitstream. To incorporate software updates into an existing bit file, see *6.6 Software update flow* on page 6-78.

# 3.5 Cortex<sup>®</sup>-M3 processor signals

For details of the Cortex-M3 signals, see the *Signal descriptions* appendix in the *Cortex®-M3 Technical Reference Manual*.

The three external AHB-Lite interfaces are not exported, and the two AXI interfaces replaces them. For more information, see *Figure 1-1 Internal memory processing* on page 1-13.

The AHB-AP interface is not exported, it is replaced by the *Serial Wire* (SW) or JTAG interface pins that are described in the *Arm*<sup>®</sup> *CoreSight*<sup>™</sup> *SoC-400 Technical Reference Manual*.

### CFGITCMEN[1:0]

This input signal is the *Instruction Tightly Coupled Memory* (ITCM) alias enable. Bit [1] sets the upper alias enable line and bit [0] sets the lower alias enable line. The value of this signal must be held constant for at least two cycles before SYSRESETn is deasserted.

If **CFGITCMEN[1]** is set, then the internal RAM ITCM is mapped to the upper address alias in the memory map.

If **CFGITCMEN[0]** is set, then the internal RAM ITCM is mapped to the lower address alias in the memory map.

Processor instruction fetches that are to memory addresses that are not aliased to the ITCM is output on the CM3\_CODE\_AXI3 port.

For more information, see Figure 1-1 Internal memory processing on page 1-13.

# Chapter 4 Working with the Cortex<sup>®</sup>-M3 DesignStart<sup>™</sup> example design

This chapter describes how to work with an example design targeting a low-cost evaluation board, Digilent Arty *Artix 7* (A7). This example design is provided to demonstrate the integration and software development using the Cortex-M3 processor. The example is based on the Digilent Arty A7-35T board, and uses some of the standard Xilinx peripherals to connect to some of the features on the board. The example is intended to show typical usage, rather than a completely minimal Cortex-M3 processor design.

The board provides the Digilent Pmod<sup>™</sup> peripheral module headers for peripherals, and shield expansion headers to support additional expansion. You can use the optional Arm V2C-DAPLink board with these headers to use Cortex-M3 for easy debug and software development. If you do not use the V2C-DAPLink board, you can still connect a *Serial Wire Debug* (SWD) probe (Arm Keil<sup>®</sup> ULINK<sup>™</sup> or similar) to J4 (**nSRST** on **I/O[39**], **SWDIO** on **I/O[40**], and **SWCLK** on **I/O[41**]).

Some features of the example design detect the presence of the V2C-DAPLink board, and adapt accordingly. The V2C-DAPLink board includes pass-through headers for an additional shield board to be connected on top.

The block diagram of the design is available in /docs/m3\_for\_arty\_a7\_example\_design.pdf.

The example design has the following functions:

- UART to output to either the Arty onboard USB connector, or the V2C-DAPLink board, when fitted.

- GPIO\_0 connected to the four DIP switches, SW[3:0], and the four green LEDs LD[7:4].

- GPIO\_1 connected to the four push button switches, BTN[3:0], and the four multicolor LEDs.

- QSPI\_0 connected to the Arty on-board *Quad Serial Port Interface* (QSPI) flash memory.

- BRAM ctrl 0 connected to 64KB of internal FPGA BRAM.

The following peripherals are connected to the V2C-DAPLink adaptor board using J4.

- QSPI 1 connected to the adaptor board QSPI flash memory.

- SPI 0 connected to the adaptor board SD card memory.

A number of pre-built files are provided with the example design. For more information, see *6.3 Example design reference files* on page 6-70.

The example design files are modified by the Vivado tool when you open the design, so it might be useful to copy the /hardware directory before working with it. For more information on the directory structure, see *1.2 Directory structure* on page 1-12.

It contains the following sections:

- 4.1 Editing the A7 example design on page 4-36.

- *4.2 Debug* on page 4-37.

– Note -

- *4.3 Memory map* on page 4-38.

- 4.4 QSPI multiplexing for the V2C-DAPLink board on page 4-41.

- *4.5 Interrupt mapping* on page 4-42.

- 4.6 Constraints on page 4-43.

- 4.7 Loading the pre-built bitstream on page 4-44.

- *4.8 Loading the flash file* on page 4-45.

- *4.9 Bit file regeneration* on page 4-47.

- 4.10 Simulation on page 4-48.

# 4.1 Editing the A7 example design

When loading the Arty Artix 7 (A7) example design for the first time, if warning messages are issued about either missing IP blocks (Cortex-M3 processor) or board files (Digilent board files), then the design must be closed and the instructions for installation of the IP repository and Digilent board files must be followed. For more information on these installations, see Chapter 2 Installing the Cortex\*-M3 DesignStart\*\* example design on page 2-14. In this scenario, it is possible that Vivado has modified the design file. Therefore, after correct installation of the IP repository and board files is complete, the original design must be installed from the archive.

### Procedure

1. Open Vivado.

- Note

- 2. Select *Open Project* on the splash screen, and select /hardware/m3\_for\_arty\_a7/m3\_for\_arty\_a7/m3\_for\_arty\_a7.xpr.

- 3. In the sources tab, navigate down the hierarchy to the m3\_for\_arty\_a7\_i instance, marked with a block diagram symbol. Double-clicking this opens the block diagram that is shown in /docs/m3\_for\_arty\_a7\_example\_design.pdf.

- 4. The design can now be navigated to understand the connectivity and configuration. Double-clicking on any of the IP blocks brings up the configuration for that block.

If you want to change the memory map, this is done in the address editor. However, you must not modify the addresses of the V2C-DAPLink interface peripherals. Additionally, the example hardware memory map matches the pre-compiled software memory map. Therefore, if other peripheral addresses are modified, the equivalent changes must be made in the software.

# 4.2 Debug

The example design uses *Serial Wire Debug* (SWD). There is no dedicated Arm debug connector on the Arty *Artix 7* (A7) board, therefore, SWD is only connected to the expansion connector. When the V2C-DAPLink adaptor board is fitted, the SWD ports are connected directly to this board and are accessible through the USB connector as part of the V2C-DAPLink interface.

To use JTAG debug, you must use a suitable debug probe, and route the JTAG connections to the expansion headers.

The example design does not connect to the trace interface. To use trace, you must route the TRACEPORT connections to the expansion headers and use a suitable trace capture device.

# 4.3 Memory map

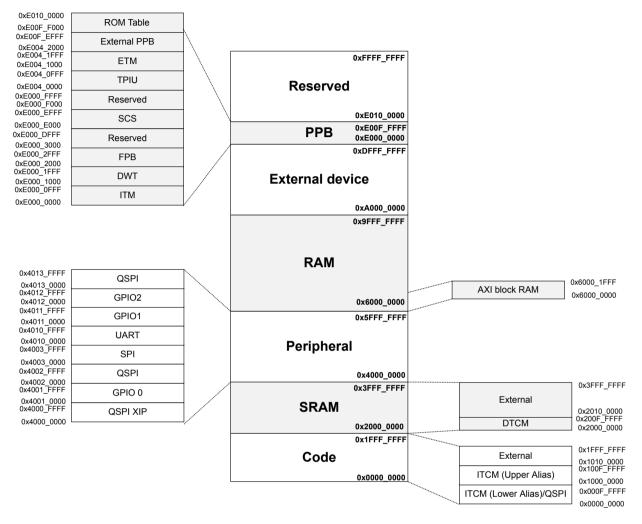

The following figure shows the memory map of the example Cortex-M3 DesignStart FPGA-Xilinx edition system.

#### Figure 4-1 Example system memory map

The following table shows the example Cortex-M3 DesignStart FPGA-Xilinx edition memory map.

#### Table 4-1 Example system memory map

| Туре       | Start      | End        | Peripheral                                              | Instance name                                  | Size         | Comment                                                                                                               |

|------------|------------|------------|---------------------------------------------------------|------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------|

| Code       | 0×00000000 | 0x000FFFF  | Instruction Tightly<br>Coupled Memory<br>(ITCM) (lower) | Integrated in the Cortex-<br>M3 processor.     | Configurable | Boot region when<br><b>CFGITCMEN[0]</b> is 1.<br>This indicates that there<br>is no V2C-DAPLink<br>board.             |

|            | 0×0000000  | 0x000FFFFF | Quad Serial<br>Peripheral<br>Interface (QSPI)           | daplink_if_0/axi-<br>_xip_quad_0               | 1MB          | Boot region when<br><b>CFGITCMEN[0]</b> is 0.<br>This indicates that there<br>is a V2C-DAPLink<br>board. <sup>a</sup> |

|            | 0x10000000 | 0x100FFFFF | ITCM (upper)                                            | Integrated in the Cortex-<br>M3 processor.     | 1MB          | Upper ITCM alias,<br><b>CFGITCMEN[1]</b> is<br>always HIGH in the<br>example design.                                  |

|            | 0x10100000 | 0x1FFFFFFF | External                                                | -                                              | -            | -                                                                                                                     |

| SRAM       | 0x20000000 | 0x200FFFFF | Data Tightly<br>Coupled Memory<br>(DTCM)                | Integrated in the Cortex-<br>M3 processor.     | Configurable | eXecute-never (XN)<br>region                                                                                          |

|            | 0x20100000 | 0x3FFFFFFF | External                                                | -                                              | -            | -                                                                                                                     |

| Peripheral | 0x40000000 | 0x4000FFFF | QSPI eXecute In<br>Place (XIP)                          | daplink_if_0/axi-<br>_xip_quad_0               | 64KB         | Provides code execution<br>from QSPI on the V2C-<br>DAPLink board. <sup>a</sup>                                       |

|            | 0x40010000 | 0x4001FFFF | GPIO 0                                                  | daplink_if_0/<br>axi_gpio_0                    | 64KB         | Control for QSPI<br>peripheral multiplexer.<br>Bit [0] selects between<br>the two QSPI<br>peripherals. <sup>a</sup>   |

|            | 0x40020000 | 0x4002FFFF | QSPI                                                    | daplink_if_0/<br>quad_spi_0                    | 64KB         | Provides programming<br>control from QSPI on the<br>V2C-DAPLink board. <sup>a</sup>                                   |

|            | 0x40030000 | 0x4003FFFF | SPI                                                     | <pre>daplink_if_0/axi-<br/>_single_spi_0</pre> | 64KB         | Single SPI on a dedicated connector.                                                                                  |

|            | 0x40040000 | 0x400FFFFF | Unused                                                  | -                                              | -            | Unused peripheral region                                                                                              |

|            | 0x40100000 | 0x4010FFFF | UART                                                    | axi_uartlite_0                                 | 64KB         | Baseboard UART or<br>V2C-DAPLink USB,<br>when fitted.                                                                 |

|            | 0x40110000 | 0x4011FFFF | GPIO 1                                                  | axi_gpio_0                                     | 64KB         | -                                                                                                                     |

|            | 0x40120000 | 0x4012FFFF | GPIO 2                                                  | axi_gpio_1                                     | 64KB         | -                                                                                                                     |

|            | 0x40130000 | 0x4013FFFF | QSPI                                                    | axi_quad_spi_0                                 | 64KB         | Provides read/write<br>access to QSPI on V2C-<br>DAPLink board. <sup>a</sup>                                          |

|            | 0x40140000 | 0x5FFFFFFF | Unused                                                  | -                                              | -            | Unused peripheral region.                                                                                             |

<sup>&</sup>lt;sup>a</sup> The V2C-DAPLink firmware uses this region. Therefore, you must not modify it to retain compatibility with the V2C-DAPLink board.

#### Table 4-1 Example system memory map (continued)

| Туре            | Start      | End        | Peripheral                                  | Instance name                              | Size | Comment                                                                                    |

|-----------------|------------|------------|---------------------------------------------|--------------------------------------------|------|--------------------------------------------------------------------------------------------|

| RAM             | 0x60000000 | 0x60001FFF | BlockRam                                    | axi_bram_ctrl_0                            | 8KB  | Additional area of RAM.<br>This also supports code<br>execution. <sup>a</sup>              |

|                 | 0x60002000 | 0x9FFFFFFF | Unused                                      | -                                          | -    | Unused RAM region.                                                                         |

| External device | 0xA0000000 | ØxDFFFFFFF | Unused                                      | -                                          | -    | Unused external device region.                                                             |

| System          | 0×E0000000 | 0xE0000FFF | Instrumentation<br>Trace Macrocell<br>(ITM) | Integrated in the Cortex-<br>M3 processor. | 4КВ  | -                                                                                          |

|                 | 0xE0001000 | 0xE0001FFF | Data Watchpoint<br>and Trace (DWT)          | Integrated in the Cortex-<br>M3 processor. | 4KB  | -                                                                                          |

|                 | 0xE0002000 | 0xE0002FFF | Flashpatch and<br>Breakpoint (FPB)          | Integrated in the Cortex-<br>M3 processor. | 4KB  |                                                                                            |

|                 | 0xE0003000 | 0xE000DFFF | Reserved                                    | -                                          | -    | -                                                                                          |

|                 | 0xE000E000 | 0xE000EFFF | System Control<br>Space (SCS)               | Integrated in the Cortex-<br>M3 processor. | 4KB  | Nested Vectored Interrupt<br>Controller (NVIC),<br>Debug, and system<br>control registers. |

|                 | 0xE000F000 | 0xE003FFFF | Reserved                                    | -                                          | -    | -                                                                                          |

|                 | 0×E0040000 | 0xE0040FFF | Trace Port<br>Interface Unit<br>(TPIU)      | Integrated in the Cortex-<br>M3 processor. | 4КВ  | -                                                                                          |

|                 | 0xE0041000 | 0xE0041FFF | Embedded Trace<br>Macrocell (ETM)           | Integrated in the Cortex-<br>M3 processor. | 4KB  |                                                                                            |

|                 | 0xE0042000 | 0xE00FEFFF | External PPB                                | -                                          | -    |                                                                                            |

|                 | 0xE00FF000 | 0xE0100000 | ROM table                                   | Integrated in the Cortex-<br>M3 processor. | 4KB  |                                                                                            |

| Reserved        | 0xE0100000 | 0xFFFFFFFF | -                                           | -                                          | -    | -                                                                                          |

All the AXI peripherals that are detailed in the example design are mapped to either of the following:

- Peripheral region (0x4000000 to 0x5FFFFFF).

- SRAM region (0x6000000 to 0x9FFFFFF) in the case of the block RAM controller.

If the V2C-DAPLink board is not fitted, then the ITCM RAM, implemented in FPGA memory, is mapped to both 0x00000000 and 0x10000000. Code that is preloaded into the ITCM RAM is executed from address 0x00000000 from boot-up.

If the V2C-DAPLink board is fitted, then the ITCM RAM is only mapped to 0x10000000. For code execution, the V2C-DAPLink board contains a QSPI AXI peripheral configured to *eXecute In Place* (XIP) mode. This peripheral is named qspi\_xip and is mapped to address 0x00000000. Code is executed from this XIP QSPI device on boot-up.

The DTCM is always mapped starting at 0x20000000. In contrast to other Cortex-M processors, which do not have a TCM, the DTCM is XN.

# 4.4 QSPI multiplexing for the V2C-DAPLink board

The *Quad Serial Port Interface* (QSPI) device, that is fitted to the V2C-DAPLink board, has two Xilinx QSPI AXI controllers. A single GPIO signal from a GPIO peripheral can select one of the two controllers to use. One of the controllers is configured in *eXecute In Place* (XIP) mode, the other controller is configured in normal mode, which is required to write to the memory device.

For more information on the peripherals and their memory map, see *Table 5-1 Interface type* on page 5-53

— Caution ——

If software is intended to be run from the V2C-DAPLink board, then the software must not switch the GPIO signal across to the controller in normal mode. If this happened, then the processor can no longer read the code and the processor enters LOCKUP state.

# 4.5 Interrupt mapping

The following table shows the interrupts that the example system uses.

#### Table 4-2 Example system interrupts

| Number | Name              | Description                                                 |

|--------|-------------------|-------------------------------------------------------------|

| 0      | UART0_IRQn        | UART 0 interrupt                                            |

| 1      | GPIO0_IRQn        | GPIO 0 interrupt                                            |

| 2      | GPIO1_IRQn        | GPIO 1 interrupt                                            |

| 3      | QSPI0_IRQn        | Quad Serial Port Interface (QSPI) 0, (Arty board) interrupt |

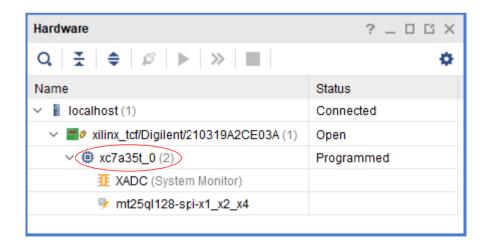

| 4      | DAP_QSPI0_IRQn    | V2C-DAPLink board QSPI 0 interrupt                          |