# Arm<sup>®</sup> CoreLink<sup>™</sup> SSE-200 Subsystem for Embedded

Revision: r1p0

**Technical Reference Manual**

# Arm® CoreLink™ SSE-200 Subsystem for Embedded

# **Technical Reference Manual**

Copyright © 2016, 2017 Arm Limited (or its affiliates). All rights reserved.

# **Release Information**

# **Document History**

| Issue   | Date              | Confidentiality  | fidentiality Change                        |  |

|---------|-------------------|------------------|--------------------------------------------|--|

| A       | 20 December 2016  | Confidential     | First release for r0p0 Beta (ARM DDI0574). |  |

| 0100-00 | 26 September 2017 | Non-Confidential | First release for r1p0 EAC (ARM 101104).   |  |

# **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or TM are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at <a href="http://www.arm.com/company/policies/trademarks">http://www.arm.com/company/policies/trademarks</a>.

Copyright © 2016, 2017 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

# **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

# **Product Status**

The information in this document is Final, that is for a developed product.

# Web Address

http://www.arm.com

# Contents

# **Arm® CoreLink™ SSE-200 Subsystem for Embedded Technical Reference Manual**

|           | Preta | ace                           |      |

|-----------|-------|-------------------------------|------|

|           |       | About this book               | 7    |

|           |       | Feedback                      | 10   |

| Chapter 1 | Intro | oduction                      |      |

|           | 1.1   | About the SSE-200             | 1-12 |

|           | 1.2   | Features of the SSE-200       | 1-14 |

|           | 1.3   | CoreLink SIE-200 components   | 1-15 |

|           | 1.4   | Compliance                    | 1-16 |

|           | 1.5   | Product revisions             | 1-17 |

| Chapter 2 | Fund  | ctional description           |      |

|           | 2.1   | Top-level system partitioning | 2-19 |

|           | 2.2   | Clocks                        | 2-22 |

|           | 2.3   | Resets                        | 2-27 |

|           | 2.4   | CPU elements                  | 2-32 |

|           | 2.5   | Base element                  | 2-43 |

|           | 2.6   | SRAM elements                 | 2-49 |

|           | 2.7   | System control element        | 2-50 |

|           | 2.8   | Debug element                 | 2-52 |

|           | 2.9   | Power control infrastructure  | 2-59 |

|           | 2.10  | Crypto element                | 2-70 |

| Chapter 3  | Prog | grammers Model                          |            |

|------------|------|-----------------------------------------|------------|

|            | 3.1  | About the programmers model             | 3-73       |

|            | 3.2  | Memory map                              | 3-74       |

|            | 3.3  | CPU element                             | 3-82       |

|            | 3.4  | Base element                            | 3-92       |

|            | 3.5  | SRAM element                            | 3-121      |

|            | 3.6  | System control element                  | 3-122      |

|            | 3.7  | Debug and trace                         | 3-142      |

| Appendix A | Sign | nal Descriptions                        |            |

|            | A.1  | Clock, reset, and power control signals | Appx-A-146 |

|            | A.2  | Interrupt signals                       | Appx-A-152 |

|            | A.3  | AHB expansion bus signals               |            |

|            | A.4  | Debug and Trace signals                 | Appx-A-157 |

|            | A.5  | Security component interfaces           | Appx-A-161 |

|            | A.6  | Miscellaneous top-level signals         | Appx-A-165 |

|            | A.7  | CryptoCell-312 signals                  | Appx-A-168 |

|            | A.8  | Top-level parameters                    | Appx-A-170 |

|            | A.9  | Top-level render time configurations    | Appx-A-175 |

| Appendix B | Rev  | isions                                  |            |

|            | B.1  | Revisions                               | Appx-B-178 |

# **Preface**

This preface introduces the  $Arm^*$   $CoreLink^{**}$  SSE-200 Subsystem for Embedded Technical Reference Manual.

It contains the following:

- About this book on page 7.

- Feedback on page 10.

# About this book

This book is for the Arm® CoreLink™SSE-200 Subsystem for Embedded (SSE-200). It provides a high-level overview of the SSE-200. It describes architectural information, and as such, facilitates the creation of software or a SoC targeted at an Internet of Things (IoT) application.

# Product revision status

The rmpn identifier indicates the revision status of the product described in this book, for example, r1p2, where:

- rm Identifies the major revision of the product, for example, r1.

- pn Identifies the minor revision or modification status of the product, for example, p2.

# Intended audience

This book is written for system designers, system integrators, and programmers who are designing or programming a System-on-Chip (SoC) that uses the SSE-200.

# Using this book

This book is organized into the following chapters:

# **Chapter 1 Introduction**

This chapter introduces the SSE-200.

# Chapter 2 Functional description

This chapter describes the functionality of the SSE-200.

# **Chapter 3 Programmers Model**

This chapter describes the SSE-200 memory regions and registers, and provides information on how to program a SoC that contains an implementation of the SSE-200.

# Appendix A Signal Descriptions

This appendix summarizes the interface signals present in the SSE-200 elements.

# Appendix B Revisions

This appendix describes the technical changes between released issues of this book.

# Glossary

The Arm® Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

See the Arm® Glossary for more information.

# Typographic conventions

italic

Introduces special terminology, denotes cross-references, and citations.

# bold

Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.

# monospace

Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.

# monospace

Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.

# monospace italic

Denotes arguments to monospace text where the argument is to be replaced by a specific value.

### monospace bold

Denotes language keywords when used outside example code.

<and>

Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:

```

MRC p15, 0, <Rd>, <CRn>, <CRm>, <Opcode_2>

```

SMALL CAPITALS

Used in body text for a few terms that have specific technical meanings, that are defined in the *Arm*<sup>®</sup> *Glossary*. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE.

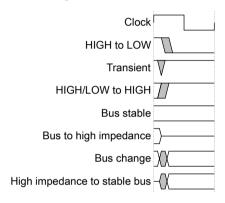

# **Timing diagrams**

The following figure explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

Figure 1 Key to timing diagram conventions

# **Signals**

The signal conventions are:

# Signal level

The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals.

- LOW for active-LOW signals.

# Lowercase n

At the start or end of a signal name denotes an active-LOW signal.

# **Additional reading**

This book contains information that is specific to this product. See the following documents for other relevant information.

# **Arm publications**

- Arm<sup>®</sup> CoreLink<sup>™</sup> SSE-200 Subsystem for Embedded Technical Reference Manual (Arm 101104)

- Arm® CoreLink™ SIE-200 System IP for Embedded Technical Reference Manual (Arm DDI 0571).

- Arm® Cortex®-M System Design Kit Technical Reference Manual (Arm DDI 0479).

- Arm® Cortex®-M33 Processor Technical Reference Manual (Arm 100230).

- Arm® Cortex®-M33 Processor User Guide Reference Material (Arm 100234).

The following confidential books are only available to licensees or require registration with ARM:

- Arm® CoreLink™ SSE-200 Subsystem for Embedded Configuration and Integration Manual (Arm 100224).

- Arm® CoreLink™ SSE-200 Subsystem for Embedded Release Note (Arm EPM-135617).

- Arm®v7-M Architecture Reference Manual (Arm DDI 0403).

- Arm®v8-M Architecture Reference Manual (Arm DDI 0553).

- Arm® Cortex®-M33 Processor Integration and Implementation Manual (Arm 100323).

- Arm<sup>®</sup> CoreSight<sup>™</sup> Components Technical Reference Manual (Arm DDI 0314).

- AMBA® Low Power Interface Specification, Arm® Q-Channel and P-Channel Interfaces (Arm IHI 0068).

- Arm® Power Policy Unit Architecture Specification, version 1.1 (Arm DEN 0051).

- Arm® Debug Interface Architecture Specification ADIv5.0 to ADIv5.2 (Arm IHI 0031).

- Arm® Embedded Trace Macrocell (ETMv4) Architecture Specification (Arm IHI 0064).

- Arm® AMBA® 5 AHB Protocol Specification (Arm IHI 0033).

- Arm® AMBA® APB Protocol Specification Version 2.0 (Arm IHI 0024).

- Arm<sup>®</sup> TrustZone<sup>®</sup> CryptoCell-312 Technical Reference Manual (ARM 100774).

# Other publications

None.

# **Feedback**

# Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

# Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- The title Arm CoreLink SSE-200 Subsystem for Embedded Technical Reference Manual.

- The number 101104 0100 00 en.

- If applicable, the page number(s) to which your comments refer.

- A concise explanation of your comments.

| Arm also welcomes general suggestions for additions and improvements.                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note                                                                                                                                                          |

| Arm tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader. |

# Chapter 1 **Introduction**

This chapter introduces the SSE-200.

It contains the following sections:

- 1.1 About the SSE-200 on page 1-12.

- 1.2 Features of the SSE-200 on page 1-14.

- 1.3 CoreLink SIE-200 components on page 1-15.

- 1.4 Compliance on page 1-16.

- 1.5 Product revisions on page 1-17.

# 1.1 About the SSE-200

The Arm CoreLink SSE-200 Subsystem for Embedded is a collection of pre-assembled elements to use as the basis of an *Internet of Things* (IoT) *System on Chip* (SoC).

It is complemented by software libraries that are integrated with the Mbed™ operating system. The SSE-200 is part of the CoreLink SDK-200 System Design Kit (SDK-200) which also contains the CoreLink SIE-200 System IP for Embedded product and other components. The SDK-200 provides components to quickly create systems that are based on Cortex-M processors.

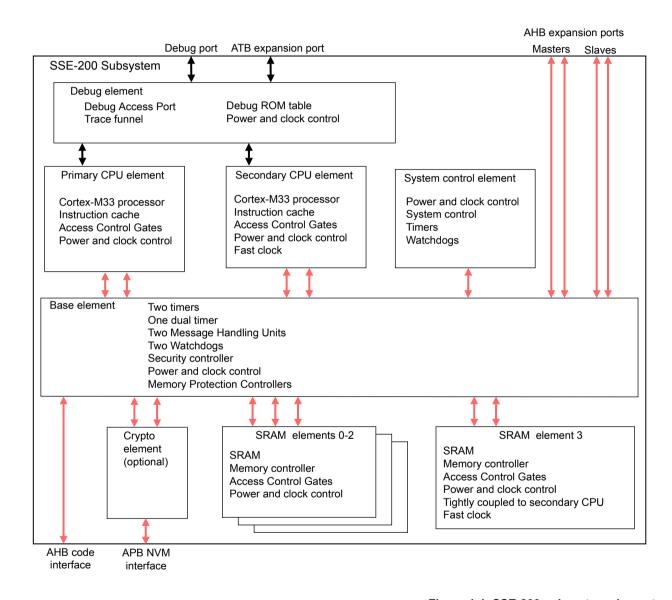

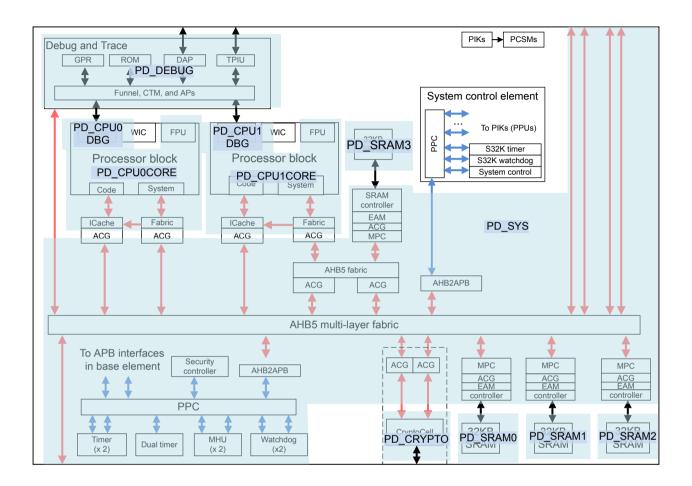

The following figure shows the major blocks present in the SSE-200.

Figure 1-1 SSE-200 subsystem elements

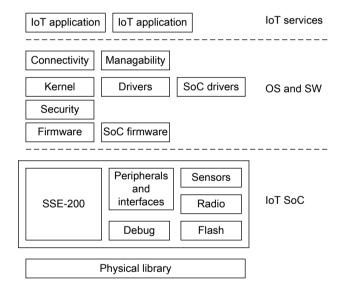

# 1.1.1 About IoT System on Chip implementations

The SSE-200 subsystem must be extended to create an IoT SoC. A complete system typically contains the following components:

# **Compute subsystem**

The compute subsystem consists of two Cortex-M33 processors and associated bus, debug, controller, peripherals, and interface logic supplied by Arm.

# Reference system memory and peripherals

SRAM is part of the SSE-200, but a SoC requires extra memory, control, and peripheral components beyond the minimum subsystem components. Flash memory, for example, is not provided with the SSE-200.

# **Communication interface**

The endpoint must have some way of communicating with other nodes or masters in the system. This interface could be WiFi, Bluetooth, or a wired connection.

# Sensor or control component

To be useful as an endpoint, the reference design is typically extended by adding sensors or control logic such as temperature input or motor control output.

# Software development environment

Arm provides a complete software development environment which includes the Mbed operating system, Arm or GNU (GCC) compilers and debuggers, and firmware.

Custom peripherals typically require corresponding third-party firmware that can be integrated into the software stack.

# IoT hardware and software

The following figure shows a block diagram of the hardware and software in an IoT system.

Figure 1-2 Hardware and software solution

# 1.2 Features of the SSE-200

The SSE-200 contains the following components:

- Two Cortex-M33 processors:

- Optional *Floating-Point Unit* (FPU) and *Digital Signal Processor* (DSP) extensions (configurable).

- Embedded Trace Macrocell (ETM).

For more information, see the Arm® Cortex®-M33 Processor Technical Reference Manual.

- CoreSight debug system with configurable Secure Debug and Trace.

- Secure AMBA interconnect:

- Advanced High Performance Bus (AHB5) Bus Matrix.

- AHB5 TrustZone Memory Protection Controller (MPC).

- AHB5 TrustZone Peripheral Protection Controller (PPC).

- AHB5 Exclusive Access Monitor (EAM).

- AHB5 Access Control Gates (ACG).

- AHB5 to Advanced Peripheral Bus (APB) Bridges.

- Expansion AHB5 master and slave buses (two each).

- Memory system:

- AHB5 master bus to external code memory.

- Static memory controllers.

- Multiple banks of SRAM.

One bank of SRAM functions as *Tightly Coupled Memory* (TCM).

- Instruction caches.

- Security components:

- TrustZone CryptoCell-312 (optional).

- Implementation Defined Attribution Unit (IDAU).

- Secure expansion ports.

- System Security Controller.

- System Controller.

- APB peripherals with security support:

- Three general-purpose timers with configurable security. One timer is on the 32KHz domain and two are on the SYSCLK PD SYS domain.

- A Cortex-M System Design Kit (CMSDK) dual timer with configurable security.

- Three Watchdog timers with fixed security. One Secure watchdog is on the 32KHz domain and one Secure and one Non-Secure is on the SYSCLK PD SYS domain.

- Two Message Handling Units (MHUs) allow software to raise interrupts.

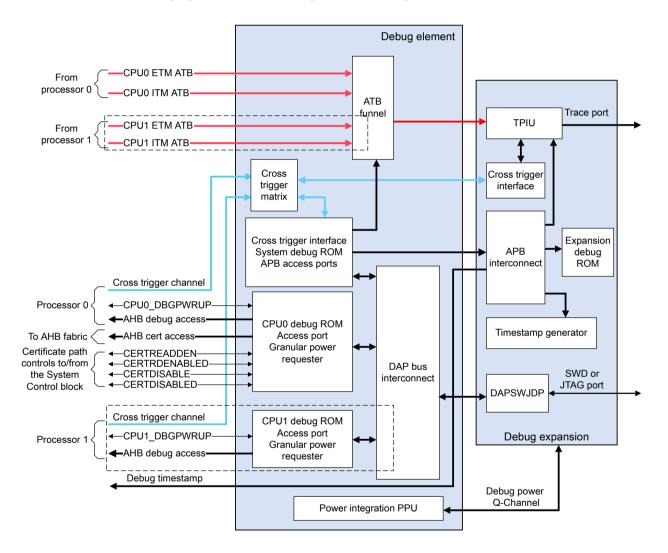

- Power-control components:

- Power Dependency Control Matrix (PDCM).

- Power Policy Units (PPU).

- CoreLink LPD-500 Low Power Distributor.

- Wakeup on interrupt from *External Wakeup Controllers* (EWC) and *Wakeup Interrupt Controllers* (WIC).

# 1.3 CoreLink SIE-200 components

The SSE-200 uses the following components from the CoreLink SIE-200 System IP for Embedded product:

- AHB5 to AHB5 Sync-down Bridge.

- AHB5 to AHB5 Sync-up Bridge.

- AHB5 Slave Multiplexer.

- AHB5 Master Multiplexer.

- AHB5 Default Slave.

- AHB5 Bus Matrix.

- AHB5 to APB4 Synchronous Bridge.

- AHB5 to APB4 Asynchronous Bridge.

- AHB5 Access Control Gate.

- AHB5 Exclusive Access Monitor.

- AHB5 to SRAM Interface.

- AHB5 TrustZone Memory Protection Controller.

- APB4 TrustZone Peripheral Protection Controller.

- Power Dependency Control Matrix.

The following CoreLink SIE-200 components can be added to the SSE-200 by the system integrator:

- · AHB5 GPIO.

- AHB5 Example Slave.

- AHB5 to External SRAM Interface.

- AHB5 to Flash Interface Modules.

- AHB5 to AHB5 and APB4 Asynchronous Bridge.

- AHB5 Downsizer.

- AHB5 Upsizer.

# 1.4 Compliance

The SSE-200 complies with, or includes components that comply with, the following specifications:

- 1.4.1 Arm® Architecture on page 1-16.

- 1.4.2 Debug on page 1-16.

- 1.4.3 Interrupt controller architecture on page 1-16.

- 1.4.4 Advanced Microcontroller Bus Architecture on page 1-16.

This Technical Reference Manual complements the TRMs for included components, architecture reference manuals, architecture specifications, protocol specifications, and relevant external standards. It does not duplicate information from these sources.

# 1.4.1 Arm® Architecture

The Cortex-M33 processor in the SSE-200 implements the Armv8-M architecture which executes the Arm-v8M T32 instruction set.

See the Arm®v8-M Architecture Reference Manual for more information.

# Security

The Arm TrustZone technology in the Armv8-M architecture enables memory and peripheral spaces to be partitioned into Secure and Non-secure regions. No access to Secure assets is possible from the Non-secure world.

# 1.4.2 **Debug**

The SSE-200 implements the Arm CoreSight debug interface.

See the *Arm*<sup>®</sup> *CoreSight*<sup>™</sup> *Components Technical Reference Manual* for more information.

# 1.4.3 Interrupt controller architecture

The SSE-200 implements the following features:

- Arm Nested Vectored Interrupt Controller (NVIC).

- Arm Wakeup Interrupt Controller (WIC).

See the *Arm*<sup>®</sup> *Cortex*<sup>®</sup>-*M33 Processor Technical Reference Manual* for more information on the NVIC. See the *Arm*<sup>®</sup> *Cortex*<sup>®</sup>-*M33 Processor User Guide Reference Material* for more information on the WIC.

# 1.4.4 Advanced Microcontroller Bus Architecture

The SSE-200 complies with the:

• Advanced High Performance Bus (AHB5) protocol.

See the *Arm*<sup>®</sup> *AMBA*<sup>®</sup> *5 AHB Protocol Specification*.

• Advanced Peripheral Bus (APB4) protocol.

See the Arm® AMBA® APB Protocol Specification Version 2.0.

The SSE-200 contains components that use Arm TrustZone technology that supports the ARMv8-M Security Extension for Secure and Non-secure states.

# Related references

1.4.1 Arm® Architecture on page 1-16.

1.4.2 Debug on page 1-16.

1.4.3 Interrupt controller architecture on page 1-16.

1.4.4 Advanced Microcontroller Bus Architecture on page 1-16.

# 1.5 Product revisions

This section describes the differences in functionality between product revisions:

r0p0

First release.

r1p0

Technical updates.

# Chapter 2 **Functional description**

This chapter describes the functionality of the SSE-200.

It contains the following sections:

- 2.1 Top-level system partitioning on page 2-19.

- 2.2 Clocks on page 2-22.

- *2.3 Resets* on page 2-27.

- 2.4 CPU elements on page 2-32.

- 2.5 Base element on page 2-43.

- 2.6 SRAM elements on page 2-49.

- 2.7 System control element on page 2-50.

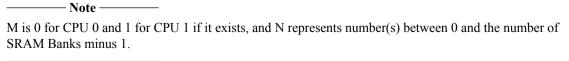

- 2.8 Debug element on page 2-52.

- 2.9 Power control infrastructure on page 2-59.

- 2.10 Crypto element on page 2-70.

# 2.1 Top-level system partitioning

This section describes the top-level partitioning of the SSE-200 subsystem.

This section contains the following subsections:

- 2.1.1 Overview on page 2-19.

- 2.1.2 Configuration options on page 2-20.

- 2.1.3 Interface signals on page 2-21.

# 2.1.1 Overview

The SSE-200 components are organized into the following blocks or elements:

- · Base element.

- CPU elements.

- Debug element.

- System control element.

- SRAM elements.

- Crypto element.

| Note                                                                                               |

|----------------------------------------------------------------------------------------------------|

| The provided system components only form part of the finished SoC. Arm expects the system designer |

| to extend and customize the subsystem for their application requirements.                          |

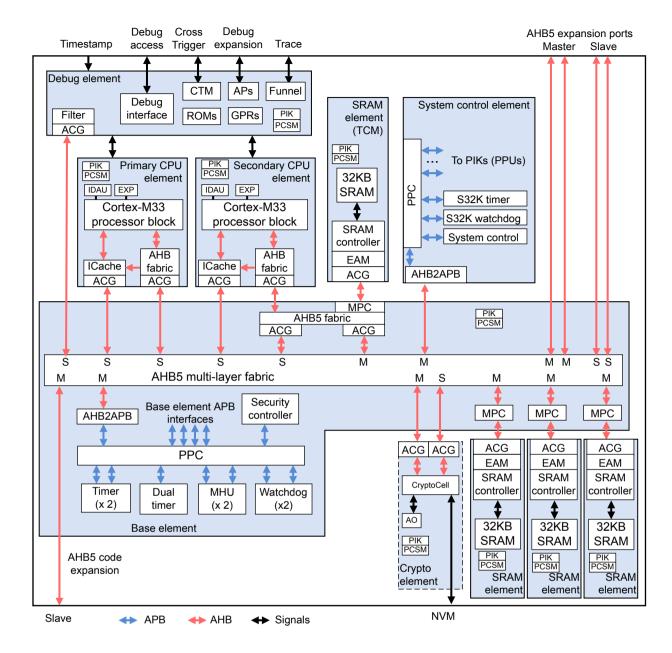

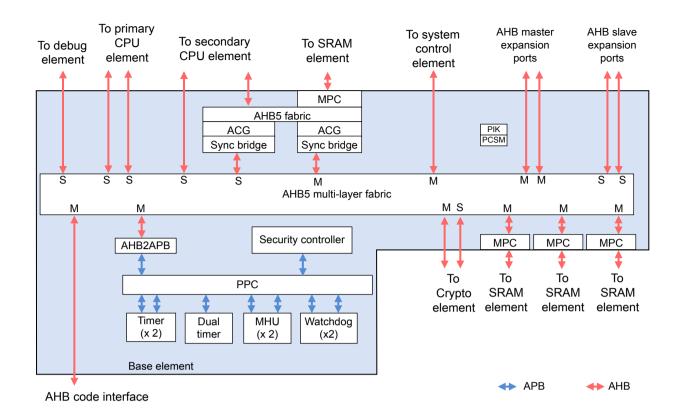

The top-level view of the subsystem elements and the AHB5 and APB bus interconnections is shown in the following figure. The following abbreviations are used in the figure:

ACG

AHB5/APB Access Control Gate.

EAM

AHB5 Exclusive Access Monitor.

MHU

Message Handling Unit.

MPC

AHB5 Memory Protection Controller.

Master Security Controller. **PCSM**

**MSC**

Power Control State Machine. **PIK**

Power Integration Kit. **PPC**

AHB5/APB Peripheral Protection Controller.

Figure 2-1 Top-level element interconnections

# 2.1.2 Configuration options

Configuration parameters set some of the processor and system options, for example:

- · Reset value for the vector table offset addresses for both processors.

- CPU IDs.

- Number of expansion interrupts for the processors and the wakeup controllers.

- Interrupt latencies.

- Presence of FPUs and support for DSP extension instructions.

- · Debug resources.

- · Clock divider values.

\_\_\_\_\_ Note \_\_\_\_

- See the Arm® CoreLink™ SSE-200 Subsystem for Embedded Configuration and Integration Manual for more configuration details.

- This manual is only available to customers who have licensed the SSE-200 product.

# Related references

- A.1 Clock, reset, and power control signals on page Appx-A-146.

- A.2 Interrupt signals on page Appx-A-152.

- A.3 AHB expansion bus signals on page Appx-A-154.

- A.4 Debug and Trace signals on page Appx-A-157.

- A.5 Security component interfaces on page Appx-A-161.

- A.6 Miscellaneous top-level signals on page Appx-A-165.

- A.7 CryptoCell-312 signals on page Appx-A-168.

# 2.1.3 Interface signals

The SSE-200 has the following interfaces at the boundary of subsystem to allow customers to customize the subsystem:

- · Clock and reset.

- · Processor-related signals:

- Processor control.

- Interrupts.

- Configuration signals.

- Base element:

- AHB expansion.

- System control:

- Static configuration signals.

- Power control expansion interfaces.

- External Wakeup Controller interrupt inputs.

- · Debug and Trace:

- Debug access.

- Timestamp.

- Cross Trigger Channel.

- Debug APB expansion.

- ATB Trace.

- Debug authentication.

- Crypto: This element integrates the CryptoCell-312 into the system to provide cryptographic acceleration. This element is optional, and it includes:

- NVM APB interface.

- Debug Control Unit (DCU) signals.

- *Life Cycle State* (LCS) signals.

- Security.

- Top-level static configuration signals.

# Related references

- A.1 Clock, reset, and power control signals on page Appx-A-146.

- A.2 Interrupt signals on page Appx-A-152.

- A.3 AHB expansion bus signals on page Appx-A-154.

- A.4 Debug and Trace signals on page Appx-A-157.

- A.5 Security component interfaces on page Appx-A-161.

- A.6 Miscellaneous top-level signals on page Appx-A-165.

- A.7 CryptoCell-312 signals on page Appx-A-168.

# 2.2 Clocks

This section describes the clocks in the SSE-200 subsystem.

This section contains the following subsections:

- 2.2.1 Overview on page 2-22.

- 2.2.2 Clock generation and control on page 2-24.

- 2.2.3 External wakeup controller clocks on page 2-25.

- 2.2.4 Power control expansion on page 2-25.

- 2.2.5 Component clocks on page 2-25.

# 2.2.1 Overview

The following clocks are present in the SSE-200:

- The subsystem uses the clock MAINCLK input to derive:

- SYSCLK which is the clock for the primary processor, bus matrix, most of the SRAMs, and peripherals.

- FCLK is used by the debug system, secondary processor, and the last SRAM.

- SRAM element 3 is also used for *Tightly Coupled Memory* (TCM) to provide higher performance for data accesses.

- A slow clock is used by some modules within the system control element.

The **S32KCLK** clock is an asynchronous clock input that is used primarily to drive the S32KWATCHDOG. **S32KCLK** also drives the S32KTIMER, and other logic that must be clocked at the lowest system power mode (hibernation).

All derived clocks are synchronous to the main input clock and a range of primary to secondary ratios are supported.

The generated clocks are locally clock gated within each element depending on which reset domain it is on, and the activity and power state of the dependent logic. The power state of dependent logic is controlled by the related *Power Policy Unit* (PPU). Some of the gated clocks are output for expansion logic in the same clock, reset, and power domains.

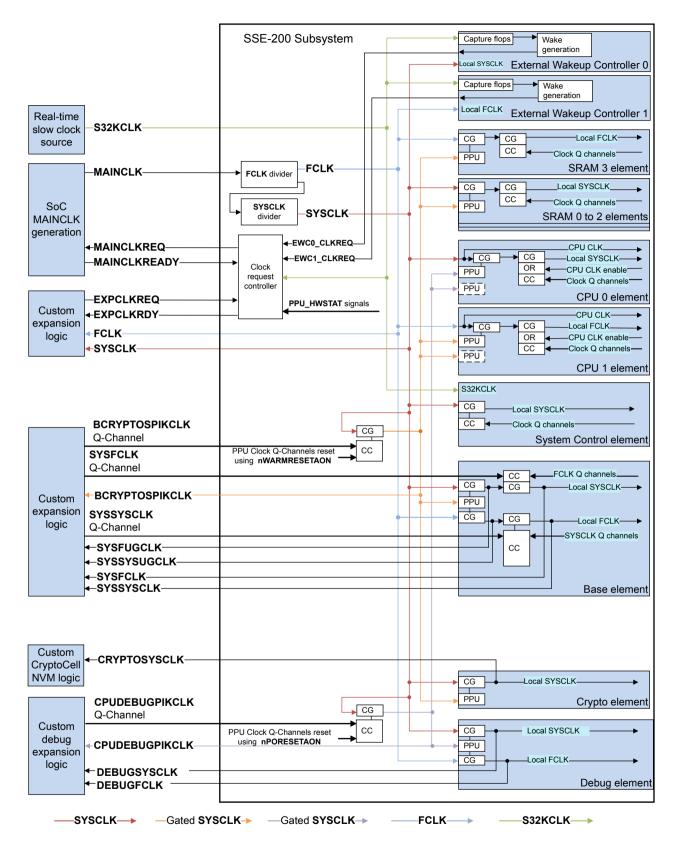

The following diagram shows the interconnections for the clock signals:

In the diagram:

- The CC blocks are clock controllers for hierarchical clock gating.

- The CG blocks are clock gates.

- The PPU blocks are Power Policy Units.

Figure 2-2 Clock interconnection

The Clock Request Controller handshakes with the external clock generator to turn off the main clock when it is not required.

System control registers control the clock divider.

Q-Channel based clock control logic provides the following features:

- Access Control Gates can isolate clock domains and provide Q-Channel handshake interfaces.

- A clock controller in each domain connects to the domains and gates the clock when the domain is

idle.

# 2.2.2 Clock generation and control

This section describes clock generation and control for MAINCLK, FCLK, and SYSCLK and clocks derived from them

# **MAINCLK**

Most clocks within the subsystem are derived from **MAINCLK**, the subsystem main input clock. The following handshake signals control the clock state:

- MAINCLKREO is the system request for MAINCLK to become active.

- MAINCLKREADY is the notification that MAINCLK is ready to be used.

**MAINCLK** is required in the following conditions:

- Any PPU in the system is in the ON state.

- Any External Wakeup Controller (EWC) is requesting that a core wakes up.

- Expansion logic uses the EXP\_CLK\_REQ and EXP\_CLK\_ACK handshake logic to request that

ungated clocks are available.

Therefore, **MAINCLK** only turns off when the system goes into the Hibernate state and no other parts of the system, including from external expansion logic, requests the clocks to be available.

# **FCLK and SYSCLK**

FCLK and SYSCLK are generated from MAINCLK:

- FCLK is generated by dividing down MAINCLK.

- SYSCLK is then generated by dividing down FCLK.

- The divider ratio can be set from configuration parameters and also by software.

| Note                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| When generating SYSCLK, ensure that the MAINCLK frequency, and the selected clock divider ratio for FCLK and SYSCLK, result in a SYSCLK frequency of more than double the S32KCLK frequency                                                                                                                                                                                                                                                   |

| The subsystem uses the <b>EXPCLKREQ</b> and <b>EXPCLKREADY</b> handshake signals to provide <b>SYSCL</b> and <b>FCLK</b> on request from external hardware. The handshake follows the same protocol as the <b>MAINCLKREQ</b> and <b>MAINCLKREADY</b> handshake signals. When using the <b>EXPCLKREQ</b> and <b>EXPCLKREADY</b> handshake signals to request active clocks, the SSE-200 also requests that the <b>MAINCLK</b> clock is active. |

| Note                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| All signals described previously connect to and from the always ON (AON) part of the system.                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Clock and reset outputs are provided for expansion of other power domains within the subsystem as follows:

For the PD\_SYS power domain, SYSFCLK and SYSSYSCLK are power-gated and hierarchical clock-gated versions of FCLK and SYSCLK. These are used for expansion logic that resides in the

- PD SYS power domain. In additional SYSSYSUGCLK and SYSFUGCLK are the equivalent power-gated but not hierarchical clock-gated versions of SYSCLK and FCLK.

- For the PD DEBUG power domain, DEBUGFCLK and DEBUGSYSCLK are hierarchical clock gated versions of FCLK and SYSCLK. These are used for debug expansion logic that resides in the PD DEBUG power domain.

- The HINTSYSCLKENCLK and DEBUGHINTSYSCLKENCLK signals are clock pulses that are generated by the divider to indicate when, relative to the divided clock FCLK or DEBUGFCLK, an enable must be generated. These are used by expansion logic external to the subsystem to generate

| the enables locally so that they can be used with bridges or other equivalent logic for crossing |

|--------------------------------------------------------------------------------------------------|

| between FCLK and SYSCLK clock domains. The enables would normally occur at the last FCLK         |

| cycle prior and up to the rising edge of SYSCLK. HINTSYSCLKENCLK is used to generate the         |

| enable in the Always ON domain while <b>DEBUGHINTSYSCLKENCLK</b> is used in the debug power      |

| domain to do the same.                                                                           |

|                                                                                                  |

| Note                                                                                             |

All fast clock outputs, FCLK, SYSFCLK and DEBUGFCLK can be gated by HINTSYSCLKENCLK when CPU 1 in the system is turned off. To enable gating, set the FCLKHINTGATE ENABLE bit in the CLOCK FORCE register to HIGH.

This allows all logic that runs on the faster clock to run at the same clock speed as the rest of the system and reduces power consumption, but at the cost of slightly higher latency when accessing SRAM3.

### 2.2.3 External wakeup controller clocks

The capture flops in the EWC typically run on S32KCLK, and therefore S32CLK is expected to be always on. If however, the system designer replaces the interrupt capture flops in the EWC with latches, the EWC does not require S32KCLK...

The wakeup request must be able to be generated from the capture flops without any other clock running. other than S32KCLK, if flops are used instead of latches. All other flops in the EWCs are expected to run on SYSCLK or FCLK depending on which core it is associated with.

### 2.2.4 Power control expansion

Two clocks allow the system designer to add extra power control logic in the Always-On power domain:

CPUDEBUGPIKCLK is a hierarchically gated version of SYSCLK clock that is related to the nPORESETAON reset domain.

The resynchronized reset signal for this clock is **nCPUDEBUGPIKRESET**.

A Q-Channel interface is also provided to allow expansion logic on this clock domain to influence the hierarchical gating of the clock.

This clock is typically used for power control logic that supports expansion of the CPU and Debug elements.

BCRYPTOSPIKCLK is a hierarchically gated version of SYSCLK that is related to the nWARMRESETAON reset domain.

The resynchronized reset signal for this clock is **nBCRYPTOSPIKRESET**.

A O-Channel interface is provided to allow expansion logic on this clock domain to influence the hierarchical gating of the clock.

This clock is typically used for power control logic that supports expansion of the main system that is reset directly or indirectly by nWARMRESETAON.

### 2.2.5 **Component clocks**

The elements use the system clocks as follows:

# **SRAM** element

Each SRAM runs on one clock. Most run on **SYSCLK**. Optionally one SRAM can run on **FCLK** instead of **SYSCLK**.

The PPU gates the clock that is used in the element for power management.

The SRAM element can locally implement dynamic clock control to further reduce the amount of time the clock is active when the element is idle.

# **CPU** element

Each CPU element runs on a single clock:

- The primary core runs on SYSCLK.

- The secondary core runs on FCLK.

Because the Cortex-M33 processor has its own clock gating control, the Cortex-M33 cores require an ungated clock to be supplied to each core.

The PPU can gate the clock to the rest of the CPU element, including the instruction cache and the ACG, for power management. Additional dynamic clock control is combined with Cortex-M33 processor clock enable output to further reduce the amount of time the clock is active when the element is idle.

## Base element

The base element requires both FCLK and SYSCLK.

The PPU gates each clock for power management.

The base element locally implements dynamic clock control to further reduce the amount of time each clock is active when the element is idle. These clocks are available for expansion use as the **SYSFCLK**, **SYSSYSCLK**, and **SYSSYSUGCLK** clock outputs.

# **Debug element**

The debug element requires both FCLK and SYSCLK.

The PPU gates each clock for power management.

The debug element does not implement dynamic clock control. The local clocks are running whenever the element is powered ON. These clocks are available for expansion use as the **DEBUGFCLK** and **DEBUGSYSCLK** clock outputs.

# System control element

The system control element requires S32KCLK, FCLK, and SYSCLK.

Because the control element is in the always-on power domain, the element does not have a PPU to gate clocks.

The element implements dynamic clock control for **SYSCLK** to reduce the amount of time **SYSCLK** clock is active when the element is idle.

# Crypto element

The CryptoCell, if present, runs on SYSCLK.

For power control, the PPU gates this clock. The **CRYPTOSYSCLK** is the power-gated and hierarchical clock-gated version of **SYSCLK**. This clock is available to use for CryptoCell NVM Interface expansion.

The element also implements dynamic clock control for **SYSCLK**, to reduce the amount of time **SYSCLK** is active when the element is idle.

# Related references

A.1 Clock, reset, and power control signals on page Appx-A-146.

# 2.3 Resets

This section describes the resets in the SSE-200 subsystem.

This section contains the following subsections:

- 2.3.1 Overview on page 2-27.

- 2.3.2 Reset inputs and outputs on page 2-28.

- 2.3.3 nPORESET handling on page 2-29.

- 2.3.4 Processor reset handling on page 2-30.

- 2.3.5 nWARMRESETAON on page 2-30.

- 2.3.6 Power control reset on page 2-31.

# 2.3.1 Overview

The SSE-200 reset infrastructure takes reset inputs and requests from external sources and from within the subsystem, and generates the resets that are distributed through the system.

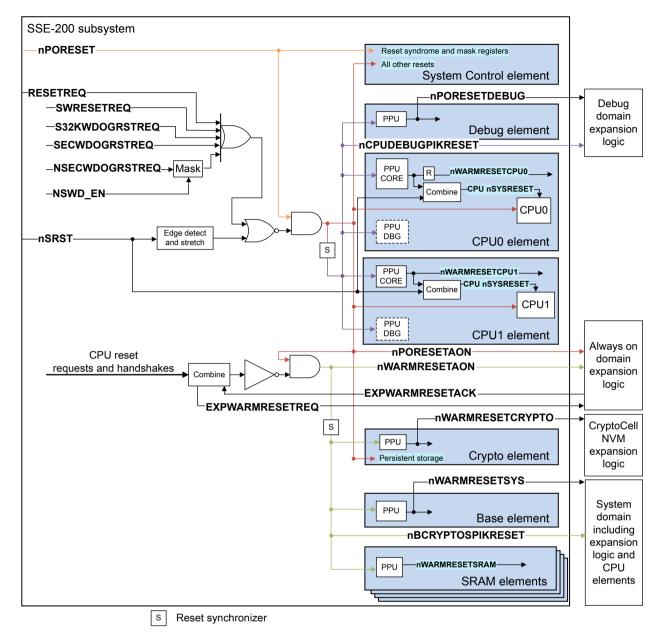

The following figure shows the reset infrastructure:

Figure 2-3 Reset interconnection

# 2.3.2 Reset inputs and outputs

The following reset-related signals in the subsystem are from or to the Always On part of the subsystem:

# nPORESET

This is the Power-on reset input for the SSE-200. Arm recommends that this signal is one or more **S32CLK** cycles long.

# nSRST

This signal, typically from an external debugger, is the system-wide reset request:

- This reset is applied to the subsystem on the falling edge of the **nSRST** signal and then removed, except for the **nSYSRESET** pin of each processor core.

- If nSRST is held low, all processor cores are also stopped from booting.

The nSRST input must be a minimum of three S32KCLK cycles long. nSRST can be held LOW while performing other debug related tasks to indefinitely prevent the processor from execution. This might be done, for example, when inserting a debug certificate into the SRAM. After nSRST is deasserted after its assertion, it must be held inactive for at least three S32KCLK cycles before being asserting again.

# **nWARMRESETAON**

This signal performs a Warm reset of the system. This signal:

- Must not be used to reset any debug-related logic.

- Is also asserted if **nPORESETAON** is asserted.

- Merges other reset sources that are required to cause system reset.

- Is asynchronous and must be resynchronized before use.

# nPORESETAON

The **nPORESETAON** reset output is the Power-on reset signal intended for use by the expansion subsystem logic. This reset output merges other reset sources that are required to cause power-on reset. This reset output is asynchronous and must be resynchronized before use.

# **RESETREQ**

This allows external expansion logic to request a system reset:

- After it is asserted, the signal must be held HIGH until the reset occurs on nPORESETAON.

- The signal must be cleared because of the assertion of **nPORESETAON**.

# **EXPWARMRESETREO**

The **EXPWARMRESETREQ** expansion Warm reset output signal, when set to HIGH, indicates that the reset logic is about to assert a Warm reset to the system. This waits for the **EXPWARMRESETACK** signal to be HIGH before asserting the reset, allowing any external logic to complete critical operations by delaying the assertion of Warm reset.

| Note               | <del></del>                                             |

|--------------------|---------------------------------------------------------|

| If EXPWARMRES      | SETREQ is not used, you must connect EXPWARMRESETREQ to |

| <b>EXPWARMRESE</b> | TACK.                                                   |

|                    |                                                         |

# **EXPWARMRESETACK**

The **EXPWARMRESETACK** expansion Warm reset input signal works along with **EXPWARMRESETREQ**, allowing external logic to delay the assertion of Warm reset.

The following signals are provided for expansion of other power domains in the subsystem:

# **nWARMRESETSYS**

This is the system reset signal for expansion logic in the PD SYS power domain.

It supports logic retention and is not asserted if the PD\_SYS power domain is entering retention state.

# nPORESETDEBUG

This is the Power-on reset signal for debug expansion logic in the PD\_DEBUG power domain.

# Related references

A.1 Clock, reset, and power control signals on page Appx-A-146.

# 2.3.3 nPORESET handling

**nPORESET** directly resets the Reset Syndrome registers and Mask register.

**nPORESET** is combined with the masked and combined reset requests from watchdog timers, the **RESETREQ** input, the SWRESETREQ register value, and the negative-edge detect and stretched signal of **nSRST**. This generates the internal combined Power-on reset signal **nPORESETAON**, which resets almost all logic within the system.

**nPORESETAON** resets the PPU, in each PPU-controlled power domain. The PPU then resets the other logic in the domain using its reset pins:

- **DEVWARMRESETn** if the domain does not support retention.

- **DEVRETRESETn** if the domain supports logic or full retention.

# 2.3.4 Processor reset handling

Because the Cortex-M33 core normally handles reset on its own, **nPORESETAON** is fed directly to the Cortex-M33 core. **nSYSRESET** of the Cortex-M33 core is generated from the local PPU as the PPU can handle Warm reset of the core.

The reset from the PPU, **DEVRETRESETn**, is combined with **nSRST** to hold the core in reset until **nSRST** is deasserted. This allows a debugger to hold the processor core in reset while it uses the Debug Access Port to perform debug operations

# **Boot after reset**

After reset, both processors boot the instruction at the boot address from the vector offset address register in the System Control Registers.

- Static top-level configuration parameters determine the contents of the vector offset address register in the System Control Registers. The default address is 0x00000000 and is statically mapped to code memory of the AHB Master Expansion Code interface.

- Software can modify the boot addresses before a warm reboot of the processors.

- See A.6.2 Top-level static configuration signals on page Appx-A-166 and the Arm® CoreLink™ SSE-200 Subsystem for Embedded Configuration and Integration Manual.

The TrustZone-M requirement for boot up is that execution starts from a Secure memory space, and optionally automatically executes Non-secure firmware after Secure world initialization. At boot, the SRAM is Secure only. Software must change or restore the settings in the MPC to release memory for Non-secure world use.

The **CPUWAIT** input can force the Cortex-M33 processor to wait before executing the instruction. Each processor in the system has an associated CPU\_WAIT register that controls it, if it starts running boot code when it wakes.

See the *Arm*<sup>®</sup> *Cortex*<sup>®</sup>-*M33 Processor Technical Reference Manual*.

# Related references

A.6.2 Top-level static configuration signals on page Appx-A-166. Certificate Access on page 2-54.

# 2.3.5 nWARMRESETAON

The **nWARMRESETAON** signal performs a System reset. **nWARMRESETAON** is generated by merging reset requests from the following sources, possibly after masking with the value in the RESET MASK Register:

- nPORESETAON.

- The system reset request from the Cortex-M33 core.

| nV | VARMRESETAON is provided to system designers for external components.                         |

|----|-----------------------------------------------------------------------------------------------|

| _  | Note                                                                                          |

| nV | VARMRESETAON resets each PPU-controlled power domain. The PPU generates the reset in each     |

| po | wer domain including the <b>nWARMRESETAON</b> reset and the local power management reset. The |

| PP | U reset pin is either:                                                                        |

| •  | <b>DEVWARMRESETn</b> if the element does not support retention.                               |

| •  | <b>DEVRETRESETn</b> if the element supports logic or full retention.                          |

# 2.3.6 Power control reset

The *Power Policy Units* (PPUs) in the system are hierarchically clock gated and divided into two clock and reset groups. Each set of clocks and resets are made available for use by expansion power control logic:

- The first group of PPUs run on the **CPUDEBUGPIKCLK** clock. These PPUs are reset using a resynchronized version of **nPORESETAON**, called **nCPUDEBUGPIKRESET**.

- The second group of PPUs run on the **BCRYPTOSPIKCLK** clock. These PPUs are reset using a resynchronized version of **nWARMRESETAON**, called **nBCRYPTOSPIKRESET**.

# 2.4 CPU elements

This section describes the CPU elements.

This section contains the following subsections:

- 2.4.1 Overview on page 2-32.

- 2.4.2 Cortex-M33 configurations on page 2-33.

- 2.4.3 Instruction cache on page 2-37.

- 2.4.4 CPU WAIT control on page 2-39.

- 2.4.5 Interrupts on page 2-39.

- *2.4.6 Power domains* on page 2-41.

- 2.4.7 Clock domains on page 2-41.

- 2.4.8 Security on page 2-41.

- 2.4.9 External wakeup on page 2-42.

# 2.4.1 Overview

There are two Cortex-M33 cores in the SSE-200:

- The primary core in the CPU0 element is synchronous to main interconnect and runs the operating system.

- The secondary core in the CPU1 element contains an FPU and DSP. It is synchronous to the main clock, but runs *N* times faster.

The Cortex-M33 processor has the following features:

- Three-stage pipeline.

- ARMv8-M Mainline profile.

- TrustZone-M Security.

- Up to eight SAU entries each (configurable).

- Up to 16 MPU regions with eight Secure and eight Non-secure (configurable).

- IDAU defining high-level security memory mapping.

Each processor has configuration parameters that can be set in the design stage to specify the processor features including:

- If the FPU is present.

- If the Digital Signal Processing extension instructions are included.

- If the coprocessor interface is present.

- The number of Non-secure and Secure MPU regions.

- The number of security attribution unit regions.

- The number of user interrupts.

- The interrupt priority and interrupt latency that is implemented in the NVIC.

- Debug resources and trace support.

See 2.4.2 Cortex-M33 configurations on page 2-33 and the SSE-200 Configuration and Integration Manual for more details on system configuration options.

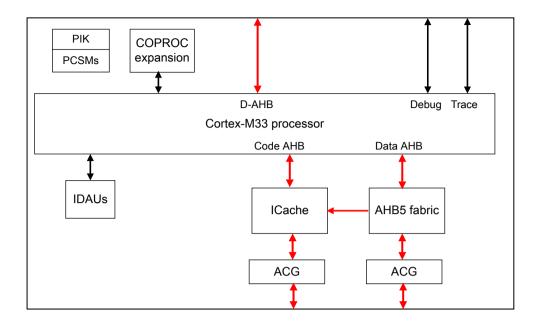

The following figure shows a block diagram of the Cortex-M33 processor logic and CoreSight SoC interface:

Figure 2-4 CPU element

# Related references

2.4.2 Cortex-M33 configurations on page 2-33.

# 2.4.2 Cortex-M33 configurations

Each processor supports the following configuration with the following features.

**Table 2-1 Core configurations**

| Parameter | CPU 0 option | CPU 1 option | CPU 0<br>default | CPU 1<br>default | Description                                                             |

|-----------|--------------|--------------|------------------|------------------|-------------------------------------------------------------------------|

| FPU       | CPU0_FPU     | CPU1_FPU     | 0                | HAS_FP<br>U      | Define if <i>Floating Point Unit</i> (FPU) is present:  0: Not Present. |

|           |              |              |                  |                  | 1: Present.                                                             |

| DSP       | CPU0_DSP     | CPU1_DSP     | 0                | 1                | Digital Signal Processing (DSP) extension instructions are included.    |

|           |              |              |                  |                  | 0: Not included.                                                        |

|           |              |              |                  |                  | 1: Included.                                                            |

| SECEXT    | 1            | 1            | -                | -                | ARMv8-M Security Extensions are always included.                        |

# Table 2-1 Core configurations (continued)

| Parameter  | CPU 0 option                                                                        | CPU 1 option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CPU 0<br>default | CPU 1<br>default | Description                                                                                   |

|------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|-----------------------------------------------------------------------------------------------|

| CPIF       | CPU0_CPIF                                                                           | CPU1_CPIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                | 0                | Coprocessor interface is included.                                                            |

|            |                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  |                  | 0: Not included. This is the only supported value.                                            |

|            |                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  |                  | 1: Included.                                                                                  |

|            |                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  |                  | These are driven by top-level parameters.                                                     |

| MPU_NS     | CPU0_MPU_NS                                                                         | CPU1_MPU_NS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8                | 8                | Defines the number of Non-<br>secure <i>Memory Protection Unit</i><br>(MPU) regions included. |

|            |                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  |                  | Options are: 0, 4, 8, 12, and 16.                                                             |

| MPU_S      | CPU0_MPU_S                                                                          | CPU1_MPU_S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8                | 8                | Defines the number of Secure MPU regions included.                                            |

|            |                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  |                  | Options are: 0, 4, 8, 12, and 16.                                                             |

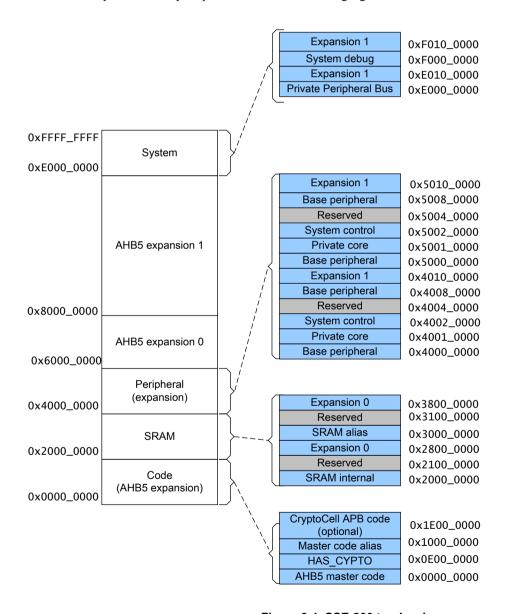

| SAU        | CPU0_SAU                                                                            | CPU1_SAU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8                | 8                | Defines the number of Security Attribution Unit (SAU) regions included.                       |