# Arm<sup>®</sup> CoreLink<sup>™</sup> GIC-600 Generic Interrupt Controller

Revision: r1p6

**Technical Reference Manual**

## Arm<sup>®</sup> CoreLink<sup>™</sup> GIC-600 Generic Interrupt Controller

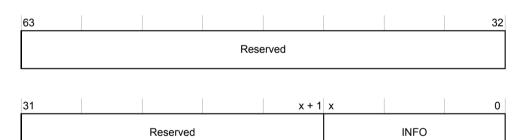

## **Technical Reference Manual**

Copyright © 2016–2019 Arm Limited or its affiliates. All rights reserved.

#### **Release Information**

#### **Document History**

| Issue   | Date             | Confidentiality  | Change                   |

|---------|------------------|------------------|--------------------------|

| 0000-00 | 29 July 2016     | Confidential     | First release for r0p0.  |

| 0000-01 | 26 October 2016  | Confidential     | Second release for r0p0. |

| 0001-00 | 31 March 2017    | Confidential     | First release for r0p1.  |

| 0002-00 | 07 June 2017     | Confidential     | First release for r0p2.  |

| 0002-01 | 15 June 2017     | Non-Confidential | Second release for r0p2. |

| 0003-00 | 08 January 2018  | Non-Confidential | First release for r0p3.  |

| 0102-00 | 02 February 2018 | Non-Confidential | First release for r1p2.  |

| 0103-00 | 27 March 2018    | Non-Confidential | First release for r1p3   |

| 0104-00 | 27 July 2018     | Non-Confidential | First release for r1p4.  |

| 0106-00 | 08 February 2019 | Non-Confidential | First release for r1p6.  |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. **No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.**

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with <sup>®</sup> or <sup>TM</sup> are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at *http://www.arm.com/company/policies/trademarks*.

Copyright © 2016-2019 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

#### **Product Status**

The information in this document is Final, that is for a developed product.

#### Web Address

http://www.arm.com

## Contents Arm<sup>®</sup> CoreLink<sup>™</sup> GIC-600 Generic Interrupt Controller Technical Reference Manual

|           | Preface |                            |  |

|-----------|---------|----------------------------|--|

|           |         | About this book            |  |

|           |         | Feedback                   |  |

| Chapter 1 | Intro   | oduction                   |  |

|           | 1.1     | About the GIC-600          |  |

|           | 1.2     | Components                 |  |

|           | 1.3     | Compliance                 |  |

|           | 1.4     | Features                   |  |

|           | 1.5     | Test features              |  |

|           | 1.6     | Product documentation      |  |

|           | 1.7     | Product revisions          |  |

| Chapter 2 | Con     | nponents and configuration |  |

|           | 2.1     | Distributor                |  |

|           | 2.2     | Redistributor              |  |

|           | 2.3     | ITS                        |  |

|           | 2.4     | MSI-64 Encapsulator        |  |

|           | 2.5     | SPI Collator               |  |

|           | 2.6     | Wake Request               |  |

|           | 2.7     | Interconnect               |  |

|           | 2.8     | Hierarchy                  |  |

|           |         |                            |  |

| Chapter 3  | Ореі  | ration                                                        |            |

|------------|-------|---------------------------------------------------------------|------------|

|            | 3.1   | Interrupt types                                               | 3-48       |

|            | 3.2   | Interrupt groups                                              | 3-51       |

|            | 3.3   | Physical interrupt signals (PPIs and SPIs)                    | 3-52       |

|            | 3.4   | Affinity routing and assignment                               | 3-53       |

|            | 3.5   | 1 of N SPI interrupt selection                                |            |

|            | 3.6   | Power management                                              | 3-57       |

|            | 3.7   | Getting started                                               |            |

|            | 3.8   | Security                                                      | 3-61       |

|            | 3.9   | Backwards compatibility                                       | 3-63       |

|            | 3.10  | Interrupt translation service (ITS)                           |            |

|            | 3.11  | LPI caching                                                   | 3-67       |

|            | 3.12  | Memory access and attributes                                  | 3-68       |

|            | 3.13  | MSI-64                                                        |            |

|            | 3.14  | RAM                                                           | 3-71       |

|            | 3.15  | Performance Monitoring Unit                                   |            |

|            | 3.16  | Reliability, Accessibility, and Serviceability                | 3-74       |

|            | 3.17  | Multichip operation                                           | 3-96       |

| Chapter 4  | Prog  | rammer's model                                                |            |

|            | 4.1   | The GIC-600 registers                                         | 4-103      |

|            | 4.2   | Distributor registers (GICD/GICDA) summary                    | 4-106      |

|            | 4.3   | Distributor registers (GICA) for message-based SPIs summary   | 4-125      |

|            | 4.4   | Redistributor registers for control and physical LPIs summary |            |

|            | 4.5   | Redistributor registers for SGIs and PPIs summary             | 4-135      |

|            | 4.6   | ITS control register summary                                  | 4-141      |

|            | 4.7   | ITS translation register summary                              | 4-152      |

|            | 4.8   | GICT register summary                                         | 4-153      |

|            | 4.9   | GICP register summary                                         | 4-171      |

| Appendix A | Sign  | al descriptions                                               |            |

|            | A.1   | Common control signals                                        | Appx-A-186 |

|            | A.2   | Power control signals                                         | Appx-A-188 |

|            | A.3   | Interrupt signals                                             | Аррх-А-189 |

|            | A.4   | CPU interface signals                                         | Аррх-А-190 |

|            | A.5   | ACE interface signals                                         | Appx-A-191 |

|            | A.6   | Miscellaneous signals                                         | Appx-A-196 |

|            | A.7   | Interblock signals                                            | Аррх-А-197 |

|            | A.8   | Interdomain signals                                           | Аррх-А-200 |

|            | A.9   | Interchip signals                                             | Аррх-А-201 |

| Appendix B | Imple | ementation-defined features                                   |            |

|            | B.1   | Implementation-defined features reference                     | Аррх-В-203 |

| Appendix C | Revi  | sions                                                         |            |

|            | C.1   | Revisions                                                     | Аррх-С-206 |

## Preface

This preface introduces the Arm<sup>®</sup> CoreLink<sup>™</sup> GIC-600 Generic Interrupt Controller Technical Reference Manual.

It contains the following:

- *About this book* on page 7.

- Feedback on page 10.

## About this book

This book is for the Arm<sup>®</sup> CoreLink<sup>™</sup> GIC-600 Generic Interrupt Controller.

## Product revision status

The *rmpn* identifier indicates the revision status of the product described in this book, for example, r1p2, where:

- rm Identifies the major revision of the product, for example, r1.

- pn Identifies the minor revision or modification status of the product, for example, p2.

## Intended audience

This book is for system designers, system integrators, and programmers who are designing or programming a *System-on-Chip* (SoC) that uses the GIC-600 Generic Interrupt Controller.

## Using this book

This book is organized into the following chapters:

## **Chapter 1 Introduction**

This chapter introduces the GIC-600 and its features.

## **Chapter 2 Components and configuration**

This chapter describes the major components of the GIC-600.

## **Chapter 3 Operation**

This chapter provides an operational description of the GIC-600.

## Chapter 4 Programmer's model

This chapter describes the memory map and registers, and provides information about programming the device.

## Appendix A Signal descriptions

This appendix describes the input and output signals.

### Appendix B Implementation-defined features

This appendix describes the features that are IMPLEMENTATION DEFINED.

## Appendix C Revisions

This appendix describes changes between released issues of this book.

## Glossary

The Arm<sup>®</sup> Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

See the Arm® Glossary for more information.

## **Typographic conventions**

#### italic

Introduces special terminology, denotes cross-references, and citations.

### bold

Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.

#### monospace

Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.

monospace

Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.

monospace italic

Denotes arguments to monospace text where the argument is to be replaced by a specific value.

#### monospace bold

Denotes language keywords when used outside example code.

<and>

Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:

MRC p15, 0, <Rd>, <CRn>, <CRm>, <Opcode\_2>

#### SMALL CAPITALS

Used in body text for a few terms that have specific technical meanings, that are defined in the *Arm*<sup>®</sup> *Glossary*. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE.

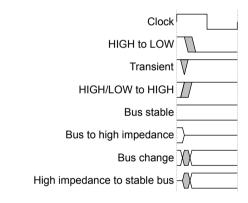

## **Timing diagrams**

The following figure explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

#### Figure 1 Key to timing diagram conventions

## Signals

The signal conventions are:

#### Signal level

The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals.

- LOW for active-LOW signals.

#### Lowercase n

At the start or end of a signal name denotes an active-LOW signal.

## Additional reading

This book contains information that is specific to this product. See the following documents for other relevant information.

## Arm publications

- Arm<sup>®</sup>AMBA<sup>®</sup> AXI and ACE Protocol Specification (IHI 0022).

- Arm<sup>®</sup>AMBA<sup>®</sup> 4 AXI4-Stream Protocol Specification (IHI 0051).

- *AMBA*<sup>®</sup> Low Power Interface Specification, Arm<sup>®</sup> Q-Channel and P-Channel Interfaces (IHI 0068).

- Arm<sup>®</sup> Generic Interrupt Controller Architecture Specification, GIC architecture version 3.0 and version 4.0 (IHI 0069).

- Arm<sup>®</sup> Architecture Reference Manual ARMv8, for ARMv8-A architecture profile (DDI 0487).

- Arm<sup>®</sup> GICv3 and GICv4 Software Overview (DAI 0492).

- Arm<sup>®</sup>CoreLink<sup>™</sup> CMN-600 Coherent Mesh Network Technical Reference Manual (100180).

- Arm<sup>®</sup> Reliability, Availability, and Serviceability (RAS) Architecture Specification ARMv8, for the ARMV8-A architecture profile (DDI 0587B.a).

The following confidential books are only available to licensees or require registration with Arm:

- Arm<sup>®</sup>CoreLink<sup>™</sup> GIC-600 Generic Interrupt Controller Configuration and Integration Manual (100337).

- Arm<sup>®</sup>CoreLink<sup>™</sup> ADB-400 AMBA<sup>®</sup> Domain Bridge User Guide (DUI 0615).

- Arm<sup>®</sup>CoreLink<sup>™</sup> CMN-600 Coherent Mesh Network Configuration and Integration Manual (100613).

## **Other publications**

• JEDEC, Standard Manufacturer's Identification Code, JEP106.

## Feedback

## Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

## Feedback on content

If you have comments on content then send an e-mail to *errata@arm.com*. Give:

- The title Arm CoreLink GIC-600 Generic Interrupt Controller Technical Reference Manual.

- The number 100336 0106 00 en.

- If applicable, the page number(s) to which your comments refer.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

\_\_\_\_\_ Note \_\_\_\_\_

Arm tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader.

## Chapter 1 Introduction

This chapter introduces the GIC-600 and its features.

It contains the following sections:

- 1.1 About the GIC-600 on page 1-12.

- *1.2 Components* on page 1-13.

- *1.3 Compliance* on page 1-17.

- 1.4 Features on page 1-18.

- 1.5 Test features on page 1-19.

- 1.6 Product documentation on page 1-20.

- 1.7 Product revisions on page 1-21.

## 1.1 About the GIC-600

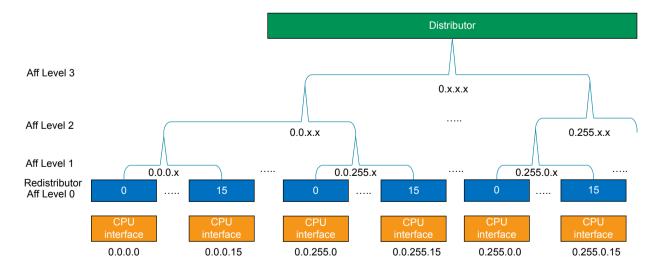

The GIC-600 is a generic interrupt controller that handles interrupts from peripherals to the cores and between cores. The GIC-600 supports a distributed microarchitecture containing several individual blocks that are used to provide a flexible GIC implementation.

The GIC-600 supports the GICv3 architecture, see the Arm<sup>®</sup> Generic Interrupt Controller Architecture Specification, GIC architecture version 3.0 and version 4.0.

The microarchitecture scales from a single core to coherent multichip environments containing up to 16 chips of up to 64 cores each.

\_\_\_\_\_ Note \_\_\_\_\_

- Note

This manual defines a *chip* as an SoC that is integrated with the GIC-600. A single-chip system has one SoC. A multichip system can have several SoCs that are connected externally, or an SoC comprising several SoCs connected inside a single physical package. In all cases, each SoC is integrated with the GIC-600.

All the GIC-600 blocks communicate through fully credited AXI4-Stream interface channels. This means that the interface exerts transient backpressure only on their **ic**<**xy**>**tready** signals, enabling packets to be routed over any free-flowing interconnect. Channels can be routed over dedicated AXI4-Stream buses, or over any available free-flowing transport layer in the system. A channel is described as free-flowing if all transactions on that channel complete without a non-transient dependency on any other transaction.

The GIC-600 includes build scripts that can create appropriate levels of hierarchy for any particular configuration. In small configurations, the distribution can be hidden and internally optimized.

All ACE-Lite interfaces are compliant to ACE4-Lite and do not support ACE5-Lite features unless explicitly stated in this document.

## 1.2 Components

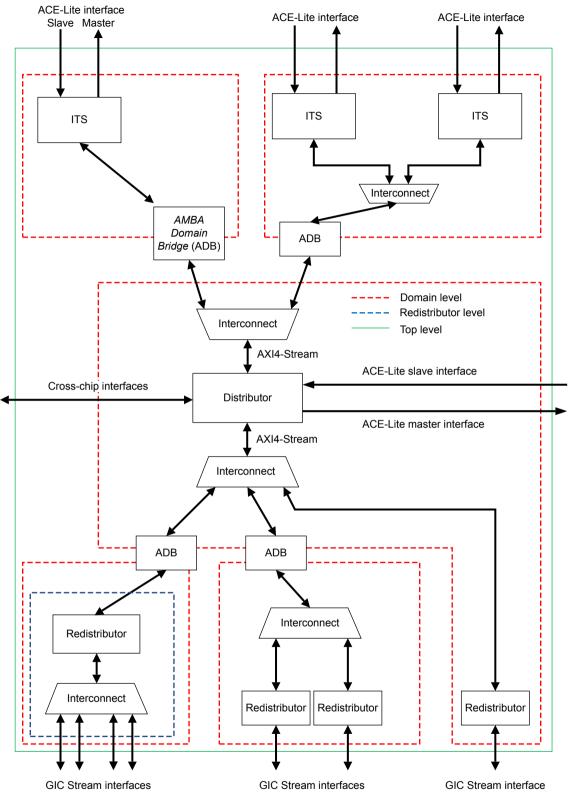

The GIC-600 comprises several significant blocks that work in combination to create a single architecturally compliant GICv3 implementation within the system. The GIC-600 top level can have one of several optional structures.

The GIC-600 consists of the following blocks:

## Distributor

The Distributor is the hub of all the GIC communications and contains the functionality for all *Shared Peripheral Interrupts* (SPIs) and *Locality-specific Peripheral Interrupts* (LPIs). It is responsible for the entire GIC programmers model, except for the GITS\_TRANSLATER register, which is hosted in the *Interrupt Translation Service* (ITS) block.

The Distributor also maintains the coherency of the SPI register space in multichip configurations.

\_\_\_\_\_ Note \_\_\_\_\_

The LPI functionality for all cores on a chip is combined into a single cache in the Distributor.

## Redistributor

The Redistributor maintains the *Private Peripheral Interrupts* (PPIs) and *Software Generated Interrupts* (SGIs) for a particular set of cores. A Redistributor can scale from 1-64 cores and is best placed next to the processors that it is servicing to reduce wiring to the cores.

A Redistributor is also referred to as a PPI block.

The GICv3 architecture specifies a Redistributor address space containing two pages per core. The SGI page functionality is contained in the GIC-600 Redistributor. However, the command and control pages for all cores on a chip are contained in the Distributor.

The GIC-600 supports powering down the Redistributors and the associated cores.

## **Interrupt Translation Service**

The ITS translates message-based interrupts, *Message-Signaled Interrupts* (MSI/MSIx), from an external *PCI Express* (PCIe) *Root Complex* (RC), or other sources. The ITS also manages LPIs during core power management.

The GIC-600 supports up to 16 ITS blocks per chip.

For more information about the ITS, see the Arm® GICv3 and GICv4 Software Overview.

### **MSI-64 Encapsulator**

The MSI-64 Encapsulator is a small block that combines the *DeviceID* (DID), required by writes to the GITS\_TRANSLATER register, into a single memory access.

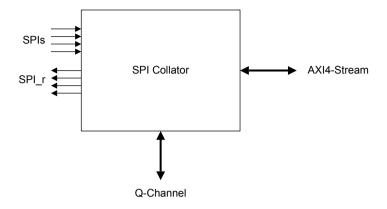

## **SPI** Collator

The GIC-600 supports up to 960 SPIs that are spread across the system. The SPI Collator enables SPIs to be converted into messages remotely from the Distributor. This enables hierarchical clock gating of the Distributor and the use of other more aggressive low-power states.

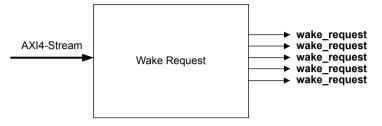

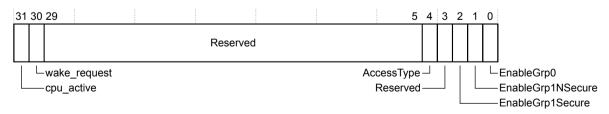

## Wake Request

The Wake Request contains all the architecturally defined **wake\_request** signals for each core on the chip. It is a separate block that can be positioned remotely from the Distributor, such as next to a system control processor if necessary.

## **GIC** interconnect

The GIC interconnect is a set of components that can be used for routing the AXI4-Stream interfaces between the different blocks.

## **Top level**

The top level has no specific interfaces but combines the interfaces of other blocks within the clock or power domain to reduce the number of domain bridges. The GIC-600 build scripts enable you to build the GIC from a single combined block or a set of individual blocks that are interconnected using your own transport layer.

These blocks can be combined in different ways:

- In systems where there is an available free-flowing transport layer in place, existing buses can be used to route the GIC traffic.

- The GIC-600 includes a narrow, 16-bit, AXI4-Stream interconnect that can be used for routing internal traffic.

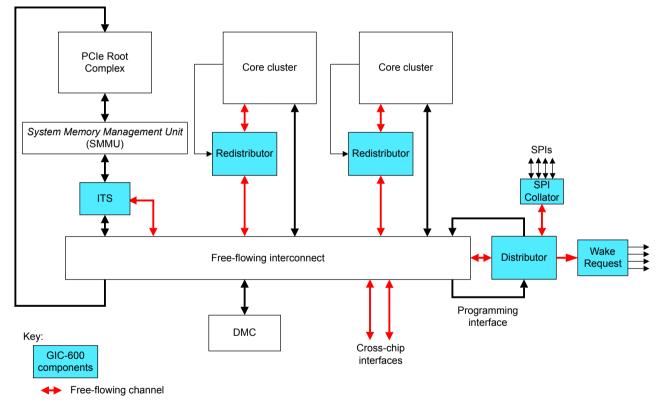

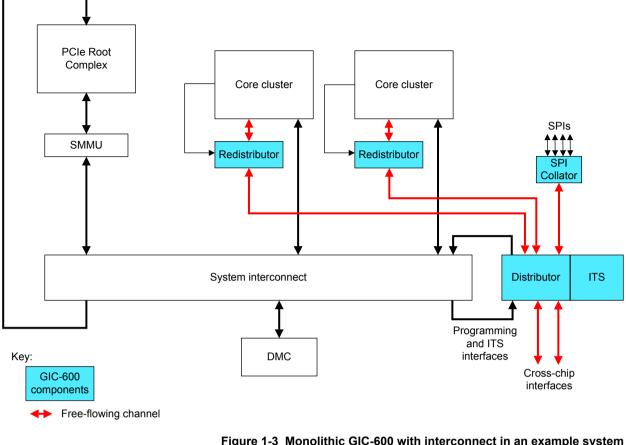

The following figure shows a GIC-600 with a free-flowing interconnect in an example system.

A free-flowing channel is clear to transmit a transaction that arrives at its destination without any non-transient dependencies on other transactions.

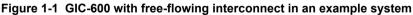

The following figure shows a GIC-600 with interconnect in an example system.

- Note -

## Figure 1-2 GIC-600 with interconnect in an example system

Cross-chip interfaces enable communication between cores in a multichip configuration. Cross-chip is supported in product version r1p2 onwards.

– Note –

The following figure shows a monolithic GIC-600 with interconnect in an example system.

If the GIC supports LPIs, there must be free-flowing access to main memory. This requirement is irrespective of the interconnect that is used for routing the AXI4-Stream interfaces. For more information, see the Arm<sup>®</sup>CoreLink<sup>™</sup> GIC-600 Generic Interrupt Controller Configuration and Integration Manual.

- Note -

The GIC-600 supports cores that implement only the ARMv8.0-A architecture, and later versions such as v8.2-A. The cores must also support the GIC CPU interface with the standard GIC AXI4-Stream protocol interface. The GIC-600 implements version 3.0 of the Arm® Generic Interrupt Controller Architecture Specification, GIC architecture version 3.0 and version 4.0.

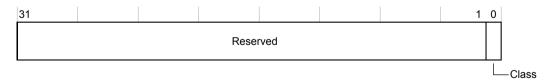

## 1.3 Compliance

The GIC-600 interfaces are compliant with Arm specifications and protocols.

The GIC-600 is compliant with:

- The AMBA AXI4-Stream protocol. See the Arm<sup>®</sup>AMBA<sup>®</sup> AXI and ACE Protocol Specification.

- Version 3.0 of the Arm GIC architecture specification. See the Arm<sup>®</sup> Generic Interrupt Controller Architecture Specification, GIC architecture version 3.0 and version 4.0.

The GIC Stream protocol is based on the following specifications:

- The AMBA AXI4-Stream protocol. See the Arm®AMBA® 4 AXI4-Stream Protocol Specification.

- The GIC Stream Protocol Interface. See the Arm<sup>®</sup> Generic Interrupt Controller Architecture Specification, GIC architecture version 3.0 and version 4.0.

## 1.4 Features

The GIC-600 provides interrupt services and masking, registers and programming, interrupt grouping, security, performance monitoring, and error correction.

## Interrupt services and masking

The GIC-600 provides the following interrupt services and masking features:

- Support for the following interrupt types:

- Up to 56000 LPIs. A peripheral generates these interrupts by writing to a memory-mapped register in the GIC-600. See 2.1.7 *Distributor configuration* on page 2-27.

- Up to 960 SPIs in groups of 32. See 2.1.7 Distributor configuration on page 2-27.

- Up to 16 PPIs that are independent for each core and can be programmed to support either edgetriggered or level-sensitive interrupts. See 2.2.6 Redistributor configuration on page 2-31.

- Up to 16 SGIs that are generated through the GIC CPU interface of a core.

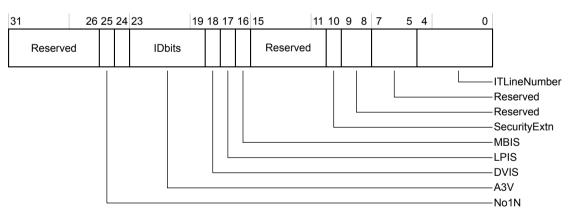

- Up to 16 ITS modules that provide device isolation and ID translation for message-based interrupts and enable virtual machines to program devices directly.

- Interrupt masking and prioritization with 32 priority levels, five bits per interrupt.

## **Registers and programming**

The GIC-600 provides the following programming features:

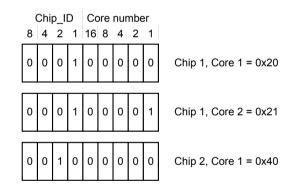

- Flexible affinity routing, using the *Multiprocessor Identification Register* (MPIDR) addresses, including support for all four affinity levels.

- Single ACE-Lite slave port on each chip for programming of all *GIC Distributor* (GICD) registers, GIC *Interrupt Translation Service* (GITS) registers, and *GIC Redistributor* (GICR) registers. Each ITS has an optional ACE-Lite slave port for programming the GITS TRANSLATER register.

- Coherent view of SPI register data across multiple chips.

## Security

The GIC-600 provides the following security features:

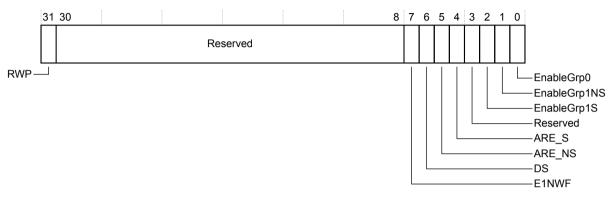

- A global Disable Security (DS) bit. This bit enables support for systems without security.

- The following interrupt groups allow interrupts to target different Exception levels:

- Group 0.

- Non-secure Group 1.

- Secure Group 1.

See 3.8 Security on page 3-61 for more information about security and groupings.

—— Note —

For more information about Exception levels, see the *Arm*<sup>®</sup> *Architecture Reference Manual ARMv8, for ARMv8-A architecture profile.*

## **Performance monitoring**

The GIC-600 provides the following performance monitoring features:

• Performance Monitoring Unit (PMU) counters with snapshot functionality.

## **Error correction**

The GIC-600 provides the following error correction features:

- ARMv8.2 Reliability Accessibility Serviceability (RAS) architecture-compliant error reporting for:

- Software access errors.

- ITS command and translation errors.

- Error Correcting Code (ECC) errors.

## 1.5 Test features

The GIC-600 provides Design for Test (DFT) signals for test mode.

**Related reference**

A.1 Common control signals on page Appx-A-186

## 1.6 Product documentation

Documentation that is provided with this product includes a *Technical Reference Manual* (TRM) and a *Configuration and Integration Manual* (CIM), together with architecture and protocol information.

For relevant protocol and architectural information that relates to this product, see *Additional reading* on page 8.

The GIC-600 documentation is as follows:

## **Technical Reference Manual**

The TRM describes the functionality and the effects of functional options on the behavior of the GIC-600. It is required at all stages of the design flow. The choices that are made in the design flow can mean that some behaviors that the TRM describes are not relevant. If you are programming the GIC-600, contact:

- The implementer to determine:

- The build configuration of the implementation.

- What integration, if any, was performed before implementing the GIC-600.

- The integrator to determine the signal configuration of the device that you use.

The TRM complements architecture and protocol specifications and relevant external standards. It does not duplicate information from these sources.

## **Configuration and Integration Manual**

The CIM describes:

- The available build configuration options.

- How to configure the *Register Transfer Level* (RTL) with the build configuration options.

- How to integrate the GIC-600 into a SoC.

- How to implement the GIC-600 into your design.

- The processes to validate the configured design.

The Arm product deliverables include reference scripts and information about using them to implement your design.

The CIM is a confidential book that is only available to licensees.

## 1.7 Product revisions

This section describes the differences in functionality between product revisions.

| r0p0      | First release.                                                             |

|-----------|----------------------------------------------------------------------------|

| r0p0-r0p1 | <ul><li>Functional changes are:</li><li>Bug fixes.</li></ul>               |

| r0p1-r0p2 | <ul><li>Functional changes are:</li><li>Bug fixes.</li></ul>               |

| r0p2-r0p3 | <ul><li>Functional changes are:</li><li>Bug fixes.</li></ul>               |

| r0p3-r1p2 | <ul><li>Functional changes are:</li><li>Multichip functionality.</li></ul> |

| r1p2-r1p3 | <ul><li>Functional changes are:</li><li>Bug fixes.</li></ul>               |

| r1p3-r1p4 | <ul><li>Functional changes are:</li><li>Bug fixes</li></ul>                |

| r1p4-r1p6 | <ul><li>Functional changes are:</li><li>Bug fixes</li></ul>                |

## Chapter 2 Components and configuration

This chapter describes the major components of the GIC-600.

It contains the following sections:

- *2.1 Distributor* on page 2-23.

- 2.2 Redistributor on page 2-29.

- 2.3 ITS on page 2-32.

- 2.4 MSI-64 Encapsulator on page 2-38.

- 2.5 SPI Collator on page 2-41.

- 2.6 Wake Request on page 2-43.

- 2.7 Interconnect on page 2-44.

- 2.8 *Hierarchy* on page 2-45.

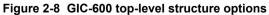

## 2.1 Distributor

The Distributor is the main communication point between all GIC-600 blocks. It performs SPI management and LPI caching, and all communications with other blocks and chips.

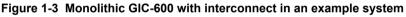

The following figure shows the Distributor and its interfaces.

## Figure 2-1 GIC-600 Distributor

The Distributor is the main hub of the GIC and it implements most of the GICv3 architecture including:

- Programming, forwarding, and prioritization of SPIs, see 3.1.3 SPIs on page 3-48.

- Caching and forwarding of LPIs, see 3.1.4 LPIs on page 3-49.

- SGI routing and forwarding.

- Register programming of all registers apart from GITS\_TRANSLATER.

- Power control of cores and Redistributor blocks.

This section contains the following subsections:

- 2.1.1 Distributor AXI4-Stream interfaces on page 2-24.

- 2.1.2 Distributor ACE-Lite slave interface on page 2-24.

- 2.1.3 Distributor ACE-Lite master interface on page 2-25.

- 2.1.4 Distributor *Q*-Channels on page 2-26.

- 2.1.5 P-Channel on page 2-26.

- 2.1.6 Distributor miscellaneous signals on page 2-27.

- 2.1.7 Distributor configuration on page 2-27.

## 2.1.1 Distributor AXI4-Stream interfaces

The GIC-600 uses AXI4-Stream interfaces to communicate between blocks.

These interfaces are fully credited.

— Note — —

- ic<xy>tready xy can be cd, dc, pd, dp, id, di, rd, dr, or dw.

- Packets must not be reordered between endpoints, for example, between the Distributor and a single Redistributor block, irrespective of the interconnect that is used. Packets must never be interleaved.

For information about AXI4-Stream signals, see the Arm®AMBA® 4 AXI4-Stream Protocol Specification.

For information about the **TWAKE** signal, see section E.2.9 of the *Arm®AMBA® AXI and ACE Protocol Specification*. The **TWAKE** signal is equivalent to the **AWAKEUP** signal.

The following table lists the AXI4-Stream input interfaces.

| Table 2-1 | AXI4-Stream | input interface | descriptions |

|-----------|-------------|-----------------|--------------|

|-----------|-------------|-----------------|--------------|

| Bus  | Destination                  | Width                     | ic <xy>dtid</xy>     |

|------|------------------------------|---------------------------|----------------------|

| ICID | ITS to Distributor           | 16-bit or 64-bit          | ITS number           |

| ICPD | Redistributor to Distributor | 16-bit, 32-bit, or 64-bit | Redistributor number |

| ICCD | SPI Collator to Distributor  | 16-bit                    | 0                    |

| ICRD | Remote Chip to Distributor   | 64-bit                    | 0                    |

The following table lists the AXI4-Stream output interfaces.

## Table 2-2 AXI4-Stream output interface descriptions

| Bus  | Destination                       | Width                     | ic <xy>dtdest</xy>   |

|------|-----------------------------------|---------------------------|----------------------|

| ICDI | Distributor to ITS                | 16-bit or 64-bit          | ITS number           |

| ICDP | Distributor to Redistributor      | 16-bit, 32-bit, or 64-bit | Redistributor number |

| ICDC | Distributor to SPI Collator       | 16-bit                    | 0                    |

| ICDR | Distributor to Remote Chip        | 64-bit                    | Programmed value     |

| ICDW | Distributor to Wake Request block | 16-bit                    | -                    |

Each bus has an associated **ic**<**xy**>**twakeup** signal that requests wakeup through the **qactive** signals when the Distributor, or destination block, is hierarchically clock gated through the Q-Channel. The **ic**<**xy**>**twakeup** input signal must be driven from a cleanly registered version of the **ic**<**xy**>**tvalid** signal to prevent spurious wakeups caused by signal glitches.

For information about the Distributor Q-Channels, see 2.1.4 Distributor Q-Channels on page 2-26.

## 2.1.2 Distributor ACE-Lite slave interface

The AMBA AXI4 ACE-Lite slave port on the GIC-600 Distributor provides access to the entire register map except for the GITS\_TRANSLATER register. The interface supports either 64-bit, 128-bit, or 256-bit data widths.

The GIC-600 only accepts single beat accesses of the sizes for each register that are shown in the Programmers model, see *Chapter 4 Programmer's model* on page 4-102. All other accesses are rejected and given either an OKAY or SLVERR response that is based on the GICT\_ERROCTLR.UE bit.

When the GIC-600 is a monolithic configuration, the Distributor and ITS both share an ACE-Lite slave port, and the DeviceID for the ITS translation is taken from **awuser\_s[DEVICE\_ID\_WIDTH+2:3**]. See *2.3 ITS* on page 2-32, for more information about the ITS.

\_\_\_\_\_ Note \_\_\_\_\_

The a<x>user\_s[2:0] signals are not used and must be tied LOW.

The following table shows the acceptance capabilities of the Distributor ACE-Lite slave interface.

Table 2-3 Distributor ACE-Lite slave interface acceptance capabilities

| Attribute                      | Capability |

|--------------------------------|------------|

| Combined acceptance capability | 3          |

| Read acceptance capability     | 2          |

| Read data reorder depth        | 1          |

| Write acceptance capability    | 2          |

The GIC-600 uses **a**<**x**>cache\_s, a<**x**>domain\_s, and **a**<**x**>bar\_s signals to detect cache maintenance operations and barrier transactions that are responded to in a protocol-compliant manner but are otherwise ignored. The GIC-600 also ignores other cachability, shareability, and protection settings, except for security signal **a**<**x**>prot\_s[1].

If you are connecting to an AXI3 or AXI4 port, signals **a**<**x**>**domain**>\_**s**, **a**<**x**>**bar\_s** and, for AXI3, **a**<**x**>**len**[7:4] must all be tied LOW.

The GIC-600 has a separate **awakeup\_s** signal to force the GIC to wakeup when it is hierarchically clock gated through the Q-Channel. The **awakeup\_s** signal must be connected to a cleanly registered version of **(awvalid\_s | arvalid\_s)** to ensure that the GIC does not request to be woken up due to incoming signal glitches.

The GIC-600 address map can have several pages. The number of pages depends on your configuration. See *4.1.1 Register map pages* on page 4-103.

You must set up the system address map so that each core accesses the GICD page on its local chip at the same address. All other pages must be globally accessible, although access of pages on a remote chip by a core is expected to be rare.

In most configurations, the GIC-600 ignores address bits above ceiling[log<sub>2</sub>(page\_count)] + 15. For example, a configuration that uses 11 pages ignores address bits above 19, and any address bits of the form 0xXXXXX00000 is accepted to access the GICD page of the memory map. However, in monolithic configurations, where the Distributor and ITS share the ACE-Lite slave port, there are two address tie-offs that specify the full page address of the GICD and GITS\_TRANSLATER pages. The page address comprises address bits[x:16]. For example, if the GICD page is at 32-bit address 0xFFFF0000, the tie-off is 16-bit 0xFFFF. See 2.1.6 Distributor miscellaneous signals on page 2-27 for information about the Distributor miscellaneous signals.

## **Related reference**

4.1.1 Register map pages on page 4-103

## 2.1.3 Distributor ACE-Lite master interface

The GICD uses the AMBA AXI4 ACE-Lite master interface to access LPI Property and Pending tables. If LPIs are not supported, then this interface is not present.

The interface can be configured to be 64-bit, 128-bit, or 256-bit wide.

The following table shows the issuing capabilities of the Distributor ACE-Lite master interface.

| Attribute                                            |      | Capability |          |  |

|------------------------------------------------------|------|------------|----------|--|

|                                                      | Read | Write      | Combined |  |

| 256-bit aligned read and writes to any Pending table | 3    | 3          | 3        |  |

| 8-bit read and writes to any Pending table           |      | 1          | 1        |  |

| 256-bit aligned reads to the Property table          |      | 0          | 1        |  |

| 8-bit reads to the Property table                    |      | 0          | 4        |  |

## Table 2-4 Distributor ACE-Lite master interface issuing capabilities

Each transaction uses a unique transaction ID, and properties come from either the GICR\_PROPBASER or GICR\_PENDBASER registers according to the destination. There is one copy of the attribute fields for all GICR\_PROPBASER registers and another for all GICR\_PENDBASER registers, so software must program these registers to a consistent value in all Redistributors.

The ACE-Lite master port cannot issue barriers or *Cache Maintenance Operations* (CMOs). However, it can issue shareable, *ReadOnce* and *WriteUnique*, transactions if programmed to do so.

See 3.12 Memory access and attributes on page 3-68 for more information.

The **a**<**x**>**user\_m** signal outputs the GICR\_TYPER.ProcessorNumber of the core that is associated with each transaction, but it can be ignored and it is not necessary to route it anywhere else.

——— Note ——

If the Distributor and ITS both share the same ACE-Lite master port, the issuing capabilities are cumulative.

## 2.1.4 Distributor Q-Channels

There is a single Q-Channel for clock gating the GIC-600 Distributor. The Q-Channel interface denies access if the Distributor block is busy processing interrupts.

The Distributor also has a separate Q-Channel that enables power control for each configured ITS. The Q-Channel reads GITS\_CTLR.Quiescent to check whether the ITS is fully disabled. If the Quiescent bit is set, the Q-Channel **qacceptn\_its** signal is asserted, and the GIC guarantees that the bus to the relevant ITS is idle in both directions and that the ITS can be powered down. To perform wake-on-LPI functionality, you can use GITS\_FCTLR.PWE to disable the bus while the ITS is still active and able to translate interrupts. If the bus is disabled, the system must re-enable the bus based on the status of the ITS **qactive** signal, that is, when **qactive\_its** is not asserted.

------ Note ---

The **qreqn**\* signals are synchronized internally, and can be driven asynchronously. See *A.2 Power control signals* on page Appx-A-188.

For more information, see *AMBA*<sup>®</sup> Low Power Interface Specification, Arm<sup>®</sup> Q-Channel and P-Channel Interfaces.

## 2.1.5 P-Channel

The P-Channel is used for power control of the GIC-600 Distributor.

The P-Channel is present only in multichip configurations. It is used to safely isolate the Distributor from other chips to allow the save and restore of its register states.

## **Related concepts**

3.6 Power management on page 3-57

## 2.1.6 Distributor miscellaneous signals

The Distributor generates or processes several signals, such as tie-offs, interrupts, and handshakes.

The following table shows the Distributor miscellaneous signals.

## Table 2-5 Distributor miscellaneous signals

| Signal           | Direction | Description                                                                                                                                                                                                                                                                           |  |

|------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| chip_id          | Input     | Tie off this signal to identify the chip in the system. Only present if there is more than one chip in the system.                                                                                                                                                                    |  |

| fault_int        | Output    | These fault handling and error reporting interrupts are defined in Arm® Reliability, Availability, and                                                                                                                                                                                |  |

| err_int          | Output    | <i>Serviceability (RAS) Architecture Extension.</i> The GIC-600 can deliver these interrupts internally but the outputs are provided for any other device such as a system control processor that does not receive normal interrupts from the GIC.                                    |  |

|                  |           | See 3.16 Reliability, Accessibility, and Serviceability on page 3-74.                                                                                                                                                                                                                 |  |

| pmu_int          | Output    | The PMU counter overflow interrupt. This interrupt can be routed internally but is provided as an external output to trigger an external agent to service the GIC, for example, to read out the PMU counter snapshot registers.<br>See 3.15 Performance Monitoring Unit on page 3-72. |  |

| sample_req,      | Input     | This 4-phase handshake provides a hardware mechanism to snapshot the PMU counters and has the same effect as writing to the GICP_CAPR register.                                                                                                                                       |  |

| sample_ack       | Output    |                                                                                                                                                                                                                                                                                       |  |

| gict_allow_ns,   | Input     | From reset, these tie-off signals control whether Non-secure software can access the GICT RAS, and the GICP PMU, pages. Secure software can override the values at any time.                                                                                                          |  |

| gicp_allow_ns    | Input     |                                                                                                                                                                                                                                                                                       |  |

| gicd_page_offset | Input     | This tie-off signal is used to set the page address bits[x:16] of the GICD page. Only present in monolithic configurations.                                                                                                                                                           |  |

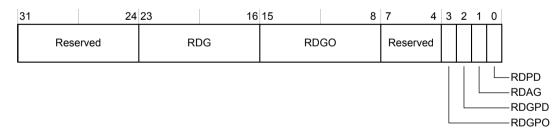

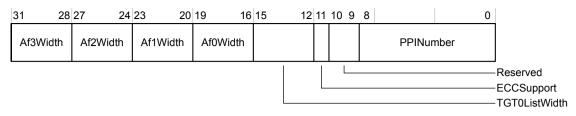

## 2.1.7 Distributor configuration

You can configure several options that relate to the operation of the Distributor block.

## Table 2-6 Configurable options for the Distributor

| Feature                                          | Range of options             |

|--------------------------------------------------|------------------------------|

| Number of chips                                  | 1-16                         |

| Affinity level that is used for chip selection   | 2, 3                         |

| Affinity0 width                                  | 0-4                          |

| Affinity1 width                                  | 0-8                          |

| Affinity2 width                                  | 0-8                          |

| Affinity3 width                                  | 0-8                          |

| LPI support                                      | True, False                  |

| LPI cache size (entries / 2)                     | 8, 16, 32, 64, 128, 256, 512 |

| Number of ITS                                    | 0-16                         |

| Number of Redistributors on chip                 | 1-64                         |

| Number of message-based SPIs permitted in system | 32-960, in blocks of 32      |

## Table 2-6 Configurable options for the Distributor (continued)

| Feature                                         | Range of options                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of SPI wires on chip for wire-based SPIs | 0-960                                                                                                                                                                                                                                                                                                                                               |

| Security support                                | Options include:         • Security support programmable. Resets to support security.         • Security support always present.         • Security support not present.         • Note         See Security model in the Arm* GICv3 and GICv4 Software Overview for information about the implications of setting Security support to not present. |

For more information, see the Arm<sup>®</sup>CoreLink<sup>™</sup> GIC-600 Generic Interrupt Controller Configuration and Integration Manual and Arm<sup>®</sup> GICv3 and GICv4 Software Overview.

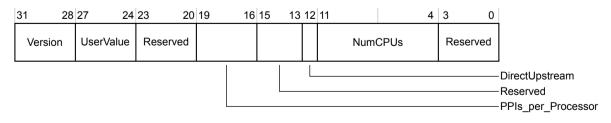

## 2.2 Redistributor

The Redistributor is responsible for PPIs and SGIs that are associated with its related cluster or group of cores. A Redistributor is also referred to as a PPI block.

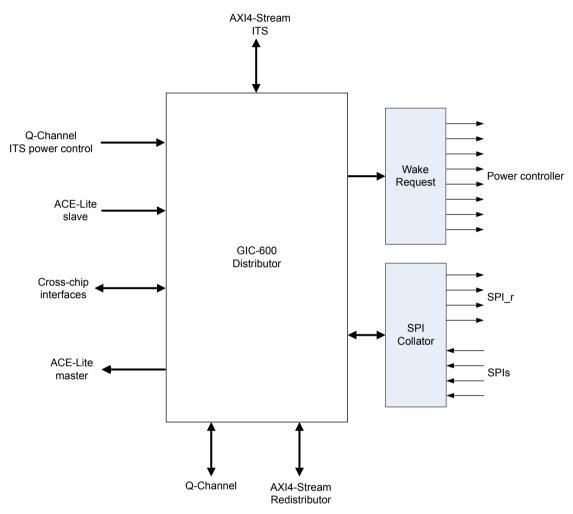

The following figure shows the Redistributor block.

Figure 2-2 GIC-600 Redistributor

The Redistributor performs the following functions:

- Maintaining the SGI and PPI programming.

- Monitoring, and if necessary, synchronizing the PPI wires.

- Prioritizing SGIs, PPIs, and any other interrupts that are sent from the Distributor, and forwarding them to the core.

- Maintaining the GIC Stream protocol and communicating with the cluster.

There can be multiple Redistributors in a configuration and they can be sized to match your system. For example, if you have two clusters of eight cores, then you can have one Redistributor positioned next to each cluster. You can use a Redistributor for each cluster to reduce the PPI wiring and enable the Redistributor to be powered down with the cores for extra power savings. Alternatively, for a small system, combining all cores into one Redistributor block might be the best solution. See *Configuration options* in the *Arm*<sup>®</sup>*CoreLink*<sup>™</sup> *GIC-600 Generic Interrupt Controller Configuration and Integration Manual* for more information.

## - Note

The Redistributor (GICR) registers are programmed through the Distributor ACE-Lite slave port. The Distributor also contains the architectural LPI functionality.

This section contains the following subsections:

- 2.2.1 Redistributor AXI4-Stream interface on page 2-30.

- 2.2.2 Redistributor GIC Stream protocol interface on page 2-30.

•

- 2.2.3 Redistributor Q-Channel on page 2-30.

- 2.2.4 Redistributor PPI signals on page 2-30.

- 2.2.5 Redistributor miscellaneous input signals on page 2-31.

- 2.2.6 Redistributor configuration on page 2-31.

## 2.2.1 Redistributor AXI4-Stream interface

Each Redistributor has an upstream and downstream AXI4-Stream port for communicating with the Distributor. This interface is either 16-bit or 64-bit wide and uses a fully credited protocol.

See 1.1 About the GIC-600 on page 1-12.

## 2.2.2 Redistributor GIC Stream protocol interface

The GIC-600 uses the GIC Stream protocol interface to send interrupts to the core and receive notifications when the core activates interrupts. The GIC Stream protocol interface has a pair of 16-bit wide AXI4-Stream interfaces, one upstream interface, and one downstream interface.

The GIC Stream protocol interface, also referred to as the GIC Stream interface, uses the GIC Stream protocol to pass interrupts and responses to the CPU interface inside each core.

## Table 2-7 GIC Stream protocol interface signals

| Signal name | Description                                                                                                                                                                                                    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| iri         | Prefix which identifies the names of the downstream interface signals. These signals are sent by the GIC Stream master. On this interface, the Redistributor is the master and the CPU interface is the slave. |

| icc         | Prefix which identifies the names of the upstream interface signals. These signals are sent by the GIC Stream slave.<br>On this interface, the CPU interface is the master and the Redistributor is the slave. |

| iritdest    | The GIC Stream master interface uses this signal to direct packets to one core within the cluster.                                                                                                             |

| icctid      | The GIC Stream slave interface uses this signal to determine which core within the cluster sent a packet.                                                                                                      |

Both the **iritdest** and **icctid** can support 64 cores that use packed binary encoding, as opposed to one-hot encoding. They can also be divided down using an AXI4-Stream crossbar to support clusters of an arbitrary number of cores from 1-64.

The necessary crossbar is generated as part of the render process based on the number of GIC-Stream buses that are specified for each Redistributor.

## 2.2.3 Redistributor Q-Channel

The Redistributor has a single Q-Channel input that is used to ensure that the Redistributor can be safely clock gated hierarchically.

If the Redistributor is busy, actively processing interrupts or sending messages up or downstream, the Q-Channel denies a quiescence request, **qreqn**, by asserting the **qdeny** signal. For more information, see the *AMBA*<sup>®</sup> *Low Power Interface Specification, Arm*<sup>®</sup> *Q*-Channel and *P*-Channel Interfaces.

—— Note —

The **qreqn** input is synchronized inside the Redistributor.

The **qactive** signal is connected to the PPI wires directly, and must be considered as an asynchronous output.

### **Related reference**

A.2 Power control signals on page Appx-A-188

## 2.2.4 Redistributor PPI signals

GIC-600 supports 8, 12, or 16 PPIs, and synchronized output return wires, for each core. The number of PPIs and return wires must be the same for all cores sharing a Redistributor.

Level-sensitive PPI signals are active-LOW by default, as with previous Arm GIC implementations. However, individual PPI signals can be inverted and synchronized using parameters gic600\_<config\_name>\_PPI<ppi\_id>\_<cpu\_number>\_<ppi\_number>\_<INV/SYNC>.

Every wire has a corresponding wire from after the synchronizer or capture flop. These can be used to create pulse extenders for edge-triggered interrupts that cross clock domains.

– Note -

If you plan to use edge-triggered PPIs and the Q-Channel to clock gate the Redistributor hierarchically, you must use pulse extenders to ensure that interrupts are not missed while the clock is restarted.

For information about the purpose of each PPI used by the core in your system, refer to the relevent core *Technical Reference Manual*.

## 2.2.5 Redistributor miscellaneous input signals

The Redistributor receives signals that identify the status of each core. It also has a tie-off signal that provides the Redistributor with a unique identifier.

## Table 2-8 Redistributor miscellaneous input signals

| Signal       | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cpu_active   | Input     | This signal indicates if the core is active and not in a low-power state such as retention. The GIC can decide to target only active cores for 1 of N SPIs. See <i>3.15 Performance Monitoring Unit</i> on page 3-72.<br><b>Note cpu_active</b> is not synchronized into the Redistributor. If <b>cpu_active</b> is driven from a different domain, it must be synchronized externally.<br> |

| ppi_id[15:0] | Input     | This tie-off signal provides the Redistributor with a unique identifier that is used primarily to ensure that the GIC is correctly integrated into the system.                                                                                                                                                                                                                              |

## **Related concepts**

3.6 Power management on page 3-57

## 2.2.6 Redistributor configuration

You can configure several options that relate to the operation of the Redistributor block.

## Table 2-9 Configurable options for the Redistributor

| Feature                    | Range of options           |  |

|----------------------------|----------------------------|--|

| Number of cores downstream | 1-64                       |  |

| PPIs per core              | 8, 12, 16                  |  |

| ECC support <sup>a</sup>   | True, False                |  |

| Bus data width             | 16 or 32                   |  |

| GIC Stream bus structure   | Flexible buses and domains |  |

For more information, see the Arm<sup>®</sup>CoreLink<sup>™</sup> GIC-600 Generic Interrupt Controller Configuration and Integration Manual and Arm<sup>®</sup> GICv3 and GICv4 Software Overview.

## **Related concepts**

3.1 Interrupt types on page 3-48

100336\_0106\_00\_en

<sup>&</sup>lt;sup>a</sup> See 3.16 Reliability, Accessibility, and Serviceability on page 3-74 for more information.

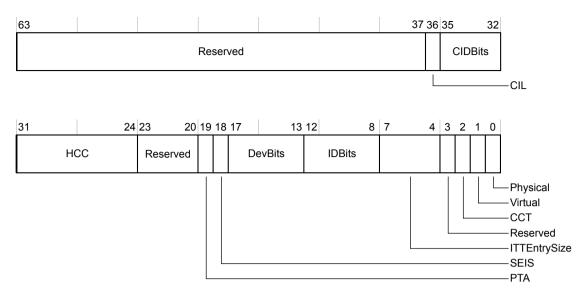

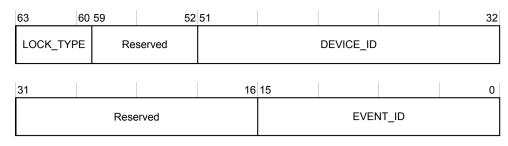

## 2.3 ITS

The ITS provides a software mechanism for translating message-based interrupts into LPIs. The ITS is supported optionally in configurations that support LPIs.

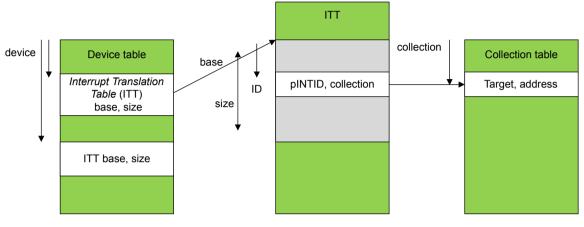

A peripheral generates an LPI by writing to the GITS\_TRANSLATER in the ITS. The write provides the ITS with the following information:

- *EventID* (VID). A value written to GITS\_TRANSLATER. The EventID identifies which interrupt the peripheral is sending. Each interrupt source is identified by an *Interrupt Identifier* (INTID). The EventID might be the same as the INTID, or it might be translated by the ITS into the INTID.

- DeviceID (DID). The DeviceID is a unique identifier that identifies the peripheral.

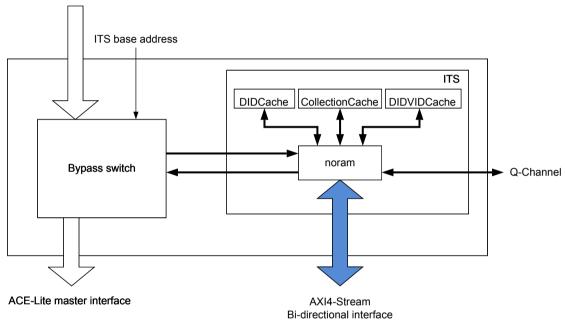

The following figure shows the ITS block.

## ACE-Lite slave interface

## Figure 2-3 ITS block

The ITS is an implementation of the GICv3 Interrupt Translation Service as described in the *Arm*<sup>®</sup> *Generic Interrupt Controller Architecture Specification, GIC architecture version 3.0 and version 4.0.* The ITS translates MSI requests to the required LPI and target. It also has a set of commands for managing LPIs for core power management and load balancing.

A main use of the ITS is the translation of MSI/MSIx messages from a PCIe *Root Complex* (RC). To complete the translation, the ITS must be supplied with a DeviceID that is derived from the PCIe RequestorID. To reduce the distance that the DeviceID is transferred and to enable better compartmentalization between RCs, the ITS is best placed next to the RC. To ease integration, the ITS has an optional bypass switch as shown in the ITS block diagram. If the bypass switch is not configured, the ACE-Lite slave and master ports connect to the ITS directly. See *2.3.1 ITS ACE-Lite slave interface* on page 2-33 and *2.3.2 ITS ACE-Lite master interface* on page 2-35.

In accordance with PCIe dependency rules, read responses on a PCIe Root Complex slave port must be ordered against completion of posted writes on a Root Complex master port. This means that writes must always make forward progress. The functionality of the ITS means that there is a dependency between

writes to the GITS\_TRANSLATER register and reads to memory and therefore one of the following must be true:

- The interconnect must allow forward progress of reads under all circumstances.

- The GIC parameter <dgi\_mem\_support> must be set. This option provides support for routing all ITS translation dependent traffic via the ACE-Lite master port on the Distributor which must have free flowing access to memory. Once configured this feature must be enabled at boot time via writes to the GITS\_FCTLR.DMA to route the traffic via the distributor.

This increases the width of the AxID fields on the Distributor master interface.

Note -

If the neither of the above is then you must not use the configuration shown in *Figure 2-3 ITS block* on page 2-32. This also applies to the CoreLink CMN-600 Coherent Mesh Network if the I/O coherent Requesting Node (RN-I) is able to access the same I/O Home Node (HN-I) that provides access to the PCIe Root Complex slave port. If the ITS is configured without a bypass switch, then a bypass switch can still be used to provide ITS access to memory through a different interconnect port, without merging the master ports.

See 3.10 Interrupt translation service (ITS) on page 3-64 for more information.

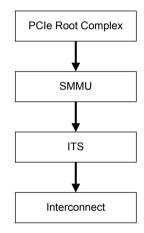

The following figure provides an example of the ITS integration process.

## Figure 2-4 ITS integration

An ITS can be placed anywhere in the system so that it is seen by devices that want to send MSIs. However, the system is responsible for ensuring that the DeviceID reaching each ITS is not spoofed by rogue software using either a < x > user signals or MSI-64. See 2.4 MSI-64 Encapsulator on page 2-38.

If the ITS is placed downstream of an ACE interconnect, care must be taken to avoid system deadlock. For more information, see the chapter describing Key Integration points in the *Arm*<sup>®</sup>*CoreLink*<sup>™</sup> *GIC-600 Generic Interrupt Controller Configuration and Integration Manual.*

See 3.10 Interrupt translation service (ITS) on page 3-64 for more information about each inner block.

This section contains the following subsections:

- 2.3.1 ITS ACE-Lite slave interface on page 2-33.

- 2.3.2 ITS ACE-Lite master interface on page 2-35.

- 2.3.3 ITS AXI4-Stream interface on page 2-36.

- 2.3.4 ITS Q-Channel on page 2-36.

- 2.3.5 ITS miscellaneous signals on page 2-36.

- 2.3.6 ITS configuration on page 2-36.

## 2.3.1 ITS ACE-Lite slave interface

The ITS AMBA AXI4 ACE-Lite slave interface has a configurable width of 64 bits, 128 bits, or 256 bits. The slave, master, and address data widths must match.

The ITS ACE-Lite slave port contains only the GITS\_TRANSLATER register. See the *Arm*<sup>®</sup> *Generic Interrupt Controller Architecture Specification, GIC architecture version 3.0 and version 4.0* for more information.

If the bypass switch configuration option is selected, the port accepts all ACE-Lite traffic, and filters accesses to the ITS based on an address match set by the ITS base address tie-off **target\_address[<n>ADDR\_WIDTH-17:0]**. Without the bypass switch, the upper bits of the address, 16 and above, are ignored, and the system address decoders must ensure that only relevant ITS writes arrive at the ITS.

The ACE-Lite slave interface ignores all **a**<**x**>**snoop**, **a**<**x**>**cache**, **a**<**x**>**domain**, and **a**<**x**>**prot** information other than to filter CMOs and Barriers to ensure that it replies in a protocol-compliant manner.

To generate an LPI, the ITS requires the DeviceID of the issuing master. For PCIe, the DeviceID is derived from the RequestorID.

The GIC-600 supports two different methods for deriving the DeviceID:

- When using the MSI-64 config parameter, the write to GITS\_TRANSLATER is converted to 64-bit accesses at an unmapped system address and the DeviceID is transferred in the upper 32 bits of the access. In this case, only burst length 1, 64-bit ACE-Lite writes are accepted.

- When not using MSI-64, the DeviceID is transported on the **AWUSER** bus with the address (AW) phase of the register access. In this case, burst length 1, 32-bit or 16-bit writes are accepted.

The DeviceID must be transferred using a method that cannot be spoofed by malicious software.

\_\_\_\_\_ Note \_\_\_\_\_

These two modes cannot be mixed on a single ITS.

If the bypass switch is configured, it includes a transaction tracker that ensures PCIe ordering requirements are met. There are two options that are based on the full\_bypass\_tracker tag:

0 = A simple scheme is used, which ensures that all previous transactions sent downstream have completed before forwarding an MSI to the ITS, and conversely, that the ITS has accepted all MSIs before continuing to send traffic downstream.

1 = A more complex scheme, which allows continuous downstream traffic including interleaved MSIs, unless the buffer slots become full. There are two buffers, bypass\_max\_outstanding, which specifies the number of concurrent downstream transactions allowed and bypass\_interrupt\_count, which specifies the number of concurrent MSIs that can be waiting for their prerequisite transactions to complete.

\_\_\_\_\_ Note \_\_\_\_\_

The ITS slave port contains only write-only registers, therefore the read channel always uses the simple transaction tracker.

If the bypass switch is configured, the slave and master ports must both have the same data width and the same address width.

If the Distributor and ITS both share the ACE-Lite slave port, the port properties match those of the Distributor ACE-Lite slave port, which are described in 2.1.2 Distributor ACE-Lite slave interface on page 2-24.

The following table shows the acceptance capabilities of the ITS ACE-Lite slave interface.

| Attribute                      | With bypass switch                                       | Without bypass switch |

|--------------------------------|----------------------------------------------------------|-----------------------|

| Combined acceptance capability | Read acceptance capability + Write acceptance capability | 3                     |

| Read acceptance capability     | 128                                                      | 1                     |

| Read data reorder depth        | 128                                                      | 1                     |

| Write acceptance capability    | 128 or bypass_max_outstanding                            | 2                     |

## Table 2-10 ITS ACE-Lite slave interface acceptance capabilities

The ITS ACE-Lite slave interface has an associated **awakeup** signal. To ensure that incoming traffic wakes the ITS correctly when it is clock gated hierarchically through the Q-Channel, **awakeup** must be driven from a registered version of **awvalid** and **arvalid**. To prevent spurious wake events, ensure that the **awakeup** signal is registered cleanly.

## 2.3.2 ITS ACE-Lite master interface

The ITS AMBA AXI4 ACE-Lite master interface has a configurable width of 64 bits, 128 bits, or 256 bits. If the bypass switch is not included, the ID width is 4 bits, otherwise the ID width is one more than the ID width of the corresponding input channel.

The ACE-Lite master port issues accesses to the ITS private tables and Command queue. If the bypass switch is configured, the port also forwards transactions from the slave interface. The ACE-Lite bus can issue I/O coherent transactions, therefore you can place these tables in shared memory if required. Placing the Command queue in shared memory avoids having to flush the cache before executing ITS commands.

## \_\_\_\_\_ Note \_\_\_\_\_

- When heavily loaded, the ITS creates a necessary dependency between writes on its slave port and reads on its master port. You must ensure that any writes that back up to the slave port do not prevent the free-flow of both reads and writes to the memory.

- In an ACE system, you must ensure that the write channel from any core cache that could be snooped is not blocked by accesses to the ITS slave port. If the write channel is blocked, and the snoop is prevented from completing its task, a potential deadlock can result.

Arm recommends that if you place the ITS downstream of an ACE interconnect, then you must not place tables in shareable memory.

The ITS can issue the following transaction types:

- 256-bit aligned read to the Command queue.

- 64-bit aligned read and write to the Device table.

- 32-bit aligned read and write to the Interrupt Translation Table (ITT).

- 16-bit aligned read and write to the Collection table.

- If the bypass switch is configured, any bypassed transactions from the slave port.

ITS issued transactions output the DeviceID on the  $a < x>user_signals$ . The DeviceID is used for information and does not have to be routed anywhere if it is not required. If the bypass switch is included, ITS issued transactions are identified by a value of 0 on a < x>id[0].

\_\_\_\_\_ Note \_\_\_\_\_

The ITS issues only one outstanding transaction per ID. This gives a maximum of one outstanding write and five outstanding reads, excluding any transactions from the slave port. If this port is combined with the Distributor ACE-Lite master port, some of these properties are changed. See *Figure 2-8 GIC-600 top-level structure options* on page 2-46 for more information.

For more information, see Arm® GICv3 and GICv4 Software Overview.

## 2.3.3 ITS AXI4-Stream interface

The ITS AXI4-Stream interface is a bi-directional AXI4-Stream interface of either 16-bit or 64-bit width for communication between the ITS and the GIC Distributor components on the same chip.

Arm expects a typical distributed system to be 16 bits wide. When a pre-existing wide interconnect is used, the 64-bit option allows messages to be efficiently packed.

The interface is fully credited so all messages can be accepted without dependency on any other ports.

## 2.3.4 ITS Q-Channel

The ITS has a Q-Channel interface which controls requests from an external clock gating source.

If the ITS is busy, the Q-Channel interface asserts the **qdeny** signal to deny an external request to gate its clock. When an external request occurs, the interface requests a wakeup by asserting **qactive**.

The qreqn input is synchronized to the ITS. See A.2 Power control signals on page Appx-A-188.

## **Related reference**

A.2 Power control signals on page Appx-A-188

## 2.3.5 ITS miscellaneous signals

The ITS generates or processes several signals, such as an ID tie-off, and the ITS page offset.

## Table 2-11 ITS miscellaneous signals

| Signal                                      | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| target_address<br>[ <n>ADDR_WIDTH-17:0]</n> | Input     | Modifies the address map to ensure only writes to the correct location trigger MSI requests. Only present when the bypass switch is configured.                                                                                                                                                                                                                                              |

|                                             |           | Specifies the 64K page address that includes the GITS_TRANSLATER register address, and is matched against <b>axaddr[ADDR_WIDTH-1:16]</b> .                                                                                                                                                                                                                                                   |

| its_id                                      | Input     | This is an ID tie-off. It must be tied to the <b>ic</b> < <b>x</b> > <b>dtdest</b> value used to read the ITS on the AXI4-Stream interface. This ID value feeds into the GITS_CFGID register and is used to check that the GIC system is correctly interconnected. If top-level stitching is used, which creates a hierarchical level from the other components, this signal is not visible. |

| its_transr_page_offset                      | Input     | This tie-off signal is used to set the page address of the GITS_TRANSLATER register.<br>Only present in monolithic configurations.                                                                                                                                                                                                                                                           |

## 2.3.6 ITS configuration

You can configure several options that relate to the operation of the ITS block.

## Table 2-12 Configurable options for the ITS

| Feature                                        | Range of options |

|------------------------------------------------|------------------|

| DeviceID                                       | 3-20             |

| For more information, see 2.3 ITS on page 2-32 |                  |

| EventID size                                   | 1-16             |

| For more information, see 2.3 ITS on page 2-32 |                  |

| Bypass_ports                                   | 1 or 0           |

| ACE-Lite data width                            | 64, 128, or 256  |

| MSI-64 support                                 | True or False    |

# Table 2-12 Configurable options for the ITS (continued)

| Feature                                                                                       | Range of options                                  |

|-----------------------------------------------------------------------------------------------|---------------------------------------------------|

| ACE-Lite read ID width                                                                        | 1-32                                              |

| ACE-Lite write ID width                                                                       | 1-32                                              |

| ECC support                                                                                   | True or False                                     |

| For more information, see 3.16 Reliability, Accessibility, and Serviceability on page 3-74.   |                                                   |

| DID cache size                                                                                | 2, 4, 8, 16, 32, 64, or 128                       |

| DID and VID cache size                                                                        | 2, 4, 8, 16, 32, 64, 128, 256, 512, 1024, or 2048 |

| Collection cache size                                                                         | 2, 4, 8, 16, 32, 64, 128, 256, or 512             |

| Domain                                                                                        | Any legal domain identifier                       |

| For more information, see <i>Figure 2-8 GIC-600 top-level structure options</i> on page 2-46. |                                                   |

For more information, see Arm® GICv3 and GICv4 Software Overview.

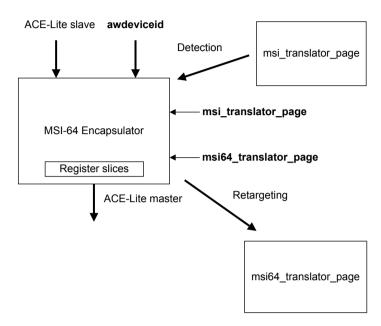

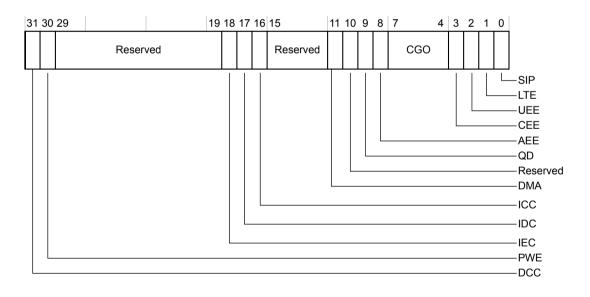

# 2.4 MSI-64 Encapsulator

The MSI-64 Encapsulator reduces system wiring by combining the DeviceID onto the Data bus for writes to the GITS\_TRANSLATER register.

The following figure shows an overview of the MSI-64 Encapsulator process.

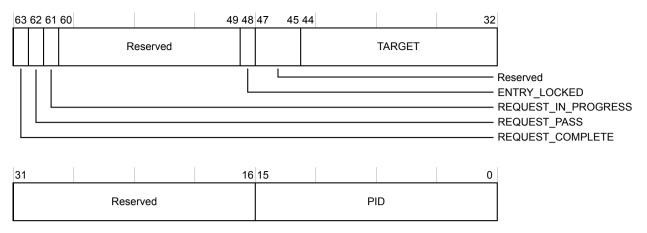

### Figure 2-5 MSI-64 Encapsulator