## Arm<sup>®</sup> CoreLink<sup>™</sup> MMU-600 System Memory Management Unit

Revision: r0p1

**Technical Reference Manual**

## Arm<sup>®</sup> CoreLink<sup>™</sup> MMU-600 System Memory Management Unit

#### **Technical Reference Manual**

Copyright © 2016, 2017 Arm Limited (or its affiliates). All rights reserved.

#### Release Information

#### **Document History**

| Issue   | Date             | Confidentiality  | Change                  |

|---------|------------------|------------------|-------------------------|

| 0000-00 | 16 December 2016 | Confidential     | First release for r0p0  |

| 0000-01 | 19 May 2017      | Confidential     | Second release for r0p0 |

| 0001-00 | 23 August 2017   | Confidential     | First release for r0p1  |

| 0001-01 | 10 November 2017 | Non-Confidential | Second release for r0p1 |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or TM are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at http://www.arm.com/company/policies/trademarks.

Copyright © 2016, 2017 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

#### LES-PRE-20349

### **Additional Notices**

Some material in this document is based on IEEE 754-2008 IEEE Standard for Binary Floating-Point Arithmetic. The IEEE disclaims any responsibility or liability resulting from the placement and use in the described manner.

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

#### **Product Status**

The information in this document is Final, that is for a developed product.

#### Web Address

http://www.arm.com

## Contents

# **Arm® CoreLink™ MMU-600 System Memory Management Unit Technical Reference Manual**

|           | Pref  | face                                  |      |

|-----------|-------|---------------------------------------|------|

|           |       | About this book                       |      |

|           |       | Feedback                              |      |

| Chapter 1 | Intro | oduction                              |      |

|           | 1.1   | About the MMU-600                     | 1-12 |

|           | 1.2   | Compliance                            | 1-13 |

|           | 1.3   | Features                              | 1-14 |

|           | 1.4   | Interfaces                            | 1-10 |

|           | 1.5   | Configurable options                  | 1-1  |

|           | 1.6   | Product documentation and design flow | 1-18 |

|           | 1.7   | Product revisions                     | 1-20 |

| Chapter 2 | Fun   | ctional description                   |      |

|           | 2.1   | About the functions                   | 2-22 |

|           | 2.2   | Interfaces                            | 2-28 |

|           | 2.3   | Operation                             | 2-36 |

|           | 2.4   | Constraints and limitations of use    | 2-48 |

| Chapter 3 | Prog  | grammers model                        |      |

|           | 3.1   | About the programmers model           | 3-58 |

|           | 3.2   | SMMU architectural registers          | 3-57 |

|           |       |                                       |      |

|            | 3.3   | MMU-600 memory map                            | 3-61       |

|------------|-------|-----------------------------------------------|------------|

|            | 3.4   | Register summary                              | 3-63       |

|            | 3.5   | TCU Component and Peripheral ID Registers     | 3-66       |

|            | 3.6   | TCU PMU Component and Peripheral ID Registers | 3-67       |

|            | 3.7   | TCU microarchitectural registers              | 3-68       |

|            | 3.8   | TCU RAS registers                             | 3-76       |

|            | 3.9   | TBU Component and Peripheral ID Registers     | 3-81       |

|            | 3.10  | TBU PMU Component and Peripheral ID Registers | 3-82       |

|            | 3.11  | TBU microarchitectural registers              | 3-83       |

|            | 3.12  | TBU RAS registers                             | 3-85       |

| Appendix A | Sign  | al descriptions                               |            |

|            | A.1   | Clock and reset signals                       | Appx-A-90  |

|            | A.2   | TCU QTW/DVM interface signals                 | Appx-A-91  |

|            | A.3   | TCU programming interface signals             | Appx-A-93  |

|            | A.4   | TCU SYSCO interface signals                   | Appx-A-94  |

|            | A.5   | TCU PMU snapshot interface signals            |            |

|            | A.6   | TCU LPI_PD interface signals                  | Appx-A-96  |

|            | A.7   | TCU LPI_CG interface signals                  | Appx-A-97  |

|            | A.8   | TCU DTI interface signals                     | Appx-A-98  |

|            | A.9   | TCU interrupt signals                         | Appx-A-99  |

|            | A.10  | TCU tie-off signals                           | Appx-A-100 |

|            | A.11  | TCU and TBU test and debug signals            | Appx-A-101 |

|            | A.12  | TBU TBS interface signals                     | Appx-A-102 |

|            | A.13  | TBU TBM interface signals                     | Appx-A-104 |

|            | A.14  | TBU PMU snapshot interface signals            | Appx-A-106 |

|            | A.15  | TBU LPI_PD interface signals                  | Appx-A-107 |

|            | A.16  | TBU LPI_CG interface signals                  | Appx-A-108 |

|            | A.17  | TBU DTI interface signals                     | Appx-A-109 |

|            | A.18  | TBU interrupt signals                         | Appx-A-110 |

|            | A.19  | TBU tie-off signals                           | Аррх-А-111 |

|            | A.20  | DTI interconnect switch signals               | Appx-A-113 |

|            | A.21  | DTI interconnect sizer signals                | Appx-A-115 |

|            | A.22  | DTI interconnect register slice signals       | Appx-A-117 |

| Appendix B | Softv | ware initialization examples                  |            |

|            | B.1   | Initializing the SMMU                         | Аррх-В-120 |

|            | B.2   | Enabling the SMMU                             |            |

| Appendix C | Revi  | sions                                         |            |

|            | C.1   | Revisions                                     | Appx-C-127 |

## **Preface**

This preface introduces the  $Arm^*$   $CoreLink^*$  MMU-600 System Memory Management Unit Technical Reference Manual.

It contains the following:

- About this book on page 7.

- Feedback on page 10.

#### About this book

This book is for the Arm® CoreLink™ MMU-600 System Memory Management Unit.

#### **Product revision status**

The rmpn identifier indicates the revision status of the product described in this book, for example, r1p2, where:

- rm Identifies the major revision of the product, for example, r1.

- pn Identifies the minor revision or modification status of the product, for example, p2.

#### Intended audience

This book is written for system designers, system integrators, and programmers who are designing or programming a System-on-Chip (SoC) that uses the MMU-600.

## Using this book

This book is organized into the following chapters:

#### **Chapter 1 Introduction**

This chapter provides an overview of the MMU-600.

#### **Chapter 2 Functional description**

This chapter describes the functionality of the MMU-600.

#### Chapter 3 Programmers model

This chapter describes the MMU-600 programmers model.

## Appendix A Signal descriptions

This appendix describes the MMU-600 external signals.

#### Appendix B Software initialization examples

This appendix provides examples of how software can initialize and enable the MMU-600.

#### Appendix C Revisions

This appendix describes the technical changes between released issues of this book.

#### Glossary

The Arm® Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

See the *Arm*<sup>®</sup> *Glossary* for more information.

#### Typographic conventions

italic

Introduces special terminology, denotes cross-references, and citations.

#### bold

Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.

#### monospace

Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.

#### <u>mono</u>space

Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.

## monospace italic

Denotes arguments to monospace text where the argument is to be replaced by a specific value.

#### monospace bold

Denotes language keywords when used outside example code.

<and>

Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:

```

MRC p15, 0, <Rd>, <CRn>, <CRm>, <Opcode_2>

```

SMALL CAPITALS

Used in body text for a few terms that have specific technical meanings, that are defined in the *Arm*<sup>®</sup> *Glossary*. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE.

## **Timing diagrams**

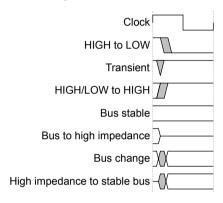

The following figure explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

Figure 1 Key to timing diagram conventions

### **Signals**

The signal conventions are:

#### Signal level

The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals.

- · LOW for active-LOW signals.

#### Lowercase n

At the start or end of a signal name denotes an active-LOW signal.

## **Additional reading**

This section lists publications by Arm and by third parties.

See Infocenter http://infocenter.arm.com, for access to Arm documentation.

#### Arm publications

This book contains information that is specific to this product. See the following documents for other relevant information:

- Arm® System Memory Management Unit Architecture Specification, SMMU architecture version 3.0 and version 3.1 (IHI 0070).

- Arm® Architecture Reference Manual, ARMv8, for ARMv8-A architecture profile (DDI 0487).

- Arm® AMBA® Distributed Translation Interface (DTI) Protocol Specification (100225).

- Arm® AMBA® APB Protocol Specification (IHI 0024).

- Arm<sup>®</sup> CoreSight<sup>™</sup> Architecture Specification (IHI 0029).

- Arm® AMBA® AXI and ACE Protocol Specification (IHI 0022F).

- Arm® AMBA® 4 AXI4-Stream Protocol Specification (IHI 0051).

- AMBA® Low Power Interface Specification, Arm® Q-Channel and P-Channel Interfaces (IHI 0068).

- Arm® CoreLink™ LPD-500 Low Power Distributor Technical Reference Manual (100361).

- Arm® Server Base System Architecture (DEN-0029).

The following confidential books are only available to licensees:

- Arm<sup>®</sup> CoreLink<sup>™</sup> MMU-600 System Memory Management Unit Configuration and Integration Manual (100311).

- Arm<sup>®</sup> CoreLink<sup>™</sup> ADB-400 AMBA<sup>®</sup> Domain Bridge User Guide (DUI 0615).

### **Feedback**

## Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- The title Arm CoreLink MMU-600 System Memory Management Unit Technical Reference Manual.

- The number 100310 0001 01 en.

- If applicable, the page number(s) to which your comments refer.

- A concise explanation of your comments.

| Arm also welcomes general suggestions for additions and improvements.                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note                                                                                                                                                          |

| Arm tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader. |

## Chapter 1 **Introduction**

This chapter provides an overview of the MMU-600.

It contains the following sections:

- 1.1 About the MMU-600 on page 1-12.

- 1.2 Compliance on page 1-13.

- 1.3 Features on page 1-14.

- 1.4 Interfaces on page 1-16.

- 1.5 Configurable options on page 1-17.

- 1.6 Product documentation and design flow on page 1-18.

- 1.7 Product revisions on page 1-20.

### 1.1 About the MMU-600

The MMU-600 is a *System*-level *Memory Management Unit* (SMMU) that translates an input address to an output address. This translation is based on address mapping and memory attribute information that is available in the MMU-600 internal registers and translation tables.

The MMU-600 implements the Arm SMMU architecture version 3.1, SMMUv3.1, as defined by the *Arm® System Memory Management Unit Architecture Specification, SMMU architecture version 3.0 and version 3.1*.

An address translation from an input address to an output address is described as a stage of address translation. The MMU-600 can perform:

- Stage 1 translations that translate an input *virtual address* (VA) to an output *physical address* (PA) or *intermediate physical address* (IPA).

- Stage 2 translations that translate an input IPA to an output PA.

- Combined stage 1 and stage 2 translations that translate an input VA to an IPA, and then translate that IPA to an output PA. The MMU-600 performs translation table walks for each stage of the translation.

In addition to translating an input address to an output address, a stage of address translation also defines the memory attributes of the output address. With a two-stage translation, the stage 2 translation can modify the attributes that the stage 1 translation defines. A stage of address translation can be disabled or bypassed, and the MMU-600 can define memory attributes for disabled and bypassed stages of translation.

The MMU-600 uses inputs from the requesting master to identify a context. Configuration tables in memory tell the MMU-600 how to translate each context, such as which translation tables to use.

The MMU-600 can cache the result of a translation table lookup in a *Translation Lookaside Buffer* (TLB). It can also cache configuration tables in a configuration cache.

The MMU-600 contains the following key components:

- Translation Buffer Units (TBUs) that use a TLB to cache translation tables.

- A Translation Control Unit (TCU) that controls and manages address translations.

- *Distributed Translation Interface* (DTI) interconnect components that connect multiple TBUs to the TCU.

#### Related concepts

2.1 About the functions on page 2-22.

## 1.2 Compliance

The MMU-600 complies with, or implements, the specifications that this section describes. This *Technical Reference Manual* (TRM) complements architecture reference manuals, architecture specifications, protocol specifications, and relevant external standards. It does not duplicate information from these sources.

#### 1.2.1 Arm® architecture

The MMU-600 implements parts of the ARMv8 *Virtual Memory System Architecture* (VMSA), as defined by the *Arm® Architecture Reference Manual, ARMv8, for ARMv8-A architecture profile*. The SMMUv3 architecture describes the parts of VMSA that apply to the MMU-600.

#### 1.2.2 SMMU architecture

The MMU-600 implements the SMMUv3.1 architecture, as defined by the *Arm*<sup>®</sup> *System Memory Management Unit Architecture Specification, SMMU architecture version 3.0 and version 3.1.*

#### Related concepts

2.4.1 SMMUv3 support on page 2-48.

## 1.2.3 AMBA® DTI protocol

The MMU-600 implements the *Distributed Translation Interface* (DTI) protocol, as defined by the *Arm*<sup>®</sup> *AMBA*<sup>®</sup> *Distributed Translation Interface* (DTI) *Protocol Specification*.

The DTI interfaces use an AXI4-Stream interface, as defined by the *Arm*\* *AMBA*\* *4 AXI4-Stream Protocol Specification*.

## **Related concepts**

2.3.2 DTI overview on page 2-42.

#### 1.2.4 AMBA® ACE-Lite and AMBA® AXI5 protocol

The MMU-600 complies with the AMBA ACE-Lite protocol. It also supports certain functionality from the AMBA 5 AXI protocol, AXI5.

See the Arm® AMBA® AXI and ACE Protocol Specification for more information.

#### Related references

2.4.2 AMBA support on page 2-51.

### 1.2.5 AMBA® APB protocol

The MMU-600 complies with the AMBA APB4 protocol, as defined by the *Arm® AMBA® APB Protocol Specification*.

### 1.3 Features

The MMU-600 provides the following features:

- Compliance with the SMMUv3.1 architecture:

- Support for Stage 1 translation, Stage 2 translation, and Stage 1 followed by stage 2 translation.

- Support for ARMv8 AArch32 and AArch64 translation table formats.

- Support for 4KB, 16KB and 64KB granule sizes in AArch64 format.

- Masters can be stalled while a processor handles translation faults, enabling software support for demand paging.

- Configuration tables in memory can support millions of active translation contexts.

- Queues in memory perform MMU-600 management, no requirement to stall a processor when it accesses the MMU-600.

- Support for PCI Express (PCIe) integration, including Address Translation Services (ATS) and Process Address Space IDs (PASIDs).

- Support for *Generic Interrupt Controller* (GIC) integration, with *Message Signaled Interrupts* (MSIs) supported for common interrupt types.

- A *Performance Monitoring Unit* (PMU) in each TBU and TCU that enables MMU-600 performance to be investigated.

- Reliability, Serviceability and Availability (RAS) features for cache corruption detection and correction.

- Support for AMBA interfaces, including:

- ACE5-Lite TBU transaction interfaces that support cache stash transactions, deallocating transactions, and cache maintenance.

- An architected AXI5 extension that communicates per-transaction translation stream information.

- An ACE5-Lite + Distributed Virtual Memory (DVM) TCU table walk interface that enables ARMv8.2 processors to perform shared TLB invalidate operations without accessing the MMU-600 directly.

- An ACE5 Low Power extension that enables the TCU to subscribe to DVM TLB invalidate requests on powerup and powerdown without reprogramming the DTI interconnect.

- AMBA DTI communication between the TCU and TBUs, enabling masters to request translations and implement TBU functionality internally.

- Support for the AMBA *Low-Power Interface* (LPI) Q-Channel so that standard controllers can control power and clock gating.

- AXI5 WAKEUP signaling on all interfaces, including DTI and APB interfaces.

- Support for flexible integration:

- A configurable number of TBUs can be placed close to the masters being translated.

- Communication between TBU and TCU over AXI4-Stream, supported using the supplied DTI interconnect components, or any other AXI4-Stream interconnect.

- DTI interconnect components support hierarchical topologies, and control of the tradeoff between number of wires and DTI bandwidth.

- Support for high-performance translation:

- Scalable configurable micro TLB and Main TLB in the TBU can reduce the number of translation requests to the TCU.

- Optimization to store all architecturally defined page and block sizes, including contiguous page and block entries, as a single entry in the TBU and TCU TLBs.

- Per-TBU prioritization in the TCU enable high-priority transaction streams to be translated before low-priority streams.

- *Hit-Under-Miss* (HUM) support in the TBU enables transactions with different AXI IDs to be propagated out of order, when a translation is available.

- TBU detection of multiple transactions that require the same translation so that only one TBU request to the TCU is required.

- TCU detection of multiple translations that require the same table in memory so that only one TCU memory request is required.

- Multi-level, multi-stage walk caches in the TCU reduce translation cost by performing only part

of the table walk process on a miss.

- A configurable number of concurrent translations in the TBU and TCU promotes high translation throughput.

## 1.4 Interfaces

Both the TCU and TBU support the following common interfaces:

- DTI.

- Tie-offs.

- Interrupts.

- PMU snapshot.

- Test and debug.

- · LPI clock gating.

- LPI powerdown.

The TCU also supports the following interfaces:

- · Programming.

- System coherency.

- Queue and Table Walk (QTW)/DVM.

The TBU also supports the following interfaces:

- Transaction slave (TBS).

- Transaction master (TBM).

## **Related concepts**

2.2 Interfaces on page 2-28.

## 1.5 Configurable options

The MMU-600 is highly configurable and provides configuration options for each of the main blocks.

For the TCU, you can configure:

- The size of each of the caches.

- The data width of the QTW/DVM interface.

- The number of translations that can be performed at the same time.

- The number of translation requests that can be accepted from all DTI masters.

For the TBU, you can configure:

- Write data buffer depth.

- The size of each of the caches.

- The number of transactions that can be translated at the same time.

- The number of outstanding read and write transactions that the TBM interface supports.

- The width of data, ID, user, StreamID, and SubstreamID signals on the TBS and TBM interfaces.

| Note                                                  |  |

|-------------------------------------------------------|--|

| Depths are specified as a discrete number of entries. |  |

| <del></del>                                           |  |

You can also configure the DTI interconnect components to meet your system requirements.

## 1.6 Product documentation and design flow

This section describes the MMU-600 documentation in relation to the design flow.

#### 1.6.1 Documentation

The MMU-600 documentation is as follows:

#### **Technical Reference Manual**

The *Technical Reference Manual* (TRM) describes the functionality and the effects of functional options on the behavior of the MMU-600. It is required at all stages of the design flow. The choices that are made in the design flow can mean that some behaviors that are described in the TRM are not relevant. If you are programming the MMU-600, then contact:

- The implementer to determine:

- The build configuration of the implementation.

- What integration, if any, was performed before implementing the MMU-600.

- The integrator to determine the pin configuration of the device that you are using.

#### **Configuration and Integration Manual**

The Configuration and Integration Manual (CIM) describes:

- The available build configuration options and related issues in selecting them.

- How to integrate the MMU-600 into a SoC. This section includes describing the pins that the integrator must tie off to configure the macrocells for the required integration.

- The processes to sign off the configuration, integration, and implementation of the design.

The Arm product deliverables include reference scripts and information about using them to implement your design. Reference methodology flows that Arm supplies are example reference implementations. Contact your EDA vendor for EDA tool support.

The CIM is a confidential book that is only available to licensees.

### 1.6.2 Design flow

The MMU-600 is delivered as synthesizable RTL. Before it can be used in a product, it must go through the following processes:

#### **Implementation**

The implementer configures and synthesizes the RTL to produce a hard macrocell. This process might include integrating RAMs into the design.

## Integration

The integrator connects the implemented design into a SoC. Integration includes connecting the design to a memory system and peripherals.

#### **Programming**

The system programmer develops the software to configure and initialize the MMU-600, and tests the required application software.

Each process is separate, and can include implementation and integration choices that affect the behavior and features of the MMU-600.

The operation of the final device depends on:

#### **Build configuration**

The implementer chooses the options that affect how the RTL source files are pre-processed. These options usually include or exclude logic that affects one or more of the following:

- Area

- Maximum frequency.

- Features of the resulting macrocell.

### **Configuration inputs**

The integrator configures some features of the MMU-600 by tying inputs to specific values. These configurations affect the start-up behavior before any software configuration is made. They can also limit the options that are available to the software, for example, by enabling QoS features.

## **Software configuration**

The programmer configures the MMU-600 by programming particular values into registers. This configuration affects the behavior of the MMU-600.

## **Related concepts**

1.5 Configurable options on page 1-17.

### Related references

1.2 Compliance on page 1-13.

## 1.7 Product revisions

This section describes the differences in functionality between product revisions:

r0p0

First release.

## r0p0-r0p1

The following changes apply to this release:

- Modified bits in TCU\_CTRL.

- Modified bits in TBU\_CTRL.

# **Chapter 2 Functional description**

This chapter describes the functionality of the MMU-600.

It contains the following sections:

- 2.1 About the functions on page 2-22.

- 2.2 Interfaces on page 2-28.

- 2.3 Operation on page 2-36.

- 2.4 Constraints and limitations of use on page 2-48.

### 2.1 About the functions

The major functional blocks of the MMU-600 are the TCU, TBU, and DTI interconnect.

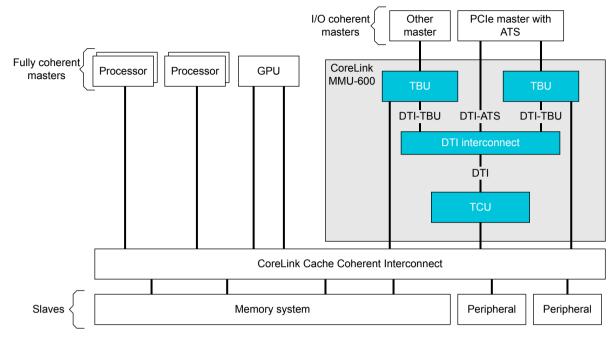

The following figure shows an example system that uses the MMU-600.

Figure 2-1 Example system with the MMU-600

The MMU-600 contains the following key components:

#### Translation Buffer Unit (TBU)

The TBU contains *Translation Lookaside Buffers* (TLBs) that cache translation tables. The MMU-600 implements at least one TBU for each connected master, and these TBUs are local to the corresponding master.

#### Translation Control Unit (TCU)

The TCU controls and manages the address translations. The MMU-600 implements a single TCU. In MMU-600-based systems, the AMBA DTI protocol defines the standard for communicating with the TCU.

#### **DTI** interconnect

The DTI interconnect connects multiple TBUs to the TCU.

When an MMU-600 TBU receives a transaction on the TBS interface, it looks for a matching translation in its TLBs. If it has a matching translation, it uses it to translate the transaction and outputs the transaction on the TBM interface. If it does not have a matching translation, it requests a new translation from the TCU using the DTI interface.

When the TCU receives a DTI translation request, it uses the QTW interface to perform:

- Configuration table walks, which return configuration information for the translation context.

- Translation table walks, which return translation information specific to the transaction address.

The TCU contains caches that reduce the number of configuration and translation table walks that are to be performed. Sometimes no walks are required.

When the TBU receives the translation from the TCU, it stores it in its TLBs. If the translation was successful, the TBU uses it to translate the transaction, otherwise it terminates it.

A processor controls the TCU by:

- Writing commands to a Command queue in memory.

- Receiving events from an Event queue in memory.

- Writing to its configuration registers using the programming interface.

See the Arm® System Memory Management Unit Architecture Specification, SMMU architecture version 3.0 and version 3.1 for more information about translation and how software communicates with the TCU.

This section contains the following subsections:

- 2.1.1 Translation Control Unit (TCU) on page 2-23.

- 2.1.2 Translation Buffer Unit (TBU) on page 2-25.

- 2.1.3 DTI interconnect on page 2-26.

## 2.1.1 Translation Control Unit (TCU)

A typical SMMUv3-based system includes a single TCU. The TCU is usually the largest block in the system, and performs several roles.

#### The TCU:

- · Manages the memory queues.

- Performs translation table walks.

- Performs configuration table walks.

- Implements backup caching structures.

- Implements the SMMU programmers model.

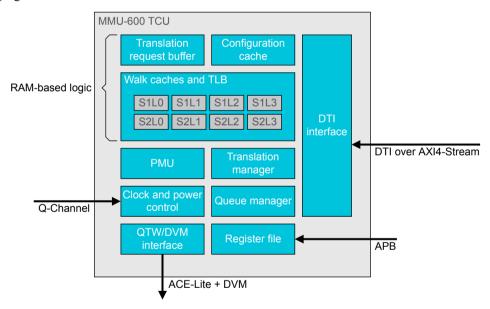

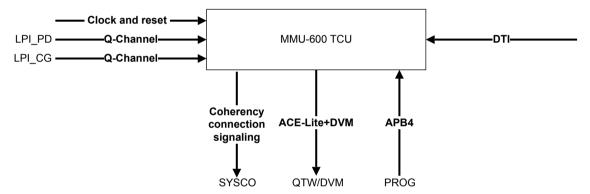

The following figure shows the TCU.

Figure 2-2 MMU-600 TCU

The TCU consists of:

#### Walk caches

The TCU includes separate four-way set-associative walk caches to store results of translation table walks. During MMU-600 configuration, the cache line entries are split to create separate walk caches that are reserved for:

- Stage 1 level 0 table entries.

- Stage 1 level 1 table and block entries.

- Stage 1 level 2 table and block entries.

- Stage 1 level 3 table entries.

- Stage 2 level 0 table entries.

- Stage 2 level 1 table and block entries.

- Stage 2 level 2 table and block entries.

- Stage 2 level 3 table entries.

To enable and disable the walk cache for a particular stage and level of translation, use the TCU\_CTRL register. If an error occurs for a cache line entry, the TCU\_ERRSTATUS register identifies the affected entry.

The walk cache is useful in cases where a translation request results in a miss in other TCU caches. A subsequent hit in the walk cache requires only a single memory access to complete the translation table walk and fetch the required descriptor.

## Configuration cache

The configuration caches are 4-way set-associative cache structures that store configuration information. Each entry stores the *Context Descriptor* (CD) and *Stream Table Entry* (STE) contents for a translation context.

| Note |

|------|

|------|

The configuration cache does not cache the contents of intermediate configuration tables.

## Translation manager

The translation manager manages translation requests that are in progress. All translation table walks and configuration table walks are hazard-checked to reduce the possibility of multiple transactions requesting duplicate walks.

## Translation request buffer

The translation request buffer stores translation requests from TBUs when all translation manager slots are full. The translation request buffer supports more slots than the translation manager. When correctly configured, this buffer has enough space to store all translation requests that TBUs can issue simultaneously. This buffer therefore prevents the DTI interface from becoming blocked.

#### **PMU**

The PMU counts TCU performance-related events.

#### Clock and power control

The TCU has its own clock and power control, provided by the Q-Channel.

#### Queue manager

The queue manager manages all SMMUv3 Command queues and Event queues that are stored in memory.

#### QTW/DVM interface

The Queue and Table Walk (QTM)/Distributed Virtual Memory (DVM) interface is an ACE-Lite +DVM master interface.

## Register file

The register file implements the SMMUv3 programmers model, as defined by the *Arm® System Memory Management Unit Architecture Specification, SMMU architecture version 3.0 and version 3.1*.

#### DTI interface

The slave DTI interface uses the DTI protocol, typically over AXI4-Stream, to enable the TCU to communicate with a master component. For the MMU-600, the master component is either a TBU or a PCIe master.

## **Related concepts**

2.2 Interfaces on page 2-28.

#### Related references

3.2 SMMU architectural registers on page 3-57.

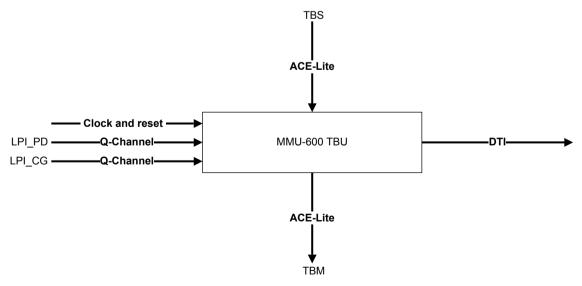

## 2.1.2 Translation Buffer Unit (TBU)

A typical SMMUv3-based system includes multiple TBUs. Each TBU is located close to the component that it provides address translation for.

A TBU intercepts transactions and provides the required translation from a *Translation Lookaside Buffer* (TLB) if possible. If a TLB does not contain the required translation, the TBU requests translations from the TCU and then caches the translation in one of the TLBs.

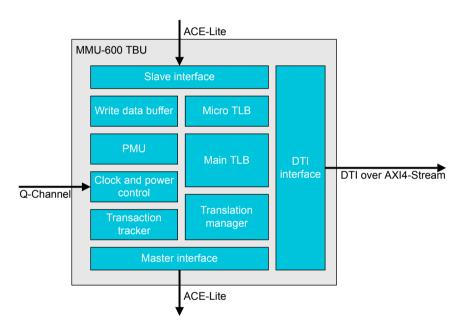

The following figure shows the TBU.

Figure 2-3 MMU-600 TBU

The TBU consists of:

#### Master and slave interfaces

These interfaces manage the TBS and TBM interfaces.

#### Micro TLB

The TBU compares incoming transactions with translations that are cached in the micro TLB before looking in the *Main TLB* (MTLB). The micro TLB is a fully associative TLB that provides configuration cache and TLB functionality. You can use a tie-off signal to configure the cache replacement policy as either round-robin or *Pseudo Least Recently Used* (PLRU).

## Main TLB

Each TBU includes an optional *Main TLB* (MTLB) that caches translation table walk entries from:

- Stage 1 translations.

- Stage 2 translations.

- Stage 1 combined with stage 2 translations.

The MTLB is a configurable four-way set associative cache structure that uses a random cache replacement policy.

If multiple translation sizes are in use, a single transaction might require multiple lookups. Lookups are pipelined to permit a sustained rate of one lookup per cycle.

#### Translation manager

The translation manager manages translation requests that are in progress. Each transaction occupies a translation slot until it is propagated downstream through the master interface. All transactions are hazard-checked to reduce the possibility of duplicate translation requests being sent to the TCU.

There is no restriction on the ordering of transactions with different AXI IDs. Transactions with different AXI IDs can be propagated downstream out-of-order.

All transactions with a given AXI ID value must remain ordered. The translation manager propagates such transactions when the translation is ready, provided no other transaction with the same AXI ID is already waiting.

See the *Arm*® *AMBA*® *AXI and ACE Protocol Specification* for more information about AXI transaction identifiers.

#### Write data buffer

The optional write data buffer enables write transactions with different AXI IDs to progress through the TBU out-of-order. It reorders the data to match the downstream transaction order.

#### **PMU**

The PMU counts TBU performance-related events.

#### Clock and power control

The TBU has its own clock and power control, provided by the Q-Channel.

#### **DTI** interface

The master DTI interface uses the DTI protocol, typically over AXI4-Stream, to enable the TBU to communicate with a slave component. For the MMU-600, the slave component is the TCU. Although you can implement DTI over different transport protocols, the MMU-600 interfaces use AXI4-Stream.

#### Transaction tracker

The transaction trackers manage outstanding read and write transactions, permitting invalidation and synchronization to take place without stalling the AXI interfaces.

#### Related references

3.2 SMMU architectural registers on page 3-57.

#### 2.1.3 DTI interconnect

The TBU and TCUs use a DTI interface to communicate. The DTI interconnect enables the DTI interface to use the AXI4-Stream protocol.

The DTI interconnect can connect any components that conform to the AXI4 Stream subset, as defined by the *Arm*<sup>®</sup> *AMBA*<sup>®</sup> *Distributed Translation Interface (DTI) Protocol Specification*.

The DTI interconnect contains internal components that are hierarchically composable, that is, they can be connected in different ways to suit your system requirements. For example, within an MMU-600 system, you can use the switch component to combine the DTI interfaces of multiple TBUs into a single DTI interface. You can then connect the combined DTI interface to another DTI interconnect that is closer to the TCU. The DTI interconnect includes switch, sizer, and register slice components.

#### Switch

The switch connects multiple DTI masters, such as TBUs, to a DTI slave such as a TCU. The switch implements the following parallel networks:

- For TBU to TCU traffic, a network that connects multiple AXI4-Stream slave interfaces to a single AXI4-Stream master interface.

- For TCU to TBU traffic, a network that connects a single AXI4-Stream slave interface to multiple AXI4-Stream master interfaces.

| N                        | Tote ———                                                                        |

|--------------------------|---------------------------------------------------------------------------------|

| The switch do interface. | oes not store any data, and therefore does not require a Q-Channel clock-gating |

#### Sizer

The sizer connects channels that have different data widths, enabling different tradeoffs of bandwidth to area. The sizer supports conversion between any of the supported AXI4-Stream data widths:

- 1 byte.

- 4 bytes.

- 10 bytes.

- 20 bytes.

The sizer includes a Q-Channel interface to provide clock-gating control.

### Register slice

Use the register slice to improve timing. The register slice includes a Q-Channel interface to provide clock-gating control.

The MMU-600 DTI interconnect components do not include a component to connect different clock and power domains. You can connect DTI interfaces in different clock and power domains by using the *Bidirectional AXI4-Stream* (BAS) configuration of the ADB-400 AMBA Domain Bridge.

## **Related concepts**

2.3 Operation on page 2-36.

### 2.2 Interfaces

The MMU-600 includes interfaces for each of the TCU, TBU, and DTI interconnect components.

The DTI interconnect consists of switch, sizer, and register slice components that can be connected separately, and therefore have their own interfaces.

The PMU snapshot interface is common to both TCU and TBU.

This section contains the following subsections:

- 2.2.1 TCU interfaces on page 2-28.

- 2.2.2 TBU interfaces on page 2-30.

- 2.2.3 DTI interconnect interfaces on page 2-33.

#### 2.2.1 TCU interfaces

The MMU-600 contains various TCU interfaces.

The following figure shows the TCU interfaces.

Figure 2-4 TCU interfaces

#### TCU Queue and Table Walk/Distributed Virtual Memory (QTW/DVM) interface

The QTW/DVM interface is an ACE-Lite+DVM master interface.

The QTW/DVM interface issues the following transaction types:

- ReadNoSnoop.

- WriteNoSnoop.

- ReadOnce.

- · WriteUnique.

- DVM Complete.

The QTW/DVM interface uses the write address transaction ID signal **awid\_qtw**, and the read address transaction ID signal, **arid\_qtw**. The value of **awid\_qtw** is always 0, and the value of **arid\_qtw** depends on the transaction type. The following table shows the possible values of **arid\_qtw**.

Table 2-1 Possible arid\_qtw values

| Transaction type       | arid_qtw[n:1]                                                    | arid_qtw[0] |

|------------------------|------------------------------------------------------------------|-------------|

| Translation table walk | Indicates the slot that is requesting the translation table walk | 1           |

| Command queue read     | All bits = $0$ .                                                 | 0           |

| DVM Complete           | All bits = $1$ .                                                 | 0           |

To support 16-bit Virtual Machine IDentifiers (VMIDs), the interface provides DVMv8.1 support.

The interface does not issue cache maintenance operations or exclusive accesses.

#### **Related concepts**

2.3.5 Distributed Virtual Memory (DVM) messages on page 2-43. 2.3.6 Error responses on page 2-44.

#### Related references

AXI5 support on page 2-53.

A.2 TCU QTW/DVM interface signals on page Appx-A-91.

#### **TCU PROG interface**

The PROG interface is an AMBA APB4 slave interface. It enables software to program the MMU-600 internal registers and read the *Performance Monitoring Unit* (PMU) registers and the debug registers.

This interface runs synchronously with the other TCU interfaces.

The applicable address width for this interface depends on the value of TCUCFG\_NUM\_TBU:

- When TCUCFG\_NUM\_TBU = 14, the address width is 21 bits.

- When TCUCFG\_NUM\_TBU = 62, the address width is 23 bits.

Transactions are Read-As-Zero, Writes Ignored (RAZ/WI) when any of the following apply:

- An unimplemented register is accessed.

- PSTRB[3:0] is not 0b1111 for write transfers.

- PPROT[1] is not set to 0 for Secure register accesses.

See the Arm® AMBA® APB Protocol Specification for more information.

#### Related references

A.3 TCU programming interface signals on page Appx-A-93.

#### **TCU LPI PD interface**

This Q-Channel slave interface manages LPI powerdown for the TCU.

See the AMBA® Low Power Interface Specification, Arm® Q-Channel and P-Channel Interfaces for more information.

#### Related references

A.6 TCU LPI PD interface signals on page Appx-A-96.

#### **TCU LPI CG interface**

This Q-Channel slave interface enables LPI clock-gating for the TCU.

See the AMBA® Low Power Interface Specification, Arm® Q-Channel and P-Channel Interfaces for more information.

## Related references

A.7 TCU LPI CG interface signals on page Appx-A-97.

#### **TCU DTI interface**

The DTI interface manages communication between the TBUs and the TCU, using the DTI protocol. The DTI protocol can be conveyed over different transport layer mediums, including AXI4-Stream.

The TCU includes a slave DTI interface and each TBU includes a master DTI interface. To permit bidirectional communication, each DTI interface includes one AXI4-Stream master interface and one AXI4-Stream slave interface.

See the Arm® AMBA® Distributed Translation Interface (DTI) Protocol Specification and the Arm® AMBA® 4 AXI4-Stream Protocol Specification for more information.

#### **Related concepts**

2.3.2 DTI overview on page 2-42.

#### Related references

A.8 TCU DTI interface signals on page Appx-A-98.

#### **TCU** interrupt interfaces

This interface provides global, per-context, and performance interrupts.

#### Related references

A.9 TCU interrupt signals on page Appx-A-99.

### **TCU SYSCO interface**

The MMU-600 provides a hardware system coherency interface. This interface permits the TCU to remove itself from a coherency domain in response to an LPI request.

The SYSCO interface uses the **syscoreq** and **syscoack** handshake signals to enter or exit a coherency domain.

If the **sup** btm signal is tied LOW:

- syscoreq is always driven LOW and syscoack is ignored.

- The TCU SYSCO interface is not used and can be left unconnected.

#### Related references

A.4 TCU SYSCO interface signals on page Appx-A-94.

## TCU tie-off signals

The TCU tie-off signals enable you to initialize various operating parameters on exit from reset state.

At reset, the value of each tie-off signal controls the respective bits in the SMMU IDR0 Register.

#### Related references

A.10 TCU tie-off signals on page Appx-A-100.

#### 2.2.2 TBU interfaces

The following figure shows the TBU interfaces.

Figure 2-5 TBU interfaces

#### **TBU TBS interface**

The *transaction slave* (TBS) interface is an ACE5-Lite interface on which the TBU receives incoming untranslated memory accesses.

This interface supports a 64-bit address width.

The interface implements optional signals to support the following AXI5 extensions:

- Untranslated Transactions.

- · Cache Stash Transactions.

- · DeAllocation Transactions.

- · Low Power Signals.

The TBS interface implements **AWAKEUP** to support the Low\_Power\_Signals extension. It does not support the other signals that AXI5 associates with this extension.

The TBS interface does not support WriteEvict transactions, and therefore does not support the **AWUNIQUE** signal.

The TBS interface supports ACE Exclusive accesses.

If a transaction is terminated in the TBU, the transaction tracker returns the transaction with the user-defined AXI RUSER and BUSER bits set to 0.

#### **Related concepts**

2.3.6 Error responses on page 2-44.

#### Related references

A.12 TBU TBS interface signals on page Appx-A-102.

#### **TBU TBM interface**

The TBM transaction master interface is an ACE5-Lite interface on which the TBU sends outgoing translated memory accesses.

The AXI ID of a transaction on this interface is the same as the AXI ID of the corresponding transaction on the TBS interface.

This interface supports a 64-bit address width, and TBUCFG\_DATA\_WIDTH defines the data width.

This interface can issue read and write transactions until the outstanding transaction limit is reached. The MMU-600 provides parameters that permit you to configure:

- · The outstanding read transactions limit.

- · The outstanding write transactions limit.

- The total outstanding read and write transactions limit.

The interface implements optional signals to support the following AXI5 extensions:

- Untranslated Transactions.

- Cache\_Stash\_Transactions.

- · DeAllocation Transactions.

- Low\_Power\_Signals.

| <br>Note — |

|------------|

| Note       |

The TBM interface implements **AWAKEUP** to support the Low\_Power\_Signals extension. It does not support the other signals that AXI5 associates with this extension.

| <br>Note - |

|------------|

| TAULE      |

The TBM interface does not support WriteEvict transactions, and therefore does not support the **AWUNIQUE** signal.

When receiving an SLVERR or DECERR response to a downstream transaction, the TBM interface propagates the same response to the TBS interface.

The TBM interface supports ACE Exclusive accesses.

#### Related concepts

2.3.6 Error responses on page 2-44.

#### Related references

2.4.2 AMBA support on page 2-51.

A.13 TBU TBM interface signals on page Appx-A-104.

#### TBU LPI\_PD interface

This Q-Channel slave interface manages LPI powerdown for the TBU.

See the AMBA® Low Power Interface Specification, Arm® Q-Channel and P-Channel Interfaces for more information.

#### Related references

A.15 TBU LPI PD interface signals on page Appx-A-107.

## TBU LPI\_CG interface

This Q-Channel slave interface enables LPI clock-gating for the TBU.

See the AMBA® Low Power Interface Specification, Arm® Q-Channel and P-Channel Interfaces for more information.

## Related references

A.16 TBU LPI\_CG interface signals on page Appx-A-108.

#### **TBU DTI interface**

The TBU DTI interface enables master devices with their own TLB and prefetch capability to request translations from the MMU-600. This interface uses the DTI-TBU protocol for communication between the TBU and the TCU.

The TCU includes a slave DTI interface and each TBU includes a master DTI interface. To permit bidirectional communication, each DTI interface includes one AXI4-Stream master interface and one AXI4-Stream slave interface.

See the Arm® AMBA® Distributed Translation Interface (DTI) Protocol Specification and the Arm® AMBA® 4 AXI4-Stream Protocol Specification for more information.

## **Related concepts**

2.3.2 DTI overview on page 2-42.

### Related references

A.17 TBU DTI interface signals on page Appx-A-109.

## **TBU** interrupt interfaces

This interface provides global, per-context, and performance interrupts.

#### Related references

A.18 TBU interrupt signals on page Appx-A-110.

#### TBU tie-off signals

The TBU tie-off signals enable you to initialize various operating parameters on exit from reset state.

At reset, the value of each tie-off signal controls the respective bits in the SMMU IDR0 Register.

#### Related references

A.19 TBU tie-off signals on page Appx-A-111.

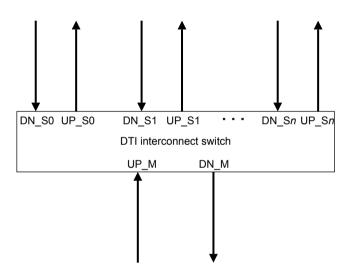

#### 2.2.3 DTI interconnect interfaces

The DTI interconnect includes interfaces for each of the switch, sizer, and register slice components.

#### **DTI** interconnect switch interfaces

The DTI interconnect switch component includes dedicated interfaces.

The following figure shows the DTI interconnect switch interfaces.

Figure 2-6 DTI interconnect switch interfaces

The following table provides more information about the switch interfaces.

Table 2-2 DTI interconnect switch interfaces

| Interface | Interface type | Protocol    | Description                                                                          |

|-----------|----------------|-------------|--------------------------------------------------------------------------------------|

| DN_Sn     | Slave          | AXI4-Stream | Slave downstream interface. One DN_Sn interface is present for each slave interface. |

| UP_Sn     | Master         |             | Slave upstream interface. One UP_Sn interface is present for each slave interface.   |

| DN_M      | Master         |             | Master downstream interface.                                                         |

| UP_M      | Slave          |             | Master upstream interface.                                                           |

\_\_\_\_\_ Note \_\_\_\_\_

The interconnect switch does not store any data, and therefore does not require a Q-Channel clock-gating interface.

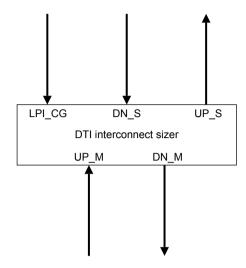

### **DTI** interconnect sizer interfaces

The DTI interconnect sizer component includes dedicated interfaces.

The following figure shows the DTI interconnect sizer interfaces.

Figure 2-7 DTI interconnect sizer interfaces

The following table provides more information about the sizer interfaces.

Table 2-3 DTI interconnect sizer interfaces

| Interface | Interface type | Protocol    | Description                  |

|-----------|----------------|-------------|------------------------------|

| LPI_CG    | Slave          | Q-Channel   | Clock-gating interface.      |

| DN_S      | Slave          | AXI4-Stream | Slave downstream interface.  |

| UP_S      | Master         |             | Slave upstream interface.    |

| DN_M      | Master         |             | Master downstream interface. |

| UP_M      | Slave          |             | Master upstream interface.   |

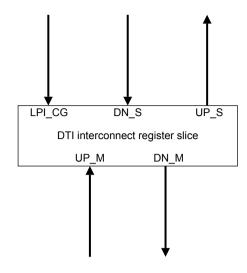

## DTI interconnect register slice interfaces

The DTI interconnect register slice component includes dedicated interfaces.

The following figure shows the DTI interconnect register slice interfaces.

Figure 2-8 DTI interconnect register slice interfaces

The following table provides more information about the register slice interfaces.

Table 2-4 DTI interconnect register slice interfaces

| Interface | Interface type | Protocol    | Description                  |

|-----------|----------------|-------------|------------------------------|

| LPI_CG    | Slave          | Q-Channel   | Clock-gating interface.      |

| DN_S      |                | AXI4-Stream | Slave downstream interface.  |

| UP_S      | Master         |             | Slave upstream interface.    |

| DN_M      |                |             | Master downstream interface. |

| UP_M      | Slave          |             | Master upstream interface.   |

## 2.3 Operation

This section provides information about the operation of the MMU-600 features.

This section contains the following subsections:

- 2.3.1 Performance Monitoring Unit on page 2-36.

- 2.3.2 DTI overview on page 2-42.

- 2.3.3 Reliability, Availability, and Serviceability on page 2-43.

- 2.3.4 Quality of Service on page 2-43.

- 2.3.5 Distributed Virtual Memory (DVM) messages on page 2-43.

- 2.3.6 Error responses on page 2-44.

- 2.3.7 Conversion between ACE-Lite and ARMv8 attributes on page 2-44.

## 2.3.1 Performance Monitoring Unit

The MMU-600 includes a PMU for the TCU and a PMU for each TBU. The PMU events and counters indicate the runtime performance of the MMU-600.

The MMU-600 includes logic to gather various statistics on the operation of the MMU during runtime, using events and counters. These events, which the SMMUv3 architecture defines, provide useful information about the behavior of the MMU. You can use this information when debugging or profiling traffic.

The **sec override** signal permits certain registers to be accessible to Non-secure software.

A single DTI translation request might correspond to multiple translation request events in either of the following circumstances:

- A translation results in a stall fault event and is restarted.

- If a translation results in a stall fault event because of the Event queue being full, the translation is retried when an Event queue slot becomes available.

## SMMUv3 architectural performance events

Both the TCU and the TBU implement performance events that the SMMUv3 Performance Monitor extension defines.

The SMMU\_PMCG\_SMR0 register can filter some events so that only events with a particular StreamID are counted.

The following table shows the architecturally defined MMU-600 TCU performance events.

Table 2-5 SMMUv3 performance events for the TCU

| Event                                                           | Event ID | SMMU_PMCG_SMR0 filterable | Description                                                                                              |

|-----------------------------------------------------------------|----------|---------------------------|----------------------------------------------------------------------------------------------------------|

| Clock cycle.                                                    | 0x0      | No                        | Counts clock cycles.  Cycles where the clock is gated after a clock Q-Channel handshake are not counted. |

| Transaction.                                                    | 0x1      | Yes                       | Counts translation requests that originate from a DTI-TBU or DTI-ATS master.                             |

| TLB miss caused by incoming transaction or translation request. | 0x2      | Yes                       | Counts translation requests where the translation walks new translation table entries.                   |

Table 2-5 SMMUv3 performance events for the TCU (continued)

| Event                                                                  | Event ID | SMMU_PMCG_SMR0 filterable | Description                                                                              |

|------------------------------------------------------------------------|----------|---------------------------|------------------------------------------------------------------------------------------|

| Configuration cache miss caused by transaction or translation request. | 0x3      | Yes                       | Counts translation requests where the translation walks new configuration table entries. |

| Translation table walk access.                                         | 0x4      | Yes                       | Counts translation table walk accesses.                                                  |

| Configuration structure access.                                        | 0x5      | Yes                       | Counts configuration table walk accesses.                                                |

| PCIe ATS Translation Request received.                                 | 0x6      | Yes                       | Counts translation requests that originate from a DTI-ATS master.                        |

The following table shows the architecturally defined MMU-600 TBU performance events.

Table 2-6 SMMUv3 performance events for the TBU

| Event                                                           | Event ID | SMMU_PMCG_SMR0 filterable | Description                                                                                              |

|-----------------------------------------------------------------|----------|---------------------------|----------------------------------------------------------------------------------------------------------|

| Clock cycle.                                                    | 0x0      | No                        | Counts clock cycles.  Cycles where the clock is gated after a clock Q-Channel handshake are not counted. |

| Transaction.                                                    | 0x1      | Yes                       | Counts transactions that are issued on the TBM interface.                                                |

| TLB miss caused by incoming transaction or translation request. | 0x2      | Yes                       | Counts non-speculative translation requests that are issued to the TCU.                                  |

| PCIe ATS Translation<br>Request received.                       | 0x7      | Yes                       | Counts ATS-translated transactions that are issued on the TBM interface.                                 |

See the *Arm*<sup>®</sup> *System Memory Management Unit Architecture Specification, SMMU architecture version 3.0 and version 3.1* for more information.

## MMU-600 TCU events

The MMU-600 PMU can be configured to monitor a range of IMPLEMENTATION DEFINED TCU performance events.

The SMMU\_PMCG\_SMR0 register can filter some TCU performance events so that only events with a particular StreamID are counted.

The following table shows the TCU performance events.

Table 2-7 MMU-600 TCU performance events

| Event   Event ID   SMMU_PMCG_SMR0   Description   filterable |      | Description |                                                                                           |

|--------------------------------------------------------------|------|-------------|-------------------------------------------------------------------------------------------|

| S1L0WC lookup                                                | 0x80 | Yes         | Counts translation requests that access the S1L0WC walk cache.                            |

| S1L0WC miss                                                  | 0x81 | Yes         | Counts translation requests that access the S1L0WC walk cache and do not result in a hit. |

| S1L1WC lookup                                                | 0x82 | Yes         | Counts translation requests that access the S1L1WC walk cache.                            |

# Table 2-7 MMU-600 TCU performance events (continued)

| Event                   | Event ID | SMMU_PMCG_SMR0 filterable | Description                                                                                                                                                                                                                        |

|-------------------------|----------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S1L1WC miss             | 0x83     | Yes                       | Counts translation requests that access the S1L1WC walk cache and do not result in a hit.                                                                                                                                          |

| S1L2WC lookup           | 0×84     | Yes                       | Counts translation requests that access the S1L2WC walk cache.                                                                                                                                                                     |

| S1L2WC miss             | 0x85     | Yes                       | Counts translation requests that access the S1L2WC walk cache and do not result in a hit.                                                                                                                                          |

| S1L3WC lookup           | 0x86     | Yes                       | Counts translation requests that access the S1L3WC walk cache.                                                                                                                                                                     |

| S1L3WC miss             | 0x87     | Yes                       | Counts translation requests that access the S1L3WC walk cache and do not result in a hit.                                                                                                                                          |

| S2L0WC lookup           | 0×88     | Yes                       | Counts translation requests that access the S2L0WC walk cache.                                                                                                                                                                     |

| S2L0WC miss             | 0x89     | Yes                       | Counts translation requests that access the S2L0WC walk cache and do not result in a hit.                                                                                                                                          |

| S2L1WC lookup           | 0×8A     | Yes                       | Counts translation requests that access the S2L1WC walk cache.                                                                                                                                                                     |

| S2L1WC miss             | 0x8B     | Yes                       | Counts translation requests that access the S2L1WC walk cache and do not result in a hit.                                                                                                                                          |

| S2L2WC lookup           | 0×8C     | Yes                       | Counts translation requests that access the S2L2WC walk cache.                                                                                                                                                                     |

| S2L2WC miss             | 0x8D     | Yes                       | Counts translation requests that access the S2L2WC walk cache and do not result in a hit.                                                                                                                                          |

| S2L3WC lookup           | 0x8E     | Yes                       | Counts translation requests that access the S2L3WC walk cache.                                                                                                                                                                     |

| S2L3WC miss             | 0x8F     | Yes                       | Counts translation requests that access the S2L3WC walk cache and do not result in a hit.                                                                                                                                          |

| WC read                 | 0×90     | Yes                       | Counts reads from the walk cache RAMs, excluding reads that are caused by invalidation requests.  Note  A single walk cache lookup might result in multiple RAM reads. This behavior permits contiguous entries to be located.     |

| Buffered translation    | 0x91     | Yes                       | Counts translations written to the translation request buffer because all translation slots are full.                                                                                                                              |

| CC lookup               | 0x92     | Yes                       | Counts lookups into the configuration cache.                                                                                                                                                                                       |

| CC read                 | 0x93     | Yes                       | Counts reads from the configuration cache RAMs, excluding reads that are caused by invalidation requests.  Note  A single cache lookup might result in multiple RAM reads. This behavior permits contiguous entries to be located. |

| Speculative translation | 0xA0     | Yes                       | Counts translation requests that are marked as speculative.                                                                                                                                                                        |

Table 2-7 MMU-600 TCU performance events (continued)

| Event         | Event ID | SMMU_PMCG_SMR0 filterable | Description                                                                  |

|---------------|----------|---------------------------|------------------------------------------------------------------------------|

| S1L0WC error  | 0xC0     | No                        | RAS corrected error in S1L0 walk cache.                                      |

|               |          |                           | This Secure event is visible only when the SMMU_PMCG_SCR.SO bit is set to 1. |

| S1L1WC error  | 0xC1     | No                        | RAS corrected error in S1L1 walk cache.                                      |

|               |          |                           | This Secure event is visible only when the SMMU_PMCG_SCR.SO bit is set to 1. |

| S1L2WC error  | 0xC2     | No                        | RAS corrected error in S1L2 walk cache.                                      |

|               |          |                           | This Secure event is visible only when the SMMU_PMCG_SCR.SO bit is set to 1. |

| S1L3WC error  | 0xC3     | No                        | RAS corrected error in S1L3 walk cache.                                      |

|               |          |                           | This Secure event is visible only when the SMMU_PMCG_SCR.SO bit is set to 1. |

| S2L0WC error  | 0xC4     | No                        | RAS corrected error in S2L0 walk cache.                                      |

|               |          |                           | This Secure event is visible only when the SMMU_PMCG_SCR.SO bit is set to 1. |

| S2L1WC error  | 0xC5     | No                        | RAS corrected error in S2L1 walk cache.                                      |

|               |          |                           | This Secure event is visible only when the SMMU_PMCG_SCR.SO bit is set to 1. |

| S2L2WC error  | 0xC6     | No                        | RAS corrected error in S2L2 walk cache.                                      |

|               |          |                           | This Secure event is visible only when the SMMU_PMCG_SCR.SO bit is set to 1. |

| S2L3WC error  | 0xC7     | No                        | RAS corrected error in S2L3 walk cache.                                      |

|               |          |                           | This Secure event is visible only when the SMMU_PMCG_SCR.SO bit is set to 1. |

| Configuration | 0xC8     | No                        | RAS corrected error in configuration cache.                                  |

| cache error   |          |                           | This Secure event is visible only when the SMMU_PMCG_SCR.SO bit is set to 1. |

## MMU-600 TBU events

The MMU-600 PMU can be configured to monitor a range of IMPLEMENTATION DEFINED TBU performance events.

The SMMU\_PMCG\_SMR0 register can filter the TBU performance events so that only events with a particular StreamID are counted.

The following table shows the TBU performance events.

# Table 2-8 MMU-600 TBU performance events

| Event                                       | Event<br>ID | SMMU_PMCG_SMR0 filterable | Description                                                                                                                                                                                                                             |

|---------------------------------------------|-------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Main TLB lookup                             | 0x80        | Yes                       | Counts Main TLB lookups.                                                                                                                                                                                                                |

| Main TLB miss                               | 0x81        | Yes                       | Counts translation requests that miss in the Main TLB.                                                                                                                                                                                  |

| Main TLB read                               | 0x82        | Yes                       | Counts once per access to the Main TLB RAMs, excluding reads that are caused by invalidation requests.  Note  A transaction might access the Main TLB multiple times to look for different page sizes.                                  |

| Micro TLB lookup                            | 0x83        | Yes                       | Counts micro TLB lookups.                                                                                                                                                                                                               |

| Micro TLB miss                              | 0x84        | Yes                       | Counts translation requests that miss in the micro TLB.                                                                                                                                                                                 |

| Slots full                                  | 0x85        | No                        | Counts once per cycle when all slots are occupied and not ready to issue transactions downstream.                                                                                                                                       |

|                                             |             |                           | This Secure event is visible only when the SMMU_PMCG_SCR.SO bit is set to 1.                                                                                                                                                            |

| Out of translation tokens                   | 0x86        | No                        | Counts once per cycle when a translation request cannot be issued because all translation tokens are in use.                                                                                                                            |

|                                             |             |                           | This Secure event is visible only when the SMMU_PMCG_SCR.SO bit is set to 1.                                                                                                                                                            |

| Write data buffer full                      | 0x87        | No                        | Counts once per cycle when a transaction is blocked because the write data buffer is full.                                                                                                                                              |

|                                             |             |                           | This Secure event is visible only when the SMMU_PMCG_SCR.SO bit is set to 1.                                                                                                                                                            |

| Translation request                         | 0x88        | Yes                       | Counts translation requests, including both speculative and non-speculative requests.                                                                                                                                                   |

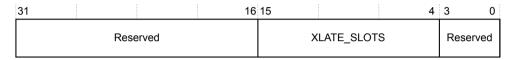

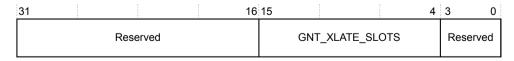

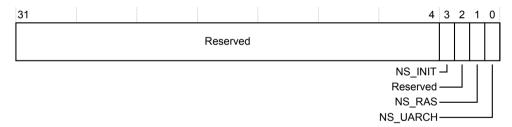

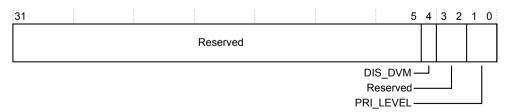

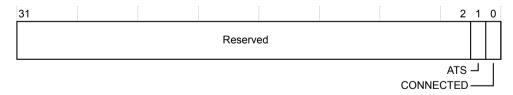

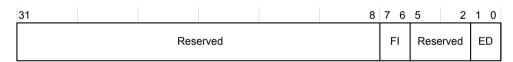

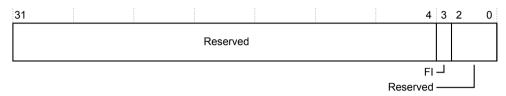

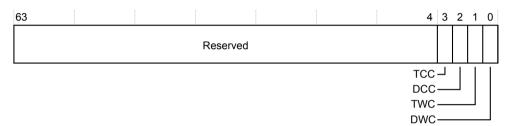

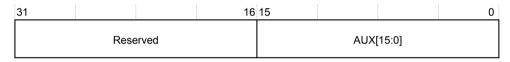

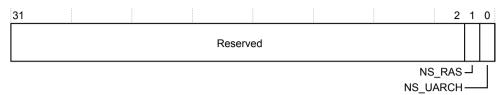

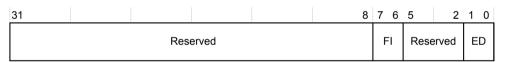

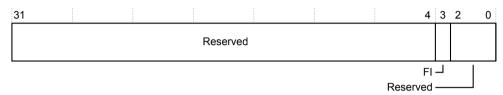

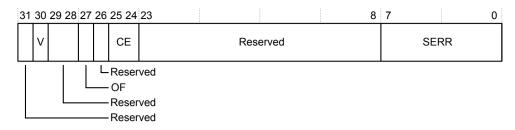

| Write data uses<br>write data buffer        | 0x89        | Yes                       | Counts transactions with write data that is stored in the write data buffer.                                                                                                                                                            |