# Arm<sup>®</sup> Cortex<sup>®</sup>-M33 Processor

Revision: r0p4

**Technical Reference Manual**

#### Arm<sup>®</sup> Cortex<sup>®</sup>-M33 Processor

#### **Technical Reference Manual**

Copyright © 2016-2018 Arm Limited or its affiliates. All rights reserved.

#### **Release Information**

#### **Document History**

| Issue   | Date              | Confidentiality  | Change                 |

|---------|-------------------|------------------|------------------------|

| 0000-00 | 28 September 2016 | Confidential     | First release for r0p0 |

| 0001-00 | 03 February 2017  | Confidential     | First release for r0p1 |

| 0002-00 | 10 May 2017       | Non-Confidential | First release for r0p2 |

| 0003-00 | 06 December 2017  | Non-Confidential | First release for r0p3 |

| 0004-00 | 18 April 2018     | Non-Confidential | First release for r0p4 |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. **No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.**

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with <sup>®</sup> or <sup>TM</sup> are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at *http://www.arm.com/company/policies/trademarks*.

Copyright © 2016-2018 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

#### **Product Status**

The information in this document is Final, that is for a developed product.

#### Web Address

http://www.arm.com

# Contents Arm<sup>®</sup> Cortex<sup>®</sup>-M33 Processor Technical Reference Manual

|            | Preface |                                  |       |

|------------|---------|----------------------------------|-------|

|            |         | About this book                  |       |

|            |         | Feedback                         |       |

| Part A     | Intro   | oduction                         |       |

| Chapter A1 | Intro   | duction                          |       |

|            | A1.1    | About the processor              | A1-18 |

|            | A1.2    | About the processor architecture | A1-19 |

|            | A1.3    | Processor configuration options  | A1-20 |

|            | A1.4    | Component blocks                 | A1-22 |

|            | A1.5    | Interfaces                       | A1-25 |

|            | A1.6    | Compliance                       |       |

|            | A1.7    | Design process                   |       |

|            | A1.8    | Documentation                    | A1-28 |

|            | A1.9    | Product revisions                | A1-29 |

| Part B     | Fun     | ctional description              |       |

| Chapter B1 | Prog    | rammers Model                    |       |

|            | B1.1    | About the programmers model      | B1-34 |

|            | B1.2  | Modes of operation and execution                                    | B1-35 |

|------------|-------|---------------------------------------------------------------------|-------|

|            | B1.3  | Instruction set summary                                             | B1-36 |

|            | B1.4  | Memory model                                                        | B1-37 |

|            | B1.5  | Exclusive monitor                                                   | B1-39 |

|            | B1.6  | Processor core registers summary                                    | B1-40 |

|            | B1.7  | Exceptions                                                          | B1-42 |

| Chapter B2 | Syst  | em Control                                                          |       |

|            | B2.1  | Identification register summary                                     | B2-44 |

|            | B2.2  | Auxiliary Control Register                                          | B2-49 |

|            | B2.3  | CPUID Base Register                                                 | B2-51 |

| Chapter B3 | Secu  | irity Attribution and Memory Protection                             |       |

|            | B3.1  | About security attribution and memory protection                    | B3-54 |

|            | B3.2  | SAU register summary                                                | B3-56 |

|            | B3.3  | MPU register summary                                                | ВЗ-57 |

| Chapter B4 | Nest  | ed Vectored Interrupt Controller                                    |       |

|            | B4.1  | NVIC programmers model                                              | B4-60 |

| Chapter B5 | Float | ting-Point Unit                                                     |       |

|            | B5.1  | About the FPU                                                       | B5-64 |

|            | B5.2  | FPU functional description                                          | B5-65 |

|            | B5.3  | FPU programmers model                                               | B5-67 |

| Chapter B6 | Exte  | rnal coprocessors                                                   |       |

|            | B6.1  | About external coprocessors                                         | B6-70 |

|            | B6.2  | Operation                                                           | B6-71 |

|            | B6.3  | Usage restrictions                                                  | B6-72 |

|            | B6.4  | Data transfer rates                                                 | B6-73 |

|            | B6.5  | Configuring which coprocessors are included in Secure and Non-secur |       |

|            | B6.6  | Debug access to coprocessor registers usage constraints             |       |

|            | B6.7  | Exceptions and context switch                                       | B6-76 |

| Part C     | Deb   | oug and trace components                                            |       |

| Chapter C1 | Debu  | Ja                                                                  |       |

|            | C1.1  | Debug functionality                                                 | C1-80 |

|            | C1.2  | About the D-AHB interface                                           |       |

| Chapter C2 | Instr | umentation Trace Macrocell Unit                                     |       |

|            | C2.1  | ITM programmers model                                               | C2-88 |

| Chapter C3 | Data  | Watchpoint and Trace Unit                                           |       |

|            | C3.1  | DWT functional description                                          | C3-94 |

|            | C3.2  | DWT programmers model                                               |       |

| Chapter C4 | Cros  | s Trigger Interface                                                 |       |

|            | C4.1  | About the Cross Trigger Interface                                   | C4-98 |

|            | C4.2  | CTI functional description                                          |       |

|            |       |                                                                     |       |

|            | C4.3        | CTI programmers model                                    | C4-101     |

|------------|-------------|----------------------------------------------------------|------------|

| Chapter C5 | Brea        | kpoint Unit                                              |            |

| -          | C5.1        | About the Breakpoint Unit                                | C5-104     |

|            | C5.2        | BPU programmers model                                    | C5-105     |

|            | C5.3        | BPU functional description                               | C5-107     |

| Part D     | Арр         | pendices                                                 |            |

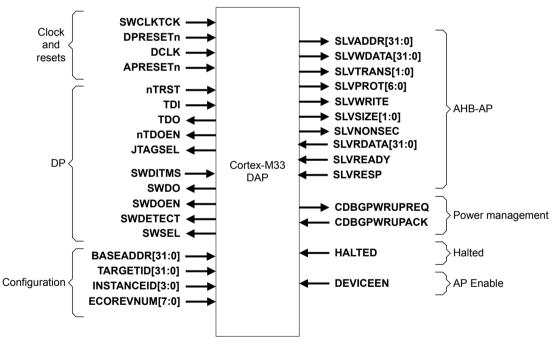

| Appendix A | Debu        | ig Access Port                                           |            |

|            | A.1         | About the Debug Access Port                              | Аррх-А-112 |

|            | A.2         | Functional description                                   | Аррх-А-114 |

|            | A.3         | DAP register summary                                     | Аррх-А-115 |

|            | A.4         | DAP register descriptions                                | Аррх-А-117 |

| Appendix B | Trace       | e Port Interface Unit                                    |            |

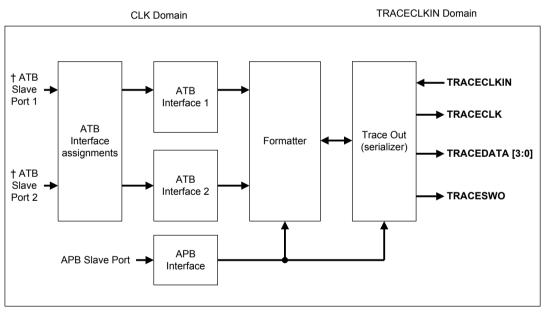

|            | B.1         | About the TPIU                                           | Аррх-В-134 |

|            | B.2         | TPIU functional description                              | Аррх-В-135 |

|            | B.3         | TPIU programmers model                                   | Аррх-В-137 |

| Appendix C | UNPI        | REDICTABLE Behaviors                                     |            |

|            | C.1         | Use of instructions defined in architecture variants     | Аррх-С-148 |

|            | C.2         | Use of Program Counter - R15 encoding                    | Аррх-С-149 |

|            | C.3         | Use of Stack Pointer - as a general purpose register R13 | Аррх-С-150 |

|            | C.4         | Register list in load and store multiple instructions    | Аррх-С-151 |

|            | C.5         | Exception-continuable instructions                       | Аррх-С-152 |

|            | C.6         | Stack limit checking                                     | Аррх-С-153 |

|            | <b>C</b> .7 | UNPREDICTABLE instructions within an IT block            | Аррх-С-154 |

|            | C.8         | Memory access and address space                          | Аррх-С-155 |

|            | C.9         | Load exclusive and Store exclusive accesses              | Аррх-С-156 |

|            | C.10        | Armv8-M MPU programming                                  | Аррх-С-157 |

|            | C.11        | Miscellaneous UNPREDICTABLE instruction behavior         | Аррх-С-158 |

| Appendix D | Revis       | sions                                                    |            |

|            | D.1         | Revisions                                                | Аррх-D-160 |

# Preface

This preface introduces the Arm<sup>®</sup> Cortex<sup>®</sup>-M33 Processor Technical Reference Manual.

It contains the following:

- *About this book* on page 10.

- Feedback on page 13.

### About this book

This book is for the Cortex®-M33 processor.

#### Product revision status

The *rmpn* identifier indicates the revision status of the product described in this book, for example, r1p2, where:

- rm Identifies the major revision of the product, for example, r1.

- pn Identifies the minor revision or modification status of the product, for example, p2.

#### Intended audience

This manual is written to help system designers, system integrators, verification engineers, and software programmers who are implementing a *System on Chip* (SoC) device based on the Cortex<sup>®</sup>-M33 processor.

#### Using this book

This book is organized into the following chapters:

#### **Part A Introduction**

#### **Chapter A1 Introduction**

This chapter introduces the Cortex-M33 processor and its features, configurable options, and product documentation.

#### Part B Functional description

#### Chapter B1 Programmers Model

This chapter describes the Cortex-M33 processor register set, modes of operation, and provides other information for programming the processor.

#### Chapter B2 System Control

This chapter describes registers that contain IMPLEMENTATION DEFINED information or functionality.

#### **Chapter B3 Security Attribution and Memory Protection**

This chapter describes the security attribution and memory protection facilities that the Cortex-M33 processor provides.

Chapter B4 Nested Vectored Interrupt Controller

This chapter describes the Nested Vectored Interrupt Controller (NVIC).

#### **Chapter B5 Floating-Point Unit**

This chapter describes the Floating-Point Unit (FPU).

#### Chapter B6 External coprocessors

This chapter describes the external coprocessors.

#### Part C Debug and trace components

#### Chapter C1 Debug

This chapter summarizes the debug system.

#### Chapter C2 Instrumentation Trace Macrocell Unit

This chapter describes the Instrumentation Trace Macrocell (ITM) unit.

#### Chapter C3 Data Watchpoint and Trace Unit

This chapter describes the Data Watchpoint and Trace (DWT) unit.

#### Chapter C4 Cross Trigger Interface

This chapter describes the Cross Trigger Interface (CTI).

#### Chapter C5 Breakpoint Unit

This section describes the Breakpoint Unit (BPU).

#### Part D Appendices

#### Appendix A Debug Access Port

This appendix describes the DAP for the Cortex-M33 processor.

#### Appendix B Trace Port Interface Unit

This appendix describes the Cortex-M33 TPIU that can be used with the Cortex-M33 processor.

#### Appendix C UNPREDICTABLE Behaviors

This appendix summarizes the behavior of the Cortex-M33 processor in cases where the Armv8-M architecture is UNPREDICTABLE.

#### Appendix D Revisions

This appendix describes the technical changes between released issues of this book.

#### Glossary

The Arm<sup>®</sup> Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

See the Arm® Glossary for more information.

#### **Typographic conventions**

italic

Introduces special terminology, denotes cross-references, and citations.

#### bold

Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.

#### monospace

Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.

#### <u>mono</u>space

Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.

#### monospace italic

Denotes arguments to monospace text where the argument is to be replaced by a specific value.

#### monospace bold

Denotes language keywords when used outside example code.

<and>

Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:

ADD Rd, SP, #<imm>

#### SMALL CAPITALS

Used in body text for a few terms that have specific technical meanings, that are defined in the *Arm*<sup>®</sup> *Glossary*. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE.

#### Additional reading

This book contains information that is specific to this product. See the following documents for other relevant information.

#### **Arm publications**

- Armv8-M Architecture Reference Manual (DDI 0553)

- Arm<sup>®</sup> AMBA<sup>®</sup> 5 AHB Protocol Specification (IHI 0033)

- AMBA® APB Protocol Version 2.0 Specification (IHI 0024)

- AMBA® 4 ATB Protocol Specification (IHI 0032)

- CoreSight<sup>™</sup> Components Technical Reference Manual (DDI 0314)

- Lazy Stacking and Context Switching Application Note 298 (DAI0298).

- AMBA<sup>®</sup> Low Power Interface Specification Arm<sup>®</sup> Q-Channel and P-Channel Interfaces (IHI 0068).

- Arm<sup>®</sup> Embedded Trace Macrocell Architecture Specification ETMv4 (IHI 0064).

- Arm<sup>®</sup> CoreSight<sup>™</sup> Architecture Specification v2.0 (IHI 0029).

- Arm<sup>®</sup> Debug Interface Architecture Specification, ADIv5.0 to ADIv5.2 (IHI 0031).

The following confidential books are only available to licensees:

• Arm<sup>®</sup> Cortex<sup>®</sup>-M33 Processor Integration and Implementation Manual (100323)

#### **Other publications**

- IEEE Std 1149.1-2001, Test Access Port and Boundary-Scan Architecture (JTAG).

- ANSI/IEEE Std 754-2008, IEEE Standard for Binary Floating-Point Arithmetic.

# Feedback

#### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

#### Feedback on content

If you have comments on content then send an e-mail to *errata@arm.com*. Give:

- The title Arm Cortex-M33 Processor Technical Reference Manual.

- The number 100230 0004 00 en.

- If applicable, the page number(s) to which your comments refer.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

\_\_\_\_\_ Note \_\_\_\_\_

Arm tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader.

# Part A Introduction

# Chapter A1 Introduction

This chapter introduces the Cortex-M33 processor and its features, configurable options, and product documentation.

\_\_\_\_\_ Note \_\_\_\_\_

A Cortex-M33 *Debug Access Port* (DAP) and a Cortex-M33 *Trace Port Interface Unit* (TPIU), which form part of an example system, are included in the Cortex-M33 processor deliverables. As a result, your implementation might include a Cortex-M33 DAP and a Cortex-M33 TPIU.

It contains the following sections:

- *A1.1 About the processor* on page A1-18.

- *A1.2 About the processor architecture* on page A1-19.

- *A1.3 Processor configuration options* on page A1-20.

- *A1.4 Component blocks* on page A1-22.

- *A1.5 Interfaces* on page A1-25.

- A1.6 Compliance on page A1-26.

- *A1.7 Design process* on page A1-27.

- A1.8 Documentation on page A1-28.

- *A1.9 Product revisions* on page A1-29.

# A1.1 About the processor

The Cortex-M33 processor is a low gate count, highly energy efficient processor that is intended for microcontroller and deeply embedded applications. The processor is based on the Armv8-M architecture and is primarily for use in environments where security is an important consideration.

The interfaces that the processor supports include:

- Code AHB (C-AHB) interface.

- System AHB (S-AHB) interface.

- External PPB (EPPB) APB interface.

- Debug AHB (D-AHB) interface.

The processor has optional:

- Arm TrustZone<sup>®</sup> technology, using the Armv8-M Security Extension supporting Secure and Nonsecure states.

- Memory Protection Units (MPUs), which you can configure to protect regions of memory.

- Floating-point arithmetic functionality with support for single precision arithmetic.

- Support for ETM and MTB trace.

The processor is highly configurable and is intended for a wide range of high-performance, deeply embedded applications that require fast interrupt response features.

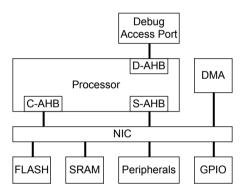

The following figure shows the processor in a typical system.

Figure A1-1 Example processor system

# A1.2 About the processor architecture

The processor implements the Armv8-M architecture with the Main Extension.

The processor has optional support for each of the following extensions:

- The Security Extension.

- The Floating-point Extension.

- The Digital Signal Processing (DSP) Extension.

- The Debug Extension.

The processor includes the following features:

- An in-order issue pipeline.

- Thumb-2 technology. See the Armv8-M Architecture Reference Manual.

- Data accesses performed as either big or little endian.

- A *Nested Vectored Interrupt Controller* (NVIC) closely integrated with the processor with up to 480 interrupts.

- An optional *Floating Point Unit* (FPU) supporting single-precision arithmetic.

- Support for exception-continuable instructions, such as LDM, LDMDB, STM, STMDB, PUSH, and POP. If the processor supports FPU, the VLDM, VSTM, VPUSH, VPOP exception-continuable instructions are also included.

- A low-cost debug solution with the optional ability to:

- Implement breakpoints.

- Implement watchpoints, tracing, and system profiling.

- Support printf() style debugging through an *Instrumentation Trace Macrocell* (ITM).

- Support for two different instruction trace options:

- *Micro Trace Buffer* (MTB). See the *Arm<sup>®</sup> CoreSight<sup>™</sup> MTB-M33 Technical Reference Manual* for more information.

- *Embedded Trace Macrocell* (ETM). See the *Arm<sup>®</sup> CoreSight<sup>™</sup> ETM-M33 Technical Reference Manual* for more information.

- Optional coprocessor interface for external hardware accelerators.

- Low-power features including architectural clock gating, sleep mode, and a power aware system with optional *Wake-up Interrupt Controller* (WIC).

- A memory system, which can include optional memory protection and security attribution.

# A1.3 Processor configuration options

The Cortex-M33 processor has configurable options that you can set during the implementation and integration stages to match your functional requirements.

| Feature                                 | Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Floating-point                          | No floating-point.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                         | Single-precision floating-point only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DSP Extension                           | No Armv8-M DSP Extension.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                         | <ul> <li>Armv8-M DSP Extension supported, including the following instruction classes:</li> <li>Pack halfword.</li> <li>Saturating.</li> <li>Arithmetic.</li> <li>Reverse bits/bytes.</li> <li>Select bytes.</li> <li>Sign-extend.</li> <li>Sum of absolute differences.</li> <li>SIMD arithmetic.</li> <li>Extended signed multiplies with overflow detection.</li> <li>Extended signed multiplies with optional rounding.</li> <li>SIMD multiplies with overflow detection.</li> <li>Extended unsigned multiply.</li> </ul> |

| Security Extension                      | No Armv8-M Security Extension.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                         | Armv8-M Security Extension.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Non-secure protected memory regions     | 0 region, 4 regions, 8 regions, 12 regions, or 16 regions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Secure protected memory regions         | 0 region, 4 regions, 8 regions, 12 regions, or 16 regions when the Armv8-M Security Extension is included.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Security Attribution Unit (SAU)         | 0 region, 4 regions, or 8 regions when the Armv8-M Security Extension is included.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Interrupts                              | 1-480 interrupts. To support non-contiguous mapping, you can remove individual interrupts.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Number of bits of interrupt priority    | Between three and eight bits of interrupt priority, between 8 and 256 levels of priority implemented.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Debug watchpoints and breakpoints       | Minimal debug. No Halting debug or memory and peripheral access.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                         | Reduced set. Two data watchpoint comparators and four breakpoint comparators.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                         | Full set. Four data watchpoint comparators and eight breakpoint comparators.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ITM and Data Watchpoint and Trace (DWT) | No ITM or DWT trace.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| trace functionality                     | Complete ITM and DWT trace.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Embedded Trace Macrocell (ETM)          | No ETM support.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                         | ETM instruction execution trace.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Micro Trace Buffer (MTB)                | No MTB support.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                         | MTB instruction trace.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

The following table shows the processor configurable options available at implementation time.

#### (continued)

| Feature                            | Options                              |

|------------------------------------|--------------------------------------|

| Cross Trigger Interface (CTI)      | No CTI.                              |

|                                    | CTI included.                        |

| Wake-up Interrupt Controller (WIC) | No WIC controller.                   |

|                                    | WIC controller included.             |

| External coprocessor interface     | No support for coprocessor hardware. |

|                                    | Support for coprocessor hardware.    |

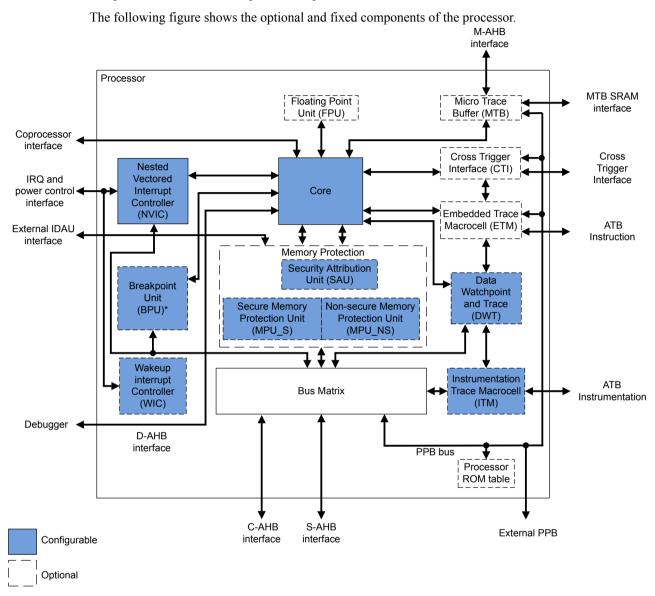

# A1.4 Component blocks

The processor has fixed and optional component blocks.

\* Flash Patching is not supported in the Cortex-M33 processor.

#### Figure A1-2 Functional block diagram

——— Note —

- The MPU\_NS, WIC, CTI, and FPU are always optional.

- If the processor is configured with minimal debug, the ETM, MTB, and ITM cannot be included.

- If the processor is configured with reduced set or full set debug, the ETM, MTB, and ITM are optional.

- If the processor is configured with the reduced set or the full set debug, the BPU and DWT are always included.

- The MPU\_S is optional if the Security Extension is present.

- The SAU is included if the Security Extension is present.

#### A1.4.1 Processor core

The processor core provides:

- Limited dual-issue of common 16-bit instruction pairs.

- Integer divide unit with support for operand-dependent early termination.

- Support for interrupted continuable load and store multiple operations.

- Load and store operations that both support precise bus errors.

#### A1.4.2 Security attribution and memory protection

The Cortex-M33 processor supports the Armv8-M Protected Memory System Architecture (PMSA) that provides programmable support for memory protection using a number of software controllable regions.

Memory regions can be programmed to generate faults when accessed inappropriately by unprivileged software reducing the scope of incorrectly written application code. The architecture includes fault status registers to allow an exception handler to determine the source of the fault and to apply corrective action or notify the system.

The Cortex-M33 processor also includes optional support for defining memory regions as *Secure* or *Non-secure*, as defined in the Armv8-M Security Extension, and protecting the regions from accesses with an inappropriate level of security.

#### **Related reference**

Chapter B3 Security Attribution and Memory Protection on page B3-53

#### A1.4.3 Floating-Point Unit

The FPU provides:

- Instructions for single-precision (C programming language float type) data-processing operations.

- Instructions for double-precision (C double type) load and store operations.

- Combined multiply-add instructions for increased precision (Fused MAC).

- Hardware support for conversion, addition, subtraction, multiplication with optional accumulate, division, and square-root.

- · Hardware support for denormals and all IEEE Standard 754-2008 rounding modes.

- 32 32-bit single-precision registers or 16 64-bit double-precision registers.

- Lazy floating-point context save. Automated stacking of floating-point state is delayed until the ISR attempts to execute a floating-point instruction. This reduces the latency to enter the ISR and removes floating-point context save for ISRs that do not use floating-point.

#### **Related reference**

Chapter B5 Floating-Point Unit on page B5-63

#### A1.4.4 Nested Vectored Interrupt Controller

The *Nested Vectored Interrupt Controller* (NVIC) is closely integrated with the core to achieve lowlatency interrupt processing.

Functions of the NVIC include:

- External interrupts, configurable from 1 to 480 using a contiguous or non-contiguous mapping. This is configured at implementation.

- Configurable levels of interrupt priority from 8 to 256. This is configured at implementation.

- Dynamic reprioritization of interrupts.

- Priority grouping. This enables selection of preempting interrupt levels and non-preempting interrupt levels.

- Support for tail-chaining and late arrival of interrupts. This enables back-to-back interrupt processing without the overhead of state saving and restoration between interrupts.

- Optional support for the Armv8-M Security extension. Secure interrupts can be prioritized above any Non-secure interrupt.

#### **Related reference**

Chapter B4 Nested Vectored Interrupt Controller on page B4-59

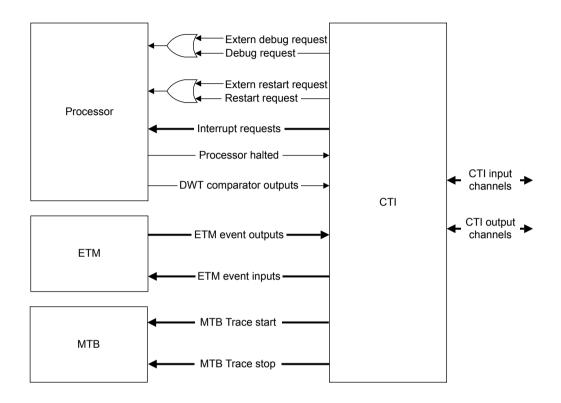

#### A1.4.5 Cross Trigger Interface Unit

The optional CTI enables the debug logic, MTB, and ETM to interact with each other and with other CoreSight components.

#### **Related reference**

Chapter C4 Cross Trigger Interface on page C4-97

#### A1.4.6 ETM

The optional ETM provides instruction-only capabilities when configured.

See the Arm<sup>®</sup> CoreSight<sup>™</sup> ETM-M33 Technical Reference Manual for more information.

#### **Related reference**

Additional reading on page 12

#### A1.4.7 MTB

The MTB provides a simple low-cost execution trace solution for the Cortex-M33 processor.

Trace is written to an SRAM interface, and can be extracted using a dedicated AHB slave interface (M-AHB) on the processor. The MTB can be controlled by memory mapped registers in the PPB region or by events generated by the DWT or through the CTI.

See the Arm<sup>®</sup> CoreSight<sup>™</sup> MTB-M33 Technical Reference Manual for more information.

#### A1.4.8 Debug and trace

Debug and trace components include a configurable *Breakpoint Unit* (BPU) for implementing breakpoints, and configurable *Data Watchpoint and Trace* (DWT) unit for implementing watchpoints, data tracing, and system profiling.

Other debug and trace components include:

- Optional ITM for support of printf() style debugging, using instrumentation trace.

- Interfaces suitable for:

- Passing on-chip data through a *Trace Port Interface Unit* (TPIU) to a *Trace Port Analyzer* (TPA), including *Serial Wire Output* (SWO) mode.

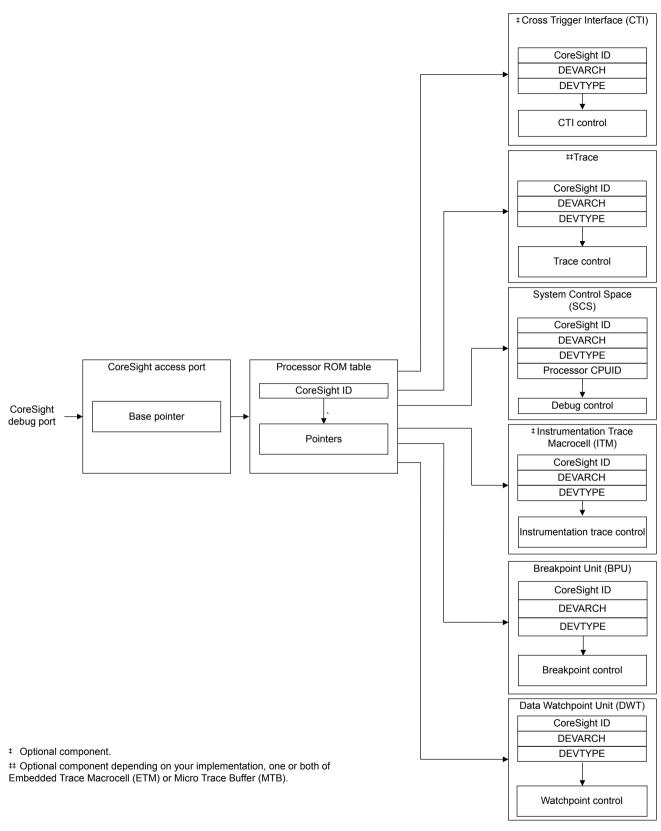

- A ROM table to allow debuggers to determine which components are implemented in the Cortex-M33 processor

- Debugger access to all memory and registers in the system, including access to memory-mapped devices, access to internal core registers when the core is halted, and access to debug control registers even when reset is asserted.

## A1.5 Interfaces

The processor has various external interfaces.

#### Code and System AHB interfaces

Harvard AHB bus architecture supporting exclusive transactions and security state.

#### System AHB interface

The *System AHB* (S-AHB) interface is used for any instruction fetch and data access to the memory-mapped SRAM, Peripheral, External RAM and External device, or Vendor\_SYS regions of the Armv8-M memory map.

#### **Code AHB interface**

The *Code AHB* (C-AHB) interface is used for any instruction fetch and data access to the Code region of the Armv8-M memory map.

#### **External Private Peripheral Bus**

The *External PPB* (EPPB) APB interface enables access to CoreSight-compatible debug and trace components in a system connected to the processor.

#### Secure attribution interface

The processor has an interface that connects to an external *Implementation Defined Attribution Unit* (IDAU), which enables your system to set security attributes based on address.

#### **ATB** interfaces

The ATB interfaces output trace data for debugging. The ATB interfaces are compatible with the CoreSight architecture. See the  $Arm^{\text{\tiny (B)}}$  CoreSight<sup> (M)</sup> Architecture Specification v2.0 for more information. The instruction ATB interface is used by the optional ETM, and the instrumentation ATB interface is used by the optional Instrumentation Trace Macrocell (ITM).

#### **Micro Trace Buffer interfaces**

The *Micro Trace Buffer* (MTB) AHB slave interface and SRAM interface are for the optional CoreSight Micro Trace Buffer.

#### **Coprocessor interface**

The coprocessor interface is designed for closely coupled external accelerator hardware.

#### **Debug AHB interface**

The *Debug AHB* (D-AHB) slave interface allows a debugger access to registers, memory, and peripherals. The D-AHB interface provides debug access to the processor and the complete memory map.

#### **Cross Trigger Interface**

The processor includes an optional *Cross Trigger Interface* (CTI) Unit that has an interface that is suitable for connection to external CoreSight components using a *Cross Trigger Matrix* (CTM).

#### Power control interface

The processor optionally supports a number of internal power domains which can be enabled and disabled using Q-channel interfaces connected to a *Power Management Unit* (PMU) in the system.

# A1.6 Compliance

The processor complies with, or implements, the relevant Arm architectural standards and protocols, and relevant external standards.

This book complements architecture reference manuals, architecture specifications, protocol specifications, and relevant external standards. It does not duplicate information from these sources.

#### Arm<sup>®</sup> architecture

The processor is compliant with the following:

- Armv8-M Main Extension.

- Armv8-M Security Extension.

- Armv8-M Protected Memory System Architecture (PMSA).

- Armv8-M Floating-point Extension.

- Armv8-M Digital Signal Processing (DSP) Extension.

- Armv8-M Debug Extension.

- Armv8-M Flash Patch Breakpoint (FPB) architecture version 2.0.

#### **Bus architecture**

The processor provides external interfaces that comply with the AMBA 5 AHB5 protocol. The processor also implements interfaces for CoreSight and other debug components using the APB4 protocol and ATBv1.1 part of the AMBA 4 ATB protocol.

For more information, see the:

- Arm<sup>®</sup> AMBA<sup>®</sup> 5 AHB Protocol Specification.

- AMBA® APB Protocol Version 2.0 Specification.

- Arm<sup>®</sup> AMBA<sup>®</sup> 4 ATB Protocol Specification ATBv1.0 and ATBv1.1.

The processor also provides a Q-Channel interface. See the AMBA<sup>®</sup> Low Power Interface Specification Arm<sup>®</sup> Q-Channel and P-Channel Interfaces

#### Debug

The debug features of the processor implement the Arm debug interface architecture.

See the Arm® Debug Interface Architecture Specification, ADIv5.0 to ADIv5.2

#### **Embedded Trace Macrocell**

The trace features of the processor implement the Arm *Embedded Trace Macrocell* (ETM) v4.2 architecture.

See the Arm<sup>®</sup> CoreSight<sup>™</sup> ETM-M33 Technical Reference Manual for more information.

#### **Floating-Point Unit**

The Cortex-M33 processor with FPU supports single-precision arithmetic as defined by the FPv5 architecture that is part of the Armv8-M architecture. The FPU provides floating-point computation functionality that is compliant with the *ANSI/IEEE Std 754-2008, IEEE Standard for Binary Floating-Point Arithmetic*.

## A1.7 Design process

The processor is delivered as synthesizable RTL that must go through implementation, integration, and programming processes before you can use it in a product.

The following definitions describe each top-level process in the design flow:

#### Implementation

The implementer configures and synthesizes the RTL.

#### Integration

The integrator connects the implemented design into a SoC. This includes connecting it to a memory system and peripherals.

#### Programming

The system programmer develops the software required to configure and initialize the processor, and tests the required application software.

Each stage in the process can be performed by a different party. Implementation and integration choices affect the behavior and features of the processor.

For MCUs, often a single design team integrates the processor before synthesizing the complete design. Alternatively, the team can synthesize the processor on its own or partially integrated, to produce a macrocell that is then integrated, possibly by a separate team.

The operation of the final device depends on:

#### **Build configuration**

The implementer chooses the options that affect how the RTL source files are pre-processed. These options usually include or exclude logic that affects one or more of the area, maximum frequency, and features of the resulting macrocell.

#### **Configuration inputs**

The integrator configures some features of the processor by tying inputs to specific values. These configurations affect the start-up behavior before any software configuration is made. They can also limit the options available to the software.

#### Software configuration

The programmer configures the processor by programming particular values into registers. This affects the behavior of the processor.

---- Note -

This manual refers to implementation-defined features that are applicable to build configuration options. Reference to a feature that is included means that the appropriate build and pin configuration options are selected. Reference to an enabled feature means one that has also been configured by software.

# A1.8 Documentation

The Cortex-M33 processor documentation can help you complete the top-level processes of implementation, integration, and programming that are required to use the product correctly.

The Cortex-M33 processor documentation comprises a Technical Reference Manual, an Integration and Implementation Manual, and User Guide Reference Material.

#### **Technical Reference Manual**

The *Technical Reference Manual* (TRM) describes the functionality and the effects of functional options on the behavior of the Cortex-M33 processor. It is required at all stages of the design flow. Some behavior described in the TRM might not be relevant because of the way that the Cortex-M33 processor is implemented and integrated. If you are programming the Cortex-M33 processor, then contact the implementer to determine:

- The build configuration of the implementation.

- What integration, if any, was performed before implementing the processor.

#### **Integration and Implementation Manual**

The Integration and Implementation Manual (IIM) describes:

- The available build configuration options and related issues in selecting them.

- How to configure the Register Transfer Level (RTL) with the build configuration options.

- How to integrate the processor into a SoC. This includes a description of the integration kit and describes the pins that the integrator must tie off to configure the macrocell for the required integration.

- The processes to sign off the integration and implementation of the design.

The Arm product deliverables include reference scripts and information about using them to implement your design.

Reference methodology documentation from your EDA tools vendor complements the IIM.

The IIM is a confidential book that is only available to licensees.

#### User Guide Reference Material

This document provides reference material that Arm partners can configure and include in a User Guide for an Arm Cortex-M33 processor. Typically:

- Each chapter in this reference material might correspond to a section in the User Guide.

- Each top-level section in this reference material might correspond to a chapter in the User Guide.

However, you can organize this material in any way, subject to the conditions of the license agreement under which Arm supplied the material.

See the *Additional reading* section for more information about the books that are associated with the Cortex-M33 processor.

#### **Related reference**

Additional reading on page 12

# A1.9 Product revisions

This section describes the differences in functionality between product revisions.

r0p0 First release.

- **r0p1** The following changes that are made in this release:

- Updated the CPUID reset value, 0x410FD211.

- The Cortex-M33 processor optionally supports stalls to guarantee the delivery of trace packets. As a result, the ITM TCR.STALLENA bit field is now RW.

- Various engineering errata fixes.

**r0p2** The following changes that are made in this release:

- Updated the CPUID reset value, 0x410FD212 in this release.

- Various engineering errata fixes.

- **r0p3** The following changes that are made in this release:

- Updated the CPUID reset value, 0x410FD213 in this release.

- Various engineering errata fixes.

**r0p4** The following changes that are made in this release:

- Updated the CPUID reset value, 0x410FD214 in this release.

- Various engineering errata fixes.

Al Introduction A1.9 Product revisions

# Part B Functional description

# Chapter B1 Programmers Model

This chapter describes the Cortex-M33 processor register set, modes of operation, and provides other information for programming the processor.

It contains the following sections:

- *B1.1 About the programmers model* on page B1-34.

- *B1.2 Modes of operation and execution* on page B1-35.

- *B1.3 Instruction set summary* on page B1-36.

- *B1.4 Memory model* on page B1-37.

- *B1.5 Exclusive monitor* on page B1-39.

- B1.6 Processor core registers summary on page B1-40.

- *B1.7 Exceptions* on page B1-42.

# B1.1 About the programmers model

The Cortex-M33 programmers model is an implementation of the Armv7-M Main Extension architecture.

For a complete description of the programmers model, refer to the *Armv7-M Architecture Reference Manual*, which also contains the Armv7-M Thumb<sup>®</sup> instructions. In addition, other options of the programmers model are described in the System Control, MPU, NVIC, FPU, Debug, DWT, ITM, and TPIU features topics.

#### **Related reference**

Chapter B2 System Control on page B2-43 Chapter B3 Security Attribution and Memory Protection on page B3-53 Chapter B4 Nested Vectored Interrupt Controller on page B4-59 Chapter B5 Floating-Point Unit on page B5-63 Chapter C1 Debug on page C1-79 Chapter C3 Data Watchpoint and Trace Unit on page C3-93 Chapter C2 Instrumentation Trace Macrocell Unit on page C2-87

# B1.2 Modes of operation and execution

The Cortex-M33 processor supports Secure and Non-secure security states, Thread and Handler operating modes, and can run in either Thumb or Debug operating states. In addition, the processor can limit or exclude access to some resources by executing code in privileged or unprivileged mode.

See the Armv8-M Architecture Reference Manual for more information about the modes of operation and execution.

#### Security states

When the Armv8-M Security Extension is included in the processor, the programmers model includes two orthogonal security states, Secure state and Non-secure state. When the Security Extension is implemented, the processor always resets into Secure state. When the security state is not implemented, the processor resets into Non-secure state. Each security state includes a set of independent operating modes and supports both privileged and unprivileged user access. Registers in the System Control Space are banked across Secure and Non-secure state, with the Non-secure register view available at an aliased address to Secure state. When the Armv8-M Security Extension is not included in the processor, the programmers model includes only the Non-secure state.

#### **Operating modes**

For each security state, the processor can operate in Thread or Handler mode. The conditions which cause the processor to enter Thread or Handler mode are as follows:

- The processor enters Thread mode on reset, or as a result of an exception return to Thread mode. Privileged and Unprivileged code can run in Thread mode.

- The processor enters Handler mode as a result of an exception. All code is privileged in Handler mode.

The processor can change security state on taking an exception, for example when a Secure exception is taken from Non-secure state, the Thread mode enters the Secure state Handler mode.

The processor can also call Secure functions from Non-secure state and Non-secure functions from Secure state. The Security Extension includes requirements for these calls to prevent secure data from being accessed in Non-secure state.

#### **Operating states**

The processor can operate in Thumb or Debug state:

- Thumb state is the state of normal execution running 16-bit and 32-bit halfword-aligned Thumb instructions.

- Debug state is the state when the processor is in Halting debug.

#### Privileged access and unprivileged user access

Code can execute as privileged or unprivileged. Unprivileged execution limits or excludes access to some resources appropriate to the current security state. Privileged execution has access to all resources available to the security state. Handler mode is always privileged. Thread mode can be privileged or unprivileged.

# B1.3 Instruction set summary

The processor implements the following instruction from Armv8-M:

- All base instructions.

- All instructions in the Main Extension.

- Optionally all instructions in the Security Extension.

- Optionally all instructions in the DSP Extension.

- Optionally all single-precision instructions and double precision load and store instructions in the Floating-point Extension.

For more information about Armv8-M instructions, see the Armv8-M Architecture Reference Manual.

# B1.4 Memory model

The processor contains a bus matrix that arbitrates instruction fetches and memory accesses from the processor core between the external memory system and the internal *System Control Space* (SCS) and debug components.

Priority is usually given to the processor to ensure that any debug accesses are as non-intrusive as possible.

The system memory map is Armv8-M Main Extension compliant, and is common both to the debugger and processor accesses.

The default memory map provides user and privileged access to all regions except for the *Private Peripheral Bus* (PPB). The PPB space is privileged access only.

The following table shows the default memory map. This is the memory map that is used by implementations without the optional MPUs, or when the included MPUs are disabled. The attributes and permissions of all regions, except that targeting the NVIC and debug components, can be modified using an implemented MPU.

| Address Range (inclusive)                                                                                   | Region                                                                     | Interface                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 0x00000000-0x1FFFFFFF                                                                                       | Code                                                                       | Instruction and data accesses performed on C-AHB.                                                                            |

| 0x20000000-0x3FFFFFFF                                                                                       | SRAM                                                                       | Instruction and data accesses performed on S-AHB. Any attempt to execute                                                     |

| 0x40000000-0x5FFFFFFF                                                                                       | Peripheral                                                                 | instructions from the peripheral and external device region results in a MemManage fault.                                    |

| 0x60000000-0x9FFFFFFF                                                                                       | External RAM                                                               | Taut.                                                                                                                        |

| 0xA0000000-0xDFFFFFF                                                                                        | External device                                                            |                                                                                                                              |

| 0xE0040000-0xE00FFFFF                                                                                       | PPB                                                                        | Reserved for system control and debug.                                                                                       |

| Cannot be used for exception vector tables. Data acceleration internally or on EPPB. Accesses in the range: |                                                                            | Cannot be used for exception vector tables. Data accesses are either performed internally or on EPPB. Accesses in the range: |

|                                                                                                             |                                                                            | <b>0xE000000-0xE0043FFF</b><br>Are handled within the processor.                                                             |

|                                                                                                             |                                                                            | <b>0xE0044000-0xE00FFFF</b><br>Appear as APB transactions on the EPPB interface of the processor.                            |

|                                                                                                             |                                                                            | Any attempt to execute instructions from the region results in a MemManage fault.                                            |

| 0xE0100000-0xFFFFFFFF                                                                                       | Vendor_SYS         Partly reserved for future processor feature expansion. |                                                                                                                              |

|                                                                                                             |                                                                            | Any attempt to execute instructions from the region results in a MemManage fault.                                            |

|                                                                                                             |                                                                            | Data accesses are performed on S-AHB                                                                                         |

#### **Default memory map**

When the Armv8-M Security Extension is included, the security level associated with an address is determined by either the internal *Secure Attribution Unit* (SAU) or an external *Implementation Defined Attribution Unit* (IDAU) in the system. Some internal peripherals have memory-mapped registers in the PPB region which are banked between Secure and Non-secure state. When the processor is in Secure state, software can access both the Secure and Non-secure versions of these registers. The Non-secure versions are accessed using an aliased address. If the Armv8-M Security Extension is not included, all memory is treated as Non-secure.

See the Armv8-M Architecture Reference Manual for more information about the memory model.

# B1.4.1 Private Peripheral Bus

The *Private Peripheral Bus* (PPB) memory region provides access to internal and external processor resources.

The internal PPB provides access to:

- The System Control Space (SCS), including the Memory Protection Unit (MPU), Secure Attribution Unit (SAU), if included, and the Nested Vectored Interrupt Controller (NVIC).

- The Data Watchpoint and Trace (DWT) unit, if included.

- The Breakpoint Unit (BPU), if included.

- The Embedded Trace Macrocell (ETM), if included.

- CoreSight Micro Trace Buffer (MTB), if included.

- Cross Trigger Interface (CTI), if included.

- The ROM table.

The external PPB (EPPB) provides access to:

• Implementation-specific external areas of the PPB memory map.

## B1.4.2 Unaligned accesses

The Cortex-M33 processor supports unaligned accesses. They are converted into two or more aligned AHB transactions on the C-AHB or S-AHB master ports on the processor.

Unaligned support is only available for load/store singles (LDR, LDRH, STR, STRH, TBH) to addresses in Normal memory. Load/store double and load/store multiple instructions already support word aligned accesses, but do not permit other unaligned accesses, and generate a fault if this is attempted. Unaligned accesses in Device memory are not permitted and fault. Unaligned accesses that cross memory map boundaries are architecturally UNPREDICTABLE.

—— Note —

If CCR.UNALIGN\_TRP for the current Security state is set, any unaligned accesses generate a fault.

# B1.5 Exclusive monitor

The Cortex-M33 processor implements a local exclusive monitor. The local monitor within the processor has been constructed so that it does not hold any physical address, but instead treats any store-exclusive access as matching the address of the previous load-exclusive. This means that the implemented exclusives reservation granule is the entire memory address range.

For more information about semaphores and the local exclusive monitor, see the *Armv7-M Architecture Reference Manual*.

# B1.6 Processor core registers summary

The following table shows the processor core register set summary. Each of these registers is 32 bits wide. When the Armv8-M Security Extension is included, some of the registers are banked. The Secure view of these registers is available when the Cortex-M33 processor is in Secure state and the Non-secure view when Cortex-M33 processor is in Non-secure state.

#### Table B1-1 Processor core register set summary

| Name                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R0-R12                 | R0-R12 are general-purpose registers for data operations.                                                                                                                                                                                                                                                                                                                                                                        |

| MSP (R13)<br>PSP (R13) | The <i>Stack Pointer</i> (SP) is register R13. In Thread mode, the CONTROL register indicates the stack pointer to use,<br><i>Main Stack Pointer</i> (MSP) or <i>Process Stack Pointer</i> (PSP).                                                                                                                                                                                                                                |

| 131 (K13)              | <ul> <li>When the Armv8-M Security Extension is included, there are two MSP registers in the Cortex-M33 processor:</li> <li>MSP_NS for the Non-secure state.</li> <li>MSP_S for the Secure state.</li> </ul>                                                                                                                                                                                                                     |

|                        | <ul> <li>When the Armv8-M Security Extension is included, there are two PSP registers in the Cortex-M33 processor:</li> <li>PSP_NS for the Non-secure state.</li> <li>PSP_S for the Secure state.</li> </ul>                                                                                                                                                                                                                     |

| MSPLIM                 | The stack limit registers limit the extent to which the MSP and PSP registers can descend respectively.                                                                                                                                                                                                                                                                                                                          |

| PSPLIM                 | <ul> <li>When the Armv8-M Security Extension is included, there are two MSPLIM registers in the Cortex-M33 processor:</li> <li>MSPLIM_NS for the Non-secure state.</li> <li>MSPLIM_S for the Secure state.</li> </ul>                                                                                                                                                                                                            |

|                        | <ul> <li>When the Armv8-M Security Extension is included, there are two PSPLIM registers in the Cortex-M33 processor:</li> <li>PSPLIM_NS for the Non-secure state.</li> <li>PSPLIM_S for the Secure state.</li> </ul>                                                                                                                                                                                                            |

| LR (R14)               | The <i>Link Register</i> (LR) is register R14. It stores the return information for subroutines, function calls, and exceptions.                                                                                                                                                                                                                                                                                                 |

| PC (R15)               | The Program Counter (PC) is register R15. It contains the current program address.                                                                                                                                                                                                                                                                                                                                               |

| PSR                    | The Program Status Register (PSR) combines:         • Application Program Status Register (APSR).         • Interrupt Program Status Register (IPSR).         • Execution Program Status Register (EPSR).         These registers provide different views of the PSR.                                                                                                                                                            |

| PRIMASK                | <ul> <li>The PRIMASK register prevents activation of exceptions with configurable priority. For information about the exception model the processor supports, see <i>B1.7 Exceptions</i> on page B1-42.</li> <li>When the Armv8-M Security Extension is included, there are two PRIMASK registers in the Cortex-M33 processor:</li> <li>PRIMASK_NS for the Non-secure state.</li> <li>PRIMASK_S for the Secure state.</li> </ul> |

| BASEPRI                | <ul> <li>The BASEPRI register defines the minimum priority for exception processing.</li> <li>When the Armv8-M Security Extension is included, there are two BASEPRI registers in the Cortex-M33 processor:</li> <li>BASEPRI_NS for the Non-secure state.</li> <li>BASEPRI_S for the Secure state.</li> </ul>                                                                                                                    |

# Table B1-1 Processor core register set summary (continued)

| Name      | Description                                                                                                                                                                                                                                                                                                             |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FAULTMASK | The FAULTMASK register prevents activation of all exceptions except for NON-MASKABLE INTERRUPT (NMI) and optionally Secure HardFault.                                                                                                                                                                                   |

|           | <ul> <li>When the Armv8-M Security Extension is included, there are two FAULTMASK registers in the Cortex-M33 processor:</li> <li>FAULTMASK_NS for the Non-secure state.</li> <li>FAULTMASK_S for the Secure state.</li> </ul>                                                                                          |

| CONTROL   | The CONTROL register controls the stack used, and optionally the privilege level, when the processor is in Thread mode.<br>When the Armv8-M Security Extension is included, there are two CONTROL registers in the Cortex-M33 processor:<br>• CONTROL_NS for the Non-secure state.<br>• CONTROL_S for the Secure state. |

\_\_\_\_\_ Note \_\_\_\_\_

See the *Armv8-M Architecture Reference Manual* for information about the processor core registers and their addresses, access types, and reset values.

# B1.7 Exceptions

Exceptions are handled and prioritized by the processor and the NVIC. In addition to architecturally defined behavior, the processor implements advanced exception and interrupt handling that reduces interrupt latency and includes implementation defined behavior.

## B1.7.1 Exception handling and prioritization

The processor core and the *Nested Vectored Interrupt Controller* (NVIC) together prioritize and handle all exceptions.

When handling exceptions:

- All exceptions are handled in Handler mode.

- Processor state is automatically stored to the stack on an exception, and automatically restored from the stack at the end of the *Interrupt Service Routine* (ISR).

- The vector is fetched in parallel to the state saving, enabling efficient interrupt entry.

The processor supports tail-chaining that enables back-to-back interrupts without the overhead of state saving and restoration.

You configure the number of interrupts, and bits of interrupt priority, during implementation. Software can choose only to enable a subset of the configured number of interrupts, and can choose how many bits of the configured priorities to use.

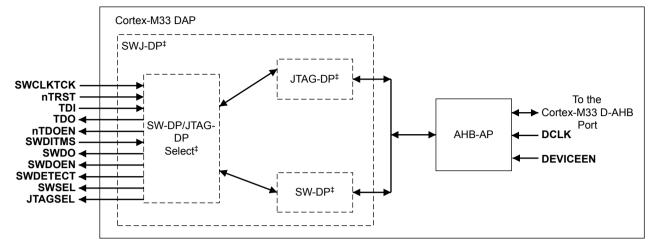

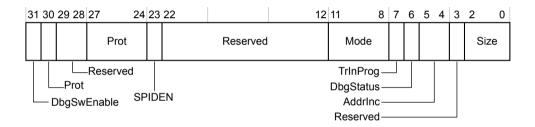

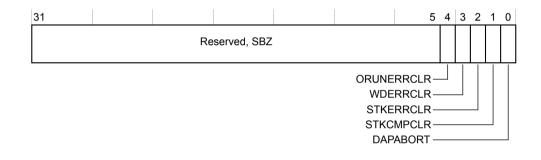

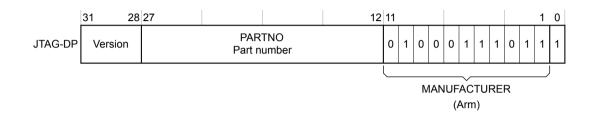

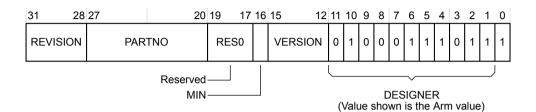

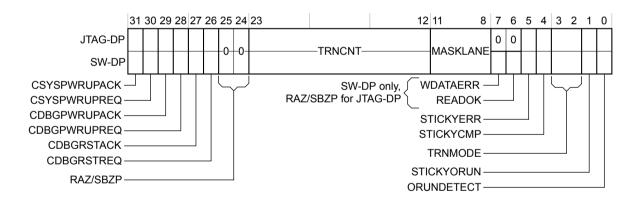

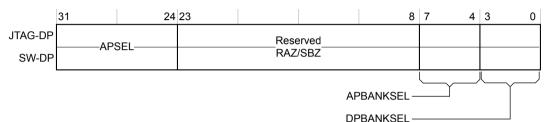

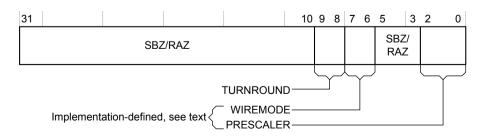

When the Armv8-M Security Extension is included, exceptions can be specified as either Secure or Nonsecure. When an exception is taken the processor switches to the associated security state. The priority of Secure and Non-secure exceptions can be programmed independently. It is possible to deprioritize Nonsecure configurable exceptions using the AIRCR.PRIS bit field to enable Secure interrupts to take priority.