# Arm<sup>®</sup> CoreSight<sup>™</sup> ELA-500 Embedded Logic Analyzer

Revision: r2p2

**Technical Reference Manual**

# Arm® CoreSight™ ELA-500 Embedded Logic Analyzer

# **Technical Reference Manual**

Copyright © 2014-2016, 2018 Arm Limited or its affiliates. All rights reserved.

#### **Release Information**

# **Document History**

| Issue      | Date              | Confidentiality  | Change                       |

|------------|-------------------|------------------|------------------------------|

| 0000-00-01 | 30 September 2014 | Confidential     | First draft for r0p0 at BETA |

| 0000-01    | 23 January 2015   | Confidential     | First release for r0p0       |

| 0000-02    | 20 March 2015     | Non-Confidential | Second release for r0p0      |

| 0100-00    | 30 October 2015   | Non-Confidential | First release for r1p0       |

| 0200-00    | 23 May 2016       | Non-Confidential | First release for r2p0       |

| 0201-00    | 09 September 2016 | Non-Confidential | First release for r2p1       |

| 0202-00    | 18 November 2016  | Non-Confidential | First release for r2p2       |

| 0202-01    | 30 September 2018 | Non-Confidential | Second release for r2p2      |

# **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or TM are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the

trademarks of their respective owners. Please follow Arm's trademark usage guidelines at http://www.arm.com/company/policies/trademarks.

Copyright © 2014–2016, 2018 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

# **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

# **Product Status**

The information in this document is Final, that is for a developed product.

# **Web Address**

http://www.arm.com

# Contents

# **Arm® CoreSight™ ELA-500 Embedded Logic Analyzer Technical Reference Manual**

|           | Pret  | race and the second |      |

|-----------|-------|----------------------------------------------------------------------------------------------------------------|------|

|           |       | About this book                                                                                                | 7    |

|           |       | Feedback                                                                                                       | 10   |

| Chapter 1 | Intro | oduction                                                                                                       |      |

|           | 1.1   | About the ELA-500 Embedded Logic Analyzer                                                                      | 1-12 |

|           | 1.2   | Definitions of terms used in this book                                                                         | 1-13 |

|           | 1.3   | Compliance                                                                                                     | 1-14 |

|           | 1.4   | Features                                                                                                       | 1-15 |

|           | 1.5   | Interfaces                                                                                                     | 1-16 |

|           | 1.6   | Configuration options                                                                                          | 1-17 |

|           | 1.7   | Test features                                                                                                  | 1-18 |

|           | 1.8   | Product documentation and design flow                                                                          | 1-19 |

|           | 1.9   | Product revisions                                                                                              | 1-21 |

| Chapter 2 | Fun   | ctional description                                                                                            |      |

|           | 2.1   | About the functions                                                                                            | 2-23 |

|           | 2.2   | Interfaces                                                                                                     | 2-25 |

|           | 2.3   | Clocking and reset                                                                                             | 2-27 |

|           | 2.4   | Trace control and capture                                                                                      | 2-29 |

|           | 2.5   | Triggering                                                                                                     | 2-33 |

|           | 2.6   | Authentication interface                                                                                       |      |

|            | 2.7  | Parameter summary                      | 2-39      |

|------------|------|----------------------------------------|-----------|

| Chapter 3  | Prog | grammers model                         |           |

|            | 3.1  | Access permissions                     |           |

|            | 3.2  | Programming sequence                   | 3-43      |

|            | 3.3  | Control register summary               | 3-44      |

|            | 3.4  | Control register descriptions          | 3-45      |

|            | 3.5  | Current State register summary         | 3-48      |

|            | 3.6  | Current State register descriptions    |           |

|            | 3.7  | RAM register summary                   | 3-51      |

|            | 3.8  | RAM register descriptions              | 3-52      |

|            | 3.9  | Trigger State register summary         | 3-55      |

|            | 3.10 | Trigger State register descriptions    |           |

|            | 3.11 | Integration Mode register summary      | 3-67      |

|            | 3.12 | Integration Mode register descriptions | 3-68      |

|            | 3.13 | Software Lock register summary         | 3-70      |

|            | 3.14 | Software Lock register descriptions    |           |

|            | 3.15 | Authentication register summary        | 3-72      |

|            | 3.16 | Authentication register descriptions   | 3-73      |

|            | 3.17 | Device register summary                | 3-74      |

|            | 3.18 | Device register descriptions           | 3-75      |

|            | 3.19 | ID register summary                    | 3-78      |

|            | 3.20 | ID register descriptions               |           |

| Appendix A | Sign | al descriptions                        |           |

|            | A.1  | Clocks and reset                       | Appx-A-85 |

|            | A.2  | Debug APB signals                      | Appx-A-86 |

|            | A.3  | Observation interface signals          | Appx-A-87 |

|            | A.4  | Timestamp interface signals            | Appx-A-88 |

|            | A.5  | Authentication interface signals       | Appx-A-89 |

|            | A.6  | DFT and MBIST interface signals        | Appx-A-90 |

|            | A.7  | Q-Channel Low-Power interface signals  | Appx-A-91 |

|            | A.8  | Output Action signals                  | Appx-A-92 |

|            | A.9  | External Trigger Input signals         |           |

| Appendix B | Revi | sions                                  |           |

|            | B.1  | Revisions                              | Appx-B-95 |

# **Preface**

This preface introduces the  $Arm^*$   $CoreSight^*$  ELA-500 Embedded Logic Analyzer Technical Reference Manual.

It contains the following:

- About this book on page 7.

- Feedback on page 10.

# About this book

This book is for the Arm® CoreSight ELA-500 Embedded Logic Analyzer.

# **Product revision status**

The rmpn identifier indicates the revision status of the product described in this book, for example, r1p2, where:

rm Identifies the major revision of the product, for example, r1.

pn Identifies the minor revision or modification status of the product, for example, p2.

# Intended audience

This book is written for system designers, system integrators, and programmers who are designing or programming a *System-on-Chip* (SoC) that uses the ELA-500.

# Using this book

This book is organized into the following chapters:

# **Chapter 1 Introduction**

This chapter describes the ELA-500 Embedded Logic Analyzer.

# **Chapter 2 Functional description**

This chapter describes the functionality of the ELA-500.

# Chapter 3 Programmers model

This chapter describes the programmers model.

# Appendix A Signal descriptions

This appendix describes the external signals of the ELA-500.

# Appendix B Revisions

This appendix describes the technical changes between released issues of this book.

# Glossary

The Arm® Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

See the *Arm*<sup>®</sup> *Glossary* for more information.

# Typographic conventions

italic

Introduces special terminology, denotes cross-references, and citations.

# bold

Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.

# monospace

Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.

# <u>mono</u>space

Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.

# monospace italic

Denotes arguments to monospace text where the argument is to be replaced by a specific value.

# monospace bold

Denotes language keywords when used outside example code.

<and>

Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:

SMALL CAPITALS

Used in body text for a few terms that have specific technical meanings, that are defined in the *Arm® Glossary*. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE.

# **Timing diagrams**

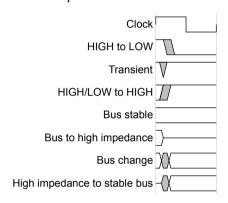

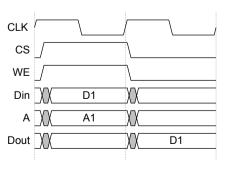

The following figure explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

Figure 1 Key to timing diagram conventions

# **Signals**

The signal conventions are:

# Signal level

The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals.

- LOW for active-LOW signals.

# Lowercase n

At the start or end of a signal name denotes an active-LOW signal.

# Additional reading

This section lists publications by ARM and by third parties.

See Infocenter http://infocenter.arm.com, for access to ARM documentation.

# **ARM** publications

This book contains information that is specific to this product. See the following documents for other relevant information:

- AMBA® Low Power Interface Specification, Arm® Q-Channel and P-Channel Interfaces (ARM IHI 0068).

- AMBA® AXI and ACE Protocol Specification (ARM IHI 0022).

- AMBA® APB Protocol Specification (ARM IHI 0024).

- *ARM*<sup>®</sup> *CoreSight*<sup>™</sup> *Architecture Specification* (ARM IHI 0029).

The following confidential books are only available to licensees:

• Arm® CoreSight™ ELA-500 Embedded Logic Analyzer Integration and Implementation Manual (ARM 100129).

# Other publications

This section lists relevant documents published by third parties:

• JEDEC Standard Manufacturer's Identification Code, JEP106 http://www.jedec.org.

# **Feedback**

# Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

# Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- The title Arm CoreSight ELA-500 Embedded Logic Analyzer Technical Reference Manual.

- The number 100127\_0202\_01\_en.

- If applicable, the page number(s) to which your comments refer.

- A concise explanation of your comments.

| Arm also welcomes general suggestions for additions and improvements.                                                                                |           |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Note                                                                                                                                                 |           |

| Arm tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quali represented document when used with any other PDF reader. | ty of the |

# Chapter 1 Introduction

This chapter describes the ELA-500 Embedded Logic Analyzer.

# It contains the following sections:

- 1.1 About the ELA-500 Embedded Logic Analyzer on page 1-12.

- 1.2 Definitions of terms used in this book on page 1-13.

- 1.3 Compliance on page 1-14.

- 1.4 Features on page 1-15.

- 1.5 Interfaces on page 1-16.

- 1.6 Configuration options on page 1-17.

- 1.7 Test features on page 1-18.

- 1.8 Product documentation and design flow on page 1-19.

- 1.9 Product revisions on page 1-21.

# 1.1 About the ELA-500 Embedded Logic Analyzer

The ELA-500 Embedded Logic Analyzer is a component for debugging hardware-related issues.

Debug signals are connected from the IP being debugged to the ELA-500, which compares the signals with a target value and drives actions. There is an optional trace capability that can be used to generate a history of the debug signals at any point in time.

# 1.2 Definitions of terms used in this book

This Technical Reference Manual uses terms that are specific to the ELA-500 Embedded Logic Analyzer.

The following terms have specific meanings within the context of this Technical Reference Manual. Wherever they are used throughout the book they are shown in *italics* and have the meanings that are shown here:

# **Trigger State**

One of the five states that the ELA-500 trigger logic can be in. The *Trigger State* controls which *Signal Group* signals are routed to the comparison logic, target comparison values, comparison and counter control, and output actions. The ELA-500 advances to the next *Trigger State* when its *Trigger Condition* is met.

| Note                           |                                                       |

|--------------------------------|-------------------------------------------------------|

| The sequence of Trigger States | is programmable and does not depend on implementation |

# **Trigger Signal Comparison**

The comparison of the *External Trigger Input Signals* and selected *Signal Group* with a target value and mask that is determined by the current *Trigger State*.

# **Trigger Counter Comparison**

The comparison of the up-counter of the current *Trigger State* with its target value. The counter can be incremented by **ELACLK** or by *Trigger Signal Comparison* matches. The counter can be reset by a *Trigger Signal Comparison* match.

# **Trigger Signal Alternative Comparison**

An alternative comparison of the *External Trigger Input Signals* and selected *Signal Group* with a target value and mask that is determined by the current *Trigger State*.

# **Trigger Condition**

When the *Trigger Condition* is met, the ELA-500 generates an *Output Action* and transitions to the next *Trigger State*. If *Trigger Counter Comparison* is enabled, the *Trigger Condition* is met when the *Trigger Counter Comparison* is true. If *Trigger Counter Comparison* is disabled, the *Trigger Condition* is met when the *Trigger Signal Comparison* is met.

# **External Trigger Input Signals**

The ELA-500 supports eight input signals that can form part of the *Trigger Signal Comparison*. The *External Trigger Input Signals* can come from other ELA-500 instances, a CoreSight Cross Trigger Interface, or other logic in the SoC.

# **Signal Group**

A group of input signals from the Observation interface. The ELA-500 supports up to 12 *Signal Groups*, each of which is 64 bits, 128 bits, or 256 bits wide, determined by the GRP\_WIDTH parameter.

# **Output Action**

The ELA-500 generates an *Output Action* when the *Trigger Condition* is met.

The Output Action can:

- Drive the STOPCLOCK output for scan-dump analysis.

- Drive a CoreSight Embedded Cross Trigger through **CTTRIGOUT[1:0]** to a CoreSight *Cross Trigger Interface* (CTI).

- Drive other logic through **ELAOUTPUT**[3:0].

# 1.3 Compliance

The ELA-500 implements the Arm CoreSight Architecture Specification. It complies with the AMBA APB Protocol and the Arm Low Power interface Q-Channel specification.

This Technical Reference Manual complements architecture reference manuals, architecture specifications, protocol specifications, and relevant external standards. It does not duplicate information from these sources.

See the  $Arm^*$   $AMBA^*$  APB Protocol Specification, the  $Arm^*$   $CoreSight^{\mathsf{TM}}$  Architecture Specification, and the  $Arm^*$  Low Power Interface Specification, Q-Channel and P-Channel Interfaces for more information.

# 1.4 Features

The ELA-500 has many features. Some of the key features are programmable *Trigger States*, programmable *Output Actions* for each *Trigger State*, and additional *External Trigger Input Signals*.

The ELA-500 has the following key features:

- Four programmable *Trigger States*.

- Eight programmable actions, to allow each *Trigger State* to control:

- Stop clock.

- Trace control.

- CoreSight cross-trigger.

- Four general-purpose trigger outputs.

- A programmable 32-bit counter for each *Trigger State* that can be used to delay output actions, count events, or as a watchdog timer.

- An Observation interface consisting of 12 *Signal Groups* with a configurable width of 64, 128, or 256 debug signals.

- Eight External Trigger Input Signals that can be masked and compared against a target value for each Trigger State. An Output Action from one logic analyzer can be connected to these inputs on a second logic analyzer to cause a direct cross-trigger, independently of the CoreSight Embedded Cross Trigger (ECT) infrastructure. This feature enables users to have a lower-latency Embedded Logic Analyzer (ELA) cross-trigger mechanism that does not rely on the correct operation of software-debug cross-triggering components.

- Programmable *Trigger Condition* comparison with the ability to change the target comparison by selectively masking signals, and selecting =, !=, <, <=, >, >= for comparison of the masked signals and counter target value comparisons.

- Programmable *Trigger Alternative Condition* comparison with the ability to change the target comparison by selectively masking signals, and selecting =, !=, <, <=, >, >=, for comparison of the masked signals and counter target value comparisons.

- Optional support of signal trace using an integrated SRAM. The SRAM trace depth is configurable.

Timestamp trace capture is possible and enables correlation of ELA trace with other CoreSight trace sources.

# 1.5 Interfaces

The ELA-500 has numerous external interfaces, including interfaces for debug signals, trigger inputs, and authentication permissions.

The ELA-500 has the following external interfaces:

- An Observation interface to capture signals from the IP being debugged.

- An *External Trigger Input Signals* interface that enables the ELA-500 to be triggered by external logic.

- An Authentication interface that determines the type of accesses permitted.

- A debug APB slave interface that enables access to the configuration and status registers.

- An SRAM interface to enable access to SRAM for trace data capture.

- A timestamp interface to provide timestamp information with captured trace data.

- A Low-Power Q-Channel interface to determine when **ELACLK** can be stopped.

- A Memory Built-In Self-Test (MBIST) interface for testing SRAM.

# 1.6 Configuration options

This section describes the configuration options available in the ELA-500.

# 1.6.1 Configurable parameters

There are several configurable options available in the ELA-500.

Related concepts

2.7 Parameter summary on page 2-39

# 1.6.2 Static parameters

There are no configurable static parameters in the ELA-500.

# 1.6.3 Tie-off signals

There are no configurable tie-off signals in the ELA-500.

# 1.7 Test features

The ELA-500 has several test features.

See the *Arm® CoreSight™ ELA-500 Embedded Logic Analyzer Integration and Implementation Manual* for information about the test features.

# 1.8 Product documentation and design flow

The ELA-500 documentation includes a Technical Reference Manual and an Integration and Implementation Manual. These books relate to the ELA-500 design flow.

# **Documentation**

The ELA-500 documentation includes the following books:

# **Technical Reference Manual**

The *Technical Reference Manual* (TRM) describes the functionality and the effects of functional options on the behavior of the ELA-500. It is required at all stages of the design flow. The choices that you make in the design flow can mean that some behavior described in the TRM is not relevant. If you are programming the ELA-500 then contact:

- The implementer to determine:

- What integration, if any, was performed before implementing the ELA-500.

- The build configuration of the implementation.

Note

Build configuration information is also readable from the DEVID registers.

- The integrator to determine the pin configuration of the device that you are using.

# **Integration and Implementation Manual**

The Integration and Implementation Manual (IIM) describes:

- The available build configuration options and related issues in selecting them.

- How to configure the *Register Transfer Level* (RTL) with the build configuration options.

- How to integrate the ELA-500 into a SoC. This includes a description of the integration kit

and describes the pins that the integrator must tie off to configure the macrocell for the

required integration.

- How to implement the ELA-500 into your design. This includes floorplanning guidelines, Design for Test (DFT) information, and how to perform netlist dynamic verification on the ELA-500.

- The processes to sign off the integration and implementation of the design.

The Arm product deliverables include reference scripts and information about using them to implement your design.

Reference methodology documentation from your EDA tools vendor complements the IIM.

The IIM is a confidential book that is only available to licensees.

# **Design flow**

The ELA-500 is delivered as synthesizable RTL. Before it can be used in a product, it must go through the following processes:

# **Implementation**

The implementer configures and synthesizes the RTL to produce a hard macrocell. This includes integrating RAMs into the design.

# Integration

The integrator connects the implemented design into a SoC. This includes connecting it to a memory system and peripherals.

# **Programming**

This is the final process. The system programmer develops the software that is required to configure and initialize the ELA-500, and tests the required application software.

# Each process:

- Can be performed by a different party.

- Can include implementation and integration choices that affect the behavior and features of the ELA-500.

The operation of the final device depends on:

# **Build configuration**

The implementer chooses the options that affect how the RTL source files are pre-processed. These options usually include or exclude logic that affects one or more of the area, maximum frequency, and features of the resulting macrocell.

# Software configuration

| The programmer configures the ELA-500 by programming particular values into registers. This affects the behavior of the ELA-500.                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                          |

| This Technical Reference Manual refers to implementation-defined features that are applicable to build configuration options. Reference to a feature that is included means that the appropriate build and pin configuration options are selected. Reference to an enabled feature means a feature that has been configured by software. |

# 1.9 Product revisions

This section describes the differences in functionality between product revisions of the ELA-500.

r0p0

First release.

r1p0

Adds new features to support the interconnect. These features are disabled by default with parameters. The ELA-500 is backward compatible with revision r0p0.

The new features are:

- Conditional Trigger States.

- Transaction ID capture for use in a subsequent *Trigger State* comparison.

- Addition of a fifth Trigger State Trigger State 4.

- *Trigger State* 4 can run a separate comparator and trace in a separate loop to the other four *Trigger States*. Trace from *Trigger State* 4 dominates trace writes that occur at the same time from any of the other four *Trigger States*.

# Other changes in r1p0 are:

- DEVID2 and PID2 registers added.

- CTSR bit 31 FINALSTATE added.

r2p0

Adds the following new features:

- Support for 256-bit SIGNALGRPs and trace.

- A trace read data scrambler to protect exposure of designs that are sensitive to signal trace.

- The trace read data scrambler has added new parameters.

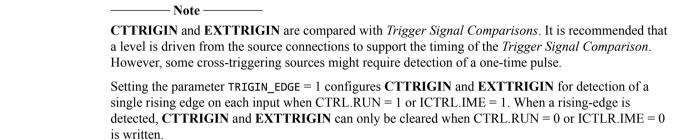

- The new TRIGIN\_EDGE parameter supports a single rising-edge trigger inputs.

- A single rising-edge trigger configuration for CTTRIGIN and EXTRIGIN cross trigger inputs.

- The Peripheral ID2 register [7:4] REVISION field was changed from 0x1 to 0x2 to identify r2p0.

r2p1

Adds the following features:

- Synchronizers replaced with a cell model.

- Peripheral ID2 register bits [7:4] REVISION field changed from 0x2 to 0x3 to identify r2p1.

r2p2

Adds the following features:

• Peripheral ID2 register bits [7:4] REVISION field changed from 0x3 to 0x4 to identify r2p2.

# Chapter 2 **Functional description**

This chapter describes the functionality of the ELA-500.

It contains the following sections:

- 2.1 About the functions on page 2-23.

- 2.2 Interfaces on page 2-25.

- 2.3 Clocking and reset on page 2-27.

- 2.4 Trace control and capture on page 2-29.

- 2.5 Triggering on page 2-33.

- 2.6 Authentication interface on page 2-38.

- 2.7 Parameter summary on page 2-39.

# 2.1 About the functions

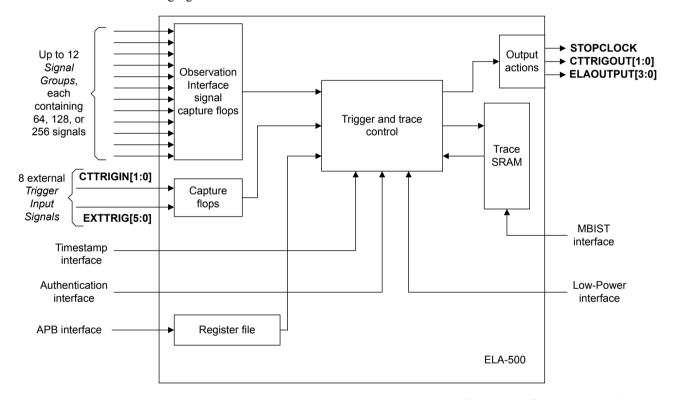

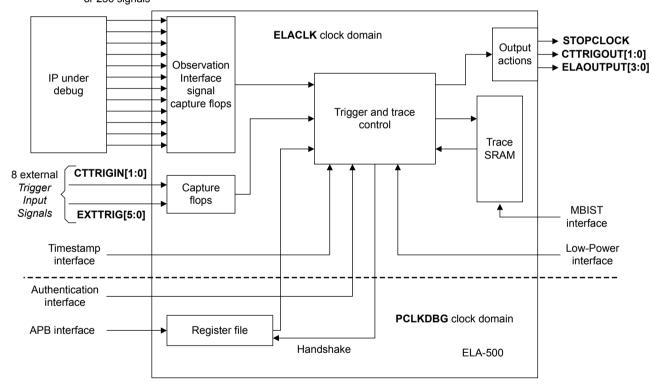

This section describes the functional blocks in the ELA-500.

The ELA-500 can be configured to have 64, 128, or 256 debug signals in a *Signal Group*. There are eight *External Trigger Input Signals* that can be used for cross-triggering from other CoreSight components including another ELA-500.

The ELA-500 is programmed from an APB bus and has architectural registers that enable identification in the CoreSight topology.

The ELA-500 also provides support for:

- A CoreSight authentication interface.

- An optional SRAM trace unit with configurable trace depth.

- Insertion of timestamps into the trace data.

There are seven output actions that can be used for various functions, such as stopping the clock to enable the system state to be extracted using a scan chain, cross triggering to a CoreSight debug subsystem, and other system-specific actions.

The following figure shows the functional blocks of the ELA-500:

Figure 2-1 ELA-500 block diagram

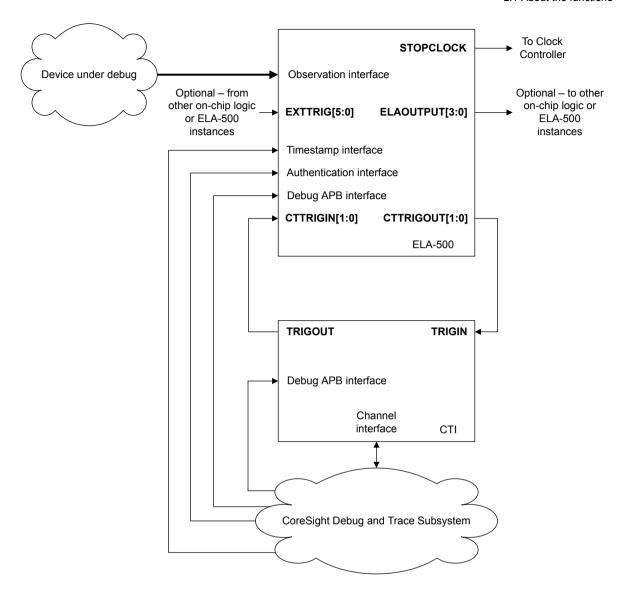

The following figure shows how to use an ELA-500 in a system:

Figure 2-2 How to use the ELA-500 in a system

# 2.2 Interfaces

The ELA-500 has numerous external interfaces. Some of these include interfaces to debug signals, trigger inputs, and authentication permissions.

The ELA-500 has the following interfaces:

# Debug APB slave interface

This interface provides access to the ELA-500 configuration register and status registers. See the *Arm® AMBA® APB Protocol Specification* and the *Arm® CoreSight™ Architecture Specification* for more information about the debug APB signals.

# **Observation Interface**

This consists of 12 *Signal Group* buses of 64, 128, or 256 bits, depending on the configuration parameter GRP WIDTH.

# **External Trigger inputs**

There are eight trigger inputs that can be used as trigger conditions. These inputs can be sourced from signals from a CoreSight CTI, or other on-chip signals, such as interrupts and debug requests, or can be an output signal from another ELA-500.

# Timestamp interface

This interface accepts a 64-bit natural binary value from a timestamp generator in the system. The timestamp is captured alongside trace data in the SRAM.

#### **Authentication interface**

The **DBGEN**, **NIDEN**, **SPIDEN**, and **SPNIDEN** signals are supported as described in the  $Arm^{\otimes}$   $CoreSight^{\bowtie}$  Architecture Specification.

# **SRAM** trace interface

If present, the SRAM trace interface connects to the SRAM that is used to store the captured trace data.

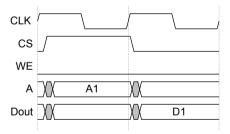

The following figure shows the SRAM read access timing:

Figure 2-3 SRAM read access timing

The following figure shows the SRAM write access timing:

Figure 2-4 SRAM write access timing

# **SRAM MBIST interface**

The *Memory Built-In Self-Test* (MBIST) interface provides a functional access path to the memories for self-test purposes.

# Low-Power interface Q-Channel

The ELA-500 provides a *Low-Power Interface* (LPI) that can be used by a clock controller to determine whether **ELACLK** can be stopped. The ELA-500 can be stopped when the following conditions are met:

- CTRL.RUN = 0.

- There are no pending debug APB register accesses, that is, **PSELDBG** is LOW.

- There is no SRAM access in progress.

- Integration test mode is disabled with ITCTLR.IME = 0.

The **ELAQACTIVE** signal is driven by an OR of the following signals:

- Unsynchronized PSELDBG.

- SRAM busy, that indicates a one cycle read or write is in progress.

- CTRL.RUN.

- ITCTRL.IME.

ITCTRL.IME = 1 is used to assert **ELAQACTIVE** so that **ELACLK** continues to run when integration mode is enabled, to avoid clock gating during integration test of the pulsed signals on **CTTRIGIN** and **EXTTRIGIN**.

An internal active signal is generated with synchronized **PSELDBG**. This internal active signal is used when **ELAQREQn** requests are asserted, to move to the Q\_STOPPED state when internal active is LOW, or to the Q\_DENIED state when internal active is HIGH.

# Related reference

A.6 DFT and MBIST interface signals on page Appx-A-90

A.7 Q-Channel Low-Power interface signals on page Appx-A-91

# 2.3 Clocking and reset

This section describes the clock and reset signals and procedures for the ELA-500.

This section contains the following subsections:

- 2.3.1 Clocking on page 2-27.

- 2.3.2 Reset on page 2-28.

# 2.3.1 Clocking

The ELA-500 has two main clock domains, the **PCLKDBG** domain that contains the debug APB interface, and the **ELACLK** domain that is the clock for sampling on the Observation interface, for *Signal Groups, Trigger State* comparisons, counters, and output actions.

Using multiple clock domains enables you to run the debug APB at much slower frequencies than sampled IP, such as cores, that can run at above 2GHz.

The following figure shows the division of the clock domains within the ELA-500.

Up to 12 Signal Groups, each containing 64, 128, or 256 signals

Figure 2-5 ELA-500 clock domains

# **Clock domain synchronization**

The ELA-500 performs synchronization of some input signals, and some signals between the **PCLKDBG** and **ELACLK** domains.

Software must take into account the following restrictions:

- The debug APB registers must only be written when the ELA-500 is stopped, that is, when CTRL.RUN is low.

- The debug APB registers must only be read when the ELA-500 is stopped. The exceptions to this rule are the Current State registers that can be read at any time to inspect the current state.

When implementing the ELA-500 in a system, you must be aware of the following points:

- All the debug signals in the Observation interface are sampled by ELACLK. These signals are not synchronized to ELACLK inside the ELA-500, and must be driven from logic clocked by ELACLK outside the ELA-500.

- The Authentication interface signals, **SPIDEN**, **DBGEN**, **NIDEN**, and **SPNIDEN**, must be synchronized to **PCLKDBG** outside the ELA-500.

- To aid debug, it is advantageous to have the logic analyzer operational during reset or during power management events of the sampled IP, such as powering down one of multiple cores. Take care with debug signals that originate from processors or other IP. The sampled IP could be power-gated or have asynchronous resets that could cause glitching or false sampling by the logic analyzer. De-assert SIGCLKEN<n> when debug inputs are changing because of:

- Assertion or de-assertion of isolation logic for debug signals that cross power domains.

- Assertion or de-assertion of asynchronous resets to the sampled IP.

- The **STOPCLOCK** output must not affect the initialization of the SoC following a powerup reset.

- The TSVALUE signals in the Timestamp interface must be synchronized to ELACLK.

# Related reference

3.6 Current State register descriptions on page 3-49

# 2.3.2 Reset

The ELA-500 has two functional resets, each corresponding to one of the two clock domains in the ELA-500.

The resets are:

- **RESETn** that resets the logic in the **ELACLK** domain.

- PRESETDBGn that resets the logic in the PCLKDBG domain.

Both resets can be asserted asynchronously to the respective clock, and must be synchronously deasserted. **RESETn** must only be asserted when powering up the **ELACLK** domain. **PRESETDBGn** must be asserted when powering up the **PCLKDBG** domain, or when a reset of system debug logic is required. Assertion of **PRESETDBGn** when the CTRL.RUN bit is set disables the ELA-500.

| required. Assertion of <b>FRESETDBGII</b> when the CTRL.RON bit is set disables the ELA-500.                     |

|------------------------------------------------------------------------------------------------------------------|

| Note                                                                                                             |

| Arm recommends that $PRESETDBGn$ is only asserted when the ELA-500 is already disabled with CTRL.RUN set to 0b0. |

| <del></del>                                                                                                      |

A third reset signal, **nMBISTRESET**, is an asynchronous test mode reset for both **ELACLK** and **PCLKDBG** domains. **nMBISTRESET** must be driven HIGH for functional operation and reset. See the *Arm*® *CoreSight*™ *ELA-500 Embedded Logic Analyzer Integration and Implementation Manual* for more information on test mode.

# 2.4 Trace control and capture

The SRAM trace unit on the ELA-500 is configurable using the parameters RAM\_ADDR\_SIZE and TRACE\_GEN.

The value of RAM\_ADDR\_SIZE represents the number of SRAM address bits. Software can read the DEVID register to determine trace depth. The trace SRAM acts as a circular buffer when trace is being captured, with the SRAM address incrementing automatically.

This section contains the following subsections:

- 2.4.1 Trace control on page 2-29.

- *2.4.2 Trace capture* on page 2-29.

- 2.4.3 Second trace comparator on Trigger State 4 on page 2-29.

- 2.4.4 Trace SRAM format on page 2-30.

- 2.4.5 Timestamp control on page 2-31.

- 2.4.6 Debug APB registers and interface to SRAM on page 2-31.

# 2.4.1 Trace control

Trace is controlled by the CTRL, TRIGCTRL, PTACTION, and ACTION<n> registers.

Trace can only be active when the ELA-500 is running, that is when CTRL.RUN =1. If PTACTION.TRACE is set, trace becomes active when CTRL.RUN is set.

When the ELA-500 is running, trace is controlled by ACTION<n>.TRACE. It is therefore possible to enable or disable trace at each *Trigger State* transition.

# 2.4.2 Trace capture

When trace is active, trace capture is controlled in each *Trigger State* by the *Trigger Control Register* (TRIGCTL<n>).

The following trace capture options are available:

- Capture on every **ELACLK**.

- Capture on a *Trigger Signal Comparison* match.

- Capture on a *Trigger Counter Comparison* match.

# Related reference

3.10.2 Trigger Control registers on page 3-59

# 2.4.3 Second trace comparator on *Trigger State* 4

*Trigger State* 4 includes additional capability that allows *Trigger State* 4 to trace SIGNALGRP<n> data while the other four *Trigger States* are programmed for comparisons and trace writes. *Trigger State* 4 is generated by setting the NUM\_TRIG\_STATES parameter to 5.

If multiple trace writes for *Trigger States* occur on the same clock cycle, trace from the highest numbered *Trigger State* takes priority. The trace write from the lower numbered *Trigger States* is dropped and the trace data overwrite bit, bit[5], in the trace header byte is set. In this implementation, where DEVID2 = 4, the trace data from *Trigger State* 4 will take precedence when there is a simultaneous write from another *Trigger State*. This feature allows a prioritized trace of two **SIGNALGRP**s at the same time.

The *Trigger State Select Register* (TSSR), controls the second trace comparator. Setting bit[4], that is ALTTS[4] = 1, enables the independent trace capability of *Trigger State* 4. When this bit is set, *Trigger State* 4 cannot be used in a loop with other *Trigger States* using NEXTSTATE<n> and ALTNEXTSTATE<n> with *Trigger State* 4 as a destination. Also, *Trigger State* 4 cannot update or drive an ACTION or ALTACTION.

*Trigger State* 4 has the following characteristics:

- Alternative comparisons do not function.

- *Trigger State* 4 runs in a continuous trace loop as if the NEXTSTATE is programmed to go back to *Trigger State* 4.

- Trigger State 4 trace stops when the other Trigger States reach a final state or CTRL.RUN is set to 0.

- The TSSR *Trigger State* TRIGCTRL4.WATCHRST = 1 sets Final State when the counter value in COUNTCOMP4 is matched. Setting Final State stops trace and the operation of all *Trigger States*. This feature is useful for stopping trace when a latency for a response is exceeded due to a stall or hang.

- The counters and trace filtering options are functional for *Trigger State* 4. TRIGCTRL4.COMPSRC, TRIGCTRL4.WATCHRST, TRIGCTRL4.COUNTSRC, TRIGCTRL4.TRACE, and TRIGCTRL4.COUNTCLR are available when ALTTS4 = 1. TRIGCTRL4.CAPTID, TRIGCTRL4.ALTCOMP, TRIGCTRL4.COUNTBRK, and TRIGCTRL4.ALTCOMPSRC are not available.

- Loops that are based on counter reset add an extra clock for the reset. For example, setting COUNTCOMP4 = 5 with TRIGCTRL4.COUNTSRC = 1, TRIGCTRL4.TRACESRC = 1 and TRIGCTRL4.COMP = 3'b001, results in trace capture when the counter reaches five trigger signal comparisons. The trace capture stays asserted until final\_state is reached. Setting TRIGCTRL4.COUNTCLR = 1 resets the counter after five trigger signal comparisons are counted. A trace is captured after every five trigger signal comparisons, with the *Trigger State* going to final\_state one ELACLK cycle later, or if CTRL.RUN is cleared. If TRIGCTRL4.TRACESRC = 0, a trace is captured every six ELACLK cycles when COUNTCOMP4 = 5.

# 2.4.4 Trace SRAM format

The trace SRAM can capture a full *Signal Group* on every **ELACLK** cycle. The width of the trace SRAM is GRP\_WIDTH + 8, with the additional eight bits being used to record a header byte that identifies the data as either a timestamp or a capture of the *Signal Group*.

Each trace SRAM word contains a data payload and a header byte. The header byte is located at the least significant byte of the SRAM word. The payload data is located in the upper bytes of the SRAM word.

For example, for a 64-bit Signal Group configuration:

```

GRP_WIDTH = 64

SRAM data[71:0] = {payload[63:0], header[7:0]}

```

For a 128-bit Signal Group configuration:

```

GRP_WIDTH = 128

SRAM data[135:0] = {payload[127:0], header[7:0]}

```

For a 256-bit Signal Group configuration:

```

GRP_WIDTH = 256

SRAM data[263:0] = {payload[255:0], header[7:0]}

```

The following table shows the header byte format.

Table 2-1 Header byte format

| Bits  | Name                 | Function                                                                                                                                                                                                                        |

|-------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6] | Trace counter[1:0]   | Two selected bits from a 16-bit cycle counter in the trace unit, used to identify a fine-grain time associated with the trace capture. The Timestamp Control Register controls the selection of the counter bits that are used. |

| [5]   | Trace data overwrite | Identifies that <i>Trigger State</i> 4 has overwritten data that was being written at the same time from a different <i>Trigger State</i> , that is <i>Trigger States</i> 0-3. Requires that TSSR.ALTTS4 = 1.                   |

# Table 2-1 Header byte format (continued)

| Bits  | Name          | Function                                                                                                                                                   |                                                                                                                                                                                                                                                                 |

|-------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [4:2] | Trigger state | Current <i>Trigger State</i> . Software can use the <i>Trigger State</i> to determine which <b>SIGNALGRP<n></n></b> was traced, by reading SIGSEL <n>.</n> |                                                                                                                                                                                                                                                                 |

| [1:0] | Туре          | Returns the type of data that follows the header byte:                                                                                                     |                                                                                                                                                                                                                                                                 |

|       |               | 0b00                                                                                                                                                       | Reserved.                                                                                                                                                                                                                                                       |

|       |               | 0b01                                                                                                                                                       | A 64-bit, 128-bit, or 256-bit data payload follows the header.                                                                                                                                                                                                  |

|       |               | 0b10                                                                                                                                                       | A timestamp value follows the header.                                                                                                                                                                                                                           |

|       |               |                                                                                                                                                            | Note                                                                                                                                                                                                                                                            |

|       |               |                                                                                                                                                            | Timestamps are optional and can be enabled using the Timestamp Control Register. A timestamp payload contains the full 64-bit timestamp value. If the ELA-500 is configured with GRP_WIDTH > 64, the payload is zero-extended above the 64-bit timestamp value. |

|       |               | 0b11                                                                                                                                                       | Reserved.                                                                                                                                                                                                                                                       |

# Related reference

3.4.2 Timestamp Control register on page 3-45

# 2.4.5 Timestamp control

Timestamps enable correlation of ELA-500 trace with trace from other CoreSight trace sources.

Timestamps in the ELA-500 have the following features:

- The Timestamp Control Register is used to enable writing of timestamps into the trace SRAM.

- Timestamps plus the associated header byte occupy 72, 136, or 264 bits of data. If the ELA-500 is configured with GRP WIDTH > 64, the timestamp value is zero-extended to 128 or 256 bits.

- Trace filtering that does not capture debug signal data on every **ELACLK** cycle enables timestamps to be written into the trace SRAM based on the interval set in the Timestamp Control Register. When the programmed timestamp interval is reached, a request is generated to insert a timestamp in the next available cycle that does not have a debug signal trace capture.

- Timestamps can be written into the trace SRAM after the trace active action is de-asserted when TIMECTRL.TSINT = 0. This guarantees that at least one timestamp is present in the circular SRAM buffer.

- When CTRL.RUN is cleared, a timestamp is written into trace SRAM if the previous trace write contained a data payload.

# 2.4.6 Debug APB registers and interface to SRAM

When configured with TRACE\_GEN = 1, the SRAM is accessible through the debug APB registers.

The SRAM is 72 bits, 136 bits, or 264 bits wide, depending on the *Signal Group* width configuration parameter GRP\_WIDTH.

Four registers enable the SRAM to be accessed through the 32-bit debug APB interface:

- RAM Read Address Register (RRAR).

- RAM Read Data Register (RRDR).

- RAM Write Address Register (RWAR).

- RAM Write Data Register (RWDR).

The RAM Read registers are provided to enable a debugger to read out captured trace data from the ELA-500. The RAM Write registers are provided to support integration testing.

The RRAR and RWAR address single 72-bit, 136-bit, or 264-bit words within the SRAM. Multiple RRDR or RWDR accesses are required for each SRAM word. An internal holding register is used to transfer data between the SRAM and RAM Data registers.

#### **SRAM** reads

When the RRAR is updated, either by a debug APB write or by an automatic increment, the SRAM data at that address is copied to the holding register.

Reads to the RRDR return the data from the holding register. The first read of the RRDR after an RRAR update returns the trace data header byte value, zero-extended to 32-bits. Subsequent reads of the RRDR return 32-bit chunks of the trace data payload, starting with the least significant chunk. This continues until all the payload data has been read, that is, two chunks if GRP\_WIDTH = 64, four chunks if GRP\_WIDTH = 128, and eight chunks if GRP\_WIDTH = 256.

When the final 32 bits of the payload have been read, the RRAR is incremented automatically. Then, the next word of SRAM data is copied into the holding register. This enables the SRAM data content to be read out efficiently.

The RRAR wraps to address zero if it is incremented beyond the maximum depth of the SRAM.

The trace read data scrambler protects the exposure of designs that are sensitive to signal trace. One or more signal groups might be scrambled. You must know the details of the specific scrambling system that was used to be able to unscramble the trace data.

For more information, see Arm® CoreSight™ ELA-500 Embedded Logic Analyzer Integration and Implementation Manual.

# **SRAM** writes

Writes to the SRAM are supported for integration-testing purposes.

A write to the RWAR sets the SRAM address for the data that is then written to the RWDR. Writes to the RWDR update the internal holding register.

The first write to the RWDR sets the header byte value with the least significant byte written. Subsequent writes to the RWDR set 32-bit chunks of the payload, starting with the least significant chunk. When the final 32 bits of the payload have been written, the content of the holding register is copied into the SRAM and the RWAR is incremented automatically.

The RWAR wraps to address zero if it is incremented beyond the maximum depth of the SRAM.

# 2.5 Triggering

Triggering is the process of causing an *Output Action* signal to be driven, or advancing to the next *Trigger State*, when a *Trigger Signal Comparison* or a *Trigger Counter Comparison* match occurs.

*Trigger Signal Comparisons* are based on the comparison of *Signal Groups* and *External Trigger Input Signals*. The masked *Signal Group* values and target values in the *Signal Compare* (SIGCOMP<n>) registers are compared, and logically ANDed, with the comparison of the masked *External Trigger Input Signals* and target values in the *External Compare* register (EXTCOMP<n>), where n = 0-4 and denotes one of the five *Trigger States*. The *Trigger Condition* is only met if both the *Signal Group* and *External Trigger Input Signal* comparisons succeed.

The GRP\_WIDTH 64-bit, 128-bit, and 256-bit SIGNALGRPs, and trace data, have the limitation that the comparator is 128 bits and operates on the lower 128 signals, for example SIGNALGRP<n>[127:0]. Registers, such as SIGCOMPn and SIGMASKn, are therefore only 128 bits. The upper 128 bits of SIGNALGRP<n> must be used to trace data that does not require a trigger signal comparison. For example, an address, or control signals, can be used for trigger signal comparisons on SIGNALGRP<n>[127:0], with the associated data being traced on SIGNALGRP<n>[255:128].

The mask registers can also support *Trigger Conditions* that only use a single set of signals. They are:

# Debug signals only

This is achieved by masking out the eight *External Trigger Input Signals* and writing the External Compare register with zeros. This causes an always true condition.

# **External Trigger Input Signals only**

This is achieved by masking out all the debug signals in the *Signal Group* and writing zeros into the Signal Compare register.

*Trigger Counter Comparisons* are made when the *Trigger State* counter counts from zero to the target value set in the *Counter Compare* register (COUNTCOMP<n>). A *Trigger Condition* can only be caused by either a *Trigger Signal Comparison* or a *Trigger Counter Comparison*.

Trigger States can be placed into loops by programming the NEXTSTATE<n> register to move to a previous Trigger State. Trigger State loops can be useful for trace filtering that is based on repeated Trigger Signal Comparison and Trigger Counter Comparison conditions. There is a Trigger State loop counter capability that can be enabled by programming TRIGCTRL.COUNTBRK = 1 and TRIGCTRL.COUNTCLR = 0. The loop counter can be used to break the loop and stop trace before the SRAM is full, or after a count of Trigger Signal Comparison events or a count of cycles. The Trigger State loop counter can also be used to control the number of ACTIONs by toggling ELA outputs ELAOUTPUT and CTTRIGOUT, which can be connected as interrupts or other CTI events.

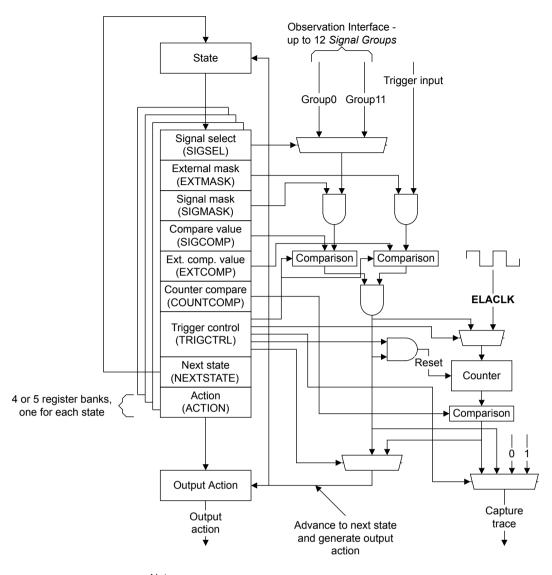

The following figure shows the triggering mechanism within the ELA-500.

Note:

Comparison represents a comparison function which can be one of:

=, >, >=, !=, <, <=.

Figure 2-6 Triggering mechanism within the ELA-500

This section contains the following subsections:

- 2.5.1 Conditional trigger states on page 2-34.

- 2.5.2 Transaction ID capture on page 2-36.

# 2.5.1 Conditional trigger states

Conditional *Trigger States* adds an optional second trigger signal comparison to each *Trigger State* when the parameter COND\_TRIG = 1.

DEVID[19:16] = 1 indicates to software that the ELA-500 supports conditional *Trigger States*.

The following pseudocode examples show *Trigger State* 0 comparisons using conditional *Trigger State* support, which adds the options that are highlighted in italic text:

Example 1: Both *Trigger State* conditions are programmed for trigger signal comparisons.

```

IF ((SIGNALGRP<n> < SIGCOMP0) && (TRIGCTRL0.COMPSEL == 0))

drive ACTION0 and goto NEXTSTATE0

ELSE IF ((SIGNALGRP<n> > SIGCOMP0) && (TRIGCTRL0.ALTCOMPSEL == 0))

```

```

drive ALTACTION0 and goto ALTNEXTSTATE0

ELSE do nothing

```

Example 2: The first condition is programmed for trigger signal comparison, and the alternative condition is programmed for counter cycle count comparison. The event count can be programmed for the first IF condition.

```

IF ((SIGNALGRP<n> < SIGCOMP0) && (TRIGCTRL0.COMPSEL == 0))

drive ACTION0 and goto NEXTSTATE0

ELSE IF ((counter == COUNTCOMP0) && (TRIGCTRL0.ALTCOMPSEL == 1) && (TRIGCTRL0.COUNTSRC == 0))

drive ALTACTION0 and goto ALTNEXTSTATE0

ELSE do nothing</pre>

```

Example 3: The first condition is programmed for signal comparison, and the alternative condition is programmed for counter comparison using loop counter COUNTBRK.

```

IF ((SIGNALGRP<n> < SIGCOMP0) && (TRIGCTRL0.COMPSEL == 0))

drive ACTION0 and goto NEXTSTATE0

ELSE IF ((event_or_cycle_count_increment) && (TRIGCTRL0.ALTCOMPSEL == 1) &&

(TRIGCTRL0.COUNTBRK == 1))

If(counter_match != 1)

goto ALTNEXTSTATE0

ELSE IF (counter_match == 1)

goto Final_state

ELSE // COUNTBRK will default to the first IF condition branch

goto NEXTSTATE0</pre>

```

Example 4: The first condition is programmed for counter comparison, and the alternative condition is programmed for signal comparison. In this case, the first condition, the counter match, dominates when there is a simultaneous signal comparison match.

Example 5: The first condition is programmed for counter comparison using loop counter COUNTBRK, and the alternative condition is programmed for signal comparison.

Example 6: Counting trigger signal comparisons as events does not need to use an alternative condition.

Filtered trace that is based on signal comparisons or counter comparisons is still independently controlled by TRIGCTRL<n>.TRACE.

If both the first IF and alternative ELSE IF trigger conditions match on the same clock cycle comparison, the first IF condition dominates and drives ACTION0 and goes to NEXTSTATE0.

- Note

TRIGCTRLn.COUNTBRK = 1 loops to the primary IF condition branch if the primary IF or alternative ELSE IF conditions do not match in the comparison clock cycle.

Two additional registers are used to provide support for the conditional *Trigger States*.

# Related reference

3.10.5 Alt Next State registers on page 3-62

3.10.6 Alt Action registers on page 3-63

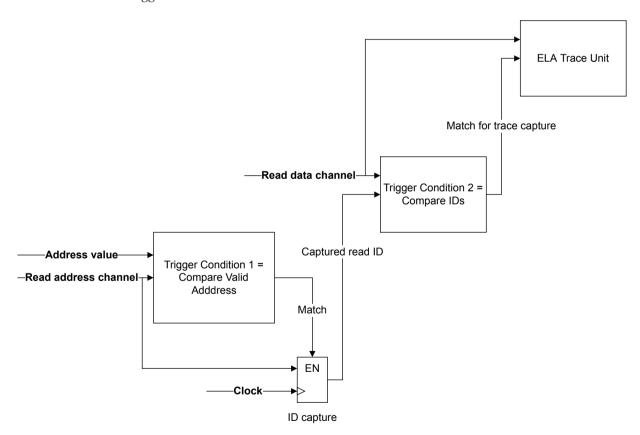

# 2.5.2 Transaction ID capture

Captures a transaction ID when there is a trigger signal match of an address request in a *Trigger State*.

The ID bits are based on debug signal wiring to the LSB bits of the SIGNALGRP and the parameter  $ID\_CATPURE\_SIZE$  which identifies the MSB of the ID, such that transaction\_ID[x:0] = SIGNALGRP < n > [x:0].

Stacked IDs can be wired to a SIGNALGRP such that {transaction\_ID1[y:x+1], transaction\_ID0[x:0]} = SIGNALGRP<n>[y:0].

**SIGMASK<n>** can be used to select the transaction ID in a subsequent trigger state.

The following figure illustrates a transaction ID capture from a read address channel on the first *Trigger State*, and use of the ID to compare with other debug signals connected to the **SIGNALGRP<n>** port in the second *Trigger State*.

Figure 2-7 Transaction ID capture from read address channel

The parameters ID\_CAPTURE\_GEN = 1 and COND\_TRIG = 1 must be set to enable generation of the ID capture feature. The ID CAPTURE SIZE parameter must be set to the number of bits in the ID tag.

If DEVID1 bits[24:20] = 0 then it indicates that the Transaction ID capture feature is disabled, otherwise DEVID1 bits[24:20] are set to ID\_CAPTURE\_SIZE. The parameter ID\_CAPTURE\_SIZE sets the size of the ID capture register which can be 2-30 bits.

## Related reference

3.18.4 Device Configuration register on page 3-76

#### 2.6 Authentication interface

be enabled.

The ELA-500 supports the authentication signals **DBGEN**, **NIDEN**, **SPIDEN**, and **SPNIDEN** through the Authentication interface.

When the ELA-500 is configured for Secure visibility, that is, the parameter SECURE MODE=1:

| enabled. When Secure non-invasive debug is disabled, the ELA-500 is stopped and does not move     |

|---------------------------------------------------------------------------------------------------|

| between Trigger States, assert any outputs, or capture any trace.                                 |

| Note                                                                                              |

| — The ELA-500 does not operate if authentication signals are set to Non-secure debug mode.        |

| — The CoreSight Authentication rules require that Non-secure debug is enabled for Secure debug to |

The ELA-500 Trigger State and trace operation are enabled when Secure non-invasive debug is

- The **STOPCLOCK** output is only asserted when Secure invasive debug is enabled.

- If Secure non-invasive debug becomes disabled dynamically, CTRL.RUN is internally gated, disabling the ELA-500. APB reads of CTRL.RUN do not indicate the state of the internally-gated run signal.

When the ELA-500 is not configured for Secure visibility, that is the parameter SECURE\_MODE=0:

- The ELA-500 *Trigger State* and trace operation are enabled when Non-secure non-invasive debug is enabled. When Non-secure non-invasive debug is disabled, the ELA-500 is stopped and does not move between *Trigger States*, assert any outputs, or capture any trace.

- The **STOPCLOCK** output is only asserted when Non-secure invasive debug is enabled.

- If Non-secure non-invasive debug becomes disabled dynamically, CTRL.RUN is automatically set to 0, disabling the ELA-500.

|   | o, disdoining the DEA-300.                                             |  |  |  |  |  |  |

|---|------------------------------------------------------------------------|--|--|--|--|--|--|

| _ | Note                                                                   |  |  |  |  |  |  |

| • | Arm does not recommend the use of SECURE_MODE=0.                       |  |  |  |  |  |  |

| • | SECURE_MODE = $1$ is the default, and the setting that Arm recommends. |  |  |  |  |  |  |

|   |                                                                        |  |  |  |  |  |  |

For more information on the Authentication interface, including the permitted values of the Authentication signals, and the CoreSight debug states, see the  $Arm^{*}$   $CoreSight^{**}$  Architecture Specification.

# 2.7 Parameter summary

The functionality of the ELA-500 is determined by configurable parameters.

The following table shows the parameters that control the configuration of the ELA-500:

Table 2-2 ELA-500 configuration parameters

| Parameter       | Values         | Default | Description                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------|----------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GRP_WIDTH       | 64,128, or 256 | 128     | 64, 128, or 256 debug signals are allowed in a Signal Group.                                                                                                                                                                                                                                                                                                                             |

|                 |                |         | When GRP_WIDTH = 64, the APB registers for the extended 128-bit SIGMASK and SICCOMP values are not available. When GRP_WIDTH = 256, signal comparisons are only made on the lower 128 bits of the SIGNALGRP.                                                                                                                                                                             |

| RAM_ADDR_SIZE   | 2-25 inclusive | 9       | Number of address bits in the SRAM.  Number of entries in the SRAM = 2RAM_ADDR_SIZE  For example, when RAM_ADDR_SIZE is 9, the SRAM has 512 entries. Arm recommends at least 512 entries, where an entry is data payload plus the header byte.  When GRP_WIDTH = 64, each entry is 9 bytes. When GRP_WIDTH = 128, each entry is 17 bytes,. When GRP_WIDTH = 256, each entry is 33 bytes. |

| TRACE_GEN       | 0 or 1         | 1       | 0: Trace unit not generated.                                                                                                                                                                                                                                                                                                                                                             |

| _               |                |         | The APB trace registers are not available and the SRAM interface signals are tied to zero.                                                                                                                                                                                                                                                                                               |

|                 |                |         | 1: Trace unit generated.                                                                                                                                                                                                                                                                                                                                                                 |

| SECURE_MODE     | 0 or 1         | 1       | 0: Non-secure mode operation.  ———————————————————————————————————                                                                                                                                                                                                                                                                                                                       |

|                 |                |         | 1: Secure mode operation.                                                                                                                                                                                                                                                                                                                                                                |

| COND_TRIG       | 0 or 1         | 0       | 0: Conditional <i>Trigger State</i> feature is disabled.                                                                                                                                                                                                                                                                                                                                 |

|                 |                |         | 1: Conditional <i>Trigger State</i> feature is enabled.                                                                                                                                                                                                                                                                                                                                  |

| ID_CAPTURE_SIZE | 2-30           | 10      | Sets the number of bits used for the captured transaction ID.                                                                                                                                                                                                                                                                                                                            |

| ID_CAPTURE_GEN  | 0 or 1         | 0       | 0: Captured transaction ID is not generated.                                                                                                                                                                                                                                                                                                                                             |

|                 |                |         | 1: Captured transaction ID is generated.  ——Note——  When ID_CAPTURE_GEN = 1, you must also set COND_TRIG = 1.                                                                                                                                                                                                                                                                            |

| NUM_TRIG_STATES | 4 or 5         | 4       | Sets the number of <i>Trigger States</i> .                                                                                                                                                                                                                                                                                                                                               |

| TRIGIN_EDGE     | 0 or 1         | 0       | Used to determine the method by which <b>CTTRIGIN</b> and <b>EXTRIG</b> are detected.  When TRIGIN_EDGE = 0, <b>CTTRIGIN</b> and <b>EXTRIG</b> are sampled when the <i>Trigger State</i> signal comparison occurs. When TRIGIN_EDGE = 1, assertion of <b>CTITRIGIN</b> and <b>EXTTRIG</b> are detected if CTRL.RUN = 1, and their assertions are latched until CTRL.RUN = 0.             |

# Chapter 3 **Programmers model**

| This chapter describes the programmers model.                                       |

|-------------------------------------------------------------------------------------|

| Note                                                                                |

| Any register bit position that is not listed in the description tables is reserved. |

#### It contains the following sections:

- 3.1 Access permissions on page 3-42.

- 3.2 Programming sequence on page 3-43.

- 3.3 Control register summary on page 3-44.

- 3.4 Control register descriptions on page 3-45.

- 3.5 Current State register summary on page 3-48.

- *3.6 Current State register descriptions* on page 3-49.

- 3.7 RAM register summary on page 3-51.

- 3.8 RAM register descriptions on page 3-52.

- 3.9 Trigger State register summary on page 3-55.

- 3.10 Trigger State register descriptions on page 3-58.

- *3.11 Integration Mode register summary* on page 3-67.

- 3.12 Integration Mode register descriptions on page 3-68.

- 3.13 Software Lock register summary on page 3-70.

- 3.14 Software Lock register descriptions on page 3-71.

- 3.15 Authentication register summary on page 3-72.

- 3.16 Authentication register descriptions on page 3-73.

- 3.17 Device register summary on page 3-74.

- 3.18 Device register descriptions on page 3-75.

- 3.19 ID register summary on page 3-78.

• 3.20 ID register descriptions on page 3-79.

# 3.1 Access permissions

Individual registers and register groups have different availability, depending on whether the ELA-500 is running or not.

The following table lists the software access permissions by register group or individual register where appropriate.

Table 3-1 Register access permissions

| Register or register group                   | Access when CTRL.RUN=1ª                       | Access when CTRL.RUN=0a      |  |

|----------------------------------------------|-----------------------------------------------|------------------------------|--|

| Logic Analyzer Control register on page 3-45 | Can be accessed by software.                  | Can be accessed by software. |  |

| Current state registers on page 3-48         |                                               |                              |  |

| Software lock registers on page 3-70         |                                               |                              |  |

| Authentication registers on page 3-72        |                                               |                              |  |

| Device registers on page 3-74                |                                               |                              |  |

| ID registers on page 3-78                    |                                               |                              |  |

| RAM registers on page 3-51                   | Must not be accessed by software.             |                              |  |

| Integration mode registers on page 3-67      |                                               |                              |  |

| Trigger state registers on page 3-55         | Can be read by software. Must not be written. |                              |  |

| Timestamp Control register on page 3-45      |                                               |                              |  |

| Pre-trigger Action register on page 3-46     |                                               |                              |  |

a Access means reads or writes, according to the Type field in the relevant register summary table.

# 3.2 Programming sequence

| 1 | Note |  |

|---|------|--|

|   | vore |  |

- In the following sequence of steps, a lowercase  $\langle n \rangle$ , where n = 0 to 4, denotes one of the five *Trigger States*.

- The order of steps 2 to 8 is not important.

#### **Procedure**

- 1. Set CTRL.RUN = 0 to stop the logic analyzer and allow the *Trigger State* and conditions to be programmed.

- 2. Select the bus to be used for comparisons for each *Trigger State* by writing to the appropriate SIGSEL<n> register.

- 3. Program the mask and compare registers for each *Trigger State* by writing to SIGMASK<n> and SIGCOMP<n>, respectively.