# Arm® Compiler Version 6.13

**Migration and Compatibility Guide**

#### **Arm® Compiler**

#### **Migration and Compatibility Guide**

Copyright © 2014–2019 Arm Limited or its affiliates. All rights reserved.

#### **Release Information**

#### **Document History**

| Issue   | Date             | Confidentiality  | Change                                                                     |

|---------|------------------|------------------|----------------------------------------------------------------------------|

| A       | 14 March 2014    | Non-Confidential | Arm Compiler v6.00<br>Release                                              |

| В       | 15 December 2014 | Non-Confidential | Arm Compiler v6.01<br>Release                                              |

| С       | 30 June 2015     | Non-Confidential | Arm Compiler v6.02<br>Release                                              |

| D       | 18 November 2015 | Non-Confidential | Arm Compiler v6.3<br>Release                                               |

| Е       | 24 February 2016 | Non-Confidential | Arm Compiler v6.4<br>Release                                               |

| F       | 29 June 2016     | Non-Confidential | Arm Compiler v6.5<br>Release                                               |

| G       | 04 November 2016 | Non-Confidential | Arm Compiler v6.6<br>Release                                               |

| 0607-00 | 05 April 2017    | Non-Confidential | Arm Compiler v6.7<br>Release. Document<br>numbering scheme has<br>changed. |

| 0608-00 | 30 July 2017     | Non-Confidential | Arm Compiler v6.8<br>Release.                                              |

| 0609-00 | 25 October 2017  | Non-Confidential | Arm Compiler v6.9<br>Release.                                              |

| 0610-00 | 14 March 2018    | Non-Confidential | Arm Compiler v6.10<br>Release.                                             |

| 0611-00 | 25 October 2018  | Non-Confidential | Arm Compiler v6.11<br>Release.                                             |

| 0612-00 | 27 February 2019 | Non-Confidential | Arm Compiler v6.12<br>Release.                                             |

| 0613-00 | 09 October 2019  | Non-Confidential | Arm Compiler v6.13<br>Release.                                             |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has

undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or TM are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at http://www.arm.com/company/policies/trademarks.

Copyright © 2014–2019 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

#### **Product Status**

The information in this document is Final, that is for a developed product.

#### Web Address

www.arm.com

### Contents

## **Arm® Compiler Migration and Compatibility Guide**

|           | Pref | ace                                                                       |         |

|-----------|------|---------------------------------------------------------------------------|---------|

|           |      | About this book                                                           | 10      |

| Chapter 1 | Con  | figuration and Support Information                                        |         |

|           | 1.1  | Support level definitions                                                 | 1-13    |

|           | 1.2  | Compiler configuration information                                        | 1-17    |

| Chapter 2 | Migr | rating from Arm <sup>®</sup> Compiler 5 to Arm <sup>®</sup> Compiler 6    |         |

|           | 2.1  | Migration overview                                                        | 2-19    |

|           | 2.2  | Toolchain differences                                                     | 2-20    |

|           | 2.3  | Default differences                                                       | 2-21    |

|           | 2.4  | Optimization differences                                                  | 2-23    |

|           | 2.5  | Backwards compatibility issues                                            | 2-25    |

|           | 2.6  | Diagnostic messages                                                       | 2-26    |

|           | 2.7  | Migration example                                                         | 2-28    |

| Chapter 3 | Migr | rating from armcc to armclang                                             |         |

|           | 3.1  | Migration of compiler command-line options from Arm® Compiler 5 to Arm® C | ompiler |

|           |      | 6                                                                         | 3-31    |

|           | 3.2  | Arm® Compiler 5 and Arm® Compiler 6 stack protection behavior             | 3-39    |

|           | 3.3  | Command-line options for preprocessing assembly source code               | 3-41    |

|           | 3.4  | Inline assembly with Arm® Compiler 6                                      | 3-42    |

|           | 3.5  | Migrating architecture and processor names for command-line options       | 3-44    |

|           | 3.6  | Preprocessing a scatter file when linking with armlink                    | 3-50    |

| Chapter 4  | Con  | piler Source Code Compatibility                                         |            |

|------------|------|-------------------------------------------------------------------------|------------|

|            | 4.1  | Language extension compatibility: keywords                              | 4-52       |

|            | 4.2  | Language extension compatibility: attributes                            | 4-55       |

|            | 4.3  | Language extension compatibility: pragmas                               | 4-58       |

|            | 4.4  | Language extension compatibility: intrinsics                            | 4-61       |

|            | 4.5  | Diagnostics for pragma compatibility                                    |            |

|            | 4.6  | C and C++ implementation compatibility                                  |            |

|            | 4.7  | Compatibility of C++ objects                                            |            |

| Chapter 5  | Migi | rating from armasm to the armclang Integrated Assembler                 |            |

|            | 5.1  | Migration of assembler command-line options from armasm to the armclang | integrated |

|            |      | assembler                                                               | 5-73       |

|            | 5.2  | Overview of differences between armasm and GNU syntax assembly code.    | 5-78       |

|            | 5.3  | Comments                                                                | 5-80       |

|            | 5.4  | Labels                                                                  | 5-81       |

|            | 5.5  | Numeric local labels                                                    |            |

|            | 5.6  | Functions                                                               |            |

|            | 5.7  | Sections                                                                | 5-85       |

|            | 5.8  | Symbol naming rules                                                     | 5-87       |

|            | 5.9  | Numeric literals                                                        |            |

|            | 5.10 | Operators                                                               |            |

|            | 5.11 | Alignment                                                               |            |

|            | 5.12 | PC-relative addressing                                                  |            |

|            | 5.13 | A32 and T32 instruction substitutions                                   |            |

|            | 5.14 | A32 and T32 pseudo-instructions                                         |            |

|            | 5.15 | Conditional directives                                                  |            |

|            | 5.16 | Data definition directives                                              |            |

|            | 5.17 | Instruction set directives                                              |            |

|            | 5.18 | Miscellaneous directives                                                |            |

|            | 5.19 | Symbol definition directives                                            |            |

|            | 5.20 | Migration of armasm macros to integrated assembler macros               |            |

| Chapter 6  | Cha  | nges Between Different Versions of Arm® Compiler 6                      |            |

|            | 6.1  | Summary of changes between Arm® Compiler 6.12 and Arm® Compiler 6.13    | 6-113      |

|            | 6.2  | Summary of changes between Arm® Compiler 6.11 and Arm® Compiler 6.12    | 6-114      |

|            | 6.3  | Summary of changes between Arm® Compiler 6.10 and Arm® Compiler 6.11    | 6-115      |

|            | 6.4  | Summary of changes between Arm® Compiler 6.9 and Arm® Compiler 6.10     | 6-117      |

|            | 6.5  | Summary of changes between Arm® Compiler 6.8 and Arm® Compiler 6.9      | 6-118      |

|            | 6.6  | Summary of changes between Arm® Compiler 6.7 and Arm® Compiler 6.8      | 6-119      |

|            | 6.7  | Summary of changes between Arm® Compiler 6.6 and Arm® Compiler 6.7      | 6-121      |

|            | 6.8  | Summary of changes between Arm® Compiler 6.5 and Arm® Compiler 6.6      | 6-122      |

|            | 6.9  | Compiling with -mexecute-only generates an empty .text section          | 6-125      |

| Appendix A | Cod  | e Examples                                                              |            |

|            | A.1  | Example startup code for Arm® Compiler 5 project                        | Appx-A-129 |

|            | A.2  | Example startup code for Arm® Compiler 6 project                        | Appx-A-131 |

| Appendix B | Lice | nses                                                                    |            |

|            | B.1  | Apache License A                                                        | Nppx-B-134 |

| List of Figures           |               |               |         |

|---------------------------|---------------|---------------|---------|

| Arm <sup>®</sup> Compiler | Migration and | Compatibility | , Guide |

| Figure 1 | 1-1 | Integration i | boundaries in A | 4rm | Compiler | 6 1 | -1 | 5 |

|----------|-----|---------------|-----------------|-----|----------|-----|----|---|

|----------|-----|---------------|-----------------|-----|----------|-----|----|---|

### **List of Tables**

# **Arm® Compiler Migration and Compatibility Guide**

| Table 1-1 | FlexNet versions                                                                      | 1-17 |

|-----------|---------------------------------------------------------------------------------------|------|

| Table 2-1 | List of compilation tools                                                             | 2-20 |

| Table 2-2 | Differences in defaults                                                               | 2-21 |

| Table 2-3 | Optimization settings                                                                 | 2-23 |

| Table 2-4 | Command-line changes                                                                  | 2-28 |

| Table 3-1 | Comparison of compiler command-line options in Arm Compiler 5 and Arm Compiler 6      | 3-31 |

| Table 3-2 | Architecture selection in Arm Compiler 5 and Arm Compiler 6                           | 3-44 |

| Table 3-3 | Processor selection in Arm Compiler 5 and Arm Compiler 6                              | 3-45 |

| Table 4-1 | Keyword language extensions in Arm Compiler 5 and Arm Compiler 6                      | 4-52 |

| Table 4-2 | Migrating thepacked keyword                                                           | 4-54 |

| Table 4-3 | Support fordeclspec attributes                                                        | 4-55 |

| Table 4-4 | Migratingattribute((at(address))) and zero-initializedattribute((section("name"))) 56 | 4    |

| Table 4-5 | Pragma language extensions that must be replaced                                      | 4-58 |

| Table 4-6 | Compiler intrinsic support in Arm Compiler 6                                          | 4-61 |

| Table 4-7 | Pragma diagnostics                                                                    | 4-65 |

| Table 4-8 | C and C++ implementation detail differences                                           | 4-67 |

| Table 5-1 | Comparison of command-line options in armasm and the armclang integrated assembler    | 5-73 |

| Table 5-2 | Operator translation                                                                  | 5-89 |

| Table 5-3 | A32 and T32 instruction substitutions supported by armasm                             | 5-92 |

| Table 5-4 | A32 and T32 pseudo-instruction migration                                              | 5-94 |

| Table 5-5 | Conditional directive translation                                                     | 5-95 |

| Table 5-6 | Data definition directives translation                                                | 5-96 |

| Table 5-7  | Instruction set directives translation                                        | 5-98      |

|------------|-------------------------------------------------------------------------------|-----------|

| Table 5-8  | Miscellaneous directives translation                                          | 5-99      |

| Table 5-9  | Symbol definition directives translation                                      | 5-101     |

| Table 5-10 | Comparison of macro directive features provided by armasm and the armclang in | ntegrated |

|            | assembler                                                                     | 5-103     |

| Table 5-11 | NOT EQUALS assertion                                                          | 5-105     |

| Table 5-12 | Unsigned integer division macro                                               | 5-106     |

| Table 5-13 | Assembly-time diagnostics macro                                               | 5-108     |

| Table 5-14 | Conditional loop macro                                                        | 5-109     |

## **Preface**

This preface introduces the Arm® Compiler Migration and Compatibility Guide.

It contains the following:

• About this book on page 10.

#### About this book

The Arm® Compiler Migration and Compatibility Guide provides migration and compatibility information for users moving from older versions of Arm Compiler to Arm Compiler 6.

#### Using this book

This book is organized into the following chapters:

#### **Chapter 1 Configuration and Support Information**

Summarizes the support levels and FlexNet versions supported by the Arm compilation tools.

#### Chapter 2 Migrating from Arm® Compiler 5 to Arm® Compiler 6

Provides an overview of the differences between Arm Compiler 5 and Arm Compiler 6.

#### Chapter 3 Migrating from armcc to armclang

Compares Arm Compiler 6 command-line options to older versions of Arm Compiler.

#### **Chapter 4 Compiler Source Code Compatibility**

Provides details of source code compatibility between Arm Compiler 6 and older armcc compiler versions.

#### Chapter 5 Migrating from armasm to the armclang Integrated Assembler

Describes how to migrate assembly code from armasm syntax to GNU syntax (used by armclang).

#### Chapter 6 Changes Between Different Versions of Arm® Compiler 6

Describes the changes that affect migration and compatibility between different versions of Arm Compiler 6.

#### Appendix A Code Examples

Provides source code examples for Arm Compiler 5 and Arm Compiler 6.

#### Appendix B Licenses

Describes the Apache license.

#### Glossary

The Arm® Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

See the Arm® Glossary for more information.

#### Typographic conventions

italic

Introduces special terminology, denotes cross-references, and citations.

#### bold

Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.

#### monospace

Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.

#### monospace

Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.

#### monospace italic

Denotes arguments to monospace text where the argument is to be replaced by a specific value.

#### monospace bold

Denotes language keywords when used outside example code.

<and>

Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:

SMALL CAPITALS

Used in body text for a few terms that have specific technical meanings, that are defined in the *Arm*® *Glossary*. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE.

#### **Feedback**

#### Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

#### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- The title Arm Compiler Migration and Compatibility Guide.

- The number 100068 0613 00 en.

- If applicable, the page number(s) to which your comments refer.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

| Note |

|------|

|------|

Arm tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader.

#### Other information

- Arm® Developer.

- Arm® Information Center.

- Arm® Technical Support Knowledge Articles.

- Technical Support.

- Arm® Glossary.

# Chapter 1 **Configuration and Support Information**

Summarizes the support levels and FlexNet versions supported by the Arm compilation tools.

It contains the following sections:

- 1.1 Support level definitions on page 1-13.

- 1.2 Compiler configuration information on page 1-17.

#### 1.1 Support level definitions

This describes the levels of support for various Arm Compiler 6 features.

Arm Compiler 6 is built on Clang and LLVM technology. Therefore, it has more functionality than the set of product features described in the documentation. The following definitions clarify the levels of support and guarantees on functionality that are expected from these features.

Arm welcomes feedback regarding the use of all Arm Compiler 6 features, and intends to support users to a level that is appropriate for that feature. You can contact support at <a href="https://developer.arm.com/support">https://developer.arm.com/support</a>.

#### Identification in the documentation

All features that are documented in the Arm Compiler 6 documentation are product features, except where explicitly stated. The limitations of non-product features are explicitly stated.

#### **Product features**

Product features are suitable for use in a production environment. The functionality is well-tested, and is expected to be stable across feature and update releases.

- Arm intends to give advance notice of significant functionality changes to product features.

- If you have a support and maintenance contract, Arm provides full support for use of all product features

- Arm welcomes feedback on product features.

- Any issues with product features that Arm encounters or is made aware of are considered for fixing in future versions of Arm Compiler.

In addition to fully supported product features, some product features are only alpha or beta quality.

#### Beta product features

Beta product features are implementation complete, but have not been sufficiently tested to be regarded as suitable for use in production environments.

Beta product features are indicated with [BETA].

- Arm endeavors to document known limitations on beta product features.

- Beta product features are expected to eventually become product features in a future release of Arm Compiler 6.

- Arm encourages the use of beta product features, and welcomes feedback on them.

- Any issues with beta product features that Arm encounters or is made aware of are considered for fixing in future versions of Arm Compiler.

#### Alpha product features

Alpha product features are not implementation complete, and are subject to change in future releases, therefore the stability level is lower than in beta product features.

Alpha product features are indicated with [ALPHA].

- Arm endeavors to document known limitations of alpha product features.

- Arm encourages the use of alpha product features, and welcomes feedback on them.

- Any issues with alpha product features that Arm encounters or is made aware of are considered for fixing in future versions of Arm Compiler.

#### **Community features**

Arm Compiler 6 is built on LLVM technology and preserves the functionality of that technology where possible. This means that there are additional features available in Arm Compiler that are not listed in the documentation. These additional features are known as community features. For information on these community features, see the *documentation for the Clang/LLVM project*.

Where community features are referenced in the documentation, they are indicated with [COMMUNITY].

- Arm makes no claims about the quality level or the degree of functionality of these features, except when explicitly stated in this documentation.

- Functionality might change significantly between feature releases.

- Arm makes no guarantees that community features will remain functional across update releases, although changes are expected to be unlikely.

Some community features might become product features in the future, but Arm provides no roadmap for this. Arm is interested in understanding your use of these features, and welcomes feedback on them. Arm supports customers using these features on a best-effort basis, unless the features are unsupported. Arm accepts defect reports on these features, but does not guarantee that these issues will be fixed in future releases.

#### Guidance on use of community features

There are several factors to consider when assessing the likelihood of a community feature being functional:

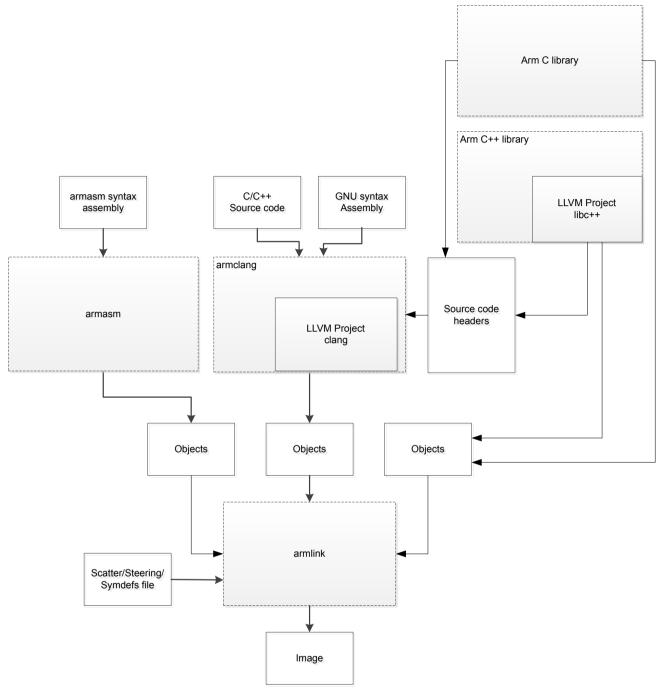

• The following figure shows the structure of the Arm Compiler 6 toolchain:

Figure 1-1 Integration boundaries in Arm Compiler 6.

The dashed boxes are toolchain components, and any interaction between these components is an integration boundary. Community features that span an integration boundary might have significant limitations in functionality. The exception to this is if the interaction is codified in one of the standards supported by Arm Compiler 6. See *Application Binary Interface (ABI) for the Arm® Architecture*. Community features that do not span integration boundaries are more likely to work as expected.

- Features primarily used when targeting hosted environments such as Linux or BSD might have significant limitations, or might not be applicable, when targeting bare-metal environments.

- The Clang implementations of compiler features, particularly those that have been present for a long time in other toolchains, are likely to be mature. The functionality of new features, such as support

for new language features, is likely to be less mature and therefore more likely to have limited functionality.

#### **Deprecated features**

A deprecated feature is one that Arm plans to remove from a future release of Arm Compiler. Arm does not make any guarantee regarding the testing or maintenance of deprecated features. Therefore, Arm does not recommend using a feature after it is deprecated.

For information on replacing deprecated features with supported features, refer to the Arm Compiler documentation and Release Notes.

#### **Unsupported features**

With both the product and community feature categories, specific features and use-cases are known not to function correctly, or are not intended for use with Arm Compiler 6.

Limitations of product features are stated in the documentation. Arm cannot provide an exhaustive list of unsupported features or use-cases for community features. The known limitations on community features are listed in *Community features* on page 1-13.

#### List of known unsupported features

The following is an incomplete list of unsupported features, and might change over time:

- The Clang option -stdlib=libstdc++ is not supported.

- C++ static initialization of local variables is not thread-safe when linked against the standard C++ libraries. For thread-safety, you must provide your own implementation of thread-safe functions as described in *Standard C++ library implementation definition*.

| Note                            |                                               |            |

|---------------------------------|-----------------------------------------------|------------|

| This restriction does not apply | to the [ALPHA]-supported multithreaded $C++1$ | libraries. |

- Use of C11 library features is unsupported.

- Any community feature that is exclusively related to non-Arm architectures is not supported.

- Compilation for targets that implement architectures older than Armv7 or Armv6-M is not supported.

- The **long double** data type is not supported for AArch64 state because of limitations in the current Arm C library.

- Complex numbers are not supported because of limitations in the current Arm C library.

#### 1.2 Compiler configuration information

Summarizes the FlexNet versions supported by the Arm compilation tools.

#### FlexNet versions in the compilation tools

Different versions of Arm Compiler support different versions of FlexNet.

The FlexNet versions in the compilation tools are:

Table 1-1 FlexNet versions

| Compilation tools version   | Windows   | Linux     |

|-----------------------------|-----------|-----------|

| Arm Compiler 6.7 and later  | 11.14.1.0 | 11.14.1.0 |

| Arm Compiler 6.01 and later | 11.12.1.0 | 11.12.1.0 |

| Arm Compiler 6.00           | 11.10.1.0 | 11.10.1.0 |

Related information

Arm DS-5 License Management Guide

### Chapter 2

## Migrating from Arm® Compiler 5 to Arm® Compiler 6

Provides an overview of the differences between Arm Compiler 5 and Arm Compiler 6.

#### It contains the following sections:

- 2.1 Migration overview on page 2-19.

- 2.2 Toolchain differences on page 2-20.

- 2.3 Default differences on page 2-21.

- 2.4 Optimization differences on page 2-23.

- 2.5 Backwards compatibility issues on page 2-25.

- 2.6 Diagnostic messages on page 2-26.

- 2.7 Migration example on page 2-28.

#### 2.1 Migration overview

Migrating from Arm Compiler 5 to Arm Compiler 6 requires the use of new command-line options and might also require changes to existing source files.

Arm Compiler 6 is based on the modern LLVM compiler framework. Arm Compiler 5 is not based on the LLVM compiler framework. Therefore migrating your project and source files from Arm Compiler 5 to Arm Compiler 6 requires you to be aware of:

- Differences in the command-line options when invoking the compiler.

- Differences in the adherence to language standards.

- Differences in compiler specific keywords, attributes, and pragmas.

- Differences in optimization and diagnostic behavior of the compiler.

Even though these differences exist between Arm Compiler 5 and Arm Compiler 6, it is possible to migrate your projects from Arm Compiler 5 to Arm Compiler 6 by modifying your command-line arguments and by changing your source code if required.

Arm Compiler 5 does not support processors based on Armv8 and later architectures. Migrating to Arm Compiler 6 enables you to generate highly efficient code for processors based on Armv8 and later architectures.

#### Related references

- 2.4 Optimization differences on page 2-23

- 2.6 Diagnostic messages on page 2-26

- 3.1 Migration of compiler command-line options from Arm® Compiler 5 to Arm® Compiler 6 on page 3-31

Chapter 4 Compiler Source Code Compatibility on page 4-51

#### Related information

Migrating projects from Arm Compiler 5 to Arm Compiler 6

#### 2.2 Toolchain differences

Arm Compiler 5 and Arm Compiler 6 share many of the same compilation tools. However, the main difference between the two toolchains is the compiler tool armclang, which is based on Clang and LLVM.

The table lists the individual compilation tools and the toolchain they apply to.

Table 2-1 List of compilation tools

| Arm Compiler 5 | Arm Compiler 6                                                   | Function                                                                                                                                                       |

|----------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| armcc          | armclang                                                         | Compiles C and C++ language source files, including inline assembly.                                                                                           |

| armcc          | armclang                                                         | Preprocessor.                                                                                                                                                  |

| armasm         | armasm                                                           | Assembles assembly language source files written in armasm syntax.                                                                                             |

| Not available  | armclang. This is also called the armclang integrated assembler. | Assembles assembly language source files written in GNU assembly syntax.                                                                                       |

| fromelf        | fromelf                                                          | Converts Arm ELF images to binary formats and can also generate textual information about the input image, such as its disassembly and its code and data size. |

| armlink        | armlink                                                          | Combines the contents of one or more object files with selected parts of one or more object libraries to produce an executable program.                        |

| armar          | armar                                                            | Enables sets of ELF object files to be collected together and maintained in archives or libraries.                                                             |

Arm Compiler 6 uses the compiler tool armclang instead of armcc. The command-line options for armclang are different to the command-line options for armcc. These differences are described in 3.1 Migration of compiler command-line options from Arm® Compiler 5 to Arm® Compiler 6 on page 3-31.

Arm Compiler 6 provides armasm, which you can use to assemble your existing assembly language source files that are written in armasm syntax. Arm recommends that you write new assembly code using the GNU assembly syntax, which you can assemble using the armclang integrated assembler. You can also migrate existing assembly language source files from armasm syntax to GNU syntax, and then assemble them using the armclang integrated assembler. For more information see *Chapter 5 Migrating from armasm to the armclang Integrated Assembler* on page 5-72.

#### Related information

Migrating projects from Arm Compiler 5 to Arm Compiler 6

#### 2.3 Default differences

| ome compiler and assembler options are different between Arm Compiler 5 and Arm Compiler 6, or ave different default values. |

|------------------------------------------------------------------------------------------------------------------------------|

| Note                                                                                                                         |

| his topic includes descriptions of [COMMUNITY] features. See Support level definitions on page 1-13.                         |

|                                                                                                                              |

The following table lists these differences.

Table 2-2 Differences in defaults

| Arm Compiler 5                        | Arm Compiler 6      | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Further information                                                 |

|---------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| hide_all                              | -fvisibility=hidden | These defaults are similar but -fvisibility=hidden does not affect extern declarations or symbol references. In Arm Compiler 6, symbols in the final image are hidden if the reference or the definition is hidden. Therefore the visibility of the reference alone does not determine the visibility of the symbol, as it does in Arm Compiler 5.                                                                                                                                                                                                                                                                                                                                                        | hide_all for Arm® Compiler 5fvisibility for Arm® Compiler 6.        |

| apcs=/hardfp or<br>apcs=/softfp       | -mfloat-abi=softfp  | The default floating-point linkage in Arm Compiler 5 depends on the specified processor. If the processor has floating-point hardware, then Arm Compiler 5 uses hardware floating-point linkage. If the processor does not have floating-point hardware, then Arm Compiler 5 uses software floating-point linkage. In Arm Compiler 6, the default is always software floating-point linkage for AArch32 state.  The -mfloat-abi option also controls the type of floating-point instructions that the compiler usesmfloat-abi=softfp uses hardware floating-point instructions. Use -mfloat-abi=soft to use software floating-point linkage and software library functions for floating-point operations. | apcs for Arm® Compiler 5mfloat-abi for Arm® Compiler 6.             |

| image.axf                             | a.out               | Default name for the executable image if none of -o, -c, -E, or -S are specified on the command-line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -o for Arm® Compiler 5o for Arm® Compiler 6.                        |

| enum_is_int is<br>disabled by default | -fno-short-enums    | enum_is_int is disabled by default in Arm Compiler 5, so the smallest data type that can hold the enumerator values is usedfno-short-enums is the default in Arm Compiler 6, so the size of the enumeration type is at least 32 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | enum_is_int for Arm® Compiler 5fno-short-enums for Arm® Compiler 6. |

#### Table 2-2 Differences in defaults (continued)

| Arm Compiler 5                        | Arm Compiler 6                     | Notes                                                                                                                                                                                                                                                  | Further information                                                                   |

|---------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| -02                                   | -00                                | Arm Compiler 5 uses high optimization (-02) by default. Arm Compiler 6 uses minimum optimization (-00) by default.                                                                                                                                     | -0 for Arm® Compiler 50 for Arm® Compiler 6. Optimization differences on page 2-23.   |

| apcs=/<br>nointerwork                 | apcs=/interwork                    | In Arm Compiler 5, armasm does not specify by default that code in the input file can safely interwork between A32 and T32. In Arm Compiler 6, armasm specifies interworking by default for AArch32 targets that support A32 and T32 instruction sets. | apcs for Arm® Compiler 5apcs for Arm® Compiler 6.                                     |

| C++03                                 | C++14                              | In Arm Compiler 5, the default C++ source language mode is C++03. In Arm Compiler 6, the default C++ source language mode is C++14. You can override the default source language with -std in Arm Compiler 6.                                          | cpp for Arm® Compiler 5std for Arm® Compiler 6.                                       |

| C90                                   | C11 [COMMUNITY]                    | In Arm Compiler 5, the default C source language mode is C90. In Arm Compiler 6, the default C source language mode is C11 [COMMUNITY]. You can override the default source language with -std in Arm Compiler 6.                                      | c90 for Arm* Compiler 5std for Arm* Compiler 6.                                       |

| no_exceptions                         | -fexceptions or<br>-fno-exceptions | In Arm Compiler 5, C++ exceptions are disabled by default (no_exceptions). In Arm Compiler 6, C++ exceptions are enabled by default (-fexceptions) for C++ sources, or disabled by default (-fno-exceptions) for C sources.                            | no_exceptions for Arm® Compiler 5fexceptions for Arm® Compiler 6.                     |

| wchar16                               | -fno-short-wchar                   | In Arm Compiler 5, the size of wchar_t is 2 bytes by default (wchar16). In Arm Compiler 6, the size of wchar_t is 4 bytes by default (-fno-short-wchar).                                                                                               | wchar16 for Arm® Compiler 5fno-short-wchar for Arm® Compiler 6.                       |

| split_sections is disabled by default | -ffunction-sections                | In Arm Compiler 5, functions are not put into separate ELF sections by default ( split_sections is disabled). In Arm Compiler 6, each function is put into a separate ELF section by default (-ffunction-sections).                                    | split_sections for<br>Arm® Compiler 5.<br>-ffunction-sections for<br>Arm® Compiler 6. |

#### 2.4 Optimization differences

Arm Compiler 6 provides more performance optimization settings than are present in Arm Compiler 5. However, the optimizations that are performed at each optimization level might differ between the two toolchains.

The table compares the optimization settings and functions in Arm Compiler 5 and Arm Compiler 6.

Table 2-3 Optimization settings

| Description                                                              | Arm Compiler 5                                                                                                                  | Arm Compiler 6                                        |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Optimization levels for performance.  Optimization levels for code size. | • -Otime -O0 • -Otime -O1 • -Otime -O2 • -Otime -O3  ———————————————————————————————————                                        | • -00 • -01 • -02 • -03 • -0fast • -0max  • -0s • -0z |

| Default                                                                  | The Arm Compiler 5 -00 option is more similar to the Arm Compiler 6 -01 option than the Arm Compiler 6 -00 option.  -Ospace -02 | -00                                                   |

| Best trade-off between image size,                                       | -Ospace -O2                                                                                                                     | -01                                                   |

| performance, and debug.                                                  |                                                                                                                                 |                                                       |

| Highest optimization for performance                                     | -Otime -03                                                                                                                      | -Omax                                                 |

| Highest optimization for code size                                       | -Ospace -O3                                                                                                                     | -0z                                                   |

Arm Compiler 6 provides an aggressive optimization setting, -Omax, which automatically enables a feature called Link Time Optimization. For more information, see *-flto*.

When using -Omax, armclang can perform link time optimizations that were not possible in Arm Compiler 5. These link time optimizations can expose latent bugs in the final image. Therefore, an image built with Arm Compiler 5 might have a different behavior to the image built with Arm Compiler 6.

For example, unused variables without the volatile keyword might be removed when using -Omax in Arm Compiler 6. If the unused variable is actually a volatile variable that requires the volatile keyword, then the removal of the variable can cause the generated image to behave unexpectedly. Since Arm Compiler 5 does not have this aggressive optimization setting, it might not have removed the

| unused variable, and the resulting | image might behave as expect | ted, and therefore the error i | in the code |

|------------------------------------|------------------------------|--------------------------------|-------------|

| would be more difficult to detect. |                              |                                |             |

| Note |

|------|

|------|

If the main() function has no arguments (no argc and argv), then Arm Compiler 5 applies a particular optimization at all optimization levels including -00. Arm Compiler 6 applies this optimization only for optimization levels other than -00.

When main() is compiled with Arm Compiler 6 at any optimization level except -00, the compiler defines the symbol \_\_ARM\_use\_no\_argv if main() does not have input arguments. This symbol enables the linker to select an optimized library that does not include code to handle input arguments to main().

When main() is compiled with Arm Compiler 6 at -00, the compiler does not define the symbol \_\_ARM\_use\_no\_argv. Therefore, the linker selects a default library that includes code to handle input arguments to main(). This library contains semihosting code.

If your main() function does not have arguments and you are compiling at -00 with Arm Compiler 6, you can select the optimized library by manually defining the symbol \_\_ARM\_use\_no\_argv using inline assembly:

```

__asm(".global __ARM_use_no_argv\n\t" "__ARM_use_no_argv:\n\t");

```

#### Also note that:

- Microlib does not support the symbol \_\_ARM\_use\_no\_argv. Only define this symbol when using the standard C library.

- Semihosting code can cause a HardFault on systems that are unable to handle semihosting code. To avoid this HardFault, you must define one or both of:

```

__use_no_semihostingARM use no argv

```

- If you define \_\_use\_no\_semihosting without \_\_ARM\_use\_no\_argv, then the library code to handle argc and argv requires you to retarget the following functions:

- \_ttywrch()

\_sys\_exit()

\_sys\_command\_string()

#### Related information

-flto armclang option

-O armclang option

Effect of the volatile keyword on compiler optimization

Optimizing across modules with link time optimization

#### 2.5 Backwards compatibility issues

Some Arm Compiler 5 options produce objects that are not compatible with Arm Compiler 6.

#### SHF\_COMDEF ELF sections

Linking with legacy objects that contain ELF sections with the legacy SHF\_COMDEF ELF section flag is deprecated. Use the GRP\_COMDAT ELF section group instead of the legacy SHF\_COMDEF ELF section flag by:

- Replacing the COMDEF section attribute of the legacy armasm syntax AREA directive with the COMGROUP=symbol name section attribute.

- Rebuilding incompatible legacy objects using one of the following:

- Arm Compiler 5 but with the --dwarf3 option. Other incompatibilities might still exist.

- Arm Compiler 6.

Related information

AREA

--dwarf3

#### 2.6 Diagnostic messages

In general, armclang provides more precise and detailed diagnostic messages compared to armcc. Therefore you can expect to see more information about your code when using Arm Compiler 6, which can help you understand and fix your source more quickly.

armclang and armcc differ in the quality of diagnostic information they provide about your code. The following sections demonstrate some of the differences.

#### Assignment in condition

The following code is an example of armclang providing more precise information about your code. The error in this example is that the assignment operator, =, must be changed to the equality operator, ==.

```

main.cpp:

#include <stdio.h>

int main()

{

int a = 0, b = 0;

if (a = b)

{

printf("Right\n");

}

else

{

printf("Wrong\n");

}

return 0;

}

```

Compiling this example with Arm Compiler 5 gives the message:

```

"main.cpp", line 6: Warning: #1293-D: assignment in condition

if (a = b)

```

Compiling this example with Arm Compiler 6 gives the message:

armclang highlights the error in the code, and also suggests two different ways to resolve the error. The warning messages highlight the specific part which requires attention from the user.

| <br>Note ——— |

|--------------|

|              |

When using armclang, it is possible to enable or disable specific warning messages. In the example above, you can enable this warning message using the -Wparentheses option, or disable it using the -Wno-parentheses option.

#### **Automatic macro expansion**

Another very useful feature of diagnostic messages in Arm Compiler 6, is the inclusion of notes about macro expansion. These notes provide useful context to help you understand diagnostic messages resulting from automatic macro expansion.

Consider the following code:

```

main.cpp:

#include <stdio.h>

#define LOG(PREFIX, MESSAGE) fprintf(stderr, "%s: %s", PREFIX, MESSAGE)

#define LOG_WARNING(MESSAGE) LOG("Warning", MESSAGE)

int main(void)

{

LOG_WARNING(123);

}

```

The macro LOG\_WARNING has been called with an integer argument. However, expanding the two macros, you can see that the fprintf function expects a string. When the macros are close together in the code it is easy to spot these errors. These errors are not easy to spot if they are defined in different part of the source code, or in other external libraries.

Compiling this example with Arm Compiler 5 armcc main.cpp gives the message:

```

main.cpp", line 8: Warning: #181-D: argument is incompatible with corresponding format

string conversion

LOG_WARNING(123);

^

```

Compiling this example with Arm Compiler 6 armclang --target=arm-arm-none-eabi -march=armv8-a gives the message:

For more information, see 4.5 Diagnostics for pragma compatibility on page 4-65.

| Note -  |  |

|---------|--|

| TAOLE - |  |

When starting the migration from Arm Compiler 5 to Arm Compiler 6, you can expect additional diagnostic messages because armclang does not recognize some of the pragmas, keywords, and attributes that were specific to armcc. When you replace the pragmas, keywords, and attributes from Arm Compiler 5 with their Arm Compiler 6 equivalents, the majority of these diagnostic messages disappear. You might require additional code changes if there is no direct equivalent for Arm Compiler 6. For more information see *Chapter 4 Compiler Source Code Compatibility* on page 4-51.

#### 2.7 Migration example

This topic shows you the process of migrating an example code from Arm Compiler 5 to Arm Compiler 6.

\_\_\_\_\_Note \_\_\_\_

This topic includes descriptions of [COMMUNITY] features. See Support level definitions on page 1-13.

#### Compiling with Arm® Compiler 5

For an example startup code that builds with Arm Compiler 5, see *Example startup code for Arm*<sup>®</sup> *Compiler 5 project* on page Appx-A-129.

To compile this example with Arm Compiler 5, enter:

```

armcc startup_ac5.c --cpu=7-A -c

```

This command generates a compiled object file for the Armv7-A architecture.

#### Compiling with Arm® Compiler 6

Try to compile the startup\_ac5.c example with Arm Compiler 6. The first step in the migration is to use the new compiler tool, armclang, and use the correct command-line options for armclang.

To compile this example with Arm Compiler 6, enter:

```

armclang --target=arm-arm-none-eabi startup_ac5.c -march=armv7-a -c -O1 -std=c90

```

The following table shows the differences in the command-line options between Arm Compiler 5 and Arm Compiler 6:

Table 2-4 Command-line changes

| Description                | Arm Compiler 5                                        | Arm Compiler 6                                                                                                          |

|----------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Tool                       | armcc                                                 | armclang                                                                                                                |

| Specifying an architecture | cpu=7-A                                               | -march=armv7-a    target is a mandatory option for armclang.                                                            |

| Optimization               | The default optimization is -02.                      | The default optimization is -00. To get similar optimizations as the Arm Compiler 5 default, use -01.                   |

| Source language mode       | The default source language mode for .c files is c90. | The default source language mode for .c files is gnu11 [COMMUNITY]. To compile for c90 in Arm Compiler 6, use -std=c90. |

Arm Compiler 6 generates the following errors and warnings when trying to compile the example startup ac5.c file in c90 mode:

The following section describes how to modify the source file to fix these errors and warnings.

#### Modifying the source code for Arm® Compiler 6

You must make the following changes to the source code to compile with armclang.

• The return type of function main function cannot be **void** in standard C. Replace the following line:

```

__declspec(noreturn) void main(void)

```

With:

```

__declspec(noreturn) int main(void)

```

• The intrinsic \_\_enable\_irq() is not supported in Arm Compiler 6. You must replace the intrinsic with an inline assembler equivalent. Replace the following line:

```

__enable_irq();

```

With:

```

__asm("CPSIE i");

```

• The #pragma import is not supported in Arm Compiler 6. You must replace the pragma with an equivalent directive using inline assembler. Replace the following line:

```

#pragma import(__use_no_semihosting)

```

With:

```

__asm(".global __use_no_semihosting");

```

• In certain situations, armclang might remove infinite loops that do not have side-effects. You must use the volatile keyword to tell armclang not to remove such code. Replace the following line:

```

while(1);

```

With:

```

while(1) __asm volatile("");

```

# Chapter 3 **Migrating from armcc to armclang**

Compares Arm Compiler 6 command-line options to older versions of Arm Compiler.

It contains the following sections:

- 3.1 Migration of compiler command-line options from Arm® Compiler 5 to Arm® Compiler 6 on page 3-31.

- 3.2 Arm® Compiler 5 and Arm® Compiler 6 stack protection behavior on page 3-39.

- 3.3 Command-line options for preprocessing assembly source code on page 3-41.

- 3.4 Inline assembly with Arm® Compiler 6 on page 3-42.

- 3.5 Migrating architecture and processor names for command-line options on page 3-44.

- 3.6 Preprocessing a scatter file when linking with armlink on page 3-50.

## 3.1 Migration of compiler command-line options from Arm® Compiler 5 to Arm® Compiler 6

The following table describes the most common Arm Compiler 5 command-line options, and shows the equivalent options for Arm Compiler 6.

More information about command-line options is available:

- The *Arm® Compiler Reference Guide* provides more information about the supported command-line options. The options described are fully supported, unless the level of support is indicated.

- For a full list of Clang command-line options, see the Clang and LLVM documentation.

Table 3-1 Comparison of compiler command-line options in Arm Compiler 5 and Arm Compiler 6

| Arm Compiler 5 option                                          | Arm Compiler 6 option                                         | Description                                                                                                                                                                                                                    |

|----------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| allow_fpreg_for_nonfpdata,<br><br>no_allow_fpreg_for_nonfpdata | <pre>-mimplicit-float, - mno-implicit-float [COMMUNITY]</pre> | Enables or disables the use of VFP and SIMD registers and data transfer instructions for non-VFP and non-SIMD data.                                                                                                            |

| apcs=/nointerwork                                              | No equivalent.                                                | Disables interworking between A32 and T32 code. Interworking is always enabled in Arm Compiler 6.                                                                                                                              |

| apcs=/ropi<br>apcs=/noropi                                     | -fropi<br>-fno-ropi                                           | Enables or disables the generation of Read-Only Position Independent (ROPI) code.                                                                                                                                              |

| apcs=/rwpi<br>apcs=/norwpi                                     | -frwpi<br>-fno-rwpi                                           | Enables or disables the generation of Read Write Position Independent (RWPI) code.                                                                                                                                             |

| arm                                                            | -marm                                                         | Targets the A32 instruction set. The compiler is permitted to generate both A32 and T32 code, but recognizes that A32 code is preferred.                                                                                       |

| arm_only                                                       | No equivalent.                                                | Enforces A32 instructions only. The compiler does not generate T32 instructions.                                                                                                                                               |

| asm                                                            | -save-temps                                                   | Instructs the compiler to generate intermediate assembly files as well as object files.                                                                                                                                        |

| bigend                                                         | -mbig-endian                                                  | Generates code for big-endian data.                                                                                                                                                                                            |

| -c                                                             | -c                                                            | Performs the compilation step, but not the link step.                                                                                                                                                                          |

| c90                                                            | -xc -std=c90                                                  | Enables the compilation of C90 source code.  -xc is a positional argument and only affects subsequent input files on the command-line. It is also only required if the input files do not have the appropriate file extension. |

Table 3-1 Comparison of compiler command-line options in Arm Compiler 5 and Arm Compiler 6 (continued)

| Arm Compiler 5 option | Arm Compiler 6 option | Description                                                                                                                                                                         |

|-----------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| c90gnu                | -xc -std=gnu90        | Enables the compilation of C90 source code with additional GNU extensions.                                                                                                          |

|                       |                       | -xc is a positional argument and only affects subsequent input files on the command-line. It is also only required if the input files do not have the appropriate file extension.   |

| c99                   | -xc -std=c99          | Enables the compilation of C99 source code.                                                                                                                                         |

|                       |                       | -xc is a positional argument and only affects subsequent input files on the command-line. It is also only required if the input files do not have the appropriate file extension.   |

| c99gnu                | -xc -std=gnu99        | Enables the compilation of C99 source code with additional GNU extensions.                                                                                                          |

|                       |                       | -xc is a positional argument and only affects subsequent input files on the command-line. It is also only required if the input files do not have the appropriate file extension.   |

| cpp                   | -xc++ -std=c++03      | Enables the compilation of C++03 source code.                                                                                                                                       |

|                       |                       | -xc++ is a positional argument and only affects subsequent input files on the command-line. It is also only required if the input files do not have the appropriate file extension. |

|                       |                       | The default C++ language standard is different between Arm Compiler 5 and Arm Compiler 6.                                                                                           |

| cppgnu                | -xc++ -std=gnu++03    | Enables the compilation of C++03 source code with additional GNU extensions.                                                                                                        |

|                       |                       | -xc++ is a positional argument and only affects subsequent input files on the command-line. It is also only required if the input files do not have the appropriate file extension. |

|                       |                       | The default C++ language standard is different between Arm Compiler 5 and Arm Compiler 6.                                                                                           |

| cpp11                 | -xc++ -std=c++11      | Enables the compilation of C++11 source code.                                                                                                                                       |

|                       |                       | -xc++ is a positional argument and only affects subsequent input files on the command-line. It is also only required if the input files do not have the appropriate file extension. |

|                       |                       | The default C++ language standard is different between Arm Compiler 5 and Arm Compiler 6.                                                                                           |

| cpp11gnu              | -xc++ -std=gnu++11    | Enables the compilation of C++11 source code with additional GNU extensions.                                                                                                        |

|                       |                       | -xc++ is a positional argument and only affects subsequent input files on the command-line. It is also only required if the input files do not have the appropriate file extension. |

|                       |                       | The default C++ language standard is different between Arm Compiler 5 and Arm Compiler 6.                                                                                           |

Table 3-1 Comparison of compiler command-line options in Arm Compiler 5 and Arm Compiler 6 (continued)

| Arm Compiler 5 option      | Arm Compiler 6 option                                                | Description                                                                                                                                    |

|----------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| cpp_compat                 | No equivalent.                                                       | Compiles C++ code to maximize binary compatibility.                                                                                            |

| cpu=8-A.32                 | target=arm-arm-<br>none-eabi -<br>march=armv8-a                      | Targets Armv8-A and AArch32 state.                                                                                                             |

| cpu 8-A.64                 | target=aarch64-<br>arm-none-eabi                                     | Targets Armv8-A and AArch64 state. (Implies -march=armv8-a if -mcpu is not specified.)                                                         |

| cpu=7-A                    | target=arm-arm-<br>none-eabi -<br>march=armv7-a                      | Targets the Armv7-A architecture.                                                                                                              |

| cpu=Cortex-M4              | target=arm-arm-<br>none-eabi -<br>mcpu=cortex-m4                     | Targets the Cortex*-M4 processor.                                                                                                              |

| cpu=Cortex-A15             | target=arm-arm-<br>none-eabi -<br>mcpu=cortex-a15                    | Targets the Cortex-A15 processor.                                                                                                              |

| -D                         | -D                                                                   | Defines a preprocessing macro.                                                                                                                 |

| depend                     | -MF                                                                  | Specifies a filename for the makefile dependency rules.                                                                                        |

| depend_dir                 | No equivalent. Use -MF to specify each dependency file individually. | Specifies the directory for dependency output files.                                                                                           |

| depend_format=unix_escaped |                                                                      | Dependency file entries use UNIX-style path separators and escapes spaces with \. This is the default in Arm Compiler 6.                       |

| depend_target              | -MT                                                                  | Changes the target name for the makefile dependency rule.                                                                                      |

| diag_error                 | -Werror                                                              | Turn compiler warnings into errors.                                                                                                            |

| diag_suppress=foo          | -Wno-foo                                                             | Suppress warning message <i>foo</i> . The error or warning codes might be different between Arm Compiler 5 and Arm Compiler 6.                 |

| -E                         | -E                                                                   | Executes only the preprocessor step.                                                                                                           |

| enum_is_int                | -fno-short-enums,-                                                   | Sets the minimum size of an enumeration type.                                                                                                  |

|                            | fshort-enums                                                         | By default Arm Compiler 5 does not set a minimum size. By default Arm Compiler 6 uses -fno-short-enums to set the minimum size to 32-bit.      |

| forceline                  | No equivalent.                                                       | Forces aggressive inlining of functions. Arm Compiler 6 automatically decides whether to inline functions depending on the optimization level. |

| fpmode=std                 | -ffp-mode=std                                                        | Provides IEEE-compliant code with no IEEE exceptions, NaNs, and Infinities. Denormals are sign preserving. This is the default.                |

| fpmode=fast                | -ffp-mode=fast                                                       | Similar to the default behavior, but also performs aggressive floating-point optimizations and therefore it is not IEEE-compliant.             |

Table 3-1 Comparison of compiler command-line options in Arm Compiler 5 and Arm Compiler 6 (continued)

| Arm Compiler 5 option                                                                 | Arm Compiler 6 option                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| fpmode=ieee_full                                                                      | -ffp-mode=full                              | Provides full IEEE support, including exceptions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |