Arm® Compiler

Version 6.11

**Errors and Warnings Reference Guide**

# **Arm® Compiler**

# **Errors and Warnings Reference Guide**

Copyright © 2014–2018 Arm Limited or its affiliates. All rights reserved.

#### **Release Information**

#### **Document History**

| Issue   | Date             | Confidentiality  | Change                                                            |

|---------|------------------|------------------|-------------------------------------------------------------------|

| A       | 14 March 2014    | Non-Confidential | Arm Compiler v6.00 Release                                        |

| В       | 15 December 2014 | Non-Confidential | Arm Compiler v6.01 Release                                        |

| С       | 30 June 2015     | Non-Confidential | Arm Compiler v6.02 Release                                        |

| D       | 18 November 2015 | Non-Confidential | Arm Compiler v6.3 Release                                         |

| Е       | 24 February 2016 | Non-Confidential | Arm Compiler v6.4 Release                                         |

| F       | 29 June 2016     | Non-Confidential | Arm Compiler v6.5 Release                                         |

| G       | 04 November 2016 | Non-Confidential | Arm Compiler v6.6 Release                                         |

| 0607-00 | 05 April 2017    | Non-Confidential | Arm Compiler v6.7 Release. Document numbering scheme has changed. |

| 0608-00 | 30 July 2017     | Non-Confidential | Arm Compiler v6.8 Release.                                        |

| 0609-00 | 25 October 2017  | Non-Confidential | Arm Compiler v6.9 Release.                                        |

| 0610-00 | 14 March 2018    | Non-Confidential | Arm Compiler v6.10 Release.                                       |

| 0611-00 | 25 October 2018  | Non-Confidential | Arm Compiler v6.11 Release.                                       |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of Arm. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to Arm's customers is not intended to create or refer to any partnership relationship with any other company. Arm may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any click through or signed written agreement covering this document with Arm, then the click through or signed written agreement prevails over and supersedes the

conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

The Arm corporate logo and words marked with ® or TM are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow Arm's trademark usage guidelines at http://www.arm.com/company/policies/trademarks.

Copyright © 2014–2018 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by Arm and the party that Arm delivered this document to.

Unrestricted Access is an Arm internal classification.

#### **Product Status**

The information in this document is Final, that is for a developed product.

#### **Web Address**

http://www.arm.com

# Contents

# **Arm® Compiler Errors and Warnings Reference Guide**

|           | Preface                                              |     |  |  |

|-----------|------------------------------------------------------|-----|--|--|

|           | About this book                                      | . 6 |  |  |

| Chapter 1 | Licensing Errors and Warnings                        |     |  |  |

|           | 1.1 List of the licensing error and warning messages | 1-9 |  |  |

| Chapter 2 | Assembler Errors and Warnings                        |     |  |  |

|           | 2.1 List of the armasm error and warning messages    | -13 |  |  |

| Chapter 3 | Linker Errors and Warnings                           |     |  |  |

|           | 3.1 Suppressing armlink error and warning messages   | -44 |  |  |

|           | 3.2 List of the armlink error and warning messages   | -45 |  |  |

| Chapter 4 | ELF Image Converter Errors and Warnings              |     |  |  |

|           | 4.1 List of the fromelf error and warning messages   | -89 |  |  |

| Chapter 5 | Librarian Errors and Warnings                        |     |  |  |

|           | 5.1 List of the armar error and warning messages     | -92 |  |  |

| Chapter 6 | Other Errors and Warnings                            |     |  |  |

|           | 6.1 Internal faults and other unexpected failures    | -94 |  |  |

|           | 6.2 List of other error and warning messages 6-      | -95 |  |  |

# **Preface**

This preface introduces the Arm® Compiler Errors and Warnings Reference Guide.

It contains the following:

• About this book on page 6.

#### About this book

The Arm® Compiler Errors and Warnings Reference Guide provides lists of the errors and warnings that each of the compilation tools can generate. It does not include errors and warnings produced by armclang.

# Using this book

This book is organized into the following chapters:

# Chapter 1 Licensing Errors and Warnings

Describes license-related error and warning messages that might be displayed by the assembler, the linker, or the ELF image converter.

# Chapter 2 Assembler Errors and Warnings

Describes the error and warning messages for the assembler, armasm.

# Chapter 3 Linker Errors and Warnings

Describes the error and warning messages for the linker, armlink.

# Chapter 4 ELF Image Converter Errors and Warnings

Describes the error and warning messages for the ELF image converter, fromelf.

# Chapter 5 Librarian Errors and Warnings

Describes the error and warning messages for the Arm librarian, armar.

# **Chapter 6 Other Errors and Warnings**

Describes error and warning messages that might be displayed by any of the tools.

# Glossary

The Arm® Glossary is a list of terms used in Arm documentation, together with definitions for those terms. The Arm Glossary does not contain terms that are industry standard unless the Arm meaning differs from the generally accepted meaning.

See the *Arm*<sup>®</sup> *Glossary* for more information.

# **Typographic conventions**

italic

Introduces special terminology, denotes cross-references, and citations.

#### bold

Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.

#### monospace

Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.

#### monospace

Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.

#### monospace italic

Denotes arguments to monospace text where the argument is to be replaced by a specific value.

# monospace bold

Denotes language keywords when used outside example code.

<and>

Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:

SMALL CAPITALS

Used in body text for a few terms that have specific technical meanings, that are defined in the *Arm*® *Glossary*. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE.

#### **Feedback**

# Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

#### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- The title *Arm Compiler Errors and Warnings Reference Guide*.

- The number 100074 0611 00 en.

- If applicable, the page number(s) to which your comments refer.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

| Note |

|------|

|------|

Arm tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader.

# Other information

- Arm® Developer.

- Arm® Information Center.

- Arm® Technical Support Knowledge Articles.

- Technical Support.

- Arm® Glossary.

| Chapter 1 |               |     |         |   |

|-----------|---------------|-----|---------|---|

| Licensing | <b>Errors</b> | and | Warning | S |

Describes license-related error and warning messages that might be displayed by the assembler, the linker, or the ELF image converter.

It contains the following section:

• 1.1 List of the licensing error and warning messages on page 1-9.

# 1.1 List of the licensing error and warning messages

A list of the error and warning messages that are caused by license-related issues.

The license error codes have three components; a prefix letter, an error number, and a suffix letter:

#### I NNNND

The prefix letter L indicates the tool that generated the error:

- For the assembler, armasm, the error code starts with A.

- For the linker, armlink, the error code starts with L.

- For the ELF image converter, fromelf, the error code starts with Q.

The error numbers, NNNN, are identical for each tool.

The suffix letter, D, indicates the severity of the error:

- · W means warning.

- E means error.

- F means fatal.

| <br>Note |  |

|----------|--|

| 11016    |  |

For the compiler, armclang, error messages are still generated, but with no error code.

[A9503E|L9503E|Q9503E]: Keys for <targetName> back-end could not be found in product definition.

[A9506E|L9506E|Q9506E]: Message received by <targetName> back-end is not valid.

[A9507E|L9507E|Q9507E]: <targetName> back-end returned status=<status> with invalid version number (<versionNumberReceived>).

[A9511E|L9511E|Q9511E]: Unable to determine the current toolkit. Ensure that ARM TOOL VARIANT is set correctly.

[A9515E|L9515E|Q9515E]: There is at least one feature CheckedOut for module <moduleName>. Unregister is not allowed until you CheckedIn all the features.

[A9517E|L9517E|Q9517E]: Parsing error: <errorMessage> (<fileName>:<lineNumber>).

[A9518W|L9518W|Q9518W]: Parsing warning: <warningMessage> (<fileName>:<lineNumber>).

[A9519E|L9519E|Q9519E]: Your installation appears to be corrupt.

This may be subsumed into a common code for these errors, where the problem is that there is something wrong with one or more of the mapping files.

[A9520E|L9520E|Q9520E]: Product definition string is empty. Set command will be ignored.

[A9521E|L9521E|Q9521E]: File I/O error when determining the current toolkit. Ensure that ARM\_TOOL\_VARIANT is set correctly, and you have read permissions for the complete toolchain installation.

$\mbox{[A9526W]L9526W]}\mbox{:}$  Failed to write to license cache file <fileName>. Error <errorNumber>: <errorString>.

[A9527W|L9527W|Q9527W]: Failed to calculate license cache file contents <fileName>.

[A9528W|L9528W|Q9528W]: Failed to close license cache file <fileName>. Error <errorNumber>: <errorString>.

[A9529W|L9529W|Q9529W]: Failed to move or copy license cache file from <source\_fileName> to <destination\_fileName>. Error <errorNumber>: <errorString>.

[A9530W|L9530W|Q9530W]: Failed to remove license cache file <fileName>. Error <errorNumber>: <errorString>.

[A9531W|L9531W|Q9531W]: Failed to read license cache file <fileName>. Error <errorNumber>: <errorString>.

[A9533W|L9533W|Q9533W]: License cache file invalid <fileName>.

[A9534E|L9534E|Q9534E]: Failed to create hash of cache file.

[A9535F|L9535F|Q9535F]: Dynamic library: error <error> while finding address of function <function> in library <dllPath>.

[A9536F|L9536F|Q9536F]: Dynamic library: error <error> while loading library <dllPath>.

[A9539F|L9539F|Q9539F]: Dynamic library: failed to create checking module in library <dllPath>.

[A9540F|L9540F|Q9540F]: Could not call DoCommand of external library, as the pointer to it is NULL.

[A9542F|L9542F|Q9542F]: Could not allocate memory for encryption key.

[A9544E|L9544E|Q9544E]: Cannot check in feature <featureName> with version <featureVersion> because it has not been checked out.

[A9545E|L9545E|Q9545E]: Info key <keyName> could not be found in product definition <mappingOrigin>.

[A9546E|L9546E|Q9546E]: Your license has expired (expiry date: <expiryDate>).

[A9547E|L9547E|Q9547E]: No license checking back-end registered with id <id> for feature <featureName>.

[A9549E|L9549E|Q9549E]: The feature <featureName> is not available with your current toolkit and license. Ensure that ARM TOOL VARIANT is set correctly for your toolkit.

[A9550E|L9550E|Q9550E]: The feature <featureName> is not available with your current toolkit and license. Ensure that ARM\_TOOL\_VARIANT is set correctly for your toolkit.

[A9552E|L9552E|Q9552E]: The feature <featureName> is not available with your current toolkit and license. Ensure that ARM\_TOOL\_VARIANT is set correctly for your toolkit.

[A9554E|L9554E|Q9554E]: Invalid data returned from <moduleId> back-end for feature <featureName>.

# [A9555E|L9555E|Q9555E]: Unable to checkout a license.

See the following table for more specific replacements per Flex error code:

| Flex error number | Message                                                                                                                        |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------|

| -1                | Unable to check out a license. The license file could not be found. Check that ARMLMD_LICENSE_FILE is set to the correct path. |

| -4                | Maximum number of license seats reached.                                                                                       |

| -5                | The provided license does not enable these tools.                                                                              |

| -9                | This host does not match the host ID in the license.                                                                           |

| -10               | The license has expired.                                                                                                       |

| -14               | Unable to resolve the license server's IP address. Check that ARMLMD_LICENSE_FILE is set correctly.                            |

| -15               | Unable to connect to the license server. Check that ARMLMD_LICENSE_FILE is set correctly and the license server is available.  |

| -30               | Cannot read license file.                                                                                                      |

| -34               | System date/time is not the same as the license server.                                                                        |

| -88               | The system clock has been set back.                                                                                            |

| -96               | Unable to connect to the license server. Check that ARMLMD_LICENSE_FILE is set correctly and the license server is available.  |

| -97               | Unable to connect to the license server. Check that ARMLMD_LICENSE_FILE is set correctly and the license server is available.  |

[A9558E|L9558E|Q9558E]: System clock tampering detected. License checkout will fail.

[A9559E|L9559E|Q9559E]: License information retrieval for feature <featureName> with version <version> was cancelled because no back-end is associated with it.

[A9561E|L9561E|Q9561E]: No generation date specified, but relative expiry dates present.

[A9580E|L9580E|Q9580E]: <target> is not available with your current toolkit and license. Ensure that ARM\_TOOL\_VARIANT is set correctly for your toolkit.

# **Chapter 2 Assembler Errors and Warnings**

Describes the error and warning messages for the assembler, armasm.

It contains the following section:

• 2.1 List of the armasm error and warning messages on page 2-13.

# 2.1 List of the armasm error and warning messages

A list of the error and warning messages that armasm produces.

\_\_\_\_\_Note \_\_\_\_\_

License-related error messages can be found in the 1.1 List of the licensing error and warning messages on page 1-9 section.

A1017E: :INDEX: cannot be used on a pc-relative expression

The :INDEX: expression operator has been applied to a PC-relative expression, most likely a program label. :INDEX: returns the offset from the base register in a register-relative expression.

If you require the offset of a label called <label> within an area called <areaname>, use <label> - <areaname>.

See the following in the armasm User Guide:

Unary operators.

A1020E: Bad predefine: <directive>

The operand to the --predefine or --pd command-line option was not recognized. The directive must be enclosed in quotes if it contains spaces, for example on Windows:

```

--predefine "versionnum SETA 5"

```

If the SETS directive is used, the argument to the directive must also be enclosed in quotes, which might require escaping, depending on the operating system and shell. For example:

```

--predefine "versionstr SETS \"5A\""

```

A1021U: No input file

No input file was specified on the command line. This might be because there was no terminating quote on a quoted argument.

```

A1023E: File "<filename>" could not be opened: <reason>

```

A1024E: File "<filename>" could not all be loaded: <reason>

A1042E: Unrecognized APCS qualifier '<qualifier>'

There is an error in the argument given to the --apcs command line option. Check the spelling of <qualifier>.

```

A1051E: Cannot open --depend file '<filename>': <reason>

```

A1055E: Cannot open --errors file '<filename>': <reason>

A1056E: Target cpu '<cpu>' not recognized

The name given in the --cpu command line option is not a recognized processor name. Check the spelling of the argument.

Use --cpu=list to list the supported processors and architectures.

A1067E: Output file specified as '<filename1>', but it has already been specified as '<filename2>'

More than one output file, -o filename, has been specified on the command line. Misspelling a command line option can cause this.

A1071E: Cannot open listing file '<filename>': <reason>

The file given in the --list <filename> command-line option could not be opened. This could be for any of the following reasons:

- The given name is not valid.

- There is no space.

- A read-only file with the same name already exists.

- The file is in use by another process.

Check you have specified the correct path for the file.

A1072E: The specified listing file '<filename>' must not be a .s or .o file

The filename argument to the --list command line option has an extension that indicates it is a source or object file. This might be because the filename argument was accidentally omitted from the command line. Check that the correct argument is given to the --list command line option.

A1073E: The specified output file '<filename>' must not be a source file

The object file specified on the command line has a filename extension that indicates it is a source file. This might be because the object filename was accidentally omitted from the command line.

A1074E: The specified depend file '<filename>' must not be a source file

The filename argument to the --depend command line option has an extension that indicates it is a source (.s) file. This might be because the filename argument was accidentally omitted from the command line. Check that the correct arguments are given.

A1075E: The specified errors file '<filename>' must not be a source file

The filename argument to the --errors command line option has an extension that indicates it is a source (.s) file. This might be because the filename argument was accidentally omitted from the command line. Check that the correct arguments are given.

A1085W: Forced user-mode LDM/STM must not be followed by use of banked R8-R14

The Arm architecture does not permit you to access banked registers in the instruction immediately following a User registers LDM or STM. Adding a NOP immediately after the LDM or STM is one way to avoid this.

For example:

```

stmib sp, \{r0-r14\}^{\wedge}; Return a pointer to the frame in a1. mov r0, sp

```

change to:

```

stmib sp, \{r0-r14\}^{\wedge}; Return a pointer to the frame in a1. nop mov r0, sp

```

A1088W: Faking declaration of area AREA |\$\$\$\$\$\$|

This is reported when no AREA directive is specified. See also message number A1105E.

A1099E: Structure stack overflow max stack size <max>

A1100E: Structure stack underflow A1105E: Area directive missing

This is reported when no AREA directive is specified. See also message number A1088W.

A1106E: Missing comma

A1107E: Bad symbol type, expect label A1108E: Multiply defined symbol '<name>'

A1109E: Bad expression type

#### A1110E: Expected constant expression

A constant expression was expected after, for example, SETA.

See the following in the armasm User Guide:

# Numeric expressions.

A1111E: Expected constant or address expression

A1112E: Expected address expression A1113E: Expected string expression

A string expression was expected after, for example, SETS.

See the following in the armasm User Guide:

#### String expressions.

A1114E: Expected register relative expression

A1116E: String operands can only be specified for DCB

A1117E: Register symbol '<name>' already defined

A1118E: No current macro expansion

A1119E: MEND not allowed within conditionals

MEND means END of Macro (not the English word mend).

See the following in the armasm User Guide:

#### About macros.

A1120E: Bad global name

A1121E: Global name '<name>' already exists

A1122E: Locals not allowed outside macros

A1123E: Bad local name

A1125E: Unknown or wrong type of global/local symbol '<name>'

A1126E: Bad alignment boundary, must be a multiple of 2

A1127E: Bad IMPORT/EXTERN name

A1128E: Common name '<sym>' already exists

A1129E: Imported name '<sym>' already exists

A1130E: Bad exported name

A1131E: Bad symbol type for exported symbol '<sym>'

A1132E: REQUIRE directive not supported for <entity> format output

A1133E: Bad required symbol name

A1134E: Bad required symbol type, expect (symbol is either external or label) and

(symbol is relocatable and absolute)

A1135E: Area name missing

AREA names starting with any non-alphabetic character must be enclosed in bars, for example change:

```

AREA 1_DataArea, CODE, READONLY

```

to:

#### AREA |1\_DataArea|, CODE, READONLY

A1136E: Entry address already set

#### A1137E: Unexpected characters at end of line

This is given when extra characters that are not part of an instruction are found on an instruction line

For example:

```

ADD r0, r0, r1 comment

```

You could change this to:

```

ADD r0, r0, r1; comment

```

A1138E: String "<string>" too short for operation, length must be > <oplength>

A1139E: String overflow, string exceeds <max> characters

A1140E: Bad operand type

A1141E: Relocated expressions may only be added or subtracted

A1142E: Subtractive relocations not supported for <entity> format output

This can occur when subtracting symbols that are in different areas, for example:

```

IMPORT sym1

IMPORT sym2

DCD (sym2 - sym1)

```

A1143E: COMMON directive not supported for %s format output

A1144E: DCDO directive not supported for %s format output

A1145E: Undefined exported symbol '<sym>'

A1146E: Unable to open output file <filename>: <reason>

A1147E: Bad shift name

A1148E: Unknown shift name <name>, expected one of LSL, LSR, ASR, ROR, RRX

A1150E: Bad symbol, not defined or external

This typically occurs in the following cases:

• When the current file requires an INCLUDE of another file to define some symbols, for example:

```

"init.s", line 2: Error: A1150E: Bad symbol 2 00000000 DCD EBI_CSR_0

```

In this case, the solution is to include the required definitions file. For example:

```

INCLUDE targets/eb40.inc

```

• When the current file requires IMPORT for some symbols, for example:

```

"init.s", line 4: Error: A1150E: Bad symbol

4 00000000 LDR r0, =||Image$$RAM$$ZI$$Limit||

```

In this case, the solution is to import the required symbol, for example:

```

IMPORT ||Image$$RAM$$ZI$$Limit||

```

# A1151E: Bad register name symbol

Example:

```

MCR p14, 3, R0, Cr1, Cr2

```

The coprocessor registers CR must be labeled as a lowercase c for the code to build. The register can be r or R:

```

MCR p14, 3, r0, c1, c2

```

or

```

MCR p14, 3, R0, c1, c2

```

A1152E: Unexpected operator

A1153E: Undefined symbol

A1154E: Unexpected operand, operator expected

A1155E: Unexpected unary operator equal to or equivalent to

A1156E: Missing open bracket

A1157E: Syntax error following directive A1158E: Illegal line start, should be blank

Some directives, for example, ENTRY, IMPORT, EXPORT, and GET must be on a line without a label at the start of the line. This error is given if a label is present.

A1159E: Label missing from line start

Some directives, for example, FUNCTION or SETS, require a label at the start of the line, for example:

```

my_func FUNCTION

```

or

label SETS

This error is given if the label is missing.

A1160E: Bad local label number

A numeric local label is a number in the range 0-99, optionally followed by a name.

See the following in the armasm User Guide:

Numeric local labels.

A1161E: Syntax error following local label definition

A1162E: Incorrect routine name '<name>'

A1163E: Unknown opcode <name> , expecting opcode or Macro

The most common reasons for this are:

• Forgetting to put white space in the left hand margin, before the instruction. For example, change the following:

```

MOV PC,LR

```

to:

MOV PC, LR

• Use of a hardware floating point instruction without using the --fpu switch. For example:

```

FMXR FPEXC, r1;

```

must be assembled with armasm --fpu=vfp

• Mis-typing the opcode:

```

ADDD

```

instead of:

ADD

A1164E: Opcode not supported on selected processor

The processor selected on the armasm command line does not support this instruction.

See the following:

Arm® Architecture Reference Manual.

A1165E: Too many actual parameters, expecting <actual> parameters

A1166E: Syntax error following label

A1167E: Invalid line start

A1168E: Translate not allowed in pre-indexed form

A1169E: Missing close square bracket

A1170E: Immediate 0x<adr> out of range for this operation, must be below (0x<adr>)

This error is given when a DCB, DCW or DCWU directive is used with an immediate that is too large.

See the following in the armasm User Guide:

- DCB.

- DCW and DCWU.

A1171E: Missing close bracket

A1172E: Bad rotator <rotator>, must be even and between 0 and 30

A1173E: ADR/L cannot be used on external symbols

The ADR and ADRL pseudo-instructions can only be used with labels within the same code area. To load an out-of-area address into a register, use LDR instead.

A1174E: Data transfer offset 0x<val> out of range. Permitted values are 0x<min> to

0x<max>

A1175E: Bad register range

A1176E: Branch offset 0x<val> out of range. Permitted values are 0x<min> to 0x<max>

Branches are PC-relative, and have a limited range. If you are using numeric local labels, you can use the ROUT directive to limit their scope. This helps to avoid referring to the wrong label by accident.

See the following in the armasm User Guide:

#### Numeric local labels.

A1179E: Bad hexadecimal number A1180E: Missing close quote

A1181E: Bad operator

A1182E: Bad based <base> number

A1183E: Numeric overflow

A1184E: Externals not valid in expressions

A1185E: Symbol missing

A1186E: Code generated in data area

An instruction has been assembled into a data area. This can happen if you have omitted the CODE attribute on the AREA directive.

See the following in the armasm User Guide:

# AREA.

A1187E: Error in macro parameters

A1188E: Register value <val> out of range. Permitted values are <min> to <max>

A1189E: Missing '#'

A1190E: Unexpected '<entity>'

A1191E: Floating point register number out of range 0 to <maxi>

A1192E: Coprocessor register number out of range 0 to 15

A1193E: Coprocessor number out of range 0 to 15

A1194E: Bad floating-point number

A1195W: Small floating point value converted to 0.0

A1196E: Too late to ban floating point

#### A1198E: Unknown operand

This can occur when an operand is accidentally mistyped.

For example:

```

armasm --cpu=8-A.64 init.s -g -PD "ROM_RAM_REMAP SETL {FALS}"

```

must be:

```

armasm --cpu=8-A.64 init.s -g -PD "ROM_RAM_REMAP SETL {FALSE}"

```

See the following in the armasm User Guide:

Assembly time substitution of variables.

A1199E: Coprocessor operation out of range 0 to <maxi>

A1200E: Structure mismatch expect While/Wend

A1201E: Substituted line too long, maximum length <max>

A1202E: No pre-declaration of substituted symbol '<name>'

See the following in the armasm User Guide:

Assembly time substitution of variables.

A1203E: Illegal label parameter start in macro prototype

A1204E: Bad macro parameter default value

A1205E: Register <reg> occurs multiply in list

A1206E: Registers should be listed in increasing register number order

This warning is given if registers in, for example, LDM or STM instructions are not specified in increasing order and the --checkreglist option is used.

A1207E: Bad or unknown attribute

This error is given when an invalid attribute is given in the AREA directive. For example:

```

AREA test, CODE, READONLY, HALFWORD

```

HALFWORD is invalid, so remove it.

See the following in the armasm User Guide:

AREA.

A1209E: ADRL cannot be used with PC as destination

A1210E: Non-zero data within uninitialized area '<name>'

A1211E: Missing open square bracket

A1212E: Division by zero

A1213E: Attribute <entity> cannot be used with attribute <entity>

A1214E: Too late to define symbol '<sym>' as register list

A1215E: Bad register list symbol A1216E: Bad string escape sequence

A1217E: Error writing to code file <codeFileName>: <reason>

A1219E: Bad APSR, CPSR or SPSR designator

For example:

```

MRS r0, PSR

```

It is necessary to specify which status register to use (CPSR or SPSR), such as, for example:

```

MRS r0, CPSR

```

A1220E: BLX <address> must be unconditional

A1221E: Area attribute '<entity>' not supported for <entity> object file format

A1223E: Comdat Symbol '<name>' is not defined

- A1224E: <entity> format does not allow PC-relative data transfers between areas

- A1225E: ASSOC attribute is not allowed in non-comdat areas

- A1226E: SELECTION attribute is not allowed in non-comdat areas

- A1227E: Comdat Associated area '<name>' undefined at this point in the file

- A1228E: Comdat Associated area '<name>' is not an area name

- A1229E: Missing COMDAT symbol

- A1230E: Missing '}' after COMDAT symbol

- A1234E: Undefined or Unexported Weak Alias for symbol '<sym>'

- A1237E: Invalid register or register combination for this operation

- A1238E: Immediate value must be word aligned when used in this operation

- A1240E: Immediate value cannot be used with this operation

- A1241E: Must have immediate value with this operation

- A1242E: Offset must be word aligned when used with this operation

- A1243E: Offset must be halfword aligned with this operation

- A1244E: Missing '!'

- A1245E: B or BL from Thumb code to ARM code

- A1246E: B or BL from ARM code to Thumb code

- A1247E: BLX from ARM code to ARM code, use BL

This occurs when there is a BLX *Label* branch from A32 code to A32 code within this assembler file. This is not permitted because BLX *Label* always results in a change of instruction set state. The usual solution is to use BL instead.

A1248E: BLX from Thumb code to Thumb code, use BL

This occurs when there is a BLX *Label* branch from T32 code to T32 code within this assembler file. This is not permitted because BLX *Label* always results in a change of instruction set state. The usual solution is to use BL instead.

- A1249E: Post indexed addressing mode not available

- A1250E: Pre indexed addressing mode not available for this instruction, use [Rn, Rm]

- A1253E: Thumb branch to external symbol cannot be relocated: not representable in

<fmt>

A1254E: Halfword literal values not supported

In the following example, change the LDRH into LDR, which is the standard way of loading constants into registers:

LDRH R3, =constant

- A1256E: DATA directive can only be used in CODE areas

- A1259E: Invalid PSR field specifier, syntax is <PSR>\_ where <PSR> is either CPSR or

SPSR

- A1260E: PSR field '<entity>' specified more than once

- A1261E: MRS cannot select fields, use APSR, CPSR or SPSR directly

This is caused by an attempt to use fields for CPSR or SPSR with an MRS instruction. For example:

MRS r0, CPSR c

- A1262U: Expression storage allocator failed

- A1265U: Structure mismatch: IF or WHILE unmatched at end of INCLUDE file

- A1267E: Bad GET or INCLUDE for file <filename>

- A1268E: Unmatched conditional or macro

- A1269U: unexpected GET on structure stack

- A1270E: File "<entity>" not found

- A1271E: Line too long, maximum line length is <MaxLineLength>

- A1272E: End of input file

- A1273E: '\\' should not be used to split strings

- A1274W: '\\' at end of comment

A1283E: Literal pool too distant, use LTORG to assemble it within 1KB

For T32 code, a literal pool must be within 1KB of an LDR instruction that is trying to access it. See also messages A1284E and A1471W.

A1284E: Literal pool too distant, use LTORG to assemble it within 4KB

For A32 code, a literal pool must be within 4KB of an LDR instruction that is trying to access it. To solve this, add an LTORG directive into your assembly source code at a convenient place.

See the following in the armasm User Guide:

- Load addresses to a register using LDR Rd, =label.

- LTORG.

```

A1285E: Bad macro name

A1286E: Macro already exists

A1287E: Illegal parameter start in macro prototype

A1288E: Illegal parameter in macro prototype

A1289E: Invalid parameter separator in macro prototype

A1290E: Macro definition too big, maximum length <max>

A1291E: Macro definitions cannot be nested

A1310W: Symbol attribute not recognized

A1311U: macro definition attempted within expansion

A1312E: Assertion failed

```

A1313W: Missing END directive at end of file

The assembler requires an END directive to know when the code in the file terminates. You can add comments or other such information in free format after this directive.

```

A1314W: Reserved instruction (using NV condition)

A1315E: NV condition not supported on targeted CPU

A1316E: Shifted register operand to MSR has undefined effect

A1319E: Undefined effect (using PC as Rs)

A1320E: Undefined effect (using PC as Rn or Rm in register specified shift)

A1321E: Undefined effect (using PC as offset register)

A1322E: Unaligned transfer of PC, destination address must be 4 byte aligned, otherwise result is UNPREDICTABLE

```

This error is reported when you try to use an LDR instruction to load the PC from a non word-aligned address. For example:

```

AREA Example, CODE

LDR pc, [pc, #6]; Error - offset must be a multiple of 4

END

```

This code gives an UNPREDICTABLE result.

```

A1323E: Reserved instruction (Rm = Rn with post-indexing)

A1324E: Undefined effect (PC + writeback)

A1327E: Non portable instruction (LDM with writeback and base in register list, final value of base unpredictable)

```

In the LDM instruction, if the base register <Rn> is specified in <registers>, and base register writeback is specified, the final value of <Rn> is UNKNOWN.

A1328E: Non portable instruction (STM with writeback and base not first in register list, stored value of base unpredictable)

In the STM instruction, if <Rn> is specified in <registers> and base register writeback is specified:

- If <Rn> is the lowest-numbered register specified in <register\_list>, the original value of <Rn> is stored.

- Otherwise, the stored value of <Rn> is UNKNOWN.

A1329E: Unpredictable instruction (forced user mode transfer with write-back to base)

This is caused by an instruction such as PUSH {r0}^ where the ^ indicates access to user registers. Writeback to the base register is not available with this instruction. Instead, the base register must be updated separately. For example:

```

SUB sp, sp,#4

STMID sp, {r0}^

```

Another example is replacing STMFD R0!, {r13, r14}^ with:

```

SUB r0, r0,#8

STM r0, {r13, r14}^

```

See also message A1085W.

```

A1331E: Unpredictable instruction (PC as source or destination)

```

A1332E: Unpredictable effect (PC-relative SWP)

A1334E: Undefined effect (use of PC/PSR)

A1335E: Useless instruction (PC cannot be written back)

A1337E: Useless instruction (PC is destination)

A1338E: Dubious instruction (PC used as an operand)

A1339E: Unpredictable if RdLo and RdHi are the same register

A1341E: Branch to unaligned destination, expect destination to be  $\langle max \rangle$  byte aligned

A1342W: <name> of symbol in another AREA will cause link-time failure if symbol is

not close enough to this instruction

A1344I: host error: out of memory

A1355U: A Label was found which was in no AREA

This can occur if no white space precedes an assembler directive. Assembler directives must be indented. For example use:

```

IF :DEF: FOO

; code

ENDIF

```

instead of:

```

IF :DEF: FOO

; code

ENDIF

```

Symbols beginning in the first column are assumed to be labels.

A1356E: Instruction not supported on targeted CPU

This occurs if you try to use an instruction that is not supported by the selected architecture or processor.

For example:

```

SMULBB r0,r0,r1 ;

```

This can be assembled with:

```

armasm --cpu 5TE

```

See the following:

Arm® Architecture Reference Manual.

A1406E: Bad decimal number

A1407E: Overlarge floating point value

A1408E: Overlarge (single precision) floating point value

A1409W: Small (single precision) floating value converted to 0.0

A1411E: Closing '>' missing from vector specifier

A1412E: Bad vector length, should be between <min> and <max>

A1413E: Bad vector stride, should be between <min> and <max>

A1414E: Vector wraps round over itself, length \* stride should not be greater than  $\langle max \rangle$

A1415E: VFPASSERT must be followed by 'VECTOR' or 'SCALAR'

A1416E: Vector length does not match current vector length <len>

A1417E: Vector stride does not match current vector stride

A1418E: Register has incorrect type '<type>' for instruction, expect floating point/

double register type

A1419E: Scalar operand not in a scalar bank

A1420E: Lengths of vector operands are different

A1421E: Strides of vector operands are different

A1422E: This combination of vector and scalar operands is not allowed

A1423E: This operation is not vectorizable

A1424E: Vector specifiers not allowed in operands to this instruction

A1425E: Destination vector must not be in a scalar bank

A1426E: Source vector must not be in a scalar bank

A1427E: Operands have a partial overlap

A1428E: Register list contains registers of varying types

A1429E: Expected register list

The assembler reports this when FRAME SAVE and FRAME RESTORE directives are not given register lists.

See the following in the armasm User Guide:

- FRAME RESTORE.

- FRAME SAVE.

A1430E: Unknown frame directive

A1431E: Frame directives are not accepted outside of PROCs/FUNCTIONs

See the following in the armasm User Guide:

Frame directives.

A1432E: Floating-point register type not consistent with selected floating-point architecture

A1433E: Only the writeback form of this instruction exists

The addressing mode specified for the instruction did not include the writeback specifier (that is, a '!' after the base register), but the instruction set only supports the writeback form of the instruction. Either use the writeback form, or replace with instructions that have the required behavior.

A1434E: Architecture attributes '<attr1>' and '<attr2>' conflict

A1435E: {PCSTOREOFFSET} is not defined when assembling for an architecture

{PCSTOREOFFSET} is only defined when assembling for a processor, not for an architecture.

A1437E: {ARCHITECTURE} is undefined

{ARCHITECTURE} is only defined when assembling for an architecture, not for a processor.

A1446E: Bad or unknown attribute '<attr>'. Use --apcs /interwork instead

For example:

```

AREA test1, CODE, READONLY

AREA test, CODE, READONLY, INTERWORK

```

This code might have originally been intended to work with the legacy Arm Software Development Toolkit (SDT). The INTERWORK area attribute is obsolete. To eliminate the error, do the following:

- Remove the ", INTERWORK" from the AREA line.

- Assemble with armasm --apcs /interwork foo.s instead.

A1447W: Missing END directive at end of file, but found a label named END

This is caused by the END directive not being indented.

```

A1448E: Deprecated form of PSR field specifier used (use _f)

A1449E: Deprecated form of PSR field specifier used (use _c)

A1450E: Deprecated form of PSR field specifier used (use _cxsf for future compatibility)

```

armasm supports the full range of MRS and MSR instructions, in the following forms:

```

MRS(cond) Rd, CPSR

MRS(cond) Rd, SPSR

MSR(cond) CPSR_fields, Rm

MSR(cond) SPSR_fields, Rm

MSR(cond) CPSR_fields, #immediate

MSR(cond) SPSR_fields, #immediate

```

where fields can be any combination of cxsf.

Legacy versions of the assembler permitted other forms of the MSR instruction to modify the control field and flags field:

- cpsr or cpsr all, control and flags field

- cpsr flg, flags field only

- cpsr ctl, control field only.

Similar control and flag settings apply for SPSR.

These forms are deprecated and must not be used. If your legacy code contains them, the assembler reports:

```

Deprecated form of PSR field specifier used (use _cxsf)

```

To avoid the warning, in most cases you can modify your code to use \_c, \_f, \_cf or \_cxsf instead.

See the following in the armasm User Guide:

- Conditional execution in A32 state.

- Conditional execution in T32 state.

- General-purpose registers in AArch32 state.

- Access to the inline barrel shifter in AArch32 state.

A1454E: FRAME STATE RESTORE directive without a corresponding FRAME STATE REMEMBER See the following in the *armasm User Guide*:

- Frame directives.

- FRAME STATE REMEMBER.

- FRAME STATE RESTORE.

A1456W: INTERWORK area directive is obsolete. Continuing as if --apcs /inter selected

For example, the following code generates this warning:

```

AREA test, CODE, READONLY, INTERWORK

```

This code might have originally been intended to work with the legacy Arm Software Development Toolkit (SDT). The INTERWORK area attribute is obsolete. To eliminate the warning, do the following:

- 1. Remove the ", INTERWORK" from the AREA line.

- 2. Assemble with armasm --apcs /interwork foo.s instead.

See also message A1446E.

A1457E: Cannot mix INTERWORK and NOINTERWORK code areas in same file

INTERWORK and (default) NOINTERWORK code areas cannot be mixed in the same file. This code might have originally been intended to work with the Arm Software Development Toolkit (SDT). The INTERWORK AREA attribute is obsolete in the Arm Compiler toolchain.

For example:

```

AREA test1, CODE, READONLY

...

AREA test2, CODE, READONLY, INTERWORK

```

To eliminate the error, carry out the following steps:

- 1. Move the two AREAs into separate assembly files, for example, test1.s and test2.s.

- 2. Remove, INTERWORK from the AREA line in test2.s.

- 3. Assemble test1.s with armasm --apcs /nointerwork.

- 4. Assemble test2.s with armasm --apcs /interwork.

- 5. At link time, the linker adds any necessary interworking veneers.

See also message A1446E.

A1458E: DCFD or DCFDU not allowed when fpu is None

A1459E: Cannot B or BL to a register

This form of the instruction is not permitted. See the following for the permitted forms:

Arm® Architecture Reference Manual.

A1461E: Specified processor or architecture does not support Thumb instructions

It is likely that you are specifying an architecture or processor using the --cpu option and incorporating T32 code in the AREA that is generating this error.

For example, in the following command line, code.s contains T32 code but the --arm\_only option forces only A32 code to be generated.

```

armasm --arm_only --cpu=7-A code.s

```

A1462E: Specified memory attributes do not support this instruction

A1463E: SPACE directive too big to fit in area, area size limit 2^32

A1464W: ENDP/ENDFUNC without corresponding PROC/FUNC

A1466W: Operator precedence means that expression would evaluate differently in C

armasm has always evaluated certain expressions in a different order to C. This warning might help C programmers from being caught out when writing in assembly language.

To avoid the warning, do either of the following:

- Modify the code to make the evaluation order explicit, by adding brackets.

- Suppress the warning with the --unsafe switch.

See the following in the armasm User Guide:

Operator precedence.

A1467W: FRAME ADDRESS with negative offset <offset> is not recommended A1468W: FRAME SAVE saving registers above the canonical frame address is not

recommended

A1469E: FRAME STATE REMEMBER directive without a corresponding FRAME STATE RESTORE See the following in the *armasm User Guide*:

- Frame directives.

- FRAME STATE REMEMBER.

- FRAME STATE RESTORE.

A1471W: Directive <directive> may be in an executable position

This can occur with, for example, the LTORG directive (see messages A1283E and A1284E). LTORG instructs the assembler to dump literal pool DCD data at this position.

To prevent this warning, the data must be placed where the processor cannot execute them as instructions. A good place for an LTORG is immediately after an unconditional branch, or after the return instruction at the end of a subroutine.

As a last resort, you could add a branch over the LTORG to avoid the data being executed. For example:

```

B unique_label

LTORG

unique_label

```

A1475E: At least one register must be transferred, otherwise result is UNPREDICTABLE

A1476E: BX r15 at non word-aligned address is UNPREDICTABLE

A1477E: This register combination results in UNPREDICTABLE behavior

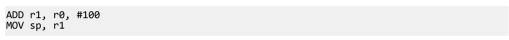

This error is generated when you are assembling an instruction that has UNPREDICTABLE results on execution. You must rewrite your code to avoid this UNPREDICTABLE behavior. For example, the following instructions all cause this error when assembling to T32, and the target architecture is Armv6T2 or later:

```

ADD sp, r0, #100 ; error - UNPREDICTABLE use of SP

CMP pc, #1 ; error - UNPREDICTABLE use of PC

PUSH {r0, pc} ; error - use of an UNPREDICTABLE register combination

```

A1479W: Requested alignment <alignreq> is greater than area alignment <align>, which has been increased

This is warning about an ALIGN directive that has a coarser alignment boundary than its containing AREA. This is not permitted. To compensate, the assembler automatically increases the alignment of the containing AREA for you. A simple test case that gives the warning is:

| AREA test, CODE,<br>ALIGN 16<br>mov pc, lr<br>END | ALIGN=3 |

|---------------------------------------------------|---------|

| END                                               |         |

In this example, the alignment of the AREA (ALIGN=3) is 2^3=8 byte boundary, but the mov pc.1r instruction is on a 16-byte boundary, causing the error.

| Note |

|------|

|------|

The two alignment types are specified in different ways.

This warning can also occur when using AREA ... ALIGN=0 to align a code section on a byte boundary. This is not possible. Code sections can only be aligned on:

- a four-byte boundary for A32 code, so use "ALIGN=2"

- a two-byte boundary for T32 code, so use "ALIGN=1".

See the following in the armasm User Guide:

- ALIGN.

- AREA.

A1480W: Macro cannot have same name as a directive or instruction A1481E: Object file format does not support this area alignment

A1482E: Shift option out of range, allowable values are from <min> to <max>

A1484W: Obsolete shift name 'ASL', use LSL instead

The Arm architecture does not have an ASL shift operation. The AArch32 barrel shifter only has the following shift types:

- ROR.

- ASR.

- LSR.

- LSL.

An arithmetic (that is, signed) shift left is the same as a logical shift left, because the sign bit always gets shifted out.

If the name ASL is used, the assembler reports this warning and converts the ASL to LSL.

See the following in the armasm User Guide:

- --unsafe.

- ASR.

A1485E: LDM/STM instruction exceeds maximum register count <max> allowed with --split ldm

A1486E: ADR/ADRL of a symbol in another AREA is not supported in ELF

The ADR and ADRL pseudo-instructions can only be used with labels within the same code section. To load an out-of-area address into a register, use LDR instead.

A1487W: Obsolete instruction name 'ASL', use LSL instead

This warning is given when the ASL instruction is used in pre-UAL T32 code, that is, when you assemble using the --16 command-line option, or you use the CODE16 directive. See the corresponding A32 ASL message A1484W.

A1488W: PROC/FUNC at line lineno> in '<filename>' without matching ENDP/ENDFUNC

A1489E: <FPU> is undefined A1490E: <CPU> is undefined

{CPU} is only defined by assembling for a processor and not an architecture.

A1491W: Internal error: Found relocation at offset <offset> with incorrect alignment

This might indicate an assembler fault. Contact your supplier.

A1492E: Immediate 0x<val> out of range for this operation. Permitted values are

0x<min> to 0x<max>

A1493E: REQUIRE must be in an AREA

A1495W: Target of branch is a data address

armasm determines the type of a symbol and detects branches to data. To suppress this warning, specify --diag-suppress 1495.

A1496W: Absolute relocation of ROPI address with respect to symbol '<symbol>' at offset <offset> may cause link failure

For example, when assembling the following code with --apcs /ropi, this warning is given. This is because it generates an absolute relocation (R ARM ABS32) to a PI code symbol.

```

AREA code, CODE

codeaddr DCD codeaddr

```

A1497W: Absolute relocation of RWPI address with respect to symbol '<symbol>' at offset <offset> may cause link failure

For example, when assembling the following code with --apcs /rwpi, this warning is given. This is because it generates an absolute relocation (R ARM ABS32) to a PI data symbol.

```

AREA data, DATA

dataaddr DCD dataaddr

```

A1498E: Unexpected characters following Thumb instruction

For example, the following instruction is valid in both UAL and pre-UAL code:

```

ADD r0, r0, r1

```

However, the following instruction is invalid in pre-UAL T32 code. The unexpected characters are , ASR #1.

```

ADD r0, r0, r1, ASR #1

```

A1499E: Register pair is not a valid contiguous pair

A1500E: Unexpected characters when expecting '<eword>'

A1501E: Shift option out of range, allowable values are 0, 8, 16 or 24

A1502W: Register <reg> is a caller-save register, not valid for this operation

A1505E: Bad expression type, expect logical expression

A1506E: Accumulator should be in form accx where x ranges from 0 to <max>

A1507E: Second parameter of register list must be greater than or equal to the first

A1508E: Structure mismatch expect Conditional

A1509E: Bad symbol type, expect label, or weak external symbol

A1510E: Immediate 0x<imm> cannot be represented by 0-255 and a rotation

A1511E: Immediate cannot be represented by combination of two data processing instructions

A1512E: Immediate 0x<val> out of range for this operation. Permitted values are <min>

to <max>

115125 . C. ....b - 1 ...

A1513E: Symbol not found or incompatible Symbol type for '<name>'

A1514E: Bad global name '<name>'

A1515E: Bad local name '<name>'

A1516E: Bad symbol '<name>', not defined or external

A1517E: Unexpected operator equal to or equivalent to <operator>

A1539E: Link Order dependency '<name>' not an area A1540E: Cannot have a link order dependency on self

A1541E: <code> is not a valid condition code

A1542E: Macro names <name1> and <name2>[parameter] conflict

A1543W: Empty macro parameter default value

A1544E: Invalid empty PSR field specifier, field must contain at least one of c,x,s,f

A1545U: Too many sections for one <objfmt> file

A1546W: Stack pointer update potentially breaks 8 byte stack alignment

The stack must be eight-byte aligned on an external boundary so pushing an odd number of registers causes this warning. For example:

```

PUSH {r0}

```

This warning is suppressed by default. To enable it, use --diag\_warning 1546.

See the following in the armasm User Guide:

--diag warning=tag{, tag}.

A1547W: PRESERVE8 directive has automatically been set

Example:

```

PUSH {r0,r1}

```

This warning is given because you have not explicitly set the PRESERVE8 directive, but the assembler has set it automatically. This warning is suppressed by default. To enable it, use --diag\_warning 1547.

See the following in the armasm User Guide:

- --diag warning=tag{, tag}.

- REQUIRE8 and PRESERVE8.

A1548W: Code contains LDRD/STRD indexed/offset from SP but REQUIRE8 is not set

This warning is given when the REQUIRE8 directive is not set when required. For example:

```

PRESERVE8

STRD r0,[sp,#8]

```

See the following in the armasm User Guide:

REQUIRE8 and PRESERVE8.

A1549W: Setting of REQUIRE8 but not PRESERVE8 is unusual

Example:

```

PRESERVE8 {FALSE}

REQUIRE8

STRD r0,[sp,#8]

```

A1550U: Input and output filenames are the same

A1551E: Cannot add Comdef area <name> to non-comdat group A1560E: Non-constant byte literal values not supported A1561E: MERGE and STRING sections must be data sections A1562E: Entry size for Merge section must be greater than 0

A1563W: Instruction stalls CPU for <stalls> cycle(s)

The assembler can give information about possible interlocks in your code caused by the pipeline of the processor chosen by the --cpu option. To do this, assemble with armasm --diag\_warning 1563.

```

_____ Note _____

```

If the --cpu option specifies a multi-issue processor such as Cortex®-A8, the interlock warnings are unreliable.

See also warning A1746W.

```

A1572E: Operator SB_OFFSET_11_0 only allowed on LDR/STR instructions

A1573E: Operator SB_OFFSET_19_12 only allowed on Data Processing instructions

A1574E: Expected one or more flag characters from "<str>

A1575E: BLX with bit[0] equal to 1 is architecturally UNDEFINED

A1576E: Bad coprocessor register name symbol

A1577E: Bad coprocessor name symbol

A1578E: Bad floating point register name symbol '<sym>'

A1581W: Added <no padbytes> bytes of padding at address <address>

```

By default, the assembler warns when it adds padding bytes to the generated code. This occurs whenever an instruction or directive is used at an address that requires a higher alignment, for example, to ensure A32 instructions start on a four-byte boundary after some T32 instructions, or where there is a DCB followed by a DCD.

For example:

```

AREA Test, CODE, READONLY

THUMB

ThumbCode

MOVS r0, #1

ADR r1, ARMProg

BX r1

; ALIGN; <<< uncomment to avoid the first warning

ARM

ARMProg

ADD r0,r0,#1

BX LR

DCB 0xFF

DCD 0x1234

END

```

This code results in the following warnings:

```

A1581W: Added 2 bytes of padding at address 0x6

8 00000008 ARM

A1581W: Added 3 bytes of padding at address 0x11

13 00000014 DCD 0x1234

```

The warning can also occur when using ADR in T32-only code. The ADR T32 pseudo-instruction can only load addresses that are word aligned, but a label within T32 code might not be word aligned. Use ALIGN to ensure four-byte alignment of an address within T32 code.

See the following in the armasm User Guide:

- ADR (PC-relative).

- *ADR* (register-relative).

- ALIGN.

- *DCB*.

- DCD and DCDU.

```

A1582E: Link Order area '<name>' undefined

A1583E: Group symbol '<name>' undefined

A1584E: Mode <mode> not allowed for this instruction

A1585E: Bad operand type (<typ1>) for operator <op>

```

A1586E: Bad operand types (<typ1>, <typ2>) for operator <op>

```

A1587E: Too many registers <count> in register list, maximum of <max>

A1588E: Align only available on VLD and VST instructions

A1589E: Element index must remain constant across all registers

A1590E: Mix of subscript and non-subscript elements not allowed

A1593E: Bad Alignment, must match transfer size UIMM * <dt>

A1595E: Bad Alignment, must match <st> * <dt>, or 64 when <st> is 4

A1596E: Invalid alignment <align> for dt st combination

A1597E: Register increment of 2 not allowed when dt is 8

A1598E: Bad Register list length

A1599E: Out of range subscript, must be between 0 and <max index>

A1600E: Section type must be within range SHT_LOOS and SHT_HIUSER

A1601E: Immediate cannot be represented

A1603E: This instruction inside IT block has UNPREDICTABLE results

A1604W: Thumb Branch to destination without alignment to <max> bytes

A1606E: Symbol attribute <attrl> cannot be used with attribute <attr2>

A1607E: Thumb-2 wide branch instruction used, but offset could fit in Thumb-1 narrow

branch instruction

A1608W: MOV pc,<rn> instruction used, but BX <rn> is preferred

A1609W: MOV <rd>,pc instruction does not set bit zero, so does not create a return

```

This warning is caused when the current value of the PC is copied into a register while executing in T32 state. An attempt to create a return address in this fashion fails because bit[0] is not set. Attempting to branch with BX to this instruction causes a state change to A32.

To create a return address, you can use:

address

```

MOV r0, pc

ADDS r0, #1

```

You can then safely suppress this warning with:

```

--diag_suppress 1609

A1611E: Register list increment of 2 not allowed for this instruction

A1612E: <type> addressing not allowed for <instr>

A1613E: Invalid register or register combination for this operation, <registers>, expected one of <expected>

A1614E: Scalar access not allowed when dt is 64

A1615E: Store of a single element or structure to all lanes is UNDEFINED

A1616E: Instruction, offset, immediate or register combination is not supported by the current instruction set

```

This error can be caused by attempting to use an invalid combination of operands. For example, in T32:

```

MOV r0, #1 ; /* Not permitted */

MOVS r0, #1 ; /* Ok */

```

See the following in the armasm User Guide:

#### A32 and T32 Instructions.

```

A1617E: Specified width is not supported by the current instruction set

A1618E: Specified instruction is not supported by the current instruction set

A1619E: Specified condition is not consistent with previous IT

A1620E: Error writing to file '<filename>': <reason>

A1621E: CBZ or CBNZ from Thumb code to ARM code

A1622E: Negative register offsets are not supported by the current instruction set

A1623E: Offset not supported by the current instruction set

A1624W: Branch from Thumb code to ARM code

A1625W: Branch from ARM code to Thumb code

```

A1626W: BL from Thumb code to ARM code A1627W: BL from ARM code to Thumb code

This occurs when there is a branch from A32 code to T32 code (or from T32 code to A32 code) within this file. The usual solution is to move the T32 code into a separate assembler file. Then, at link-time, the linker adds any necessary interworking veneers.

A1630E: Specified processor or architecture does not support ARM instructions

Arm M-profile processors, for example Cortex-M3 and Cortex-M1, implement only the T32 instruction set, not the A32 instruction set. It is likely that the assembly file contains some A32-specific instructions and is being built for one of these processors.

A1631E: Only left shifts of 1, 2 and 3 are allowed on load/stores

A1632E: Else forbidden in IT AL blocks

A1633E: LDR rx,= pseudo instruction only allowed in load word form A1634E: LDRD/STRD has no register offset addressing mode in Thumb

A1635E: CBZ/CBNZ can not be made conditional

A1636E: Flag setting MLA is not supported in Thumb

A1637E: Error reading line: <reason>

A1638E: Writeback not allowed on register offset loads or stores in Thumb

A1639E: Conditional DCI only allowed in Thumb mode

A1640E: Offset must be a multiple of four

A1641E: Forced user-mode LDM/STM not supported in Thumb

A1642W: Relocated narrow branch is not recommended

A1643E: Cannot determine whether instruction is working on single or double precision values.

A1644E: Cannot use single precision registers with FLDMX/LSTMX

A1645W: Substituted <old> with <new>

armasm can be configured to issue a warning in cases where it chooses to substitute an instruction. For example:

- ADD negative number is the same as SUB positive number

- MOV negative\_number is the same as MVN positive\_number

- CMP negative\_number is the same as CMN positive\_number.

For the T32 instruction set, UNPREDICTABLE single register LDMs are transformed into LDRs.

This warning is suppressed by default, but can be enabled with --diag\_warning 1645.

For example, when the following code is assembled with --diag warning 1645:

```

AREA foo, CODE

ADD r0, #-1

MOV r0, #-1

CMP r0, #-1

```

the assembler reports:

```

Warning: A1645W: Substituted ADD with SUB

3 00000000 ADD r0, #-1

Warning: A1645W: Substituted MOV with MVN

4 00000004 MOV r0, #-1

Warning: A1645W: Substituted CMP with CMN

5 00000008 CMP r0, #-1

```

and the resulting code generated is:

```

foo

0x00000000: e2400001 ..@. SUB r0,r0,#1

0x00000004: e3e00000 .... MVN r0,#0

0x00000008: e3700001 ..p. CMN r0,#1

```

A1647E: Bad register name symbol, expected Integer register

An integer (core) register is expected at this point in the syntax.

A1648E: Bad register name symbol, expected Wireless MMX SIMD register

A1649E: Bad register name symbol, expected Wireless MMX Status/Control or General

Purpose register

A1650E: Bad register name symbol, expected any Wireless MMX register

A1651E: TANDC, TEXTRC and TORC instructions with destination register other than R15

is undefined

A1652W: FLDMX/FSTMX instructions are deprecated in ARMv6. Please use FLDMD/FSTMD

instructions to save and restore unknown precision values.

A1653E: Shift instruction using a status or control register is undefined

A1654E: Cannot access external symbols when loading/storing bytes or halfwords

A1655E: Instruction is UNPREDICTABLE if halfword/word/doubleword is unaligned

A1656E: Target must be at least word-aligned when used with this instruction

A1657E: Cannot load a byte/halfword literal using WLDRB/WLDRH =constant

A1658W: Support for <opt> is deprecated

An option passed to armasm is deprecated.

See the following in the armasm User Guide:

# Assembler command-line options.

```

A1659E: Cannot B/BL/BLX between ARM/Thumb and Thumb-2EE

```

A1660E: Cannot specify scalar index on this register type

A1661E: Cannot specify alignment on this register

A1662E: Cannot specify a data type on this register type

A1663E: A data type has already been specified on this register

A1664E: Data type specifier not recognized

A1665E: Data type size must be one of 8, 16, 32 or 64

A1666E: Data type size for floating-point must be 32 or 64

A1667E: Data type size for polynomial must be 8 or 16

A1668E: Too many data types specified on instruction

A1669E: Data type specifier not allowed on this instruction

A1670E: Expected 64-bit doubleword register expression

A1671E: Expected 128-bit quadword register expression

A1672E: Expected either 64-bit or 128-bit register expression

A1673E: Both source data types must be same type and size

A1674E: Source operand 1 should have integer type and be double the size of source

operand 2

A1675E: Data types and sizes for destination must be same as source

A1676E: Destination type must be integer and be double the size of source

A1677E: Destination type must be same as source, but half the size

A1678E: Destination must be untyped and same size as source

A1679E: Destination type must be same as source, but double the size

A1680E: Destination must be unsigned and half the size of signed source

A1681E: Destination must be unsigned and have same size as signed source

A1682E: Destination must be un/signed and source floating, or destination floating

and source un/signed, and size of both must be 32-bits

A1683E: Data type specifiers do not match a valid encoding of this instruction

A1684E: Source operand type should be signed or unsigned with size between <min> and

A1685E: Source operand type should be signed, unsigned or floating point with size

between <min> and <max>

A1686E: Source operand type should be signed or floating point with size between

<min> and <max>

A1687E: Source operand type should be integer or floating point with size between

<min> and <max>

A1688E: Source operand type should be untyped with size between <min> and <max>

A1689E: Source operand type should be <n>-bit floating point

A1690E: Source operand type should be signed with size between <min> and <max>

A1691E: Source operand type should be integer, floating point or polynomial with size

between <min> and <max>

A1692E: Source operand type should be signed, unsigned or polynomial with size

between <min> and <max>

A1693E: Source operand type should be unsigned or floating point with size between

<min> and <max>

A1694E: Instruction cannot be conditional in the current instruction set

Conditional instructions are not permitted in the specified instruction set. The instruction MOVEQ, for example, is permitted in A32 code, and in T32 code in architectures in which the IT instruction is available.

A1695E: Scalar index not allowed on this instruction

A1696E: Expected either 32-bit, 64-bit or 128-bit register expression

A1697E: Expected either 32-bit or 64-bit VFP register expression

A1698E: Expected 32-bit VFP register expression

A1699E: 64-bit data type cannot be used with these registers

A1700E: Source operand type should be integer with size between <min> and <max>

A1701E: 16-bit polynomial type cannot be used for source operand

A1702E: Register Dm can not be scalar for this instruction

A1704E: Register Dm must be in the range D0-D<upper> for this data type

A1705W: Assembler converted Qm register to D<rnum>[<idx>]

A1706E: Register Dm must be scalar

A1708E: 3rd operand to this instruction must be a constant expression

A1709E: Expected ARM or scalar register expression

A1710E: Difference between current and previous register should be <diff>

A1711E: Scalar registers cannot be used in register list for this instruction

A1712E: This combination of LSB and WIDTH results in UNPREDICTABLE behavior

A1713E: Invalid field specifiers for APSR: must be APSR $_$  followed by at least one of n, z, c, v, q or g

A1714E: Invalid combination of field specifiers for APSR

A1715E: PSR not defined on target architecture

A1716E: Destination for VMOV instruction must be ARM integer, 32-bit single-

precision, 64-bit doubleword register or 64-bit doubleword scalar register

A1717E: Source register must be an ARM integer, 32-bit single-precision or 64-bit doubleword scalar register

A1718E: Source register must be an ARM integer register or same as the destination register

A1719W: This PSR name is deprecated and may be removed in a future release

A1720E: Source register must be a 64-bit doubleword scalar register

A1721E: Destination register may not have all-lanes specifier

A1722E: Labels not allowed inside IT blocks

A1723W: RELOC is deprecated, please use the new RELOC directive

A1724E: RELOC may only be used immediately after an instruction or data generating directive

A1725W: 'armasm inputfile outputfile' form of command-line is deprecated

A1726W: Decreasing --max\_cache below 8MB is not recommended

A1727W: Immediate could have been generated using the 16-bit Thumb MOVS instruction

A1728E: Source register must be same type as destination register

${\tt A1729E: Register\ list\ may\ only\ contain\ 32-bit\ single-precision\ or\ 64-bit\ doubleword\ registers}$

A1730E: Only IA or DB addressing modes may be used with these instructions

A1731E: Register list increment of 2 or more is not allowed for quadword registers

A1732E: Register list must contain between 1 and 4 contiguous doubleword registers

A1733E: Register list must contain 2 or 4 doubleword registers, and increment 2 is

only allowed for 2 registers

A1734E: Register list must contain <n> doubleword registers with increment 1 or 2

A1735E: Post-indexed offset must equal the number of bytes loaded/stored (<n>)

A1736E: Number of registers in list must equal number of elements

A1737E: PC or SP can not be used as the offset register

A1738E: Immediate too large for this operation

A1739W: Constant generated using single VMOV instruction; second instruction is a NOP

A1740E: Number of bytes in FRAME PUSH or FRAME POP directive must not be less than

zero

A1741E: Instruction cannot be conditional

A1742E: Expected LSL #Imm

A1744E: Alignment on register must be a multiple of 2 in the range 16 to 256

${\tt A1745W:}$  This register combination is <code>DEPRECATED</code> and may not work in future

architecture revisions

This warning is generated when all of the following conditions are satisfied:

• You are using a deprecated register combination, for example:

PUSH {r0, pc}

- You are assembling for a target architecture that supports 32-bit T32 instructions, in other words Armv6T2 or later.

- You are assembling to A32 code.

\_\_\_\_\_ Note \_\_\_\_\_

- When assembling to T32, rather than A32 code, and the target architecture is Armv6T2 or later, the assembler generates error A1477E instead.

- When assembling for an architecture or processor that does not support 32-bit T32

instructions, in other words Arm architectures before Armv6T2, by default no diagnostic is

emitted.

A1746W: Instruction stall diagnostics may be unreliable for this CPU

This warning is shown when you enable message A1563W for a processor that is not modeled accurately by the assembler. It indicates that you cannot rely on the output of A1563W when improving your code.

See also warning A1563W.

A1753E: Unrecognized memory barrier option

A1754E: Cannot change the type of a scalar register

A1755E: Scalar index has already been specified on this register

A1756E: Data type must be specified on all registers

A1757W: Symbol attributes must be within square brackets; Any other syntax is deprecated

A1758W: Exporting multiple symbols with this directive is deprecated

A1759E: Specified processor or architecture does not support Thumb-2EE instructions

A1760W: Build Attribute <from> is '<attr>'

A1761W: Difference in build attribute from '<diff>' in <from>

A1762E: Branch offset 0x<val> out of range of 16-bit Thumb branch, but offset

encodable in 32-bit Thumb branch