# ARM<sup>®</sup> CoreLink<sup>™</sup> DMC-520 Dynamic Memory Controller

Revision: r2p2

**Technical Reference Manual**

# ARM® CoreLink™ DMC-520 Dynamic Memory Controller

# **Technical Reference Manual**

Copyright © 2014-2016 ARM. All rights reserved.

#### Release information

## **Document History**

| Issue   | Date              | Confidentiality  | Change                   |

|---------|-------------------|------------------|--------------------------|

| 0000-00 | 07 March 2014     | Non-Confidential | First release for r0p0.  |

| 0001-00 | 30 September 2014 | Non-Confidential | First release for r0p1.  |

| 0100-00 | 12 February 2015  | Non-Confidential | First release for r1p0.  |

| 0200-00 | 23 June 2015      | Non-Confidential | First release for r2p0.  |

| 0200-01 | 30 October 2015   | Non-Confidential | Second release for r2p0. |

| 0200-02 | 09 March 2016     | Non-Confidential | First release for r2p1   |

| 0202-00 | 15 July 2016      | Non-Confidential | First release for r2p2   |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of ARM. No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, ARM makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to ARM's customers is not intended to create or refer to any partnership relationship with any other company. ARM may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any signed written agreement covering this document with ARM, then the signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

Words and logos marked with <sup>®</sup> or <sup>™</sup> are registered trademarks or trademarks of ARM Limited or its affiliates in the EU and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow ARM's trademark usage guidelines at <a href="http://www.arm.com/about/trademark-usage-guidelines.php">http://www.arm.com/about/trademark-usage-guidelines.php</a>

Copyright © 2014-2016, ARM Limited or its affiliates. All rights reserved.

ARM Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

# **Confidentiality status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

Unrestricted Access is an ARM internal classification.

# **Product status**

The information in this document is Final, that is for a developed product.

# Web address

http://www.arm.com

# Contents

# ARM<sup>®</sup> CoreLink<sup>™</sup> DMC-520 Dynamic Memory Controller Technical Reference Manual

|           | Pref  | face                                  |      |

|-----------|-------|---------------------------------------|------|

|           |       | About this book                       | 7    |

|           |       | Feedback                              | 10   |

| Chapter 1 | Intro | oduction                              |      |

|           | 1.1   | About the product                     | 1-12 |

|           | 1.2   | DMC-520 compliance                    | 1-13 |

|           | 1.3   | Features                              | 1-14 |

|           | 1.4   | Interfaces                            | 1-15 |

|           | 1.5   | Configurable options                  | 1-16 |

|           | 1.6   | Test features                         | 1-17 |

|           | 1.7   | Product documentation and design flow | 1-18 |

|           | 1.8   | Product revisions                     | 1-20 |

| Chapter 2 | Fun   | ctional Description                   |      |

|           | 2.1   | About the functions                   | 2-22 |

|           | 2.2   | Clocking and resets                   | 2-24 |

|           | 2.3   | Interfaces                            | 2-25 |

|           | 2.4   | Constraints and limitations of use    | 2-29 |

| Chapter 3 | Prog  | grammers Model                        |      |

|           | 3.1   | About this programmers model          | 3-31 |

|           |       |                                       |      |

|            | 3.2 Register summary      | 3-32       |

|------------|---------------------------|------------|

|            | 3.3 Register descriptions | 3-44       |

| Appendix A | Signal Descriptions       |            |

|            | A.1 Signals list          | Appx-A-145 |

| Appendix B | Revisions                 |            |

|            | B.1 Revisions             | Appx-B-160 |

# **Preface**

This preface introduces the  $ARM^{\otimes}$   $CoreLink^{\mathsf{TM}}$  DMC-520 Dynamic Memory Controller Technical Reference Manual.

It contains the following:

- About this book on page 7.

- Feedback on page 10.

# About this book

This book is for the ARM® CoreLink™ DMC-520 Dynamic Memory Controller.

#### Product revision status

The rmpn identifier indicates the revision status of the product described in this book, for example, r1p2, where:

rm Identifies the major revision of the product, for example, r1.

pn Identifies the minor revision or modification status of the product, for example, p2.

# Intended audience

This book is written for experienced engineers who want to integrate the delivered ARM DMC-520 product in a *System on Chip* (SoC) design.

# Using this book

This book is organized into the following chapters:

### **Chapter 1 Introduction**

This chapter describes the DMC-520.

# **Chapter 2 Functional Description**

This chapter describes how the DMC-520 operates.

# **Chapter 3 Programmers Model**

This chapter describes the programmers model of the DMC-520.

# Appendix A Signal Descriptions

This appendix describes the DMC-520 signals.

# Appendix B Revisions

This appendix describes the technical changes between released issues of this book.

#### Glossary

The ARM Glossary is a list of terms used in ARM documentation, together with definitions for those terms. The ARM Glossary does not contain terms that are industry standard unless the ARM meaning differs from the generally accepted meaning.

See the ARM Glossary for more information.

# Typographic conventions

italic

Introduces special terminology, denotes cross-references, and citations.

# bold

Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.

# monospace

Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.

# <u>mono</u>space

Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name.

#### monospace italic

Denotes arguments to monospace text where the argument is to be replaced by a specific value.

# monospace bold

Denotes language keywords when used outside example code.

#### <and>

Encloses replaceable terms for assembler syntax where they appear in code or code fragments. For example:

#### SMALL CAPITALS

Used in body text for a few terms that have specific technical meanings, that are defined in the *ARM glossary*. For example, IMPLEMENTATION DEFINED, IMPLEMENTATION SPECIFIC, UNKNOWN, and UNPREDICTABLE.

# **Timing diagrams**

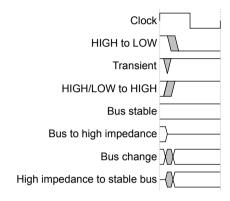

The following figure explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

Figure 1 Key to timing diagram conventions

# **Signals**

The signal conventions are:

#### Signal level

The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals.

- LOW for active-LOW signals.

# Lowercase n

At the start or end of a signal name denotes an active-LOW signal.

# **Additional reading**

This book contains information that is specific to this product. See the following documents for other relevant information.

# **ARM** publications

- ARM® AMBA® APB Protocol Specification (ARM IHI 0024).

- ARM® Low Power Interface Specification, Q-Channel and P-Channel Interfaces (ARM IHI 0068).

- Principles of ARM® Memory Maps White Paper (ARM DEN 0001).

The following confidential books are only available to licensees:

- ARM® CoreLink™ DMC-520 Dynamic Memory Controller Design Manual (ARM 100001).

- *ARM® CoreLink™ DMC-520 Dynamic Memory Controller Integration Manual* (ARM 100003).

- ARM® CoreLink™ DMC-520 Dynamic Memory Controller Implementation Guide (ARM 100002).

- *ARM*® *AMBA*® *5 CHI Architecture Specification* (ARM IHI 0050).

- ARM® CoreLink™ CCN-504 Cache Coherent Network Technical Reference Manual (ARM 100017).

# Other publications

- JEDEC STANDARD DDR3 SDRAM Specification, JESD79-3D, http://www.jedec.org.

- JEDEC STANDARD DDR3L SDRAM Specification, JESD79-3-1A, http://www.jedec.org.

- JEDEC STANDARD DDR4 SDRAM Specification, JESD79-4, http://www.jedec.org.

- JEDEC STANDARD DDR3 RDIMM Specification, JESD82-29, http://www.jedec.org.

- JEDEC STANDARD DDR4 RDIMM Common Design Specification, (pre-release), http://www.jedec.org.

- JEDEC STANDARD DDR4 LRDIMM Common Design Specification, (pre-release), http://www.jedec.org.

- JEDEC STANDARD DDR4 RCD Specification, (pre-release), http://www.jedec.org.

- JEDEC STANDARD DDR4 DB Specification, (pre-release), http://www.jedec.org.

- DDR PHY Interface DFI 3.1 Specification, http://ddr-phy.org/.

| Note                                                                                |

|-------------------------------------------------------------------------------------|

| See the ARM® CoreLink™ DMC-520 Dynamic Memory Controller Release Note for the actua |

| versions of the specifications that ARM used when designing the device.             |

# **Feedback**

# Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

# Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- The title ARM® CoreLink™ DMC-520 Dynamic Memory Controller Technical Reference Manual.

- The number ARM 100000\_0202\_00\_en.

- If applicable, the page number(s) to which your comments refer.

- A concise explanation of your comments.

| ARM also welcomes general suggestions for additions and improvements.                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note                                                                                                                                                          |

| ARM tests the PDF only in Adobe Acrobat and Acrobat Reader, and cannot guarantee the quality of the represented document when used with any other PDF reader. |

# Chapter 1 **Introduction**

This chapter describes the DMC-520.

It contains the following sections:

- 1.1 About the product on page 1-12.

- 1.2 DMC-520 compliance on page 1-13.

- 1.3 Features on page 1-14.

- 1.4 Interfaces on page 1-15.

- 1.5 Configurable options on page 1-16.

- 1.6 Test features on page 1-17.

- 1.7 Product documentation and design flow on page 1-18.

- 1.8 Product revisions on page 1-20.

# 1.1 About the product

This is a high-level overview of the DMC-520.

The DMC-520 is an ARM AMBA 5 CHI SoC peripheral developed, tested, and licensed by ARM. It is a high-performance, area-optimized memory controller that is compatible with the AMBA 5 CHI protocol. It supports the following memory devices:

- Double Data Rate 3 (DDR3) SDRAM.

- Low-voltage DDR3 SDRAM.

- Double Data Rate 4 (DDR4) SDRAM.

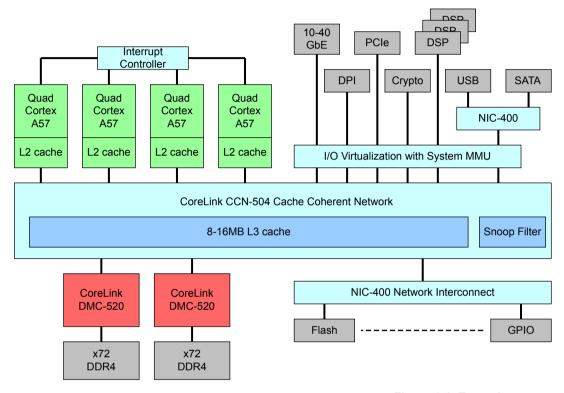

The following figure shows an example system.

Figure 1-1 Example system

The DMC-520 enables data transfer between the SoC and the SDRAM devices external to the chip. It connects to the on-chip system through a single CHI interface and to a processor through the programmers APB3 interface to program the DMC-520. It connects to the SDRAM devices through its memory interface block and the *DDR PHY Interface* (DFI).

# 1.2 DMC-520 compliance

The DMC-520 is compatible with the following protocol specifications and standards:

- AMBA 5 CHI protocol.

- AMBA 3 APB protocol.

- JEDEC DDR4 JESD79-4 standard.

- JEDEC DDR3 JESD79-3 standard.

- JEDEC DDR3L JESD79-3-1 standard.

- JEDEC JESD82-29 standard.

- JEDEC LRDIMM DDR4 Memory Buffer Spec Proposal.

- DDR4 SDRAM Registered DIMM Design Specification.

- DDR4 SDRAM Load Reduced DIMM Design Specification.

- DFI 3.1.

# 1.3 Features

The DMC-520 supports DDR3 and DDR4 SDRAMs. It also supports error checking, reliability, availability, and serviceability features. In addition, *Quality of Service* (QoS) features and ARM TrustZone® architecture security extensions are built in throughout the controller.

The system interface provides a CHI interface for connection to a CoreLink *Cache Coherent Network* (CCN), an APB3 interface for configuration and initialization purposes, and an external performance event interface for connecting to CoreSight™ on-chip debug and trace technology.

The DMC-520 has the following features:

- Profiling signals that enable performance profiling to be performed in the system.

- TrustZone architecture security extensions.

- Buffering to optimize read and write turnaround and to maximize bandwidth.

- A system interface that provides:

- A CHI interface to connect to a CCN.

- An APB3 interface for configuration and initialization purposes.

- A Memory Interface (MI) that provides:

- A DFI interface to a PHY that supports DDR3, DDR3L, and DDR4.

- Support for DFI 1:1, 1:2, and 1:4 DFI frequency ratio modes.

- Support for either a 32-bit wide data SDRAM interface or a 64-bit wide data SDRAM interface.

- Low-power operation through programmable SDRAM power modes.

- Reliability, Availability, Serviceability (RAS):

- Single Error Correcting, Double Error Detecting (SECDED) Error-Correcting Code (ECC) for off-chip DRAM.

- Symbol-based ECC, to correct memory chip and data-lane failures.

- SECDED ECC for on-chip RAM protection.

- Hardware Read-Modify-Write (RMW) for systems supporting sparse writes.

- Command-Address (CA) parity checks for DDR3 and DDR4 link errors.

- CRC write-data protection for DDR4 devices.

- A programmable mechanism for automated SDRAM scrubbing.

- Error handling and automated recovery.

- Refresh Control Logic for memory banks.

- Power Control Logic that generates powerdown requests to the SDRAM, and manages power enables for the PHY logic.

# 1.4 Interfaces

This section lists the interfaces in the DMC-520.

The DMC-520 has the following external interfaces:

- A system interface to provide read and write access to or from a master that supports the CHI protocol.

- An APB3 programmers interface to program and control the DMC-520.

- A DFI-compatible PHY interface to transfer data to and from the external memory.

- A profile and debug interface.

- A low-power clock control interface that uses the Q-Channel protocol. See *Q-Channel interface* on page 2-27.

- An abort interface that is a 4-phase request and acknowledge handshake that you can use to recover from a livelock that is caused by DRAM or PHY failure.

- User I/O ports.

- A set of interrupts that are used to report operational events and detected faults.

# 1.5 Configurable options

The DMC-520 has the following configurable options:

The different DFI frequency ratios that the DMC can support are defined in the *DFI* specification. The DMC supports the following options:

- 1:1 Frequency Ratio Mode where **dfi\_clk** = SDRAM CLK.

- 1:2 Frequency Ratio Mode where **dfi** clk =  $\frac{1}{2}$  × SDRAM CLK.

- 1:4 Frequency Ratio Mode where **dfi clk** = ½×SDRAM CLK.

| Note                                                                    |    |

|-------------------------------------------------------------------------|----|

| The DFI Frequency Ratio is the only configurable option for the DMC-520 | ). |

# 1.6 Test features

The DMC-520 provides the following test features:

- Integration test logic for integration testing.

- A debug and profile interface to enable you to monitor transaction events.

# 1.7 Product documentation and design flow

This section describes the DMC-520 books and how they relate to the design flow.

### **Documentation**

The DMC-520 documentation is as follows:

#### **Technical Reference Manual**

The *Technical Reference Manual* (TRM) summarizes the functionality of the DMC, and describes its signals.

# **Design Manual**

The *Design Manual* (DM) describes the functionality and the effects of functional options on the behavior of the DMC. It is required at all stages of the design flow. The choices that are made in the design flow can mean that some behavior described in the DM is not relevant. If you are programming the DMC, then contact:

- The implementer to determine what integration, if any, was performed before implementing the DMC.

- The integrator to determine the pin configuration of the device that you are using.

The DM is a confidential book that is only available to licensees.

# **Implementation Guide**

The Implementation Guide (IG) describes:

- How to synthesize the *Register Transfer Level* (RTL).

- How to integrate RAM arrays.

- How to run test patterns.

- The processes to sign off the configured design.

The ARM product deliverables include reference scripts and information about using them to implement your design. Contact your EDA vendor for EDA tool support.

The IG is a confidential book that is only available to licensees.

# **Integration Manual**

The *Integration Manual* (IM) describes how to integrate the DMC into a SoC. It includes a description of the pins that the integrator must tie off to connect the DMC into an SoC design or to other IP.

The IM is a confidential book that is only available to licensees.

# **Design flow**

The DMC-520 is delivered as synthesizable RTL. Before it can be used in a product, it must go through the following processes:

# **Implementation**

The implementer synthesizes the RTL to produce a hard macrocell. This includes integrating RAMs into the design.

# Integration

The integrator connects the implemented design into a SoC. This includes connecting it to a memory system.

# **Programming**

This is the last process. The system programmer develops the software that is required to initialize the DMC, and tests the required application software.

# Each process:

- Can be performed by a different party.

- Can include implementation and integration choices that affect the behavior and features of the DMC.

The operation of the final device depends on:

# **Configuration inputs**

The integrator configures some features of the DMC by tying inputs to specific values. These configurations affect the start-up behavior before any software configuration is made. They can also limit the options available to the software.

# **Software programming**

| The programmer configures the DMC | y programming particular | values into registers. Th | iis |

|-----------------------------------|--------------------------|---------------------------|-----|

| affects the behavior of the DMC.  |                          |                           |     |

| Note                                                                                                                                                                                    |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| This manual refers to implementation-defined features. Reference to a fithe appropriate signal configuration options are selected. Reference to a has also been configured by software. |  |

# 1.8 Product revisions

This section describes the differences in functionality between product revisions of the DMC-520.

**r0p0** First release.

r0p0-r0p1 • Updated DIMM support.

Updated address mode.

• Updated the scrub engine operation.

• Added an optimized 2-cycle preamble bus turnaround function.

• Added update interrupts and DCI update options.

• Added rank mask capability.

Added pwakeup.

• Updated DFT signals to latest standard.

**r0p1-r1p0** Added 32-bit memory interface support.

**r1p0-r2p0** Added configurable support for 1:1, 1:2, and 1:4 DFI frequency ratio modes.

**r2p0-r2p1** • Added the phy\_request\_cs\_remap, phy\_rdwrdata\_cs\_mask\_31\_00, and phy\_rdwrdata\_cs\_mask\_63\_32\_registers.

• Added the sparse 3ds cs bit to the feature config register.

**r2p1-r2p2** • Updated the functionality of ODT.

# Chapter 2 Functional Description

This chapter describes how the DMC-520 operates.

It contains the following sections:

- 2.1 About the functions on page 2-22.

- 2.2 Clocking and resets on page 2-24.

- 2.3 Interfaces on page 2-25.

- 2.4 Constraints and limitations of use on page 2-29.

# 2.1 About the functions

This section gives a brief description of all the functions of the device.

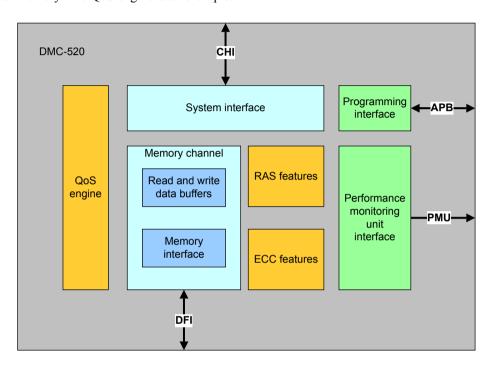

The following figure shows a block diagram of the functions of the DMC-520. The colors show the different categories of functions:

- Blue indicates the blocks that are associated with data flow. The System interface is an example.

- Green indicates the blocks that are associated with programming. The Programming interface is an

example.

- Orange indicates the blocks that are associated with the quality and efficiency of the communication to its external memory. The QoS engine is an example.

Figure 2-1 DMC functional block diagram

# System interface

The DMC-520 interfaces to the rest of the SoC through the System interface. This interface connects to a CHI *Slave Node* (SN-F) interface. For any attempted accesses that the system makes outside of the programmed address range of the DMC-520, the System interface responds with a *Non-data Error* (NDERR) response. Depending on how you program the DMC-520, it converts the system access information to the correct rank, bank, column, and row access of the external SDRAM that connects to it. The System interface supports TrustZone features to regulate Secure and Non-secure accesses to both Secure and Non-secure regions of memory.

The DMC monitors queue occupancies and dictates whether system requests of any given QoS are accepted. Prefetched and Dynamic P-Credit requests are allocated based on a threshold setting, which is derived from register settings.

# **Memory channel**

Through this interface, the DMC-520 conducts its data transactions with the SDRAM and regulates the power consumption of the SDRAM. The DMC-520 uses the ECC information that it receives from the SDRAM to maximize the reliability from these devices.

# **Programming interface**

Through this interface, a master in the system programs the DMC-520. You can define the Secure and Non-secure regions of external memory and also define how the DMC-520 addresses the external memory, from the address that the system provides on its system interface. You can also make direct accesses to the SDRAM, for example to initialize it.

# **Performance Monitoring Unit interface**

You can use the *Performance Monitoring Unit* (PMU) interface to monitor the performance and power settings for your specific application. This interface allows you to monitor the inner workings of the device and so enables additional information to be viewed.

# **QoS** engine

The DMC-520 provides controls to enable you to adjust its arbitration scheme for your system to maximize the availability of your external memory devices. It provides buffers to re-order system transaction requests. It uses an advanced scheduling algorithm to ensure that traffic going to one memory bank causes minimal disruption to traffic going to a different memory bank. It also schedules transaction requests according to the availability of the destination memory bank. For system access requests to different available memory banks, the DMC-520 arbitrates these requests using the QoS priority initially and then the temporal priority. These memory access requests all compete for control of the external SDRAM bus and SDRAM bank availability.

### **RAS**

RAS features include support for the following:

- SECDED ECC and symbol-based ECC for external DRAM. The symbol-based ECC performs quadsymbol correct and multi-symbol detect.

- SECDED ECC of on-chip SRAM buffers within the DMC-520.

- An automated retry of failed read transactions.

- · Write-back of corrected errors.

- To improve containment of faults, the DMC-520 supports:

- Link error protection for the memory interface, including automated hardware recovery for system memory access, training, and other hardware operations.

- Programmable data scrubbing. The DMC-520 periodically detects and corrects data errors in the memory autonomously.

# 2.2 Clocking and resets

The DMC-520 normally operates as one synchronous clock domain between the interconnect and the external DDR interface. However, the programming interface can operate asynchronously to this.

This section shows the clock and reset signals that the DMC-520 requires.

#### Clocks

There are either two or three clock inputs depending on the DFI frequency ratio configuration:

- **clk**. This is the main DMC clock that runs at SDRAM clock frequency. It must run synchronous to, and at the same frequency, as the CHI interface. If the CHI interface is not running at SDRAM clock frequency, then a *Device Source Synchronous Bridge* (DSSB), which is part of the CCN product must be used. When in a 1:1 DFI frequency ratio mode, this clock also serves as the **dfi clk**.

- **dfi\_clk**. This clock port only exists if the DMC is in 1:2 or 1:4 mode. The clock runs the DFI interface and connects to both the DMC and the PHY. It must be edge synchronous to **clk**, and run at half the **clk** frequency if it is in the 1:2 configuration or one quarter the **clk** frequency when in the 1:4 configuration.

- pclk. This can run asynchronously to clk and dfi clk.

#### Reset

Resets must be applied for a minimum duration of 16 clock cycles for each clock domain.

There are two reset inputs. **RESETn** resets both **clk** and **dfi clk** registers and **PRESETn** resets **pclk** registers. The **pclk** domain must be brought out of reset prior to the **clk** and **dfi clk** domains.

\_\_\_\_\_ Note \_\_\_\_\_

- To assert any DMC-520 reset signal, you must set it LOW.

- To perform a DMC-520 reset, you must assert both reset signals.

# Related references

Appendix A Signal Descriptions on page Appx-A-144.

# 2.3 Interfaces

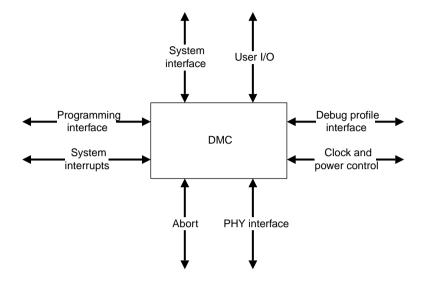

This section describes the interfaces of the DMC-520, as the following figure shows.

Figure 2-2 Interfaces of the DMC-520

This section contains the following subsections:

- 2.3.1 System interface on page 2-25.

- 2.3.2 Programming interface on page 2-25.

- 2.3.3 PHY interface on page 2-25.

- 2.3.4 Profile and debug interface on page 2-26.

- 2.3.5 Low-power clock control interface on page 2-26.

- 2.3.6 Abort interface on page 2-28.

# 2.3.1 System interface

This section describes the function of the System interface.

The System Interface provides protocol conversion between CHI and internal read/write requests. Because CHI is packet-based and a slave node only supports read and write semantics, this translation is straightforward at a transaction level because no transformation function is performed.

# 2.3.2 Programming interface

This section describes the APB3 interface, used for programming the DMC-520.

The AMBA APB3 slave interface allows software to configure the controller and to initialize the memory devices. The APB3 programming interface also provides a means of performing architectural state transitions in addition to querying certain debug and profile information. The interface is a memory-mapped register interface.

# 2.3.3 PHY interface

The PHY interface provides command scheduling and arbitration, including the generation of any required SDRAM prepare commands, for example, ACTIVATE and PRECHARGE.

The PHY interface is compatible with the DDR standards for DDR4 and DDR3 (including DDR3L). It provides:

- Command scheduling and arbitration, including generation of any required SDRAM prepare commands, for example, ACTIVATE or PRECHARGE.

- Automated AUTOREFRESH command generation.

- SDRAM interface link protection including automated retries for failed commands to ensure the correct ordering of those retried commands to SDRAM.

- Automated SDRAM and PHY logic power control.

- · Profile and debug information.

- Support for DFI 1:1, 1:2, and 1:4 frequency ratio modes.

# 2.3.4 Profile and debug interface

This section describes the profile and debug interface in the DMC-520.

The DMC-520 provides programmable features that allow system designers and software developers to fine-tune performance and power settings for their applications. A number of events can be monitored and the statistics used to fine-tune the performance of the controller by statically, or dynamically, altering the programmed state.

The information is made available through output pins that the system integrator must connect to an external monitoring unit.

The following events are monitored:

- · Channel utilization.

- Channel and chip power state information.

- Bank utilization.

- · Bank distribution.

- Activation rate.

- Read and write turnaround frequency.

- Read and write buffer fill status and the frequency of full events.

- Thresholding asserting back pressure.

- Arbitration decisions made where QoS is prioritized over efficiency.

- Read-Modify-Write (RMW) frequency.

- · Timeouts and deadline events.

Each event is implemented as a pair of signals, VALID, and either PAYLOAD or a permanently valid PAYLOAD signal.

The Profile and Debug event interface can be connected to a generic event counter block, where any combination of the signals can be logged and tracked, depending on your system requirements.

#### 2.3.5 Low-power clock control interface

This section describes the clock requirements for the DMC-520.

The DMC-520 provides a low-power control interface using the Q-Channel protocol. This is used to place the DMC into its low-power state, in which state the clock can be removed. The system can use the APB interface to put the DMC into its low-power state, and take it out of its low-power state.

SDRAM provides a number of power-saving states, as distinct from those of the DMC-520:

- 1. Idle-ready.

- 2. Clock stop.

- 3. Active power down.

- 4. Precharge power down.

- 5. Self-Refresh (SR).

- 6. Maximum Power Down (MPD) for DDR4.

All states prohibit commands apart from Idle-ready. From states 2-6, the energy saving increases, but so does the exit latency from that state. Some SDRAMs do not support dynamic clock stopping or MPD. Specific commands, together with the clock-enable **CKE** signal, are used to control states 2-5. Individual **CKE** pins are required for each chip that requires separate power control.

The features of the DMC-520 include:

- Separate clock and CKE controls for each chip select, with a set of multiplexer options to support standard DIMM configurations.

- Automated power control of SDRAM power modes based on an enable and timer. See 3.3.8 low power control next on page 3-46.

- Clock stop functionality that differs between memory devices. A programmable register controls this behavior. See 3.3.8 low power control next on page 3-46.

- Auto powerdown with minimal or no latency penalty on wakeup.

- Auto self-refresh functionality. The time delay before entry to self-refresh can be timed in refresh periods. When in self-refresh, a chip only comes out of self-refresh in response to system commands.

- Software-controlled low-power entry through the APB programming interface.

- A Q-Channel interface for hardware to control entry into the SR states. See *Q-Channel interface* on page 2-27.

| • | A separate | low-power | interface to | allow | clock | stopping | of the | progran | nming | interface |

|---|------------|-----------|--------------|-------|-------|----------|--------|---------|-------|-----------|

|---|------------|-----------|--------------|-------|-------|----------|--------|---------|-------|-----------|

| Note |             |      |     |      |     |     |

|------|-------------|------|-----|------|-----|-----|

| ant. | D1 (C 520 1 | . 11 | 1.1 | .1 1 | C 1 | 1.1 |

The DMC-520 does not allow multiple methods of low-power entry, either software or hardware, that are used at the same time. This is a restriction imposed on the system design.

The PHY logic consumes power in standby mode. If the controller is using SDRAM low-power modes, then it indicates to the PHY that it can power down. The wakeup value that the DMC signals to the PHY with the powerdown request determines the level of power state that the PHY enters. The wakeup value is determined from a programmed value that is associated with each SDRAM power-saving state. These states are:

- · Configuration.

- Idle

- Power-down.

- · Self-refresh.

- MPD.

| - Note |  |

|--------|--|

| 11016  |  |

The DMC can also indicate that the PHY must power down in the following ways:

- As a direct command from software, with a software-defined wakeup value.

- As part of a Q-Channel sequence, with a tie-off defined wakeup value.

# **Q-Channel interface**

The DMC has a Q-Channel interface that allows an external power controller to place the DMC into a low-power state.

It is a standard Q-Channel interface as defined in the ARM® Low Power Interface Specification, Q-Channel and P-Channel Interfaces using the following 4 signals.

- qactive.

- qreqn.

- qacceptn.

- qdeny.

When the DMC receives a request, it puts the DRAM into self\_refresh before asserting **qacceptn** to accept the request that indicates the clk can be stopped.

DMC denies requests to power down using the Q-Channel when geardown\_mode is enabled. In this case low-power mode can still be entered using the APB interface.

There is a separate Q-Channel interface for the **pclk** using the following signals:

- qactive apb.

- · qreqn apb.

- · qacceptn apb.

- · qdeny apb.

The DMC never denies a request to power down the APB clock although it might be delayed based on APB activity.

\_\_\_\_\_ Note \_\_\_\_\_

These two interfaces are interrelated and a change on one can cause **qactive** on the other to be asserted. If this occurs then the powerup request must be responded to in a timely fashion to allow the request to be serviced.

See ARM® Low Power Interface Specification, Q-Channel and P-Channel Interfaces.

# 2.3.6 Abort interface

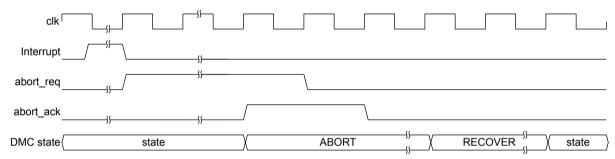

When a fault is detected on the DFI interface, it causes repeated retries of commands on the memory interface. The abort interface is a 4-phase request and acknowledge handshake that the DMC can use to recover from a livelock caused by a DRAM failure or a PHY failure.

The following diagram shows the request, acknowledge handshake.

Figure 2-3 Abort interface timing diagram

The system can issue an abort at any time, which puts the DMC into the ABORT architectural state. Software must then restore the memory state. All current system transactions are retried after software restores the memory state and puts the DMC back into the Ready state.

# 2.4 Constraints and limitations of use

The constraints and limitations of the DMC-520 depend on the SDRAMs used, and the interoperability within the PHYs. This, in turn, depends on the *DDR Physical Interface* (DFI) parameters.

The SDRAMs supported by the DMC-520 are:

- Double Data Rate 3 (DDR3) SDRAM.

- Low-voltage DDR3 SDRAM.

- Double Data Rate 4 (DDR4) SDRAM.

| ———Note                                  |                    |                |               |     |

|------------------------------------------|--------------------|----------------|---------------|-----|

| These devices are described in the JEDEC | specifications the | hat are global | standards for | the |

The DIMMs supported by the DMC-520 are:

DDR3 UDIMM.

microelectronics industry.

- DDR3 RDIMM.

- DDR4 UDIMM.

- DDR4 RDIMM.

- DDR4 LRDIMM.

- DDR4 3DS. DIMMs utilizing 3DS parts are supported.

# Chapter 3 **Programmers Model**

This chapter describes the programmers model of the DMC-520.

It contains the following sections:

- 3.1 About this programmers model on page 3-31.

- 3.2 Register summary on page 3-32.

- 3.3 Register descriptions on page 3-44.

# 3.1 About this programmers model

The following information applies to the dmc520 registers:

- The base address is not fixed, and can be different for any particular system implementation. The offset of each register from the base address is fixed.

- Do not attempt to access reserved or unused address locations. Attempting to access these locations can result in Unpredictable behavior.

- Unless otherwise stated in the accompanying text:

- Do not modify undefined register bits.

- Ignore undefined register bits on reads.

- All register bits are reset to the reset value specified in the 3.2 Register summary on page 3-32

- Access type is described as follows:

**RW** Read and write.

**RO** Read only.

**WO** Write only.

# 3.2 Register summary

The following table shows the registers in offset order from the base memory address.

Table 3-1 Register summary

| Offset | Name                               | Туре | Reset      | Width | Description                                               |

|--------|------------------------------------|------|------------|-------|-----------------------------------------------------------|

| 0x000  | memc_status                        | RO   | 0x00000000 | 32    | 3.3.1 memc_status on page 3-44                            |

| 0x004  | memc_config                        | RO   | 0x00000000 | 32    | 3.3.2 memc_config on page 3-44                            |

| 0x008  | memc_cmd                           | WO   | 0x00000000 | 32    | 3.3.3 memc_cmd on page 3-44                               |

| 0x010  | address_control_next               | RW   | 0x00030202 | 32    | 3.3.4 address_control_next on page 3-45                   |

| 0x014  | decode_control_next                | RW   | 0x00000000 | 32    | 3.3.5 decode_control_next on page 3-45                    |

| 0x018  | format_control                     | RW   | 0x22000213 | 32    | 3.3.6 format_control on page 3-45                         |

| 0x01C  | address_map_next                   | RW   | 0x00000000 | 32    | 3.3.7 address_map_next on page 3-45                       |

| 0x020  | low_power_control_next             | RW   | 0x00000020 | 32    | 3.3.8 low_power_control_next on page 3-46                 |

| 0x028  | turnaround_control_next            | RW   | 0x0F0F0F0F | 32    | 3.3.9 turnaround_control_next on page 3-46                |

| 0x02C  | hit_turnaround_control_next        | RW   | 0x08909FBF | 32    | 3.3.10 hit_turnaround_control_next on page 3-46           |

| 0x030  | qos_class_control_next             | RW   | 0x00000FC8 | 32    | 3.3.11 qos_class_control_next on page 3-47                |

| 0x034  | escalation_control_next            | RW   | 0x00080F03 | 32    | 3.3.12 escalation_control_next on page 3-47               |

| 0x038  | qv_control_31_00_next              | RW   | 0x76543210 | 32    | 3.3.13 qv_control_31_00_next on page 3-47                 |

| 0x03C  | qv_control_63_32_next              | RW   | 0xFEDCBA98 | 32    | 3.3.14 qv_control_63_32_next on page 3-47                 |

| 0x040  | rt_control_31_00_next              | RW   | 0x00000000 | 32    | 3.3.15 rt_control_31_00_next on page 3-48                 |

| 0x044  | rt_control_63_32_next              | RW   | 0x00000000 | 32    | 3.3.16 rt_control_63_32_next on page 3-48                 |

| 0x048  | timeout_control_next               | RW   | 0x00000001 | 32    | 3.3.17 timeout_control_next on page 3-48                  |

| 0x04C  | credit_control_next                | RW   | 0x00000F03 | 32    | 3.3.18 credit_control_next on page 3-49                   |

| 0x050  | write_priority_control_31_00_next  | RW   | 0x00000000 | 32    | 3.3.19 write_priority_control_31_00_next on page 3-49     |

| 0x054  | write_priority_control_63_32_next  | RW   | 0x00000000 | 32    | 3.3.20 write_priority_control_63_32_next on page 3-49     |

| 0x060  | queue_threshold_control_31_00_next | RW   | 0x00000000 | 32    | 3.3.21 queue_threshold_control_31_00_next on page 3-49    |

| 0x064  | queue_threshold_control_63_32_next | RW   | 0x00000000 | 32    | 3.3.22 queue_threshold_control_63_32_next<br>on page 3-50 |

| 0x078  | memory_address_max_31_00_next      | RW   | 0x00000010 | 32    | 3.3.23 memory_address_max_31_00_next on page 3-50         |

| 0x07C  | memory_address_max_43_32_next      | RW   | 0x00000000 | 32    | 3.3.24 memory_address_max_43_32_next on page 3-50         |

| 0x080  | access_address_min0_31_00_next     | RW   | 0x00000000 | 32    | 3.3.25 access_address_min0_31_00_next<br>on page 3-51     |

| 0x084  | access_address_min0_43_32_next     | RW   | 0x00000000 | 32    | 3.3.26 access_address_min0_43_32_next on page 3-51        |

Table 3-1 Register summary (continued)

| Offset | Name                           | Type | Reset      | Width | Description                                           |

|--------|--------------------------------|------|------------|-------|-------------------------------------------------------|

| 0x088  | access_address_max0_31_00_next | RW   | 0x00000000 | 32    | 3.3.27 access_address_max0_31_00_next on page 3-51    |

| 0x08C  | access_address_max0_43_32_next | RW   | 0x00000000 | 32    | 3.3.28 access_address_max0_43_32_next on page 3-51    |

| 0x090  | access_address_min1_31_00_next | RW   | 0x00000000 | 32    | 3.3.29 access_address_min1_31_00_next on page 3-52    |

| 0x094  | access_address_min1_43_32_next | RW   | 0x00000000 | 32    | 3.3.30 access_address_min1_43_32_next on page 3-52    |

| 0x098  | access_address_max1_31_00_next | RW   | 0x00000000 | 32    | 3.3.31 access_address_max1_31_00_next on page 3-52    |

| 0x09C  | access_address_max1_43_32_next | RW   | 0x00000000 | 32    | 3.3.32 access_address_max1_43_32_next on page 3-53    |

| 0x0A0  | access_address_min2_31_00_next | RW   | 0x00000000 | 32    | 3.3.33 access_address_min2_31_00_next on page 3-53    |

| 0x0A4  | access_address_min2_43_32_next | RW   | 0x00000000 | 32    | 3.3.34 access_address_min2_43_32_next on page 3-53    |

| 0x0A8  | access_address_max2_31_00_next | RW   | 0x00000000 | 32    | 3.3.35 access_address_max2_31_00_next on page 3-53    |

| 0x0AC  | access_address_max2_43_32_next | RW   | 0x00000000 | 32    | 3.3.36 access_address_max2_43_32_next<br>on page 3-54 |

| 0x0B0  | access_address_min3_31_00_next | RW   | 0x00000000 | 32    | 3.3.37 access_address_min3_31_00_next on page 3-54    |

| 0x0B4  | access_address_min3_43_32_next | RW   | 0×00000000 | 32    | 3.3.38 access_address_min3_43_32_next<br>on page 3-54 |

| 0x0B8  | access_address_max3_31_00_next | RW   | 0x00000000 | 32    | 3.3.39 access_address_max3_31_00_next on page 3-55    |

| 0x0BC  | access_address_max3_43_32_next | RW   | 0×00000000 | 32    | 3.3.40 access_address_max3_43_32_next on page 3-55    |

| 0x0C0  | access_address_min4_31_00_next | RW   | 0x00000000 | 32    | 3.3.41 access_address_min4_31_00_next on page 3-55    |

| 0x0C4  | access_address_min4_43_32_next | RW   | 0x00000000 | 32    | 3.3.42 access_address_min4_43_32_next<br>on page 3-55 |

| 0x0C8  | access_address_max4_31_00_next | RW   | 0x00000000 | 32    | 3.3.43 access_address_max4_31_00_next<br>on page 3-56 |

| 0x0CC  | access_address_max4_43_32_next | RW   | 0x00000000 | 32    | 3.3.44 access_address_max4_43_32_next<br>on page 3-56 |

| 0x0D0  | access_address_min5_31_00_next | RW   | 0x00000000 | 32    | 3.3.45 access_address_min5_31_00_next on page 3-56    |

| 0x0D4  | access_address_min5_43_32_next | RW   | 0x00000000 | 32    | 3.3.46 access_address_min5_43_32_next<br>on page 3-57 |

| 0x0D8  | access_address_max5_31_00_next | RW   | 0x00000000 | 32    | 3.3.47 access_address_max5_31_00_next on page 3-57    |

Table 3-1 Register summary (continued)

| Offset | Name                           | Type | Reset      | Width | Description                                           |

|--------|--------------------------------|------|------------|-------|-------------------------------------------------------|

| 0x0DC  | access_address_max5_43_32_next | RW   | 0x00000000 | 32    | 3.3.48 access_address_max5_43_32_next on page 3-57    |

| 0x0E0  | access_address_min6_31_00_next | RW   | 0x00000000 | 32    | 3.3.49 access_address_min6_31_00_next on page 3-57    |

| 0x0E4  | access_address_min6_43_32_next | RW   | 0x00000000 | 32    | 3.3.50 access_address_min6_43_32_next on page 3-58    |

| 0x0E8  | access_address_max6_31_00_next | RW   | 0x00000000 | 32    | 3.3.51 access_address_max6_31_00_next on page 3-58    |

| 0x0EC  | access_address_max6_43_32_next | RW   | 0x00000000 | 32    | 3.3.52 access_address_max6_43_32_next on page 3-58    |

| 0x0F0  | access_address_min7_31_00_next | RW   | 0x00000000 | 32    | 3.3.53 access_address_min7_31_00_next on page 3-59    |

| 0x0F4  | access_address_min7_43_32_next | RW   | 0x00000000 | 32    | 3.3.54 access_address_min7_43_32_next on page 3-59    |

| 0x0F8  | access_address_max7_31_00_next | RW   | 0x00000000 | 32    | 3.3.55 access_address_max7_31_00_next on page 3-59    |

| 0x0FC  | access_address_max7_43_32_next | RW   | 0x00000000 | 32    | 3.3.56 access_address_max7_43_32_next on page 3-59    |

| 0×100  | channel_status                 | RO   | 0x00000003 | 32    | 3.3.57 channel_status on page 3-60                    |

| 0×108  | direct_addr                    | RW   | 0x00000000 | 32    | 3.3.58 direct_addr on page 3-60                       |

| 0x10C  | direct_cmd                     | WO   | 0x00000000 | 32    | 3.3.59 direct_cmd on page 3-60                        |

| 0x110  | dci_replay_type_next           | RW   | 0x00000002 | 32    | 3.3.60 dci_replay_type_next on page 3-61              |

| 0x118  | dci_strb                       | RW   | 0x0000000F | 32    | 3.3.61 dci_strb on page 3-61                          |

| 0x11C  | dci_data                       | RW   | 0x00000000 | 32    | 3.3.62 dci_data on page 3-61                          |

| 0x120  | refresh_control_next           | RW   | 0x00000000 | 32    | 3.3.63 refresh_control_next on page 3-61              |

| 0x128  | memory_type_next               | RW   | 0x00000101 | 32    | 3.3.64 memory_type_next on page 3-62                  |

| 0x130  | feature_config                 | RW   | 0x000000F0 | 32    | 3.3.65 feature_config on page 3-62                    |

| 0x138  | nibble_failed_031_000          | RW   | 0x00000000 | 32    | 3.3.66 nibble_failed_031_000 on page 3-62             |

| 0x13C  | nibble_failed_063_032          | RW   | 0x00000000 | 32    | 3.3.67 nibble_failed_063_032 on page 3-63             |

| 0x140  | nibble_failed_095_064          | RW   | 0x00000000 | 32    | 3.3.68 nibble_failed_095_064 on page 3-63             |

| 0x144  | nibble_failed_127_096          | RW   | 0x00000000 | 32    | 3.3.69 nibble_failed_127_096 on page 3-63             |

| 0x148  | queue_allocate_control_031_000 | RW   | 0xFFFFFFF  | 32    | 3.3.70 queue_allocate_control_031_000 on page 3-63    |

| 0x14C  | queue_allocate_control_063_032 | RW   | 0xFFFFFFF  | 32    | 3.3.71 queue_allocate_control_063_032<br>on page 3-64 |

| 0x150  | queue_allocate_control_095_064 | RW   | 0xFFFFFFF  | 32    | 3.3.72 queue_allocate_control_095_064 on page 3-64    |

| 0x154  | queue_allocate_control_127_096 | RW   | 0xFFFFFFF  | 32    | 3.3.73 queue_allocate_control_127_096 on page 3-64    |

Table 3-1 Register summary (continued)

| Offset | Name                    | Туре | Reset      | Width | Description                                  |

|--------|-------------------------|------|------------|-------|----------------------------------------------|

| 0x158  | ecc_errc_count_31_00    | RW   | 0x00000000 | 32    | 3.3.74 ecc_errc_count_31_00 on page 3-65     |

| 0x15C  | ecc_errc_count_63_32    | RW   | 0x00000000 | 32    | 3.3.75 ecc_errc_count_63_32 on page 3-65     |

| 0x160  | ecc_errd_count_31_00    | RW   | 0x00000000 | 32    | 3.3.76 ecc_errd_count_31_00 on page 3-65     |

| 0x164  | ecc_errd_count_63_32    | RW   | 0x00000000 | 32    | 3.3.77 ecc_errd_count_63_32 on page 3-66     |

| 0x168  | ram_err_count           | RW   | 0x00000000 | 32    | 3.3.78 ram_err_count on page 3-66            |

| 0x16C  | link_err_count          | RW   | 0x00000000 | 32    | 3.3.79 link_err_count on page 3-66           |

| 0x170  | scrub_control0_next     | RW   | 0x1F000000 | 32    | 3.3.80 scrub_control0_next on page 3-66      |

| 0x174  | scrub_address_min0_next | RW   | 0x00000000 | 32    | 3.3.81 scrub_address_min0_next on page 3-67  |

| 0x178  | scrub_address_max0_next | RW   | 0x00000000 | 32    | 3.3.82 scrub_address_max0_next on page 3-67  |

| 0x180  | scrub_control1_next     | RW   | 0x1F000000 | 32    | 3.3.83 scrub_control1_next on page 3-67      |

| 0x184  | scrub_address_min1_next | RW   | 0x00000000 | 32    | 3.3.84 scrub_address_min1_next on page 3-68  |

| 0x188  | scrub_address_max1_next | RW   | 0x00000000 | 32    | 3.3.85 scrub_address_max1_next on page 3-68  |

| 0x190  | scrub_control2_next     | RW   | 0x1F000000 | 32    | 3.3.86 scrub_control2_next on page 3-68      |

| 0x194  | scrub_address_min2_next | RW   | 0x00000000 | 32    | 3.3.87 scrub_address_min2_next on page 3-68  |

| 0x198  | scrub_address_max2_next | RW   | 0x00000000 | 32    | 3.3.88 scrub_address_max2_next on page 3-69  |

| 0x1A0  | scrub_control3_next     | RW   | 0x1F000000 | 32    | 3.3.89 scrub_control3_next on page 3-69      |

| 0x1A4  | scrub_address_min3_next | RW   | 0x00000000 | 32    | 3.3.90 scrub_address_min3_next on page 3-69  |

| 0x1A8  | scrub_address_max3_next | RW   | 0x00000000 | 32    | 3.3.91 scrub_address_max3_next on page 3-70  |

| 0x1B0  | scrub_control4_next     | RW   | 0x1F000000 | 32    | 3.3.92 scrub_control4_next on page 3-70      |

| 0x1B4  | scrub_address_min4_next | RW   | 0x00000000 | 32    | 3.3.93 scrub_address_min4_next on page 3-70  |

| 0x1B8  | scrub_address_max4_next | RW   | 0x00000000 | 32    | 3.3.94 scrub_address_max4_next on page 3-70  |

| 0x1C0  | scrub_control5_next     | RW   | 0x1F000000 | 32    | 3.3.95 scrub_control5_next on page 3-71      |

| 0x1C4  | scrub_address_min5_next | RW   | 0x00000000 | 32    | 3.3.96 scrub_address_min5_next on page 3-71  |

| 0x1C8  | scrub_address_max5_next | RW   | 0x00000000 | 32    | 3.3.97 scrub_address_max5_next on page 3-71  |

| 0x1D0  | scrub_control6_next     | RW   | 0x1F000000 | 32    | 3.3.98 scrub_control6_next on page 3-72      |

| 0x1D4  | scrub_address_min6_next | RW   | 0x00000000 | 32    | 3.3.99 scrub_address_min6_next on page 3-72  |

| 0x1D8  | scrub_address_max6_next | RW   | 0x00000000 | 32    | 3.3.100 scrub_address_max6_next on page 3-72 |

| 0x1E0  | scrub_control7_next     | RW   | 0x1F000000 | 32    | 3.3.101 scrub_control7_next on page 3-72     |

| 0x1E4  | scrub_address_min7_next | RW   | 0x00000000 | 32    | 3.3.102 scrub_address_min7_next on page 3-73 |

| 0x1E8  | scrub_address_max7_next | RW   | 0x00000000 | 32    | 3.3.103 scrub_address_max7_next on page 3-73 |

| 0x1F0  | feature_control_next    | RW   | 0x0AA0000  | 32    | 3.3.104 feature_control_next on page 3-73    |

| 0x1F4  | mux_control_next        | RW   | 0x00000000 | 32    | 3.3.105 mux_control_next on page 3-74        |

| 0x1F8  | rank_remap_control_next | RW   | 0x76543210 | 32    | 3.3.106 rank_remap_control_next on page 3-74 |

| 0x1FC  | scrub_control_next      | RW   | 0x00001F00 | 32    | 3.3.107 scrub_control_next on page 3-74      |

| 0x200  | t_refi_next             | RW   | 0x00090100 | 32    | 3.3.108 t_refi_next on page 3-74             |

Table 3-1 Register summary (continued)

| Offset | Name               | Туре | Reset      | Width | Description                                   |

|--------|--------------------|------|------------|-------|-----------------------------------------------|

| 0x204  | t_rfc_next         | RW   | 0x00008C23 | 32    | 3.3.109 t_rfc_next on page 3-75               |

| 0x208  | t_mrr_next         | RW   | 0x00000002 | 32    | 3.3.110 t_mrr_next on page 3-75               |

| 0x20C  | t_mrw_next         | RW   | 0x0000000C | 32    | 3.3.111 t_mrw_next on page 3-75               |

| 0x210  | t_rdpden_next      | RW   | 0x0000000A | 32    | 3.3.112 t_rdpden_next on page 3-76            |

| 0x218  | t_rcd_next         | RW   | 0x00000005 | 32    | 3.3.113 t_rcd_next on page 3-76               |

| 0x21C  | t_ras_next         | RW   | 0x0000000E | 32    | 3.3.114 t_ras_next on page 3-76               |

| 0x220  | t_rp_next          | RW   | 0x00000005 | 32    | <i>3.3.115 t_rp_next</i> on page 3-77         |

| 0x224  | t_rpall_next       | RW   | 0x00000005 | 32    | 3.3.116 t_rpall_next on page 3-77             |

| 0x228  | t_rrd_next         | RW   | 0x00000404 | 32    | 3.3.117 t_rrd_next on page 3-77               |

| 0x22C  | t_act_window_next  | RW   | 0x03560014 | 32    | <i>3.3.118 t_act_window_next</i> on page 3-77 |

| 0x234  | t_rtr_next         | RW   | 0x00060404 | 32    | <i>3.3.119 t_rtr_next</i> on page 3-78        |

| 0x238  | t_rtw_next         | RW   | 0x00060606 | 32    | 3.3.120 t_rtw_next on page 3-78               |

| 0x23C  | t_rtp_next         | RW   | 0x00000004 | 32    | 3.3.121 t_rtp_next on page 3-78               |

| 0x244  | t_wr_next          | RW   | 0x00000005 | 32    | 3.3.122 t_wr_next on page 3-79                |

| 0x248  | t_wtr_next         | RW   | 0x00040505 | 32    | 3.3.123 t_wtr_next on page 3-79               |

| 0x24C  | t_wtw_next         | RW   | 0x00060404 | 32    | 3.3.124 t_wtw_next on page 3-79               |

| 0x254  | t_xmpd_next        | RW   | 0x000003FF | 32    | 3.3.125 t_xmpd_next on page 3-80              |

| 0x258  | t_ep_next          | RW   | 0x00000002 | 32    | 3.3.126 t_ep_next on page 3-80                |

| 0x25C  | t_xp_next          | RW   | 0x00060002 | 32    | 3.3.127 t_xp_next on page 3-80                |

| 0x260  | t_esr_next         | RW   | 0x0000000E | 32    | 3.3.128 t_esr_next on page 3-80               |

| 0x264  | t_xsr_next         | RW   | 0x05120100 | 32    | 3.3.129 t_xsr_next on page 3-81               |

| 0x268  | t_esrck_next       | RW   | 0x00000005 | 32    | <i>3.3.130 t_esrck_next</i> on page 3-81      |

| 0x26C  | t_ckxsr_next       | RW   | 0x00000001 | 32    | 3.3.131 t_ckxsr_next on page 3-81             |

| 0x270  | t_cmd_next         | RW   | 0x00000000 | 32    | 3.3.132 t_cmd_next on page 3-82               |

| 0x274  | t_parity_next      | RW   | 0x00000900 | 32    | 3.3.133 t_parity_next on page 3-82            |

| 0x278  | t_zqcs_next        | RW   | 0x00000040 | 32    | 3.3.134 t_zqcs_next on page 3-82              |

| 0x300  | t_rddata_en_next   | RW   | 0x00000001 | 32    | 3.3.135 t_rddata_en_next on page 3-83         |

| 0x304  | t_phyrdlat_next    | RW   | 0x00000000 | 32    | 3.3.136 t_phyrdlat_next on page 3-83          |

| 0x308  | t_phywrlat_next    | RW   | 0x00000001 | 32    | 3.3.137 t_phywrlat_next on page 3-83          |

| 0x310  | rdlvl_control_next | RW   | 0x00001080 | 32    | 3.3.138 rdlvl_control_next on page 3-83       |

| 0x314  | rdlvl_mrs_next     | RW   | 0x00000004 | 32    | 3.3.139 rdlvl_mrs_next on page 3-84           |

| 0x318  | t_rdlvl_en_next    | RW   | 0x00000000 | 32    | 3.3.140 t_rdlvl_en_next on page 3-84          |

| 0x31C  | t_rdlvl_rr_next    | RW   | 0x00000000 | 32    | 3.3.141 t_rdlvl_rr_next on page 3-84          |

| 0x320  | wrlvl_control_next | RW   | 0x00001000 | 32    | 3.3.142 wrlvl_control_next on page 3-85       |

| 0x324  | wrlvl_mrs_next     | RW   | 0x00000086 | 32    | 3.3.143 wrlvl_mrs_next on page 3-85           |

Table 3-1 Register summary (continued)

| Offset | Name                         | Type | Reset      | Width | Description                                          |

|--------|------------------------------|------|------------|-------|------------------------------------------------------|

| 0x328  | t_wrlvl_en_next              | RW   | 0x00000000 | 32    | 3.3.144 t_wrlvl_en_next on page 3-85                 |

| 0x32C  | t_wrlvl_ww_next              | RW   | 0x00000000 | 32    | 3.3.145 t_wrlvl_ww_next on page 3-86                 |

| 0x348  | phy_power_control_next       | RW   | 0x00000000 | 32    | 3.3.146 phy_power_control_next on page 3-86          |

| 0x34C  | t_lpresp_next                | RW   | 0x00000000 | 32    | 3.3.147 t_lpresp_next on page 3-86                   |

| 0x350  | phy_update_control_next      | RW   | 0x0FE00000 | 32    | 3.3.148 phy_update_control_next on page 3-87         |

| 0x358  | odt_timing_next              | RW   | 0x06000600 | 32    | 3.3.149 odt_timing_next on page 3-87                 |

| 0x360  | odt_wr_control_31_00_next    | RW   | 0x08040201 | 32    | 3.3.150 odt_wr_control_31_00_next on page 3-87       |

| 0x364  | odt_wr_control_63_32_next    | RW   | 0x80402010 | 32    | 3.3.151 odt_wr_control_63_32_next on page 3-87       |

| 0x368  | odt_rd_control_31_00_next    | RW   | 0x00000000 | 32    | 3.3.152 odt_rd_control_31_00_next on page 3-88       |

| 0x36C  | odt_rd_control_63_32_next    | RW   | 0x00000000 | 32    | 3.3.153 odt_rd_control_63_32_next on page 3-88       |

| 0x370  | temperature_readout          | RO   | 0x00000000 | 32    | 3.3.154 temperature_readout on page 3-88             |

| 0x378  | training_status              | RO   | 0x00000000 | 32    | 3.3.155 training_status on page 3-89                 |

| 0x37C  | update_status                | RO   | 0x00000000 | 32    | 3.3.156 update_status on page 3-89                   |

| 0x380  | dq_map_control_15_00_next    | RW   | 0x00000000 | 32    | 3.3.157 dq_map_control_15_00_next on page 3-89       |

| 0x384  | dq_map_control_31_16_next    | RW   | 0x00000000 | 32    | 3.3.158 dq_map_control_31_16_next on page 3-89       |

| 0x388  | dq_map_control_47_32_next    | RW   | 0x00000000 | 32    | 3.3.159 dq_map_control_47_32_next on page 3-90       |

| 0x38C  | dq_map_control_63_48_next    | RW   | 0x00000000 | 32    | 3.3.160 dq_map_control_63_48_next on page 3-90       |

| 0x390  | dq_map_control_71_64_next    | RW   | 0x00000000 | 32    | 3.3.161 dq_map_control_71_64_next on page 3-90       |

| 0x398  | rank_status                  | RO   | 0x00000000 | 32    | 3.3.162 rank_status on page 3-91                     |

| 0x39C  | mode_change_status           | RO   | 0x00000000 | 32    | 3.3.163 mode_change_status on page 3-91              |

| 0x400  | user_status                  | RO   | 0x00000000 | 32    | 3.3.164 user_status on page 3-91                     |

| 0x408  | user_config0_next            | RW   | 0x00000000 | 32    | 3.3.165 user_config0_next on page 3-92               |

| 0x40C  | user_config1_next            | RW   | 0x00000000 | 32    | 3.3.166 user_config1_next on page 3-92               |

| 0x410  | user_config2                 | RW   | 0x00000000 | 32    | 3.3.167 user_config2 on page 3-92                    |

| 0x414  | user_config3                 | RW   | 0x00000000 | 32    | 3.3.168 user_config3 on page 3-92                    |

| 0x500  | interrupt_control            | RW   | 0x00000000 | 32    | 3.3.169 interrupt_control on page 3-93               |

| 0x508  | interrupt_clr                | WO   | 0x00000000 | 32    | <i>3.3.170 interrupt_clr</i> on page 3-93            |

| 0x510  | interrupt_status             | RO   | 0x00000000 | 32    | 3.3.171 interrupt_status on page 3-93                |

| 0x518  | ram_ecc_errc_int_info_31_00  | RO   | 0x00000000 | 32    | 3.3.172 ram_ecc_errc_int_info_31_00 on page 3-94     |

| 0x51C  | ram_ecc_errc_int_info_63_32  | RO   | 0x00000000 | 32    | 3.3.173 ram_ecc_errc_int_info_63_32 on page 3-94     |

| 0x520  | ram_ecc_errd_int_info_31_00  | RO   | 0x00000000 | 32    | 3.3.174 ram_ecc_errd_int_info_31_00 on page 3-94     |

| 0x524  | ram_ecc_errd_int_info_63_32  | RO   | 0x00000000 | 32    | 3.3.175 ram_ecc_errd_int_info_63_32 on page 3-94     |

| 0x528  | dram_ecc_errc_int_info_31_00 | RO   | 0x00000000 | 32    | 3.3.176 dram_ecc_errc_int_info_31_00<br>on page 3-95 |

Table 3-1 Register summary (continued)

| Offset | Name                             | Type | Reset      | Width | Description                                             |

|--------|----------------------------------|------|------------|-------|---------------------------------------------------------|

| 0x52C  | dram_ecc_errc_int_info_63_32     | RO   | 0x00000000 | 32    | 3.3.177 dram_ecc_errc_int_info_63_32<br>on page 3-95    |

| 0x530  | dram_ecc_errd_int_info_31_00     | RO   | 0x00000000 | 32    | 3.3.178 dram_ecc_errd_int_info_31_00<br>on page 3-95    |

| 0x534  | dram_ecc_errd_int_info_63_32     | RO   | 0x00000000 | 32    | 3.3.179 dram_ecc_errd_int_info_63_32<br>on page 3-96    |

| 0x538  | failed_access_int_info_31_00     | RO   | 0x00000000 | 32    | 3.3.180 failed_access_int_info_31_00 on page 3-96       |

| 0x53C  | failed_access_int_info_63_32     | RO   | 0x00000000 | 32    | 3.3.181 failed_access_int_info_63_32 on page 3-96       |

| 0x540  | failed_prog_int_info_31_00       | RO   | 0x00000000 | 32    | 3.3.182 failed_prog_int_info_31_00 on page 3-96         |

| 0x544  | failed_prog_int_info_63_32       | RO   | 0x00000000 | 32    | 3.3.183 failed_prog_int_info_63_32 on page 3-97         |

| 0x548  | link_err_int_info_31_00          | RO   | 0x00000000 | 32    | 3.3.184 link_err_int_info_31_00 on page 3-97            |

| 0x54C  | link_err_int_info_63_32          | RO   | 0x00000000 | 32    | 3.3.185 link_err_int_info_63_32 on page 3-97            |

| 0x550  | arch_fsm_int_info_31_00          | RO   | 0x00000000 | 32    | 3.3.186 arch_fsm_int_info_31_00 on page 3-98            |

| 0x554  | arch_fsm_int_info_63_32          | RO   | 0x00000000 | 32    | 3.3.187 arch_fsm_int_info_63_32 on page 3-98            |

| 0×E00  | integ_cfg                        | RW   | 0x00000000 | 32    | 3.3.188 integ_cfg on page 3-98                          |

| 0xE08  | integ_outputs                    | WO   | 0x00000000 | 32    | 3.3.189 integ_outputs on page 3-98                      |

| 0x1010 | address_control_now              | RO   | 0x00030202 | 32    | 3.3.190 address_control_now on page 3-99                |

| 0x1014 | decode_control_now               | RO   | 0x00000000 | 32    | 3.3.191 decode_control_now on page 3-99                 |

| 0x101C | address_map_now                  | RO   | 0x00000000 | 32    | 3.3.192 address_map_now on page 3-99                    |

| 0x1020 | low_power_control_now            | RO   | 0x00000020 | 32    | 3.3.193 low_power_control_now on page 3-100             |

| 0x1028 | turnaround_control_now           | RO   | 0x0F0F0F0F | 32    | 3.3.194 turnaround_control_now on page 3-100            |

| 0x102C | hit_turnaround_control_now       | RO   | 0x08909FBF | 32    | 3.3.195 hit_turnaround_control_now on page 3-100        |

| 0x1030 | qos_class_control_now            | RO   | 0x00000FC8 | 32    | 3.3.196 qos_class_control_now on page 3-101             |

| 0x1034 | escalation_control_now           | RO   | 0x00080F03 | 32    | 3.3.197 escalation_control_now on page 3-101            |

| 0x1038 | qv_control_31_00_now             | RO   | 0x76543210 | 32    | 3.3.198 qv_control_31_00_now on page 3-101              |

| 0x103C | qv_control_63_32_now             | RO   | 0xFEDCBA98 | 32    | 3.3.199 qv_control_63_32_now on page 3-101              |

| 0x1040 | rt_control_31_00_now             | RO   | 0x00000000 | 32    | 3.3.200 rt_control_31_00_now on page 3-102              |

| 0x1044 | rt_control_63_32_now             | RO   | 0x00000000 | 32    | 3.3.201 rt_control_63_32_now on page 3-102              |

| 0x1048 | timeout_control_now              | RO   | 0x00000001 | 32    | 3.3.202 timeout_control_now on page 3-102               |

| 0x104C | credit_control_now               | RO   | 0x00000F03 | 32    | 3.3.203 credit_control_now on page 3-103                |

| 0x1050 | write_priority_control_31_00_now | RO   | 0x00000000 | 32    | 3.3.204 write_priority_control_31_00_now on page 3-103  |

| 0x1054 | write_priority_control_63_32_now | RO   | 0x00000000 | 32    | 3.3.205 write_priority_control_63_32_now on page 3-103  |

| 0x1060 | queue_threshold_control_31_00_no | RO   | 0x00000000 | 32    | 3.3.206 queue_threshold_control_31_00_now on page 3-104 |

Table 3-1 Register summary (continued)

| Offset | Name                               | Type | Reset      | Width | Description                                             |

|--------|------------------------------------|------|------------|-------|---------------------------------------------------------|

| 0x1064 | queue_threshold_control_63_32_no w | RO   | 0x00000000 | 32    | 3.3.207 queue_threshold_control_63_32_now on page 3-104 |

| 0×1078 | memory_address_max_31_00_now       | RO   | 0x00000010 | 32    | 3.3.208 memory_address_max_31_00_now on page 3-104      |

| 0x107C | memory_address_max_43_32_now       | RO   | 0x00000000 | 32    | 3.3.209 memory_address_max_43_32_now on page 3-104      |

| 0×1080 | access_address_min0_31_00_now      | RO   | 0x00000000 | 32    | 3.3.210 access_address_min0_31_00_now on page 3-105     |

| 0×1084 | access_address_min0_43_32_now      | RO   | 0x00000000 | 32    | 3.3.211 access_address_min0_43_32_now on page 3-105     |

| 0×1088 | access_address_max0_31_00_now      | RO   | 0x00000000 | 32    | 3.3.212 access_address_max0_31_00_now on page 3-105     |

| 0×108C | access_address_max0_43_32_now      | RO   | 0x00000000 | 32    | 3.3.213 access_address_max0_43_32_now on page 3-106     |

| 0x1090 | access_address_min1_31_00_now      | RO   | 0x00000000 | 32    | 3.3.214 access_address_min1_31_00_now on page 3-106     |

| 0x1094 | access_address_min1_43_32_now      | RO   | 0x00000000 | 32    | 3.3.215 access_address_min1_43_32_now on page 3-106     |

| 0x1098 | access_address_max1_31_00_now      | RO   | 0x00000000 | 32    | 3.3.216 access_address_max1_31_00_now on page 3-107     |

| 0×109C | access_address_max1_43_32_now      | RO   | 0x00000000 | 32    | 3.3.217 access_address_max1_43_32_now on page 3-107     |

| 0×10A0 | access_address_min2_31_00_now      | RO   | 0x00000000 | 32    | 3.3.218 access_address_min2_31_00_now on page 3-107     |

| 0×10A4 | access_address_min2_43_32_now      | RO   | 0x00000000 | 32    | 3.3.219 access_address_min2_43_32_now on page 3-107     |

| 0×10A8 | access_address_max2_31_00_now      | RO   | 0x00000000 | 32    | 3.3.220 access_address_max2_31_00_now on page 3-108     |

| 0x10AC | access_address_max2_43_32_now      | RO   | 0x00000000 | 32    | 3.3.221 access_address_max2_43_32_now on page 3-108     |

| 0×10B0 | access_address_min3_31_00_now      | RO   | 0x00000000 | 32    | 3.3.222 access_address_min3_31_00_now on page 3-108     |

| 0×10B4 | access_address_min3_43_32_now      | RO   | 0x00000000 | 32    | 3.3.223 access_address_min3_43_32_now on page 3-109     |

| 0×10B8 | access_address_max3_31_00_now      | RO   | 0x00000000 | 32    | 3.3.224 access_address_max3_31_00_now on page 3-109     |

| 0×10BC | access_address_max3_43_32_now      | RO   | 0x00000000 | 32    | 3.3.225 access_address_max3_43_32_now on page 3-109     |

| 0×10C0 | access_address_min4_31_00_now      | RO   | 0x00000000 | 32    | 3.3.226 access_address_min4_31_00_now on page 3-110     |

| 0x10C4 | access_address_min4_43_32_now      | RO   | 0×00000000 | 32    | 3.3.227 access_address_min4_43_32_now on page 3-110     |

Table 3-1 Register summary (continued)

| Offset | Name                          | Туре | Reset      | Width | Description                                            |

|--------|-------------------------------|------|------------|-------|--------------------------------------------------------|

| 0x10C8 | access_address_max4_31_00_now | RO   | 0x00000000 | 32    | 3.3.228 access_address_max4_31_00_now on page 3-110    |

| 0x10CC | access_address_max4_43_32_now | RO   | 0x00000000 | 32    | 3.3.229 access_address_max4_43_32_now on page 3-110    |

| 0x10D0 | access_address_min5_31_00_now | RO   | 0x00000000 | 32    | 3.3.230 access_address_min5_31_00_now on page 3-111    |

| 0x10D4 | access_address_min5_43_32_now | RO   | 0x00000000 | 32    | 3.3.231 access_address_min5_43_32_now on page 3-111    |

| 0x10D8 | access_address_max5_31_00_now | RO   | 0x00000000 | 32    | 3.3.232 access_address_max5_31_00_now on page 3-111    |

| 0x10DC | access_address_max5_43_32_now | RO   | 0x00000000 | 32    | 3.3.233 access_address_max5_43_32_now on page 3-112    |

| 0x10E0 | access_address_min6_31_00_now | RO   | 0x00000000 | 32    | 3.3.234 access_address_min6_31_00_now on page 3-112    |

| 0x10E4 | access_address_min6_43_32_now | RO   | 0x00000000 | 32    | 3.3.235 access_address_min6_43_32_now on page 3-112    |

| 0x10E8 | access_address_max6_31_00_now | RO   | 0x00000000 | 32    | 3.3.236 access_address_max6_31_00_now on page 3-113    |

| 0x10EC | access_address_max6_43_32_now | RO   | 0x00000000 | 32    | 3.3.237 access_address_max6_43_32_now on page 3-113    |

| 0x10F0 | access_address_min7_31_00_now | RO   | 0x00000000 | 32    | 3.3.238 access_address_min7_31_00_now on page 3-113    |

| 0x10F4 | access_address_min7_43_32_now | RO   | 0x00000000 | 32    | 3.3.239 access_address_min7_43_32_now on page 3-113    |

| 0x10F8 | access_address_max7_31_00_now | RO   | 0x00000000 | 32    | 3.3.240 access_address_max7_31_00_now on page 3-114    |

| 0x10FC | access_address_max7_43_32_now | RO   | 0x00000000 | 32    | 3.3.241 access_address_max7_43_32_now<br>on page 3-114 |

| 0x1110 | dci_replay_type_now           | RO   | 0x00000002 | 32    | 3.3.242 dci_replay_type_now on page 3-114              |

| 0x1120 | refresh_control_now           | RO   | 0x00000000 | 32    | 3.3.243 refresh_control_now on page 3-115              |

| 0x1128 | memory_type_now               | RO   | 0x00000101 | 32    | 3.3.244 memory_type_now on page 3-115                  |

| 0x1170 | scrub_control0_now            | RO   | 0x1F000000 | 32    | 3.3.245 scrub_control0_now on page 3-115               |

| 0x1174 | scrub_address_min0_now        | RO   | 0x00000000 | 32    | 3.3.246 scrub_address_min0_now on page 3-116           |

| 0x1178 | scrub_address_max0_now        | RO   | 0x00000000 | 32    | 3.3.247 scrub_address_max0_now on page 3-116           |

| 0x1180 | scrub_control1_now            | RO   | 0x1F000000 | 32    | 3.3.248 scrub_control1_now on page 3-116               |

| 0x1184 | scrub_address_min1_now        | RO   | 0x00000000 | 32    | 3.3.249 scrub_address_min1_now on page 3-116           |

| 0x1188 | scrub_address_max1_now        | RO   | 0x00000000 | 32    | 3.3.250 scrub_address_max1_now on page 3-117           |

| 0x1190 | scrub_control2_now            | RO   | 0x1F000000 | 32    | 3.3.251 scrub_control2_now on page 3-117               |

| 0x1194 | scrub_address_min2_now        | RO   | 0x00000000 | 32    | 3.3.252 scrub_address_min2_now on page 3-117           |

|        |                               | _    |            |       |                                                        |

Table 3-1 Register summary (continued)

| Offset | Name                   | Туре | Reset      | Width | Description                                  |

|--------|------------------------|------|------------|-------|----------------------------------------------|

| 0x1198 | scrub_address_max2_now | RO   | 0x00000000 | 32    | 3.3.253 scrub_address_max2_now on page 3-118 |

| 0x11A0 | scrub_control3_now     | RO   | 0x1F000000 | 32    | 3.3.254 scrub_control3_now on page 3-118     |

| 0x11A4 | scrub_address_min3_now | RO   | 0x00000000 | 32    | 3.3.255 scrub_address_min3_now on page 3-118 |

| 0x11A8 | scrub_address_max3_now | RO   | 0x00000000 | 32    | 3.3.256 scrub_address_max3_now on page 3-119 |

| 0x11B0 | scrub_control4_now     | RO   | 0x1F000000 | 32    | 3.3.257 scrub_control4_now on page 3-119     |

| 0x11B4 | scrub_address_min4_now | RO   | 0x00000000 | 32    | 3.3.258 scrub_address_min4_now on page 3-119 |

| 0x11B8 | scrub_address_max4_now | RO   | 0x00000000 | 32    | 3.3.259 scrub_address_max4_now on page 3-119 |

| 0x11C0 | scrub_control5_now     | RO   | 0x1F000000 | 32    | 3.3.260 scrub_control5_now on page 3-120     |

| 0x11C4 | scrub_address_min5_now | RO   | 0x00000000 | 32    | 3.3.261 scrub_address_min5_now on page 3-120 |

| 0x11C8 | scrub_address_max5_now | RO   | 0x00000000 | 32    | 3.3.262 scrub_address_max5_now on page 3-120 |

| 0x11D0 | scrub_control6_now     | RO   | 0x1F000000 | 32    | 3.3.263 scrub_control6_now on page 3-121     |